3位二进制译码器编程实现过程

- 格式:doc

- 大小:67.00 KB

- 文档页数:2

8-3编码器,3-8译码器的verilog实现在数字系统中,由于采⽤⼆进制运算处理数据,因此通常将信息变成若⼲位⼆进制代码。

在逻辑电路中,信号都是以⾼,低电平的形式输出。

编码器:实现编码的数字电路,把输⼊的每个⾼低电平信号编成⼀组对应的⼆进制代码。

设计⼀个输⼊为8个⾼电平有效信号,输出代码为原码输出的3位⼆进制编码器。

化简逻辑表达式:由逻辑表达式可以得出,普通的8-3编码器⽤或门即可实现。

对应的verilog程序如下:module mb_83(x,y);input [7:0]x;output [2:0]y;reg [2:0]y;always@(x)begincase (x)8'b00000001:y=3'b000; //当当 x=8 ’b00000001,则则 y 输出为 3 ’b0008'b00000010:y=3'b001; //当当 x=8 ’b00000010,则则 y 输出为 3 ’b0018'b00000100:y=3'b010; //当当 x=8 ’b00000100,则则 y 输出为 3 ’b0108'b00001000:y=3'b011; //当当 x=8 ’b00001000,则则 y 输出为 3 ’b0118'b00010000:y=3'b100; //当当 x=8 ’b00010000,则则 y 输出为 3 ’b1008'b00100000:y=3'b101; //当当 x=8 ’b00100000,则则 y 输出为 3 ’b1018'b01000000:y=3'b110; //当当 x=8 ’b01000000,则则 y 输出为 3 ’b1108'b10000000:y=3'b111; //当当 x=8 ’b10000000,则则 y 输出为 3 ’b111default: y=3'b000;endcaseendendmodule上述编码器有⼀个缺点,即在某⼀个时刻只允许有⼀个有效的输⼊,⽽同时若⼜有两个或两个以上的输⼊信号要求编码,输出端⼀定会发⽣混乱,出现错误。

3-8译码器实验报告

班级:121 姓名:连森学号:02

1.实验目标与实验要求:

1.理解译码器的概念和意义

2.理解译码器在计算机电路里的作用。

2.实验器材:

Altair 80C31Small 教学实验平台杜邦线

3.实验原理(电路图):

74HC138 是集成3-8 线译码器,能将3 位二进制码转换为8 位输出信号,这8 位输出信号相对于输入的3 位二进制码的8 种编码,始终只有一位输出有效(低电平),其余7 位皆无效(高电平)

4.实验步骤

首先用杜邦线将A3实验区与逻辑开关K1~K6相连的JP1-1~JP1-6,连接到A7实验区与74HC138相连的JP9单号插针;接着在74HC138的输出端连接绿色LED显示器;然后用跳线连接JP39-1与JP39-2,即可接通电源。

5.实验结果(现象):

当K4、K5、K6 打到0、0、1时,译码器74HC138 的逻辑功能有效,相应引脚输出低电平,对应LED 熄灭。

否则,74HC138 始终输出高电平(无效电平),LED 全亮。

74hc138的工作原理

74HC138是一种3-8译码器/多路复用器,其工作原理如下:

1. 数据输入:74HC138有三个数据输入引脚(A0,A1和

A2),用于输入3位二进制数据。

2. 使能输入:74HC138有一个使能输入引脚(E),用于启用

或禁用译码器/复用器的功能。

当E引脚为低电平时,译码器/

复用器功能被启用;当E引脚为高电平时,译码器/复用器功

能被禁用。

3. 使能极性选择:74HC138还有一个使能极性选择引脚(G)

和一个输出极性选择引脚(nY2A和nY2B),用于选择译码

器/复用器的工作模式。

根据G和nY2A/nY2B引脚的状态,

可以选择正常译码器模式或扩展译码器模式。

4. 译码器功能:在正常译码器模式下,当E引脚为低电平时,根据输入的3位二进制数据,在8个输出引脚(Y0-Y7)中的

一个引脚上产生逻辑高电平,并在其他引脚产生逻辑低电平。

输出引脚的选择由输入数据决定。

例如,当输入数据为000时,Y0引脚将为高电平,其他引脚将为低电平。

这样,可以将一

个8位信号从3位数据选择输入引脚上的一个引脚输出。

5. 多路复用器功能:在扩展译码器模式下,当E引脚为低电

平时,通过设置输入的3位二进制数据,可以将8个输入通道的数据选择到一个输出引脚上(Y0-Y7)。

例如,当输入数据

为000时,从输入引脚Y0上的信号将传递到Y7引脚上。

这

可以实现数据的多路复用功能。

综上所述,74HC138是一种3-8译码器/多路复用器,根据输入数据的不同,在输出引脚上产生逻辑高电平,从而实现数据的选择和复用功能。

3 8译码器实验报告3 8译码器实验报告引言:在数字电路中,译码器是一种常见的逻辑电路,用于将输入的二进制编码转换为对应的输出信号。

本实验旨在通过搭建一个3 8译码器电路,并对其进行测试和分析,以加深对译码器工作原理的理解。

实验目的:1. 理解3 8译码器的基本原理和工作方式;2. 掌握搭建3 8译码器电路的方法;3. 进行实验测试并分析结果。

实验器材:1. 3 8译码器芯片;2. 逻辑门芯片(与门、非门等);3. 连线板、导线等。

实验步骤:1. 将3 8译码器芯片和逻辑门芯片连接到连线板上;2. 根据芯片引脚的连接要求,使用导线将各个芯片的输入和输出连接起来;3. 将输入信号接入3 8译码器芯片的输入端;4. 将输出信号接入逻辑门芯片的输入端;5. 将逻辑门芯片的输出信号连接到LED灯或其他输出设备上;6. 调整输入信号,观察输出信号的变化。

实验结果:通过实验,我们得到了以下结果:1. 当输入信号为000时,输出信号为00000001;2. 当输入信号为001时,输出信号为00000010;3. 当输入信号为010时,输出信号为00000100;4. 当输入信号为011时,输出信号为00001000;5. 当输入信号为100时,输出信号为00010000;6. 当输入信号为101时,输出信号为00100000;7. 当输入信号为110时,输出信号为01000000;8. 当输入信号为111时,输出信号为10000000。

结果分析:根据实验结果,我们可以看到,3 8译码器将输入的三位二进制编码转换为对应的八位输出信号。

每个输出信号代表一个特定的输入编码。

通过观察输出信号的变化,我们可以清晰地看到译码器的工作原理:根据输入编码的不同,译码器会激活对应的输出线路,将其输出为高电平信号,而其他输出线路则为低电平信号。

实验总结:通过本次实验,我们深入了解了3 8译码器的工作原理和应用场景。

译码器在数字电路中扮演着重要的角色,能够将复杂的二进制编码转换为易于理解和使用的信号输出。

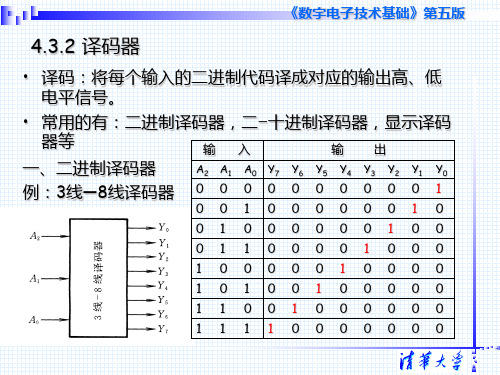

3-8译码器工作原理译码是编码的反过程。

编码是将信号转换成二进制代码,译码则是将二进制代码转换成特定的信号。

将输入的二进制代码转换成特定的高(低)电平信号输出的逻辑电路称为译码器。

假设译码器由n个输入信号和N个输出信号,如果满足N=2n,就称为全译码器,又称二进制译码器,常见的全译码器由2-4线译码器、3-8线译码器、4-16线译码器等。

如果满足N<2n,称为部分译码器,如二-十进制译码器(又称4-10译码器)、显示译码器等。

3-8线译码器是一种全译码器(二进制译码器)。

全译码器的输入是3位二进制代码,3位二进制代码共有8种组合,故输出是与这8种组合一一对应的8个输出信号。

译码器将每种二进制的代码组合译成对应的一根输出线上的高(低)电平信号。

因此这种译码器也称为3-8线译码器。

图5-44时5-6-1线译码器的框图。

图1 3-8线译码器框图根据3-8线译码器的逻辑功能可以列出它的逻辑真值表,如表1所示。

从表1中所示可以看出,输入信号的每一种组合对应着一个输出端的高电平信号,即输出端为高电平(1)时认为该输出端有输出信号。

当然,根据有需要也可以定义输出端为低电平(0)时认为该输出端有输入信号,此时称输出端低电平有效。

表1 3-8线译码器的逻辑真值表输入输出A2A1A0Y7Y6Y5Y3 Y2 Y1 Y00 0 0 0 0 0 0 0 0 0 10 0 1 00 0 0 0 1 00 1 0 0 0 0 0 0 1 0 00 10 0 0 0 1 0 0 01 0 0 0 0 0 1 0 0 0 00 1 0 0 1 0 0 0 0 01 1 0 0 1 0 0 0 0 01111根据真值表可以写出逻辑函数式为(1)根据逻辑函数式可以画出3-8线译码器的逻辑电路,如图2所示。

图2 3.8线译码器的逻辑电路图。

3-8译码器原理3-8译码器是一种数字电路,它将一个3位二进制数转换为8个输出信号之一。

它的原理是基于布尔代数和逻辑门电路实现的。

下面将详细介绍3-8译码器的原理。

3-8译码器由三个输入引脚和八个输出引脚组成。

输入引脚是A0、A1和A2,它们可以是0或1。

输出引脚是Y0到Y7,它们中的一个会被激活,其它的则处于非激活状态。

当输入引脚的二进制值为000时,输出引脚Y0会被激活。

当输入引脚的二进制值为001时,输出引脚Y1会被激活,以此类推,直到输入引脚的二进制值为111时,输出引脚Y7会被激活。

3-8译码器的实现基于布尔代数和逻辑门电路。

首先,使用Karnaugh图或真值表来确定每个输出引脚的布尔表达式。

然后,使用逻辑门电路来实现这些布尔表达式。

在3-8译码器中,使用了AND门、NOT门和OR门。

对于每个输出引脚,都需要一个布尔表达式。

例如,对于输出引脚Y0,其布尔表达式为:Y0 = A2' A1' A0'其中,A2'表示A2的反相,A1'表示A1的反相,A0'表示A0的反相。

这个布尔表达式表示当A2、A1和A0都为0时,Y0会被激活。

对于每个布尔表达式,都需要使用逻辑门电路来实现。

例如,对于Y0的布尔表达式,可以使用三个NOT门和一个AND门来实现。

首先,使用三个NOT门来反相A2、A1和A0,然后将它们的输出连接到一个AND门的输入引脚上。

当A2、A1和A0都为0时,三个NOT门的输出都为1,这样AND门的输出就会变为1,从而激活Y0。

3-8译码器的原理基于布尔代数和逻辑门电路实现。

它可以将一个3位二进制数转换为8个输出信号之一。

对于每个输出引脚,都需要一个布尔表达式和一个逻辑门电路来实现。

3-8译码器在数字电路中有广泛的应用,例如在计算机内存芯片中用于选择特定的存储单元。

三位二进制译码器实现过程

数字电路中的译码器的逻辑功能就是将输入的二进制代码转译成各路高、低电平信号输出。

3位二进制译码器有3个输入信号,可以用3位二进制代码组成8种不同的状态,3位二进制译码器的功能是将每个输入代码转译成8条输出线上不同的高、低电平信号,因此有时也称这种译码器为3线—8线译码器。

真值表如下图所示:

使用LabVIEW实现3位二进制译码器,具体步骤如下:

1、新建“3位二进制译码器.vi”。

2、在前面板上新建2个以布尔型控件为元素的簇。

第一个簇放置A0、A1、

A2输入型布尔,表示输入变量。

第二个簇放置8个布尔型控件,Y0、Y1、Y2、Y3、Y4、Y5、Y6、Y7,表示输出变量,这2个簇同时也是VI的输入

和输出参数。

如下图所示。

图 1

3、在程序框图页面放置8个复合运算符,设置逻辑关系为“与”;在簇与变

体函数中寻找“按名称解除捆绑”连线板放置在程序框图页面,设置为3输出;在簇与变体函数中寻找“按名称捆绑”连线板放置在程序框图页面,设置为8个元素的输入。

4、连线。

首先将输入簇A0-A3与“按名称解除捆绑”连线板的输入相连,

更改输出接线端的元素名为A0、A1、A2;其次,按照前面推导出的特性方程进行连线,将A0、A1、A2输出端分别与8个复合运算符的3个输入端相连接,注意运算符输入端是否需要翻转;最后,将8个逻辑运算符的输出端依次与“按名称捆绑”连线板的8个输入端相连,把输出与输出簇相连接,更改“按名称捆绑”连线板输入端的元素名称为Y0-Y7。

5、运行调试程序。

最终程序的框图如下图所示。

图 2。