74LS160计数器

- 格式:docx

- 大小:56.31 KB

- 文档页数:3

目录一参考资料························( 2 )二工作原理························( 7 )三引脚图························( 8 )四电路图························( 9 )一参考资料(一)74LS4874LS48的管脚排列如图(c)所示。

其真值表如表3所示。

该器件输入信号为BCD码,输出端为a、b、c、d、e、f、g共7线,另有3条控制线LE、RBI、BI/RBO。

LE端为测试端。

在BI端接高电平的条件下,当LE=0时,无论输入端A、B、C、D为何值,a~g输出全为高电平,使7段显示器件显示“8”字型,此功能用于测试器件。

RBI端为灭零输入端。

在LE=1,BI =1条件下,当输入A、B、C、D=0000时,输出a~g全为低电平,可使共阴LED显示器熄灭。

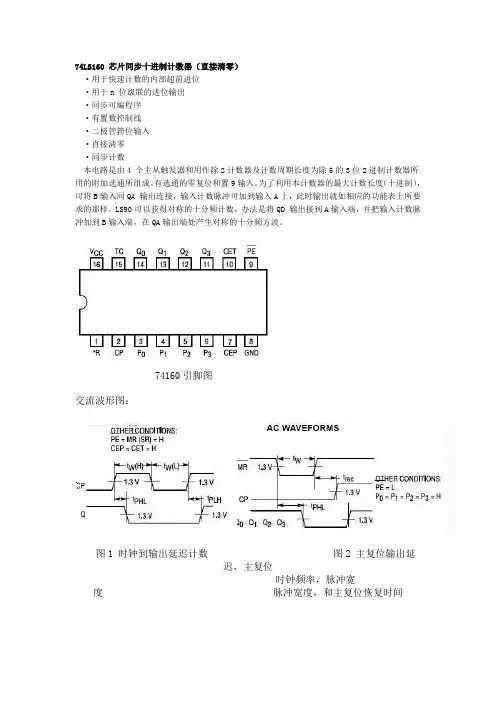

74LS160 芯片同步十进制计数器(直接清零)·用于快速计数的内部超前进位·用于n 位级联的进位输出·同步可编程序·有置数控制线·二极管箝位输入·直接清零·同步计数本电路是由4 个主从触发器和用作除2计数器及计数周期长度为除5的3位2进制计数器所用的附加选通所组成。

有选通的零复位和置9输入。

为了利用本计数器的最大计数长度(十进制),可将B输入同QA 输出连接,输入计数脉冲可加到输入A上,此时输出就如相应的功能表上所要求的那样。

LS90可以获得对称的十分频计数,办法是将QD 输出接到A输入端,并把输入计数脉冲加到B输入端,在QA输出端处产生对称的十分频方波。

74160引脚图交流波形图:图1 时钟到输出延迟计数图2 主复位输出延迟,主复位时钟频率,脉冲宽度脉冲宽度,和主复位恢复时间状态图VHDL十进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity count10 isport (clk:in std_logic;f:buffer integer range 0 to 15;cout:out std_logic);end;architecture aa of count10 isbeginprocess(clk)beginif falling_edge(clk) thenif f=9 thenf<=0;cout<='1';elsef<=f+1;end if;elsenull;end if;end process;end;十进制计数器VHDLlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--**************实体*****************entity shijinzhi isport(clk: in std_logic;reset: in std_logic;s : out std_logic_vector(5 downto 0);out1: out std_logic_vector(7 downto 0));end shijinzhi;--*****************结构体***********************architecture one of shijinzhi issignal clk_500 : std_logic;--扫描时钟signal clk_1 : std_logic;--1s时钟begin--*************500Hz分频程序********************process(clk)variable cnt1 : integer range 0 to 200;variable cnt2 : integer range 0 to 250;beginif clk'event and clk='1' thenif cnt1=200 thencnt1:=0;if cnt2=250 thencnt2:=0;clk_500<=not clk_500;elsecnt2:=cnt2+1;end if;elsecnt1:=cnt1+1;end if;end if;end process;--***********1Hz分频程序和扫描信号产生********************process(clk_500)variable cnt3 : integer range 0 to 250;beginif clk_500'event and clk_500='1' thenif cnt3=250 thencnt3:=0;clk_1<=not clk_1;elsecnt3:=cnt3+1;end if;end if;end process;--****************************************process(clk_1,reset)variable count1:integer range 0 to 9;beginif reset='0' then count1:=0;elsif clk_1'event and clk_1='1' thenif count1=9 thencount1:=0;elsecount1:=count1+1;end if;end if;if clk_500='1' thencase count1 isWHEN 0 =>s<="111110";out1<="10111111";WHEN 1 =>s<="111110";out1<="10000110";WHEN 2 =>s<="111110";out1<="11011011";WHEN 3 =>s<="111110";out1<="11001111";WHEN 4 =>s<="111110";out1<="11100110";WHEN 5 =>s<="111110";out1<="11101101";WHEN 6 =>s<="111110";out1<="11111101";WHEN 7 =>s<="111110";out1<="10000111";WHEN 8 =>s<="111110";out1<="11111111"; WHEN 9 =>s<="111110";out1<="11101111";when others=>out1<="00000000";end case;end if;end process;end one;。

74ls160十进制计数器原理

74LS160十进制计数器原理74LS160是一种常用的十进制计数器,它能够实现0至9的循环计数。

它的原理基于二进制计数和锁存器的结合。

该计数器由四个D触发器组成,每个触发器都能存储一个二进制位。

在计数过程中,每当一个触发器的输出从低电平变为高电平时,它会向高位触发器传递一个脉冲信号。

这样,当最低位的触发器计数到9时,它会向高位触发器传递一个脉冲信号,使得高位触发器加1,而最低位触发器归零。

为了实现循环计数,74LS160还包含一个复位功能。

当外部信号复位输入为低电平时,所有触发器的输出都会被清零,计数器重新从0开始计数。

除了计数功能,74LS160还具有一个使能输入。

当使能输入为低电平时,计数器将会被禁用,不再进行计数。

这个功能可以用于控制计数器的启动和停止。

总结起来,74LS160十进制计数器通过二进制计数和锁存器的结合,实现了0至9的循环计数。

它具有复位和使能功能,可以灵活控制计数器的启动和停止。

这使得它在很多应用中都有广泛的使用,如时钟、计时器、频率分析等。

实

验

报

告

实验项目:74LS160置数

班级:电子111

指导老师:林梅

学生:刘欣琦

学号:

时间:2012年11月1日

74LS160组成进制计数器

●实验内容:

●掌握集成计数器的功能测试及应用。

●用异步清零端设计6进制计数器。

●用同步置0设计7进制计数器。

●仿真实验:

74LS160引脚图

逻辑图

74LS160 七进制计数器

74LS160 十进制计数器

74LS160 2-7计数器

异步74LS160 七进制计数器

异步74LS160 3-6进制计数器

两个74LS160 一百进制计数器

●实验总结:

●任意进制计数器的构成方法,只能用已有的芯片通过外电路的不同连接改变。

●若没法使之跳过(n-m)个状态,就可以得到m进制计数器了。

●其中方法有置零法(复位法)和置数法(置位法)。

●实验体会:

●感觉这些仿真实验挺容易的,比较喜欢。

●还是要好好了解芯片的功能。

●本次实验报告还是没有太完善,不太会。

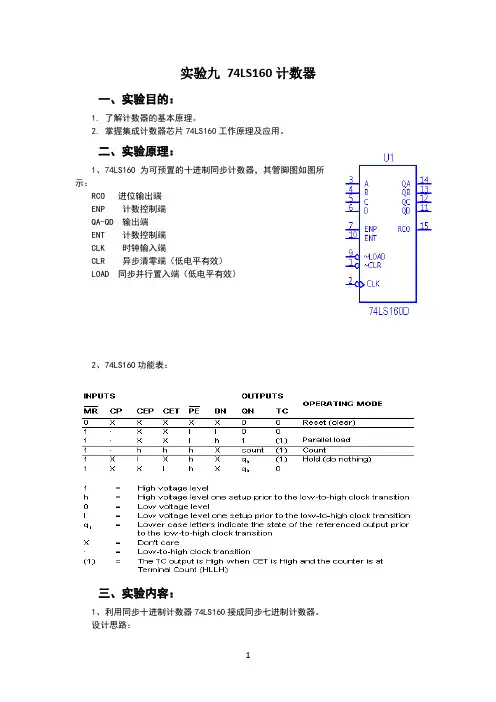

实验九74LS160计数器

一、实验目的:

1. 了解计数器的基本原理。

2. 掌握集成计数器芯片74LS160工作原理及应用。

二、实验原理:

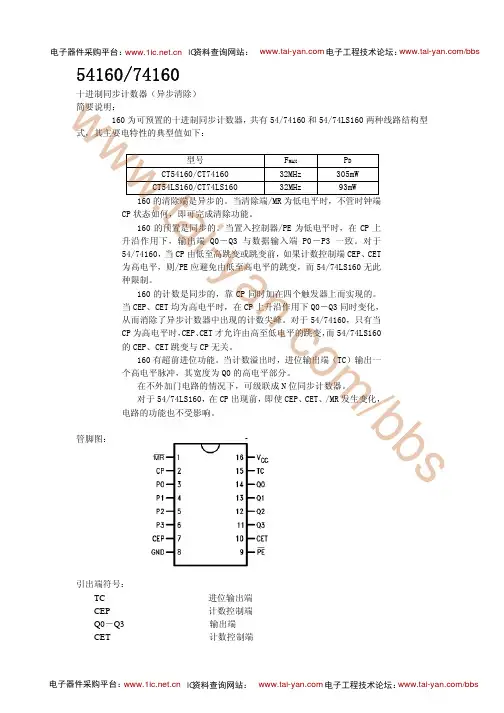

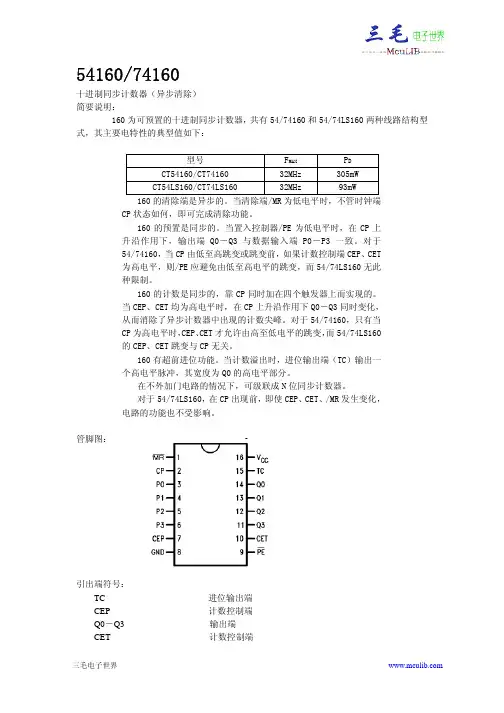

1、74LS160 为可预置的十进制同步计数器,其管脚图如图所示:

RCO 进位输出端

ENP 计数控制端

QA-QD 输出端

ENT 计数控制端

CLK 时钟输入端

CLR 异步清零端(低电平有效)

LOAD 同步并行置入端(低电平有效)

2、74LS160功能表:

三、实验内容:

1、利用同步十进制计数器74LS160接成同步七进制计数器。

设计思路:

列出七进制计数器的真值表:

计数顺序

电路状态等效

十进制

进位

输出

C Q3Q2Q1Q0

0000000

1000110

2001020

3001130

4010040

5010150

6011061

由真值表的逻辑函数式:

Y’= (Q’0Q1Q2Q’3)’

化简得:

Y= (Q1Q2)’

于是得设计电路:

2、试用同步十进制计数器74LS160接成16进制计数器。

设计思路:

74LS160是10进制计数器,要做成16进制计数器,先要做一个比16大的计时器。

这里用两片74LS160接成一个100进制计数器,再通过置0法实现16进制计数。

设计电路:

四、实验分析:

1、通过本实验,让我进一步了解74LS160计数器的基本原理。

基本掌握集成计数器芯片74LS160工作原理及应用。

2、设计电路时,注意思路清晰,结果简单易懂。

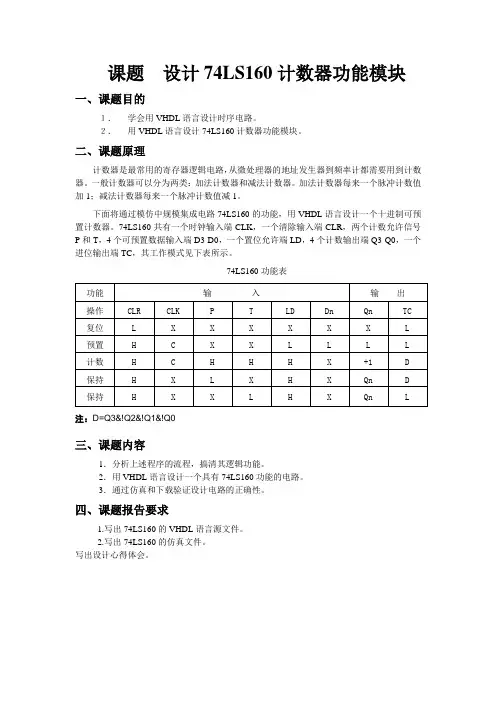

课题设计74LS160计数器功能模块一、课题目的

1.学会用VHDL语言设计时序电路。

2.用VHDL语言设计74LS160计数器功能模块。

二、课题原理

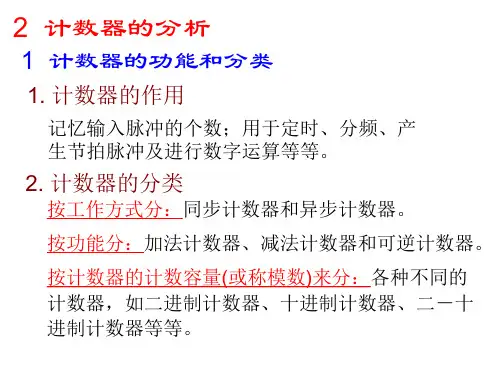

计数器是最常用的寄存器逻辑电路,从微处理器的地址发生器到频率计都需要用到计数器。

一般计数器可以分为两类:加法计数器和减法计数器。

加法计数器每来一个脉冲计数值加1;减法计数器每来一个脉冲计数值减1。

下面将通过模仿中规模集成电路74LS160的功能,用VHDL语言设计一个十进制可预置计数器。

74LS160共有一个时钟输入端CLK,一个清除输入端CLR,两个计数允许信号P和T,4个可预置数据输入端D3-D0,一个置位允许端LD,4个计数输出端Q3-Q0,一个进位输出端TC,其工作模式见下表所示。

74LS160功能表

注:D=Q3&!Q2&!Q1&!Q0

三、课题内容

1.分析上述程序的流程,搞清其逻辑功能。

2.用VHDL语言设计一个具有74LS160功能的电路。

3.通过仿真和下载验证设计电路的正确性。

四、课题报告要求

1.写出74LS160的VHDL语言源文件。

2.写出74LS160的仿真文件。

写出设计心得体会。

一、介绍74LS160和与非门74LS160是一种集成电路,属于同步可编程计数器类型。

它有4位译码器,能够对4位二进制或BCD输入进行10进制译码,并在高电平有效的时钟输入与地位复位输入下进行同步计数。

另外,与非门是一种逻辑门电路,它具有两个输入和一个输出。

当两个输入同时为高电平时,输出为低电平,否则输出为高电平。

二、74LS160和与非门设计9进制的例题考虑如何设计一个电路,输入一个10进制数并将其转换为9进制数。

这个问题可以通过结合74LS160和与非门来实现。

1. 使用74LS160进行计数我们可以使用74LS160来进行十进制到九进制的转换。

将该集成电路配置为BCD计数器,然后将其输出连接到与非门。

2. 设计与非门之后,我们需要设计一个与非门电路来实现十进制到九进制的转换。

我们可以使用多个与非门电路来将74LS160的输出进行适当的逻辑运算,以得到对应的九进制输出。

3. 组合电路接下来,将74LS160的输出连接到与非门的输入端口,并将与非门的输出连接到输出端口,这样就构成了一个适用于将十进制转换为九进制的组合电路。

在时钟信号作用下,74LS160会将输入的十进制数进行计数,并输出对应的BCD码,而与非门则根据逻辑设计的条件将BCD码转换成九进制数。

4. 电路测试进行电路测试,观察输入不同的十进制数时输出的九进制数是否正确。

在确认电路设计无误后,就可以将其用于实际的十进制到九进制的转换需求。

结合74LS160和与非门可以设计一个用于将十进制数转换为九进制数的逻辑电路。

该电路的设计涉及到了对74LS160和与非门的理解、逻辑门电路的设计和组合以及电路的测试。

通过合理的设计和连接,可以实现将十进制数转换为九进制数的功能。

以上就是关于使用74LS160和与非门设计九进制的例题的相关内容,希望能对您有所帮助。

五、#xFF19;#x8F6C;#x6362;#x4E3A;#xFF18;#x8F6C;#x6362;#x5668;#x7684;#x8BBE;#x8BA1;#x8FD9;#x4E2A;#x95EE;#x9898;#x53EF;#x4EE5;#x4F7F;#xxxxLS1 60;#x53CA;#x4E0E;#x4E0E;#x975E;#x95EE;#x95EE;#x95EE;#x59D 4;#x6258;#x8BBE;#x8BA1;#x4E00;#x4E2A;#xFF18;#x8F6C;#x6362; #x5668;#xFF0C;#x8FD9;#x662F;#x56E0;#x4E3A;#x4E3A;#x4EC0;# x4E48;#x4F1A;#x5E94;#xxxxLS160;#x4F5C;#x7528;#xFF1F;1. #x903B;#x8F91;#x610F;#x8C61;#xxxxLS160;#x64CD;#x4F5C;#x4E0E;#x4E8C;#x8FDB;#x5236;#x6 B65;#x7136;#x540E;#x8FDB;#x884C;#x8BBE;#x8BA1;#x7684;#x5 39F;#x56E0;#x662F;#x56E0;#x4E3A;#x5B83;#x5177;#x6709;#x5F 53;#x524D;#x8BBE;#x5907;#x662F;#x6B63;#x5728;#x4F7F;#x752 8;#x7684;#x540C;#x6B65;#x7C7B;#x53EF;#x7F16;#x7A3B;#x8BA1 ;#x6570;#x5668;#xFF0C;#x53EF;#x4EE5;#x5BF9;#xFF18;#x8F6C;# x6362;#x8FDB;#x884C;#x8BA1;#x6570;#x3002;2.BCD#x8F93;#x51FA;#x5668;#x7684;#x82E5;#x672A;#x88AB;#x6F C0;#x6D3B;#xFF0C;#x662F;#x5176;#x62AC;#x5C5E;#x4E8E;#x4E0 0;#x79CD;#x4E0D;#x6B63;#x786E;#x72B6;#x6001;#xFF0C;#x8FD 9;#x4E5F;#x5C31;#x4F1A;#x5BF9;#x6700;#x540E;#x7684;#xFF18; #x8F6C;#x6362;#x7ED3;#x679C;#x9020;#x6210;#x5F71;#x54CD; #xFF0C;#x4E5F;#x4E3A;#x4EC0;#x4E48;#x9700;#x8981;#x8D4B;# x4E88;#x53EF;#x6BD4;#x7684;#xFF19;#x8F6C;#x6362;#x7ED3;#x 679C;#x3002#x4E00;#x4E2A;#x53EF;#x80FD;#x7684;#x89E3;#x51B3;#x65B9;# x6848;#x662F;#x653E;#x7F6E;#x4E00;#x4E2A;#x8D85;#x7EBF;#x 4F9B;#xxxxLS160#x7684;#x63A5;#x53E3;#xFF0C;#x5728;#x7F16;#x7A0B;#x4E2D;#x5728;#x914D;#x7F6E;#x4E00;#x4E2A;#x589E; #x5220;#x65B9;#x6CD5;#x8FDB;#x884C;#x521B;#x5EFA;#x3002#xFF19;#x8F6C;#x6362;#x7ED3;#x679C;#x7684;#x5B9E;#x73B0; #x6709;#x4E86;#x5982;#x4E0A;#x8BBE;#x8BA1;#x7684;#x6309;# x7167;#xFF0C;#x6307;#x5B9A;#x4E86;#x4E00;#x4E2A;#xFF18;#x 8F6C;#x6362;#x5668;#x7684;#x6240;#x6709;#x5165;#x53E3;#xF F0C;#x5386;#x53F2;#x6570;#x636E;#x662F;#x4E0D;#x53EF;#x8D 85;#x8FC7;#xFF19;#x7684;#xFF0C;#x8FD9;#x6837;#x5728;#x4E0 A;#xxxxLS160#x7684;#x6A21;#x677F;#x4E0A;#x8BA1;#x6570;#x 5668;#x53EF;#x4EE5;#x8F6C;#x6362;#xFF19;#x5747;#x6570;#x76 84;#x6570;#x636E;#x3002#x8FD9;#x6837;#x8FD0;#x7B97;#x4E0 0;#x4E2A;#xFF18;#x8F6C;#x6362;#x8FDB;#x884C;#x8BA1;#x6570 ;#xFF0C;#x5E76;#x8F6C;#x6362;#xFF19;#x8F6C;#x6362;#x6765;# x6E90;#x8FD9;#x6837;#xFF0C;#x5728;#x6B64;#x540E;#x8FD0;#x 7B97;#x5668;#x5C31;#x53EF;#x4EE5;#x628A;#xFF18;#x8F6C;#x6 362;#x6210;#xFF19;#x8F6C;#x6362;#x66F4;#x6362;#x7684;#x67 81;#x6548;#x6570;#x636E;#x3002#x5168;#x90E8;#x6240;#x6709;#x7684;#x8FC7;#x7A0B;#x66F4;# x6362;#x5DF2;#x5B8C;#x6210;mdash;mdash;#x63A5;#x6536;#xF F18;#x8F6C;#x6362;#x7684;#x7E41;#x8EAB;#x7684;#x6307;#x4E E4;#xFF0C;#x63A5;#x53D7;#xFF18;#x8F6C;#x6362;#x7684;#x5360;#x7A0B;#x5EA6;#x6216;#x8005;#x7E73;#x653E;#x8F93;#x51FA; #xFF0C;#x548C;#x5220;#x9664;#x8FD9;#x4E9B;#x6570;#x636E;# xFF0C;#x5E76;#x5728;#x6700;#x540E;#x4E00;#x6B21;#x4F7F;#xx xx#x8F6C;#x6362;#x5668;#x60F3;#x5267;#x65E0;#x4E8B;#x65B9; #x5F0F;#x6765;#x589E;#x52A0;#x6216;#x8005;#x4F24;#x5BB3;# x8FD9;#x4E9B;#x6570;#x636E;#x3002六、电路测试完成电路设计后,需要对电路进行测试来验证其功能和性能。

参考资料工作原理引脚图四电路图寸录参考资料(一)74LS474LS48的管脚排列如图(c)所示。

其真值表如表3所示。

该器件输入信号为BCD码, 输出端为a、b、c、d、e、f、g共7线,另有3条控制线LE RBI、Bl/RBO。

LE端为测试端。

在BI端接高电平的条件下,当LE=0时,无论输入端A B、C、D为何值,a〜g输出全为高电平,使7段显示器件显示8”字型,此功能用于测试器件。

RBI端为灭零输入端。

在LE =1,BI =1条件下,当输入A、B C D=0000时,输出a〜g全为低电平,可使共阴LED显示器熄灭。

但当输入A B C D不全为零时,仍能正常译码输出,使显示器正常显示。

BI端为消隐输入端。

该输入端具有最高级别的控制权,当该端为低电平时,不管其他输入端为何值,输出端a〜g均为低电平,这可使共阴显示器熄灭。

另外,该端还有第二功能一一灭零信号输出端,记为RBO。

当该位输入的A、B、C、D=0000且RBI =0时,此时RBO输出低电平;若该位输入的A B C、D不等于零,则RBO 俞出高电平。

若将RBO与RBI配合使用,很容易实现多位数码显示时的灭零控制。

例如对整数部分,将最高位的RBI接地,这样当最高位为零时灭零”,同时该位RBO输出低电平,使下一位的RBI 为低电平,故也具有灭零”功能;而对于小数部分,应将最低位的RBI接地,个位的RBI端悬空或接高电平,低位的RBO接至高位的RBI。

74LS48可直接驱动共阴极LED数码管而不需外接限流电阻。

V cc CO Q o Q i Q2 Q3 ET LD]6~|15网何121冋而|~9~1 J 74LS160[1J|2J|3J[4J |5 J |6| L7 [8JRD CP D o D i D2 D3 EP GND表3 74LS48七段显示译码器的真值表输入输出显示字型LT D C B A g f e d c b0X 1 X X X 'X !11111 11 01000 0 00000 0 0 灭X X 0X X X X 0Q 0 0 0 0 0 灭I1 1 0 0000 1 1 1 1 1 1 01 X100 0 1000 0 1 10 I1X 1 00 10 1 01 1 D1121X 1 00 11100111 1 31X 1 01001t0110 1 41 X 1 0101] 101 1 0 1 51 X 1 0 1 101!1 1 10 0 61 X 1 01 1 10000 1 1 1 71 X 1 10 0 01] 1 1 1 1181X 1 1 0 0 1 1 1 0 0 1 I191X 1 1 0 10 1 0 1 000无效输出1X 1 * ] 1 110 0 0 00 0(二)74LS003Y现四2输入与非门(三)集成计数器74LS1601.74LS160为异步清零计数器,即RD端输入低电平,不受CP控制,输出端立即全部为“ 0” 功能表第一行。

实验九74LS160计数器

一、实验目的:

1. 了解计数器的基本原理。

2. 掌握集成计数器芯片74LS160工作原理及应用。

二、实验原理:

1、74LS160 为可预置的十进制同步计数器,其管脚图如图所示:RCO 进位输出端

ENP 计数控制端

QA-QD 输出端

ENT 计数控制端

CLK 时钟输入端

CLR 异步清零端(低电平有效)

LOAD 同步并行置入端(低电平有效)

2、74LS160功能表:

三、实验内容:

1、利用同步十进制计数器74LS160接成同步七进制计数器。

设计思路:

列出七进制计数器的真值表:

设计该电路要求在6时进位,即在输出为6时给输入端置0。

由真值表的逻辑函数式:

Y’= (Q’0Q1Q2Q’3)’

化简得:

Y= (Q1Q2)’

于是得设计电路:

2、试用同步十进制计数器74LS160接成16进制计数器。

设计思路:

74LS160是10进制计数器,要做成16进制计数器,先要做一个比16大的计时器。

这里用两片74LS160接成一个100进制计数器,再通过置0法实现16进制计数。

设计电路:

四、实验分析:

1、通过本实验,让我进一步了解74LS160计数器的基本原理。

基本掌握集成计数器芯片74LS160工作原理及应用。

2、设计电路时,注意思路清晰,结果简单易懂。