CYCLONE2 特殊引脚

- 格式:doc

- 大小:36.50 KB

- 文档页数:5

一、外文资料译文:Cyclone II器件系列简介关键词:cyclone II器件;特点;简介;在非常成功的第一代Cyclone器件系列之后,Altera的Cyclone II FPGA系列扩大低成本的FPGA的密度,最多达68,416个逻辑单元(LE),提供622个可用的输入/输出引脚和1.1M比特的嵌入式寄存器。

Cyclone II器件的制造基于300毫米晶圆,采用台积电90nm、低K值电介质工艺,这种工艺技术是使用低绝缘体过程以确保了快速有效性和低成本。

通过使硅片面积最小化,Cyclone II器件可以在单芯片上支持复杂的数字系统,而在成本上则可以和ASIC竞争。

不像其他用电力功耗和性能来换取低成本的FPGA卖主,Altera 最新一代低价位的FPGA——cyclone II FPGA系列,和同类90nmFPGA器件相比,它提高了百分之六十的性能和降低了一半的功耗。

低成本和优化特征使Cyclone II FPGA系列为各种各样的汽车、消费、通讯、视频处理、测试与测量、和其他最终市场提供理想的解决方案。

在参考设计、系统图,和IP,使用cyclone II FPGA系列可以帮助你迅速实现最总市场方案开发。

低成本的嵌入式解决方案Cyclone II 器件支持Nio s II 嵌入式处理器,能够自己完成自定义的嵌入式处理器。

Cyclone II器件还能够扩展各种外部存储器和I/O口或者嵌入式处理器的性能。

单个或多个NiosII嵌入式系统中嵌入式处理器也可以设计成cyclone II设备以提供一些额外的同时处理的能力或者甚至取代已经在你的系统中存在的嵌入式处理器。

使用cyclone II和nios II 能够拥有成本低和高性能处理方案的共同特点,和普通的产品相比,这个特点能够延长你的产品的生命周期,提高产品进入市场的时间。

低成本DSP方案单独使用cycloneII FPGA 系列或者或者作为数字信号处理(DSP)协处理器以提高数字信号处理(DSP)应用的性价比。

一、功能描述:Cyclone II 器件包括一个二维的行和列式架构来实现定制逻辑。

不同速度的行和列互连提供逻辑阵列模块(LABs),嵌入式存储模块和嵌入式乘法器。

逻辑阵列由LABs组成,每个LAB中有16个逻辑单元。

逻辑单元是实现用户逻辑功能的最小逻辑单位。

逻辑阵列模块分为行和列跨设备。

Cyclone II器件密度范围从4608到68416。

Cyclone II器件提供一个全局时钟网络和四个锁相环(PLLs)。

全局时钟网络由16个全局时钟线组成,全局时钟线可以驱动整个器件。

全局时钟网络可以为器件内的所有资源提供时钟,像输入/输出单元,锁存单元,嵌入式乘法器和嵌入式存储模块。

全局时钟线也可作为高扇出信号。

Cyclone II PLLs 提供通用时钟,该通用时钟具有时钟合成,相移以及高速差分I/O支持的外部输出。

M4K寄存器模块是内存加校验位为4K位的双端口寄存器模块。

这些模块提供高达260MHz的专用双端口,简单单端口或者高达36位的单端口寄存器。

在某些LABs之间这些块排列成列贯穿整个器件。

Cyclone II器件提供119到1152Kbits的嵌入式寄存器。

性能达到250MHz的嵌入式乘法器模块可以通过两个9*9位或者一个18*18位的乘法器实现。

嵌入式乘法器按列排列在整个器件内。

遍布在Cyclone II器件周围的I/O管脚由IOE反馈,IOE位于LAB行和列的终端。

I/O管脚支持各种单端和差分I/O标准,比如66MHz和33MHz,64位和32位PCI标准,PCI-X,和LVDS I/O标准,LVDS I/O标准的最大输入数据率为805Mbps和最大输出数据率为640Mbps。

每个IOE包括一个双向I/O缓冲区和三个寄存输入,输出和输出使能信号的三个寄存器。

随同延迟链一起的双用途DQS,DQ和DM管脚为外部寄存器提供高达167MHz的表面支持,寄存器如DDR,DDR2和单数据率SDRAM,和QDRII SRAM器件。

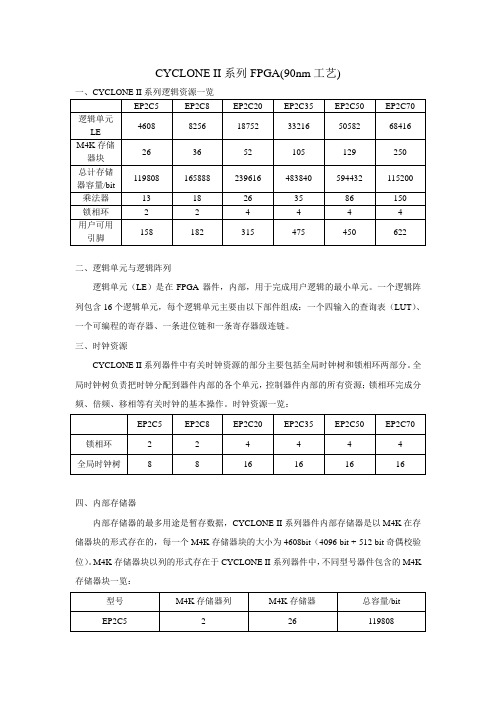

CYCLONE II系列FPGA(90nm工艺)二、逻辑单元与逻辑阵列逻辑单元(LE)是在FPGA器件,内部,用于完成用户逻辑的最小单元。

一个逻辑阵列包含16个逻辑单元,每个逻辑单元主要由以下部件组成:一个四输入的查询表(LUT)、一个可编程的寄存器、一条进位链和一条寄存器级连链。

三、时钟资源CYCLONE II系列器件中有关时钟资源的部分主要包括全局时钟树和锁相环两部分。

全局时钟树负责把时钟分配到器件内部的各个单元,控制器件内部的所有资源;锁相环完成分频、倍频、移相等有关时钟的基本操作。

时钟资源一览:四、内部存储器内部存储器的最多用途是暂存数据,CYCLONE II系列器件内部存储器是以M4K在存储器块的形式存在的,每一个M4K存储器块的大小为4608bit(4096 bit + 512 bit奇偶校验位)。

M4K存储器块以列的形式存在于CYCLONE II系列器件中,不同型号器件包含的M4K 存储器块一览:CYCLONE II 系列器件中的M4K 可以被配置为以下模式:单口模式、简单双口模式、完全双口模式、移位寄存器模式、只读存储器(ROM )模式和先入先出(fifo )模式。

五、FPGA 芯片的配置由于CYCLONE II 系列的FPGA 是基于SRAM 工艺制造的,SRAM 属于易失性的存储媒质,因此FPGA 在每次上电时必须重新配置。

CYCLONE II 系列的FPGA 支持3种配置方式:主动串行(AS )、被动串行(PS )和JATG 模式。

CYCLONE II 器件的配置分为3个阶段:复位阶段、配置阶段和初始化阶段。

六、FPGA 内部资源的使用锁相环(PLL )配置,锁相环一般用于同步输入时钟和输入数据,以及完成时钟综合,包括分频、倍频、移相等操作。

PLL 配置需求:CYCLONE II 系列器件中的M4K 配置为以下模式:单口RAM 模式、移位寄存器模式、只读存储器(ROM )模式和先入先出(fifo )模式。

Cyclone II 如何实现的DDR SDRAM 接口在不增加电路板复杂度的情况下要想增强系统性能,改善数据位宽是一个有效的手段。

通常来说,可以把系统频率扩大一倍或者把数据I/O 管脚增加一倍来实现双倍的数据位宽。

这两种方法都是我们不希望用到的,因为它们会增加整个设计系统的复杂度。

在总的数据I/O 管脚不变的情况下,使用双数据率(DDR)I/O 管脚来传输和接收数据也能够实现双倍数据位宽的要求。

DDR 器件使用时钟的两个沿来传输数据,在时钟频率和数据I/O 管脚不变的前提下,比单沿数据传输(SDR)器件快了一倍。

DDR 数据传输广泛应用于有快速数据传输需求的场合,如网络、通信、存储和图像处理等领域。

Cyclone II 器件支持如SDR SDRAM,DDR SDRAM,DDR2 SDRAM 以及QDRII RAM 等外部存储器接口。

下面将着重讨论Cyclone II 器件如何实现DDR SDRAM 接口控制的。

Cyclone II 器件有专用的与DDR SDRAM 接口的data(DQ),data strobe(DQS),clock 管脚。

一般是8 个DQ 信号对应与1 个DQS 信号,DQS 信号和DQ 信号从DDR SDRAM 输出时是沿对齐的。

进入FPGA 后要想实现中心对齐,即DQS 的变化沿与DQ 的中心对齐,那么必须在FPGA 内部对DQS 做延时处理,如Figure 9-1 所示。

DDR 输入接口实现如Figure 9-11 所示。

这也是一个涉及到异步时钟域数据通信的问题,且看它是如何进行同步的。

resynch_clk 是FPGA 内部使用的时钟,DQS 相对与和DQ 同步的时钟。

这两个时钟其实是同频不同相,相位偏移肯定是要满足FPGA 的采样时钟和数据信号中心对齐,这涉及到DDR SDRAM 的输出时钟信号的相位调整。

输入信号DQS 经过反向延时后与DQ 信号中心对齐,然后分别使用方向延时后的DQS信号的下降沿和上升沿锁存DQ 信号前后输入的数据Q0 和Q1,同时在上升沿时会对前一级采样的Q0 信号再进行一次锁存,从而使Q0 和Q1 信号在被。

Cyclone II系列FPGA特殊引脚1/1.I/O,ASDO在AS模式下是专用输出脚,在PS和JTAG模式下可以当I/O脚来用。

在AS模式下,这个脚是CII向串行配置芯片发送控制信号的脚。

也是用来从配置芯片中读配置数据的脚。

在AS模式下,ASDO有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。

ASDO脚直接接到配置芯片的ASDI脚(第5脚)。

2/2.I/O,nCSO在AS模式下是专用输出脚,在PS和JTAG模式下可以当I/O脚来用.在AS模式下,这个脚是CII用来给外面的串行配置芯片发送的使能脚。

在AS模式下,ASDO有一个内部的上拉电阻,一直有效。

这个脚是低电平有效的。

直接接到配置芯片的/CS脚(第1脚)。

3/3.I/O,CRC_ERROR当错误检测CRC电路被选用时,这个脚就被作为CRC_ERROR脚,如果不用默认就用来做I/O。

但要注意,这个脚是不支持漏极开路和反向的。

当它作为CRC_ERROR时,高电平输出则表示出现了CRC校验错误(在配置SRAM各个比特时出现了错误)。

CRC电路的支持可以在setting中加上。

这个脚一般与nCONFIG脚配合起来用。

即如果配置过程出错,重新配置.4/4.I/O,CLKUSR当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。

在所有配置数据都已经被接收后,CONF_DONE脚会变成高电平,CII器件还需要299个时钟周期来初始化寄存器,I/O等等状态,FPGA有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR接进来的时钟(最大不能超过100MHz)。

有这个功能,可以延缓FPGA开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

7/13.I/O,VREF用来给某些差分标准提供一个参考电平。

没有用到的话,可以当成I/O来用。

Altera Cyclone II FPGA的几种代码配置1、根据FPGA在配置电路中的角色,配置数据可以使用3种方式载入到目标器件中:(1) FPGA主动方式:由FPGA来主动输出控制和同步信号给FPGA的串行配置芯片(EPCS系列),配置芯片收到命令后,把配置数据发给FPGA,完成配置过程;在AS模式下,FPGA必须与AS串行配置芯片配合使用,它与FPGA的接口为四跟信号线,分别为:串行时钟输入(DCLK),AS控制信号输入 (ASDI),片选信号(nCS),串行数据输出(DATA)。

(2) FPGA被动方式:被动模式下,由系统的其他设备发起并控制配置过程,这些设备可以是配置芯片(EPC系列),或者单板的微处理器、CPLD等。

FPGA 在配置过程中完全处于被动地位,只是输出一些状态信号来配合配置过程;在PS模式下,需要配置时钟(DCLK),配置数据(DATA0),配置命令 (nCONFIG),状态信号(nSTATUS),配置完成指示(CONF_DONE)这四个信号来完成配置过程。

(3) JTAG模式:使用JTAG进行配置可以使用Altera的下载电缆,或者通过智能主机模拟JTAG的时序来进行配置;JTAG接口由四个必须的信号TDI、TDO、TMS 和TCK,以及一个可选的TRST构成。

2、若使用ByteBlasterII下载电缆,支持的配置方式有以下3种:AS方式:对AS配置芯片(ECPS系列)进行编程;PS方式:可以对FPGA进行配置;JTAG方式:可以对FPGA、CPLD以及Altera配置芯片(EPC系列)编程。

3、AS及PS模式下的注意事项PS模式:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序.只有在调试完成以后,才把程序烧在配置芯片中,然后将芯片焊上.或者配置芯片就是可以方便取下焊上的那种.这样出了问题还可以方便地调试.AS模式下: 用过一块板子用的AS下载,配置芯片一直是焊在板子上的,原来AS方式在用线缆对配置芯片进行下载的时候,会自动禁止对FPGA的配置,而PS 方式需要电路上隔离。

1.下载口。

JTAG下载接口,对应下载的文件是SOF文件,速度快,JTAG 将程序直接下载到FPGA中,但是掉电程序丢失,平时学习推荐使用JTAG方式,最后固化程序的时候再通过AS方式将程序下载到配置芯片中即可;AS下载接口,对应下载的是POF文件,速度相对较慢,需要重新上电并且拔掉下载线,才能工作,操作相对麻烦,不推荐学习的时候使用。

2.FPGA引脚作用:(1)VCCINT:这些都是内部逻辑阵列电源电压引脚。

VCCINT还可以给输入缓冲区供电,用于LVPECL,LVDS(常规I / O和CLK引脚),差分HSTL,差分SSTL I/ O标准。

Connect all VCCINT pins to 1.2 V. Decoupling depends on the design decoupling requirementsof the specific board.所有VCCINT引脚连接至1.2 V,去耦依赖于设计脱钩的要求的具体电路板。

(2)VCCIO[1…8]: 这些I / O电源电压引脚银行1至8。

每个组可以支持不同的电压水平。

VCCIO供电到输出缓冲区,所有的I / O标准。

VCCIO供电输入缓冲区用于LVTTL,LVCMOS,1.5-V,1.8 V,2.5 V,3.3 V PCI,和3.3-V PCI-X,差分SSTL。

差分HSTL。

和LVDS lrecular我/ OL I / O标准。

验证VCCIO电压等级连接是与QuartusII软件的引脚连接一致。

去耦取决于设计去耦的具体要求的具体电路板。

(3)VREFB[1..8]N[0..3]: 为每个I / O组的输入参考电压。

这些引脚被用来作电压参考引脚。

如果没有被用,就作为普通的I/O引脚。

(4)VCCA PLL[1..4]: 模拟电源锁相环[1 ..4].将这些引脚连接到1.2 V,即使不使用PLL。

更好的,使用一个孤立的线性电源钳工性能。

Cyclone II代芯片分析班级:1211自动化学号:2012118064姓名:英雄有泪Cyclone系列芯片是Altera公司推出的新一代低成本、中等规模的FPGA,其价格仅为Altera现有主流器件的30%~50%。

它通过去掉DSP块,MegaRAM,降低LVDS接口速率等指标后,可适应大多数设计的要求,同时分担用户所面临的成本压力。

该芯片采用0.13μm,全铜SRAM工艺,1.5v内核,同时还拥有2910个逻辑单元到20060个逻辑单元以及59904位RAM到294912位RAM,这使得它可用于实现多种复杂的功能。

此外,该芯片还提供了用于时钟管理的锁相环和用于连接工业标准外部存储器的专用I/O接口;而且,多种IP 核及Altera发布的Nios嵌入式微处理器软核均能在其上实现。

最后,我们具体实现了一个基于Cyclone FPGA的电子时钟的设计。

可编程器件方面,我们选用的是240管脚PQFP封装的EP1C12器件;配置时则是采用主动串行配置方案下的EPCS1器件。

在此,论文主要讲解了板卡的组成、内部设计及仿真,其中内部实现包括:原理图、PCB图的绘制和VHDL程序的编写。

Cyclone系列芯片的结构分析Cyclone现场可编程逻辑阵列芯片系列是一款低价格中等密度的FPGA,采用0.13μm的全铜SRAM工艺,容量从2910个逻辑单元到20060个逻辑单元(LEs:Logic Elements),1.5v内核。

Cyclone的性价比较高,它提供用于时钟控制的锁相环(PLLs:Phase-Locked Loops),同时它还有一个专用的双倍数据传输率(DDR)接口用于满足DDR SDARM和FCRAM(fast cycle RAM)存储器的需要,Cylone器件支持多种I/O标准接口,包括数据传输率可达311Mbps的LVDS(Low Voltage Differential Signaling,低电压差分信号)和66 MHz/32 bits的PCI接口,同时还支持ASSP(Application-specific Standard Products)和ASIC (Application-specific Integrated Circuit)器件。

EP2C5T144C8N/EP2C5Q208C8N1/1. I/O, ASDO:在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用。

在AS 模式下,这个脚是CII 向串行配置芯片发送控制信号的脚。

也是用来从配置芯片中读配置数据的脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效,配置完成后,该脚就变成三态输入脚。

ASDO 脚直接接到配置芯片的ASDI 脚(第5 脚)。

2/2. I/O,nCSO:在AS 模式下是专用输出脚,在PS 和JTAG 模式下可以当I/O 脚来用.在AS 模式下,这个脚是CII 用来给外面的串行配置芯片发送的使能脚。

在AS 模式下,ASDO 有一个内部的上拉电阻,一直有效。

这个脚是低电平有效的。

直接接到配置芯片的/CS 脚(第1 脚)。

3/3. I/O,CRC_ERROR:当错误检测CRC 电路被选用时,这个脚就被作为CRC_ERROR 脚,如果不用默认就用来做I/O。

但要注意,这个脚是不支持漏极开路和反向的。

当它作为CRC_ERROR 时,高电平输出则表示出现了CRC 校验错误(在配置SRAM 各个比特时出现了错误)。

CRC 电路的支持可以在setting 中加上。

这个脚一般与nCONFIG 脚配合起来用。

即如果配置过程出错,重新配置。

4/4. I/O,CLKUSR:当在软件中打开Enable User-supplled start-up clock(CLKUSR)选项后,这个脚就只可以作为用户提供的初始化时钟输入脚。

在所有配置数据都已经被接收后,CONF_DONE 脚会变成高电平,CII 器件还需要299 个时钟周期来初始化寄存器,I/O 等等状态,FPGA有两种方式,一种是用内部的晶振(10MHz),另一种就是从CLKUSR 接进来的时钟(最大不能超过100MHz)。

有这个功能,可以延缓FPGA 开始工作的时间,可以在需要和其它器件进行同步的特殊应用中用到。

7/13. I/O,VREF用来给某些差分标准提供一个参考电平。

没有用到的话,可以当成I/O 来用。

14/20. DATA0专用输入脚。

在AS 模式下,配置的过程是:CII 将nCSO 置低电平,配置芯片被使能。

CII然后通过DCLK 和ASDO 配合操作,发送操作的命令,以及读的地址给配置芯片。

配置芯片然后通过DATA 脚给CII 发送数据。

DATA 脚就接到CII 的DATA0 脚上。

CII 接收完所有的配置数据后,就会释放CONF_DONE 脚(即不强制使CONF_DONE 脚为低电平),CONF_DONE 脚是漏极开路(Open-Drain)的。

这时候,因为CONF_DONE 在外部会接一个10K 的电阻,所以它会变成高电平。

同时,CII 就停止DCLK 信号。

在CONF_DONE 变成高电平以后(这时它又相当于变成一个输入脚),初始化的过程就开始了。

所以,CONF_DONE 这个脚外面一定要接一个10K 的电阻,以保证初始化过程可以正确开始。

DATA0,DCLK,NCSO,ADSO 脚上都有微弱的上拉电阻,且一直有效。

在配置完成后,这些脚都会变成输入三态,并被内部微弱的上拉电阻将电平置为高电平。

在AS 模式下,DATA0就接到配置芯片的DATA(第2 脚)。

15/21. DCLK.PS 模式下是输入,AS 模式下是输出。

在PS 模式下,DCLK 是一个时钟输入脚,是外部器件将配置数据传送给FPGA 的时钟。

数据是在DCLK 的上升沿把数据,在AS 模式下,DCLK脚是一个时钟输出脚,就是提供一个配置时钟。

直接接到配置芯片的DCLK 脚上去(第6脚)。

无论是哪种配置模式,配置完成后,这个脚都会变成三态。

如果外接的是配置器件,配置器件会置DCLK 脚为低电平。

如果使用的是主控芯片,可以将DCLK 置高也可以将DCLK 置低。

配置完成后,触发这个脚并不会影响已配置完的FPGA。

这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

16/22. nCE专用输入脚。

这个脚是一个低电平有效的片选使能信号。

nCE 脚是配置使能脚。

在配置,初始化以及用户模式下,nCE 脚必须置低。

在多个器件的配置过程中,第一个器件的nCE 脚要置低,它的nCEO 要连接到下一个器件的nCE 脚上,形成了一个链。

nCE 脚在用JTAG编程模式下也需要将nCE 脚置低。

这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

20/26. nCONFIG专用的输入管脚。

这个管脚是一个配置控制输入脚。

如果这个脚在用户模式下被置低,FPGA就会丢失掉它的配置数据,并进入一个复位状态,并将所有的I/O 脚置成三态的。

nCONFIG从低电平跳变到高电平的过程会初始化重配置的过程。

如果配置方案采用增强型的配置器件或EPC2,用户可以将nCONFIG 脚直接接到VCC 或到配置芯片的nINIT_CONF 脚上去。

这个脚带了输入Buffer,支持施密特触发器的磁滞功能。

实际上,在用户模式下,nCONFIG信号就是用来初始化重配置的。

当nCONFIG 脚被置低后,初始化进程就开始了。

当nCONFIG脚被置低后,CII 就被复位了,并进入了复位状态,nSTATUS 和CONF_DONE 脚被置低,所有的I/O 脚进入三态。

nCONFIG 信号必须至少保持2us。

当nCONFIGA 又回到高电平状态后,nSTATUS 又被释放。

重配置就开始了。

在实际应用过程中可以将nCONFIG 脚接一个10K 的上拉电阻到3.3V.40/56. DEV_OEI/O 脚或全局I/O 使能脚。

在Quartus II 软件中可以使能DEV_OE 选项(Enable Device-wideoutput Enable),如果使能了这一个功能,这个脚可以当全局I/O 使能脚,这个脚的功能是,如果它被置低,所有的I/O 都进入三态。

75/107. INIT_DONEI/O 脚或漏极开路的输出脚。

当这个脚被使能后,该脚上从低到高的跳变指示FPGA 已经进入了用户模式。

如果INIT_DONE 输出脚被使能,在配置完成以后,这个脚就不能被用做用户I/O 了。

在QuartusII 里面可以通过使能EnableINIT_DONE 输出选项使能这个脚。

76/108. nCEOI/O 脚或输出脚。

当配置完成后,这个脚会输出低电平。

在多个器件的配置过程中,这个脚会连接到下一个器件的nCE 脚,这个时候,它还需要在外面接一个10K 的上拉电阻到Vccio。

多个器件的配置过程中,最后一个器件的nCEO 可以浮空。

如果想把这个脚当成可用的I/O,需要在软件里面做一下设置。

另外,就算是做I/O,也要等配置完成以后。

82/121. nSTATUS这是一个专用的配置状态脚。

双向脚,当它是输出脚时,是漏极开路的。

在上电之后,FPGA立刻将nSTATUS 脚置成低电平,并在上电复位(POR)完成之后,释放它,将它置为高电平。

作为状态输出脚时,在配置过程中如果有任何一个错误发生了,nSTATUS 脚会被置低。

作为状态输入脚时,在配置或初始化过程中,外部控制芯片可以将这个脚拉低,这时候FPGA就会进入错误状态。

这个脚不能用作普通I/O 脚。

nSTATUS 脚必须上拉一个10K 欧的电阻。

83/123. CONF_DONE这是一个专用的配置状态脚。

双向脚,当它是输出脚时,是漏极开路的。

当作为状态输出脚时,在配置之前和过程中,它都被置为低电平。

一旦配置数据接收完成,并且没有任何错误,初始化周期一开始,CONF_DONE 就会被释放。

当作为状态输入脚时,在所有数据都被接收后,要将它置为高电平。

之后器件就开始初始化再进入用户模式。

它不可以用作普通I/O来用。

这个脚外成也必须接一个10K 欧的电阻。

84/125,85/126. MSEL[1:0]这些脚要接到零或电源,表示高电平或低电平。

00 表示用AS 模式,10 表示PS 模式,01是FAST AS 模式.如果用JTAG 模式,就把它们接00, JTAG 模式跟MSEL 无关,即用JTAG模式,MSEL 会被忽略,但是因为它们不能浮空,所以都建议将它接到地。

142/206 DEV_CLRnI/O 或全局的清零输入端。

在QuartusII 里面,如果选上Enable Device-Wide Rese(t DEV_CLRn)这个功能。

这个脚就是全局清零端。

当这个脚被置低,所有的寄存器都会被清零。

这个脚不会影响到JTAG 的边界扫描或编程的操作。

EPM240T100C5N 只有以下特殊管脚,功能和Cyclone II 的是一样的:IO/GCLK0 12全局时钟脚IO/GCLK1 14全局时钟脚IO/GCLK2 62全局时钟脚IO/GCLK3 64全局时钟脚IO/DEV_OE 43全局OE 脚IO/DEV_CLRn 44全局清零脚。