半导体制造技术—第四讲:淀积工艺

- 格式:ppt

- 大小:3.18 MB

- 文档页数:67

高密度等离子体化学气相淀积工艺简介随着半导体技术的飞速发展,半导体器件特征尺寸的显著减小,相应地也对芯 片制造工艺提出了更高的要求,其中一个具有挑战性的难题就是绝缘介质在各 个薄膜层之间均匀无孔的填充以提供充分有效的隔离保护,包括浅槽隔离(STI ),金属前绝缘层(PMD ,金属层间绝缘层(IMD )等等。

本文所介绍的 高密度等离子体化学气相淀积(HDP CVD 工艺自20世纪90年代中期开始被先 进的芯片工厂采用以来,以其卓越的填孔能力,稳定的淀积质量,可靠的电学 特性等诸多优点而迅速成为 0.25微米以下先进工艺的主流。

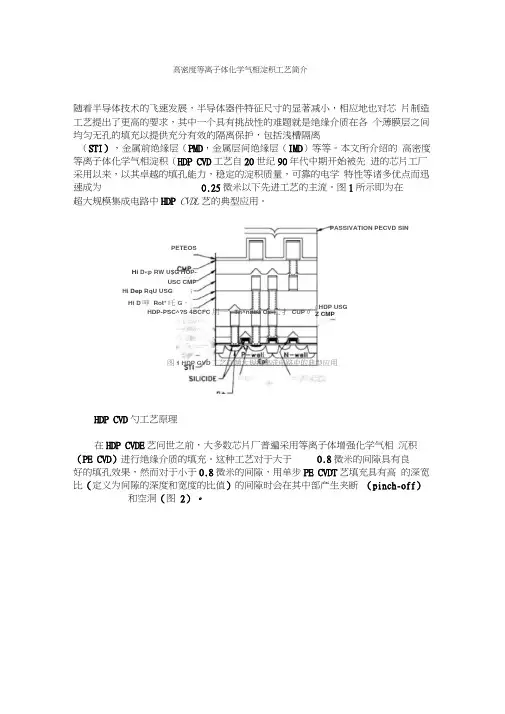

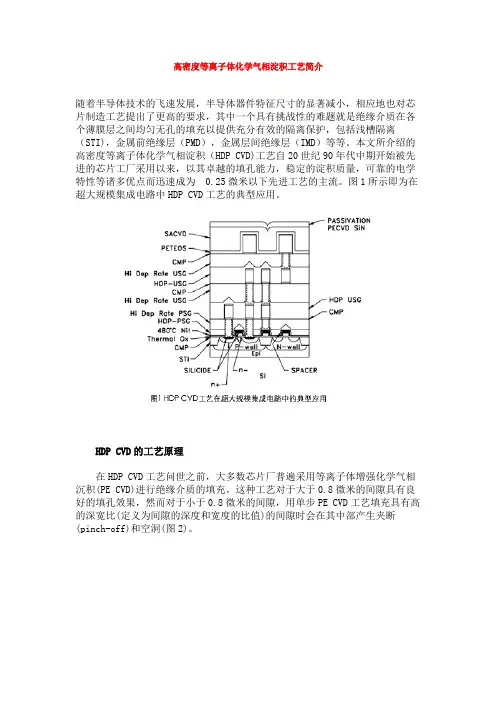

图1所示即为在 超大规模集成电路中HDP CVDL 艺的典型应用。

PASSIVATION PECVD SINPETEOSHi D«p RW U$G HOP-USC CMPHi Dep RqU USGHi D 呻 Rot* 吒G 、 HDP-PSC^?S 4BCFC 刖一^ Th^nnoJ Ox-匚扌 CUP // 图1 HDP GVD 工艺在趙大規摟集成电路中的典型应用HDP CVD 勺工艺原理在HDP CVDE 艺问世之前,大多数芯片厂普遍采用等离子体增强化学气相 沉积(PE CVD )进行绝缘介质的填充。

这种工艺对于大于 0.8微米的间隙具有良 好的填孔效果,然而对于小于0.8微米的间隙,用单步PE CVDT 艺填充具有高 的深宽比(定义为间隙的深度和宽度的比值)的间隙时会在其中部产生夹断 (pinch-off ) 和空洞(图 2)。

/ HDP USG Z CMPf?]2PECVD工艺填孑l中产生的夹斯和空洞为了解决这一难题,淀积-刻蚀-淀积工艺被用以填充0.5微米至0.8微米的间隙,也就是说,在初始淀积完成部分填孔尚未发生夹断时紧跟着进行刻蚀工艺以重新打开间隙入口,之后再次淀积以完成对整个间隙的填充(图 3 )。

显而易见,为了填充越小的间隙,越来越多的工艺循环需要被执行,在不断降低产量的同时也显著增加了芯片成本,而且由于本身工艺的局限性,即便采用循环工艺,PE CVD寸于小于0.5微米的间隙还是无能为力.其他一些传统CVD 工艺,如常压CVD(APCVD)亚常压CVD(SACVD虽然可以提供对小至0.25微米的间隙的无孔填充,但这些缺乏等离子体辅助淀积产生的膜会依赖下层表面而显示出不同的淀积特性,另外还有低密度和吸潮性等缺点,需要PE CVD增加上保护层和下保护层,或者进行后淀积处理(如退火回流等)。

高密度等离子体化学气相淀积工艺简介随着半导体技术的飞速发展,半导体器件特征尺寸的显著减小,相应地也对芯片制造工艺提出了更高的要求,其中一个具有挑战性的难题就是绝缘介质在各个薄膜层之间均匀无孔的填充以提供充分有效的隔离保护,包括浅槽隔离(STI),金属前绝缘层(PMD),金属层间绝缘层(IMD)等等。

本文所介绍的高密度等离子体化学气相淀积(HDP CVD)工艺自20世纪90年代中期开始被先进的芯片工厂采用以来,以其卓越的填孔能力,稳定的淀积质量,可靠的电学特性等诸多优点而迅速成为0.25微米以下先进工艺的主流。

图1所示即为在超大规模集成电路中HDP CVD工艺的典型应用。

HDP CVD的工艺原理在HDP CVD工艺问世之前,大多数芯片厂普遍采用等离子体增强化学气相沉积(PE CVD)进行绝缘介质的填充。

这种工艺对于大于0.8微米的间隙具有良好的填孔效果,然而对于小于0.8微米的间隙,用单步PE CVD工艺填充具有高的深宽比(定义为间隙的深度和宽度的比值)的间隙时会在其中部产生夹断(pinch-off)和空洞(图2)。

为了解决这一难题,淀积-刻蚀-淀积工艺被用以填充0.5微米至0.8微米的间隙,也就是说,在初始淀积完成部分填孔尚未发生夹断时紧跟着进行刻蚀工艺以重新打开间隙入口,之后再次淀积以完成对整个间隙的填充(图3)。

显而易见,为了填充越小的间隙,越来越多的工艺循环需要被执行,在不断降低产量的同时也显著增加了芯片成本,而且由于本身工艺的局限性,即便采用循环工艺,PE CVD对于小于0.5微米的间隙还是无能为力.其他一些传统CVD 工艺,如常压CVD(APCVD)和亚常压CVD(SACVD)虽然可以提供对小至0.25微米的间隙的无孔填充,但这些缺乏等离子体辅助淀积产生的膜会依赖下层表面而显示出不同的淀积特性,另外还有低密度和吸潮性等缺点,需要PE CVD增加上保护层和下保护层,或者进行后淀积处理(如退火回流等)。