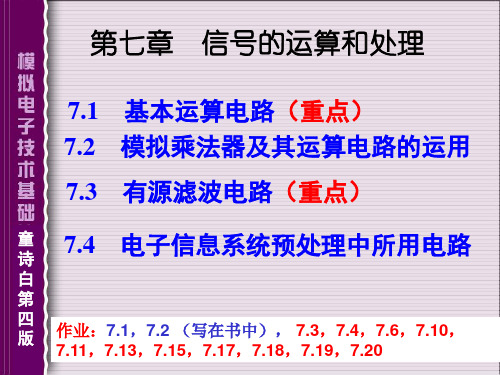

7.2_基本运算电路

- 格式:ppt

- 大小:885.00 KB

- 文档页数:29

基本运算电路基本运算电路是电子电路中常见的一种电路结构,用于实现基本的数学运算和逻辑运算。

它由若干个元件组成,通过这些元件之间的连接和相互作用,完成特定的运算功能。

基本运算电路包括加法器、减法器、乘法器、除法器、与门、或门、非门等,它们是数字电子系统的基础,广泛应用于计算机、通信设备、控制系统等各个领域。

加法器是基本运算电路中最基本的一种,用于实现数字的加法运算。

它由若干个输入端和一个输出端组成,通过输入端输入待相加的数字信号,经过电路内部的运算处理,最终在输出端得到加法运算的结果。

加法器的设计原理是将两个数字进行逐位相加,并考虑进位的情况,以确保计算结果的正确性。

减法器和加法器相似,也用于实现数字的减法运算。

它通过将减法运算转换为加法运算的方式来实现,即将被减数取反并加1,然后与减数进行加法运算,最终得到减法运算的结果。

减法器在数字电子系统中有着广泛的应用,是实现数字信号处理的重要组成部分。

乘法器用于实现数字的乘法运算,是一种复杂的基本运算电路。

它通过将乘法运算转换为多次的加法运算来实现,即将被乘数分解为若干个部分,并分别与乘数相乘,然后将这些部分的乘积进行累加,最终得到乘法运算的结果。

乘法器在数字信号处理和计算机中都有着重要的应用,是实现高效计算的关键组成部分。

除法器用于实现数字的除法运算,是基本运算电路中最复杂的一种。

它通过多次的减法运算和比较来实现,即将被除数循环减去除数,直到被除数小于除数为止,然后统计减法的次数,最终得到除法运算的商和余数。

除法器在数字信号处理和通信系统中有着重要的应用,是实现高精度计算的关键组成部分。

与门、或门、非门是基本的逻辑运算电路,用于实现逻辑运算和判断。

与门用于实现逻辑与运算,即只有当所有输入信号均为高电平时,输出信号才为高电平;或门用于实现逻辑或运算,即只要有一个输入信号为高电平,输出信号就为高电平;非门用于实现逻辑非运算,即对输入信号取反,输出信号与输入信号相反。

基本运算电路知识点总结一、基本运算电路的概念基本运算电路是指用来进行基本算术运算的电子电路。

它包括加法器、减法器、乘法器及除法器等。

它们是数字逻辑电路中的重要组成部分,用于实现数字信号的处理和运算。

在数字系统中,基本运算电路是实现数字信号加、减、乘、除等运算的基础,在数字系统中起着重要的作用。

下面将对基本运算电路的知识点进行详细总结。

二、加法器1. 概念加法器是一种用来实现数字信号加法运算的电路。

它将两个输入信号进行加法计算,得到一个输出信号。

加法器是数字逻辑电路中的基本组成部分,用于实现数字信号的加法运算。

2. 类型加法器包括半加器、全加器、并行加法器等不同类型。

其中,半加器用来对两个二进制数的最低位进行相加,得到一个部分和和一个进位;全加器用来对两个二进制数的一个位和一个进位进行相加,得到一个部分和和一个进位;而并行加法器则是将多个全加器连接起来,实现对多位二进制数的加法计算。

3. 原理以全加器为例,它由三个输入和两个输出组成。

其中,三个输入分别是两个待相加的二进制数对应位上的值和上一位的进位,而两个输出分别是当前位的部分和和进位。

全加器的原理是通过对三个输入进行逻辑门运算,得到当前位的部分和和进位。

4. 应用加法器广泛应用于数字系统中,包括计算机、数字信号处理系统、通信系统等。

在计算机中,加法器用来进行寄存器之间的运算,对数据进行加法操作;在通信系统中,加法器用来进行数字信号的处理,对数字信号进行加法运算。

三、减法器1. 概念减法器是一种用来实现数字信号减法运算的电路。

它将两个输入信号进行减法计算,得到一个输出信号。

减法器是数字逻辑电路中的基本组成部分,用于实现数字信号的减法运算。

2. 类型减法器包括半减器和全减器两种不同类型。

其中,半减器用来对两个二进制数的最低位进行相减,得到一个部分差和一个借位;全减器用来对两个二进制数的一个位和一个借位进行相减,得到一个部分差和一个借位。

3. 原理以全减器为例,它由三个输入和两个输出组成。

基本运算电路的原理和应用1. 概述基本运算电路是电子电路中最基础、常见的电路之一。

它们能够实现各种基本的数学运算和逻辑操作,广泛应用于各种电子设备和系统中。

本文将介绍三种常见的基本运算电路:加法器、减法器和乘法器,并讨论它们的原理和应用。

2. 加法器加法器是最基本的运算电路之一,用于将两个二进制数字相加。

常见的加法器有半加器、全加器和Ripple Carry Adder。

2.1 半加器半加器是最简单的加法器,用于实现两个二进制位的加法运算。

它有两个输入:两个待相加的二进制位a和b,以及两个输出:和位s和进位位c_out。

半加器的真值表如下:a b s c_out0 0 0 00 1 1 01 0 1 01 1 0 12.2 全加器全加器是半加器的扩展,用于实现三个二进制位的加法运算。

除了输入位a和b之外,全加器还有一个输入位c_in,表示进位信号。

全加器的真值表如下:a b c_in s c_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 12.3 Ripple Carry AdderRipple Carry Adder是多个全加器的级联组合,用于实现多位数的加法运算。

它通过将进位位c_out连接到下一个全加器的c_in端,从而实现进位的传递。

Ripple Carry Adder的优点是实现简单,但是由于进位的串行传递,速度较慢。

因此,在高速计算要求的情况下,通常采用更快速的加法器,如Carry Lookahead Adder或Kogge-Stone Adder。

3. 减法器减法器是实现两个二进制数字相减的运算电路。

它可以通过将减法转化为加法来实现。

常见的减法器有半减器和全减器。

3.1 半减器半减器用于实现两个二进制位的减法运算。

它有两个输入:被减数位a和减数位b,以及两个输出:差位d和借位位b_out。