Modelsim仿真设计举例

- 格式:doc

- 大小:44.00 KB

- 文档页数:7

ModelSim SE 10.0c 仿真实例(忠诚1963)前一阶段,学习了真黑金动力社区《ModelSim SE 10.0c 入门教程》(作者小小龙),利用Modelsim10进行FPGA下128分频器的仿真,一直做不通,今天放假,重新试了几次,做通了,将其记录下来,发给新学友供大家参考。

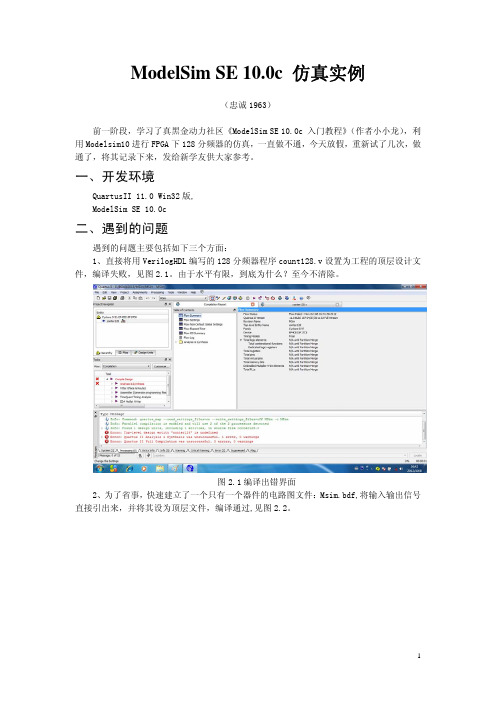

一、开发环境QuartusII 11.0 Win32版,ModelSim SE 10.0c二、遇到的问题遇到的问题主要包括如下三个方面:1、直接将用VerilogHDL编写的128分频器程序count128.v设置为工程的顶层设计文件,编译失败,见图2.1。

由于水平有限,到底为什么?至今不清除。

图2.1编译出错界面2、为了省事,快速建立了一个只有一个器件的电路图文件:Msim.bdf,将输入输出信号直接引出来,并将其设为顶层文件,编译通过,见图2.2。

图2.2 Msim.bdf为顶层文件的工程编译通过后进行仿真,仿真失败,显示结果如图2.3。

原因是已经设定仿真语言为Verilog HDL。

如图2.3 仿真失败界面没办法,只好用手工重新写了一段 Verilog HDL语言的顶层设计文件MSim.V。

编译通过,并且仿真正常。

3、用Start Test Bench Template Writer生成的仿真测试模板是用于仿真测试主模块MSim.V的,如何仿真count128.v?后面有详细说明,在此不说了。

三、正确的过程1、建立QuartusII 11.0工程(大家应该会吧)建立一个MSim的工程,将其放在了E:\BGold2013下,建立完成后样子如图3.1:图3.1QuartusII 11.0工程其中包括两个文件:MSim.V 顶层文件 和 count128.v 128分频器文件。

原来在工程中只录入了count128.v一个文件,编译总是不通,增加了一个MSim.v顶层文件,好了。

1.1 MSim 顶层文件内容MSim.v 为顶层设计文件,包括对count128的调用,具体如下://////////////////////////////////////////////////////////////////////////// Company : BJCZ// Engineer : GuoSZ// Create Date : 2013.10.01// Design Name : MSim.v// Module Name : MSim// Project Name : MSim// Target Device: Cyclone IV EP4CE15F17C8// Tool versions: Quartus II 11.0// Description : ModelSim SE 10.c 测试顶层模块//// --------------------------------------------------------------------//// Revision History :// --------------------------------------------------------------------// Ver :| Author :| Mod. Date :| Changes Made:// V1.0 :| Guoshuzhong :| 2013/10/01:| Initial Revision// Additional Comments ://///////////////////////////////////////////////////////////////////////////////module MSim(clk,rst_n);input clk,rst_n;wire divclk;wire [7:0]data;count128 i1( //例化.clk(clk),.rst_n(rst_n),.divclk(divclk),.data(data));endmodule1.2 128分频器在count128.v 中定义了一个128分频器,程序如下:////////////////////////////////////////////////////////////////////////////////// Company : BJCZ// Engineer : GuoSZ// Create Date : 2013.10.01// Design Name : count128.v// Module Name : count128// Project Name : MSim// Target Device: Cyclone IV EP4CE15F17C8// Tool versions: Quartus II 11.0// Description : 128分频器模块//// --------------------------------------------------------------------//// Revision History :// --------------------------------------------------------------------// Ver :| Author :| Mod. Date :| Changes Made: // V1.0 :| Guoshuzhong :| 2013/10/01:| Initial Revision // Additional Comments ://///////////////////////////////////////////////////////////////////////////////module count128(clk,rst_n,divclk,data);input clk,rst_n;output divclk;output [7:0]data;reg [7:0] data;assign divclk=data[7];always@(posedge clk or negedge rst_n)if(!rst_n )begindata<=8'h00;endelsebegindata<=data+1'b1;endendmodule1.3 编译Processing -> start compilation ( 或CTRL_L),编译成功后显示如下图3.2所示:图3.2 编译成功图示2、建立 Testbench2.1 生成 Testbench模板。

1. 4位加法器的ModelSim 仿真设计新建一个名为adder4,v的源文件,源代码如下:module adder4(COUT,SUM,A,B,CIN);input[3:0] A,B;input CIN;output[3:0] SUM;output COUT;assign {COUT,SUM}=A+B+CIN;endmodule接下来需要编写4位加法器的测试文件test_adder4.v 源代码如下://‘timescale 1ns/1nsmodule test_adder4;wire[3:0] SUM;wire COUT;reg[3:0] A,B;reg CIN;initialbeginA=4;B=2;CIN=1;#100A=12;B=8;CIN=0;#100A=10;B=8;CIN=0;endadder4 m( .COUT(COUT), .SUM(SUM), .A(A), .B(B), .CIN(CIN)); endmodule2. 十进制计数器的ModelSim 仿真设计counter_10源代码如下:module counter_10(clk,clr,c,out);input clk,clr;output c;output [3:0] out;reg c;reg [3:0] out;always@(posedge clk or negedge clr)beginbegin out[3:0]<=0; c<=0; endelsebegin if(out[3:0]= =9)begin c<=1; out[3:0]<=0; endelsebegin out[3:0]<= out[3:0]+1; c<=0; endendendendmodulecounter_10_tp.v是testbench文件,用来测试验证十进制计数器,代码如下:‘timescale 1ns/1nsmodule counter_10_tp;reg clk,clr;wire cout;wire [3:0] cnterout;counter_10 counter10(. clk(clk), . clr(clr) , . c(cout), . out(cnterout));always #5 clk=~clk;initialbeginclk<=0;clr<=0;#10 clr<=1;#30 clr<=0;#40 clr<=1;#2000 $stop;endendmodule3. Quartus 8.0新建一个工程,然后编写两个文件如下:顶层文件“count4.v”源码为:module count4(clk,reset,out); //4位计数器模块input clk,reset;output[3:0] out;reg[3:0] out;always @(posedge clk)beginif (reset)out<=0;elseout<=out+1;endmoduleModelSim仿真用到的测试文件“count_tp.v”源码为:(注意,该文件不加入工程中)`timescale 1ns/1ns //定义时延单位1ns和时延精度为1ns(即精确到1ns)module count_tp; //测试模块reg clk,reset; //输入激励信号定义为reg型wire[3:0] out; //输出信号定义为wire型parameter DELY=100;count4 mycount(.clk(clk),.reset(reset),.out(out)); //调用测试对象count4always #(DELY/2) clk=~clk; //产生时钟波形initial //激励波形定义beginclk=0;reset=0;#DELY reset=1;#DELY reset=0;#(DELY*20) $finish;endinitial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out);//结果显示endmodule4.简单的测试设计实例化用户设计,然后提供相应的激励。

使用Link for ModelSim ,你可以建立一个有效的环境来进行联合仿真、器件建模、以及分析和可视化。

进行如下的实例的开发。

1 :可以在MA TLAB或Simulink 中针对HDL实体开发软件测试基准(test bench) 。

2 :可以在Simulink 中对包含在大规模系统模型的HDL 模型进行开发和仿真。

3 :可以生成测试向量进行测试、调试,以及同MA TLAB/Simulink下的规范原形进行HDL 代码的验证。

4 :提供在MA TLAB/Simulink下的对HDL行为级的建模能力。

5 :可以在MA TLAB/Simulink下对HDL的实现进行验证、分析、可视化。

Link for ModelSim中MA TLAB与ModelSim 接口和Simulink与ModelSim 接口是独立的。

这使得你可以单独使用一个接口或同时使用两个。

使用ModelSim和MATLAB的接口使用Link for ModelSim后,你可以使用MA TLAB和它提供的工具箱,比如设计和仿真信号处理,或者其他的数值计算算法。

你还可以用HDL来取代算法和系统设计中的器件模型,并直接完成HDL器件和MA TLAB中剩余算法的联合仿真。

使用ModelSim和Simulink的接口你可以通过Simulink和相关的Blockset创建一个关于信号处理方面或者通信系统方面的系统级设计。

你也可以把HDL 器件合并到设计中或者用HDL模块来取代相应的子系统,并借此来创建软件测试基准来验证你的HDL实现。

ModelSim 中联合仿真模块的参数对话框可以让你很容易的设置输入输出端口,二者连接的属性,时钟,以及TCL命令。

本图显示了在MATLAB和ModelSim的接口关系。

把在MATLAB 中获得的测试基准代码输出作为输入输入到VHDL实体中,并把经过ModelSim的输出输入到MATLAB函数中Link for ModelSim还提供一个模块来生成VCD的文件格式,可以用来:1 :观察在HDL仿真环境下的Simulink仿真波形2 :使用相同或不同的仿真环境来比较多个不同仿真运行的结果。

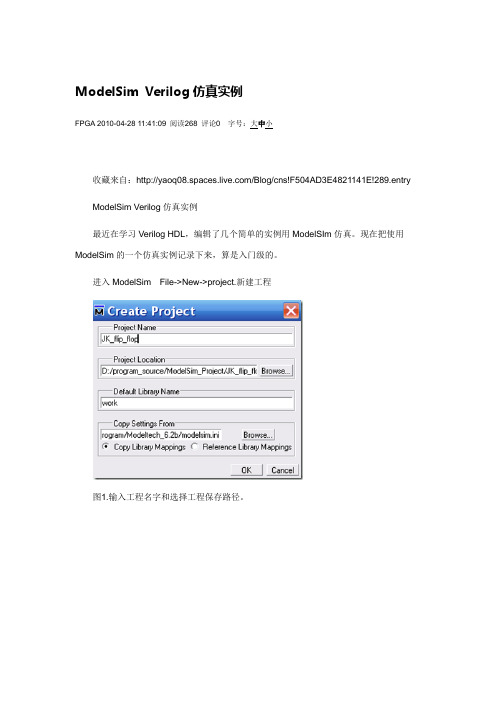

ModelSim Verilog仿真实例FPGA 2010-04-28 11:41:09 阅读268 评论0 字号:大中小收藏来自:/Blog/cns!F504AD3E4821141E!289.entry ModelSim Verilog仿真实例最近在学习Verilog HDL,编辑了几个简单的实例用ModelSIm仿真。

现在把使用ModelSim的一个仿真实例记录下来,算是入门级的。

进入ModelSim File->New->project.新建工程图1.输入工程名字和选择工程保存路径。

图2.创建新的源文件或者添加已经编辑好的文件。

添加JK_flip_flop.v文件之后,在Workspace栏中会显示出来,双击文件就可以编辑了。

编辑完之后在Workspace右键选中文件,compile->compile all,或者点击工具条上的图标。

如果在Transcript会出现# Compile of JK_flip_flop_tb.v was successful.的提示现在编辑Testbench文件,同样新建一个源文件,File->source->Verilog. 跳出编辑窗口在菜单栏中选中Source->show Language Templates,然后在Language T emplates 中撞击Create Testbench,图3.Testbench创建向导然后在work下面选中JK_flip_flop,点击next,再点击Finish。

根据自己的设计添加内容。

图4.添加内容编辑完之后进行编译。

同编译JK_flip_flop一样。

或者在菜单栏中compile->compile all,在Transcipt窗口中显示编译成功。

开始仿真菜单栏Stimulate->start Stimulation,图5.仿真选项设置然后选中work下面的JK_flip_flop_tb点击OK。

模拟电子电路multisim仿真1.1 晶体管基本放大电路1.1.1 共射极基本放大电路按下图搭建共射极基本放大电路,选择电路菜单电路图选项(Circuit/Schematic Option )中的显示/隐藏(Show/Hide)按钮,设置并显示元件的标号与数值等。

1. 静态工作点分析选择分析菜单中的直流工作点分析选项(Analysis/DC Operating Point)(当然,也可以使用仪器库中的数字多用表直接测量)分析结果表明晶体管Q1工作在放大状态。

2. 动态分析用仪器库的函数发生器为电路提供正弦输入信号Vi(幅值为5mV,频率为10kH),用示波器观察到输入,输出波形。

由波形图可观察到电路的输入,输出电压信号反相位关系。

再一种直接测量电压放大倍数的简便方法是用仪器库中的数字多用表直接测得。

3. 参数扫描分析在上图所示的共射极基本放大电路中,偏置电阻R1的阻值大小直接决定了静态电流IC 的大小,保持输入信号不变,改变R1的阻值,可以观察到输出电压波形的失真情况。

选择分析菜单中的参数扫描选项(Analysis/Parameter Sweep Analysis),在参数扫描设置对话框中将扫描元件设为R1,参数为电阻,扫描起始值为100k,终值为900k,扫描方式为线性,步长增量为400k,输出节点5,扫描用于暂态分析。

4.频率响应分析选择分析菜单中的交流频率分析项(Analysis/AC Frequency Analysis)在交流频率分析参数设置对话框中设定:扫描起始频率为1Hz,终止频率为1GHz,扫描形式为十进制,纵向刻度为线性,节点5做输出节点。

由图分析可得:当共射极基本放大电路输入信号电压VI为幅值5mV的变频电压时,电路输出中频电压幅值约为0.5V,中频电压放大倍数约为100倍,下限频率(X1)为14.22Hz,上限频率(X2)为25.12MHz,放大器的通频带约为25.12MHz。

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。

为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。

一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。

首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSim后仿真的问题,那就可能是软件版本的问题。

1, ModelSim Se 6.1b2, Synplify Pro 7.5.13, ISE 5.2i (这个是老了点)4, WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

我的邮箱是****************。

有空大家多交流。

一、为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

第8章 使用ModelSim进行设计仿真ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程序进行仿真,支持IEEE常见的各种硬件描述语言标准。

可以进行两种语言的混合仿真,但推荐大家只对一种语言仿真。

ModelSim常见的版本分为ModelSim XE和ModelSim SE两种,ModelSim版本更新很快,目前最新版本为5.8版本,该版本支持VHDL的2002标准以及Verilog的2001标准,此外,在该版本的Linux、HP和SUN工作站等平台支持VHDL、Verilog 和SystemC的混合仿真,但在Windows平台上不支持SystemC的仿真。

本章将对ModelSim5.7版本进行介绍,目的是希望看完本章,读者可以简单地使用ModelSim进行仿真,有关更深入地教程,还是参考ModelSim附带的文档。

在网址/support/上也可以找到深入的教程,在该页面上注册以后,会在电子邮件中收到发过来的密码,根据邮件地址和密码登陆后,会有一些高级教程和使用要点(Application Notes)下载。

ModelSim5.7SE版本内部划分为更细的版本编号,从ModelSim5.7aSE到ModelSim5.7gSE等等。

读者可以选择任一版本。

另外,如果ModelSim是和ISE一起使用的话,你需要编译Xilinx的一些库文件,这些库文件包括unisim、simprim、xilinxcorelib、aim、pls、cpld等,有了这些库文件,可以在ISE中生成设计的行为仿真(将设计转换为RTL描述后进行的仿真)、转换后仿真(将设计转换为Xilinx器件的基本模块来实现后进行的仿真)、映射后仿真(将设计用Xilinx的具体器件的具体模块实现后进行的仿真,仿真中包含了器件的延时,但由于没有布局布线无法提取出互连线的信息,因此仿真中不包含互连线的延时、电容、电阻等信息)、布局布线后仿真(将设计对Xilinx具体器件进行布局布线后,提取出互连线的信息,进行的仿真包含了器件的延时以及互连线的延时等信息)的各种模型,然后在ModelSim中对这些模型进行仿真,由于ISE和ModelSim已经实现了无缝的连接,在ISE中只需设置一个可视的波形文件,然后点几下鼠标就可以实现各种仿真,具体的方法在ISE的使用一章中有较为详细的介绍,可以参阅具体的章节。

实验五ModelSim仿真【实验容】1.仔细阅读ModelSim软件简要使用说明(下文)。

(“实例代码”压缩包用于ModelSim软件学习用)2.Testbench写法简要介绍。

(可以参考“Testbench模版”)3.用ModelSim完成10位全加器的功能仿真。

ModelSim软件简要使用说明ModelSim是对VHDL,Verilog,SystemC以及混合语言编写的设计文件进行仿真和调试的工具软件。

1.仿真流程在ModelSim中对一个设计进行仿真的基本步骤如下图所示:2.仿真具体步骤Create a new project选择“File > New > Project”,会弹出对话框,如图所示:其中:“Project Name”项:填写要创建的工程的名字。

“Project Location”项:确定创建的工程所要存放的位置。

请在E盘下建文件夹!“Default Library Name”项:填写工程的工作库的名字。

注:在用ModelSim进行仿真之前,必须要对设计文件进行编译,生成与设计文件逻辑功能相对应的设计单元。

由于ModelSim是用库文件来进行仿真的,所以编译后的设计单元需要存放在库文件里。

这个库文件叫作“工作库”。

926以上三项填写完毕后,点击“OK”按钮,会在指定的位置处创建工程及工作库,如图所示:在工作库文件夹,有一个名为“_info”的特殊格式文件,如图所示:这个文件指定了此文件夹为ModelSim的工作库文件夹。

在编译步骤生成的所有设计单元都会被添加到工作库文件夹。

Adding objects to the project在上一步点击OK后,ModelSim会弹出一个对话框,如图所示:其中:“Create New File”项:在工程中创建新的设计文件。

“Add Existing File”项:把已经存在的设计文件加入到工程中。

“Create Simulation”项:在工程中创建仿真配置文件。

Modelsim的仿真理解(包含仿真举例)硕1099班郝立娟3111190033常用的Verilog仿真器有Modelsim、Verilog-XL、NC-Verilog和VCS。

我们所用的ModelSim仿真软件是由MentorGraphic公司的子公司Model技术公司开发的工业界上最为通用的仿真器之一,它能提供友好的仿真环境,可以很好的用于Verilog仿真,VHDL仿真或者两者的混合仿真。

ModelSim仿真软件产品的类型很多,我们学的是ModelSim/SE,它是ModleSim主要的版本,功能最为强大,ModelSim有三种实现方法,我们所用的是用户界面的方式,能接受菜单输入和命令行输入。

Modelsim采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

它的主要特点有:⑴、RTL和门级优化,编译仿真速度快,跨平台跨版本仿真;⑵、单内核VHDL和Verilog混合仿真;⑶、源代码模版和助手,项目管理;⑷、对系统级描述语言的最全面支持,SystemVerilog,SystemC,PSL等。

Modelsim的仿真步骤:建库——建立新工程——编译源代码——启动仿真器——加入波形——执行仿真。

1、建立ModelSim 库(物理库)从主菜单里面:File->New->Library点Library得到Create a New Library 对话框。

选则a new library and a logical mapping to it,在 Library Name 中输入 work,相应的在 LibraryPhysical Name 中也会出现物理名 work。

然后点击 OK 确定。

此时在工作空间 workspace 的 Library 栏内会出现一个名为work 的库。

1. 4位加法器的ModelSim 仿真设计

新建一个名为adder4,v的源文件,源代码如下:

module adder4(COUT,SUM,A,B,CIN);

input[3:0] A,B;

input CIN;

output[3:0] SUM;

output COUT;

assign {COUT,SUM}=A+B+CIN;

endmodule

接下来需要编写4位加法器的测试文件test_adder4.v 源代码如下://‘timescale 1ns/1ns

module test_adder4;

wire[3:0] SUM;

wire COUT;

reg[3:0] A,B;

reg CIN;

initial

begin

A=4;

B=2;

CIN=1;

#100

A=12;

B=8;

CIN=0;

#100

A=10;

B=8;

CIN=0;

end

adder4 m( .COUT(COUT), .SUM(SUM), .A(A), .B(B), .CIN(CIN)); endmodule

2. 十进制计数器的ModelSim 仿真设计

counter_10源代码如下:

module counter_10(clk,clr,c,out);

input clk,clr;

output c;

output [3:0] out;

reg c;

reg [3:0] out;

always@(posedge clk or negedge clr)

begin

begin out[3:0]<=0; c<=0; end

else

begin if(out[3:0]= =9)

begin c<=1; out[3:0]<=0; end

else

begin out[3:0]<= out[3:0]+1; c<=0; end

end

end

endmodule

counter_10_tp.v是testbench文件,用来测试验证十进制计数器,代码如下:‘timescale 1ns/1ns

module counter_10_tp;

reg clk,clr;

wire cout;

wire [3:0] cnterout;

counter_10 counter10(. clk(clk), . clr(clr) , . c(cout), . out(cnterout));

always #5 clk=~clk;

initial

begin

clk<=0;

clr<=0;

#10 clr<=1;

#30 clr<=0;

#40 clr<=1;

#2000 $stop;

end

endmodule

3. Quartus 8.0新建一个工程,然后编写两个文件如下:

顶层文件“count4.v”源码为:

module count4(clk,reset,out); //4位计数器模块

input clk,reset;

output[3:0] out;

reg[3:0] out;

always @(posedge clk)

begin

if (reset)

out<=0;

else

out<=out+1;

endmodule

ModelSim仿真用到的测试文件“count_tp.v”源码为:(注意,该文件不加入工程中)

`timescale 1ns/1ns //定义时延单位1ns和时延精度为1ns(即精确到1ns)

module count_tp; //测试模块

reg clk,reset; //输入激励信号定义为reg型

wire[3:0] out; //输出信号定义为wire型

parameter DELY=100;

count4 mycount(.clk(clk),.reset(reset),.out(out)); //调用测试对象count4

always #(DELY/2) clk=~clk; //产生时钟波形

initial //激励波形定义

begin

clk=0;

reset=0;

#DELY reset=1;

#DELY reset=0;

#(DELY*20) $finish;

end

initial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out);//结果显示

endmodule

4.简单的测试设计实例化用户设计,然后提供相应的激励。

测试输出被图形化显示在仿真器的波形窗口里或者作为文本发送到用户的终端或者是管道输出文本。

以下是一个简单的用Verilog实现的设计,它实现了一个移位寄存器的功能。

module shift_reg (clock, reset, load, sel, data, shiftreg);

input clock;

input reset;

input load;

input [1:0] sel;

input [4:0] data;

output [4:0] shiftreg;

reg [4:0] shiftreg;

always @ (posedge clock)

begin

if (reset)

shiftreg = 0;

else if (load)

shiftreg = data;

else

case (sel)

2’b00 : shiftreg = shiftreg;

2’b01 : shiftreg = shiftreg << 1;

2’b10 : shiftreg = shiftreg >> 1;

default : shiftreg = shiftreg;

endcase

end

endmodule

<!--[endif]-->

以下是简单的测试设计示例移位寄存器设计的例子,verilog描述。

module testbench; // declare testbench name

reg clock;

reg load;

reg reset; // declaration of signals

wire [4:0] shiftreg;

reg [4:0] data;

reg [1:0] sel;

// instantiation of the shift_reg design below

shift_reg dut(.clock (clock),

.load (load),

.reset (reset),

.shiftreg (shiftreg),

.data (data),

.sel (sel));

//this process block sets up the free running clock initial begin

clock = 0;

forever #50 clock = ~clock;

end

initial begin// this process block specifies the stimulus.

reset = 1;

data = 5’b00000;

load = 0;

sel = 2’b00;

#200

reset = 0;

load = 1;

#200

data = 5’b00001;

#100

sel = 2’b01;

load = 0;

#200

sel = 2’b10;

#1000 $stop;

end

initial begin// this process block pipes the ASCII results to the

//terminal or text editor

$timeformat(-9,1,"ns",12);

$display(" Time Clk Rst Ld SftRg Data Sel");

$monitor("%t %b %b %b %b %b %b", $realtime,

clock, reset, load, shiftreg, data, sel);

end

endmodule

以上的测试设计实例化设计,设置时钟,提供激励信号。

所有的进程块在仿真时间零点开始。

英镑标记(#)说明下一个激励作用前的延迟。

$stop命令使仿真器停止测试仿真(所有测试设计中都应该包含一个停止命令)。

最后,$monitor语句返回ascII格式的结果到屏幕或者管道输出到一个文本编辑器。

接

后的是一个vhdl描述的的测试设计,它实例化设计并提供激励到上述用verilog 描述的移位寄存器.。