Quartus调用ModelSim仿真教程

- 格式:pdf

- 大小:764.44 KB

- 文档页数:20

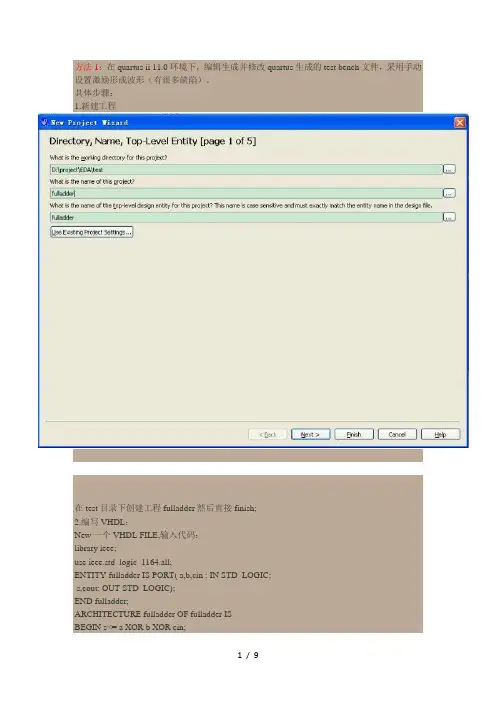

方法1:在quartus ii 11.0环境下,编辑生成并修改quartus生成的test bench文件,采用手动设置激励形成波形(有很多缺陷)。

具体步骤:1.新建工程在test目录下创建工程fulladder然后直接finish;2.编写VHDL:New一个VHDL FILE,输入代码:library ieee;use ieee.std_logic_1164.all;ENTITY fulladder IS PORT( a,b,cin : IN STD_LOGIC;s,cout: OUT STD_LOGIC);END fulladder;ARCHITECTURE fulladder OF fulladder ISBEGIN s<= a XOR b XOR cin;cout <=(a AND b) OR (a AND cin) OR (b AND cin);END fulladder;保存在test目录下,文件名为默认fulladder。

3. 在Quartes II 11.0界面菜单栏中选择 Tools-->options选项卡中选中EDA tool options,在该选项卡中下面的ModelSim-Altera一项指定安装路径为(如d:/Altera/11.0/modelsim_ae/win32aloem)4.在Quartes II 11.0界面菜单栏中选择Assignments->Settings。

选中该界面下EDA Tool settings中的Simulation一项;Tool name中选择ModelSim-Altera;Format for output netlist中选择开发语言的类型VHDL或其它,如图:然后点击APPLY应用和OK。

5.设置完成后,编译工程:在Quartus II 11.0界面菜单栏中选择菜单栏选择Processing-->start Compilation,等待编译,无错后会在test目录下生成simulation目录,执行下一步。

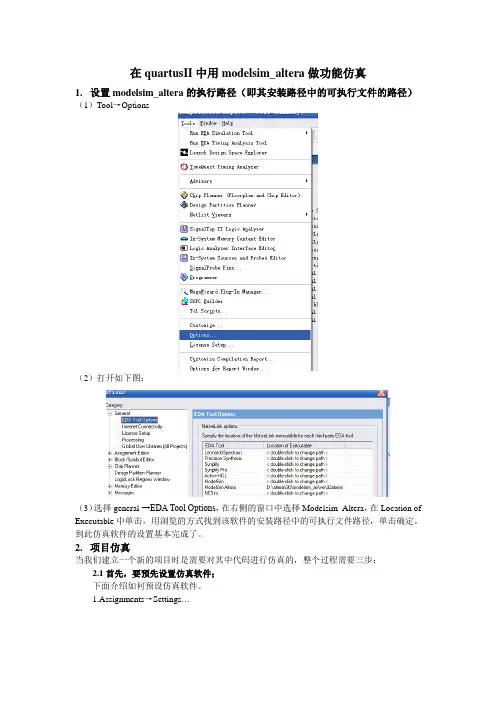

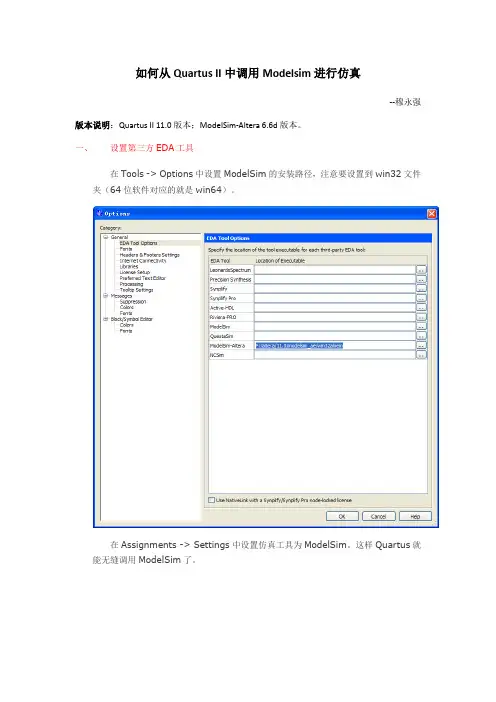

在quartusII中用modelsim_altera做功能仿真1.设置modelsim_altera的执行路径(即其安装路径中的可执行文件的路径)(1)Tool→Options(2)打开如下图:(3)选择general →EDA Tool Options,在右侧的窗口中选择Modelsim_Altera,在Location of Executable中单击,用浏览的方式找到该软件的安装路径中的可执行文件路径,单击确定。

到此仿真软件的设置基本完成了。

2.项目仿真当我们建立一个新的项目时是需要对其中代码进行仿真的,整个过程需要三步:2.1首先,要预先设置仿真软件;下面介绍如何预设仿真软件。

1.Assignments→Settings…2.打开如下界面3选择“Simulation”,右侧设置按上图设置。

2.2其次,仿真之前需要编写测试平台,测试平台有两种的方法:●直接建立XX.v文件●在quartusII中自动生成测试平台模板文件,文件为XX.vt文件下面介绍如何自动生成测试平台模板文件。

1.Processing→Start→Start Test Bench Template Writer注意:要生成testbench模板的前提条件是为项目选择预用的仿真软件,然后模块必须编译成功。

Testbench模板生成后的默认路径为:项目目录\simulation\modelsim\项目名.vt(因为刚才在预设置仿真软件时的“Output Directory”选择的是默认的值simulation\modelsim)。

2.对于自动生成的测试平台模版需要打开修改测试激励信号,这里不做介绍,很简单的。

2.3改写完后要在项目里添加测试平台文件到项目里。

1.Assignments→Settings…2.在打开界面做如下操作:(1)选择“Compile test bench”,然后单击“Test Benches…”(2)打开下面的窗口(3)单击“New”打开下面的窗口,且按图中填写相关信息这个窗口是用来输入testbench的资料和选择testbench的路径的。

目录Quartus中设置modelsim仿真 (1)一、运行环境 (1)2.1、在Quartus中设置仿真环境 (1)2.2在Quartus中设置仿真参数 (3)2.3仿真 (5)Quartus中设置modelsim仿真一、运行环境1.1软件环境:Quartus V11.1Modelsim10.0.Cwindows7.01.2硬件环境芯片:MAXII EPM1270T144二、设置过程2.1、在Quartus中设置仿真环境点上图中的【Launch Simulation Library Compiler】,处在上图中我们按数字顺序设置:①仿真工具路径及我们安装的modelsim的路径,记住是modelsim.exe所在文件位置。

②选择我们要使用的仿真库,我们现在用的是maxII系列的,所以选择它,如你还要其它的,可以自己选择③选择仿真语言,你用verilog编写的测选择verilog④设置编译后的输处路径⑤选择是否将设置加到工程中设置好后点【StartCompilation】开始编译编译完成后会出现以下窗口点OK后,我们会看到一些信息如上的信息则表示没有问题2.2在Quartus中设置仿真参数回到主窗口,按下图中步骤打开设置窗口设置窗口如下,在category中点【EDA Tool Settings】中的【Simulation】按上图中的,先选择Tool Name再一步一步设置设置完1,2,3步后开始设置第4步,设置quartus与modelsim的链接按下图操作先选择Compile test bench,再点击【Test benches】按钮,打开设置窗口按上图1、2、3、4设置好后,开始添加仿真驱动文件(此驱动文件就是modelsim仿真文件了,要自己编写,但不需要加到工程中。

我写的是一个sim.v文件,sim.v中的模块名也为sim.2.3仿真做完以上操作就可以进行仿真了仿真前先编译一下工程文件,如没有任何问题则可以进行以下操作点击仿真按钮后,Quartus就会自动调用modelsim了。

quartus 中调用modelsim仿真

在quartus中调用modelsim仿真,不需要调用额外的库,因为一直以来没有完完整整的好好认真的学习altera fpga,所以一直是旁门左道的折腾,导致学到的,一段时间后又忘记了,所以现在做点笔记,下次忘记的时候能不走弯路。

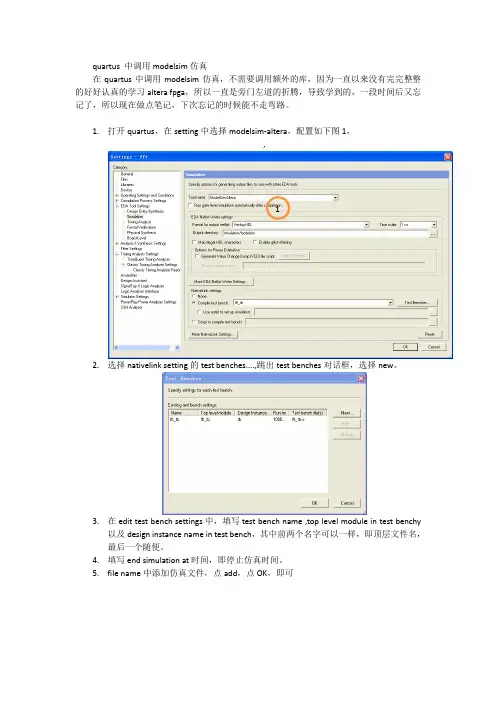

1.打开quartus,在setting中选择modelsim-altera,配置如下图1,

,

1

2.选择nativelink setting的test benches....,跳出test benches对话框,选择new。

3.在edit test bench settings中,填写test bench name ,top level module in test benchy

以及design instance name in test bench,其中前两个名字可以一样,即顶层文件名,最后一个随便。

4.填写end simulation at时间,即停止仿真时间。

5.file name中添加仿真文件,点add,点OK,即可

6.重新编译

7.tools ,run eda simulate tool,rtl eda simulation.

8.结束,直接进入modelsim altera界面仿真。

2014-06-24--------------------------------------------------------------------angry_kua_max。

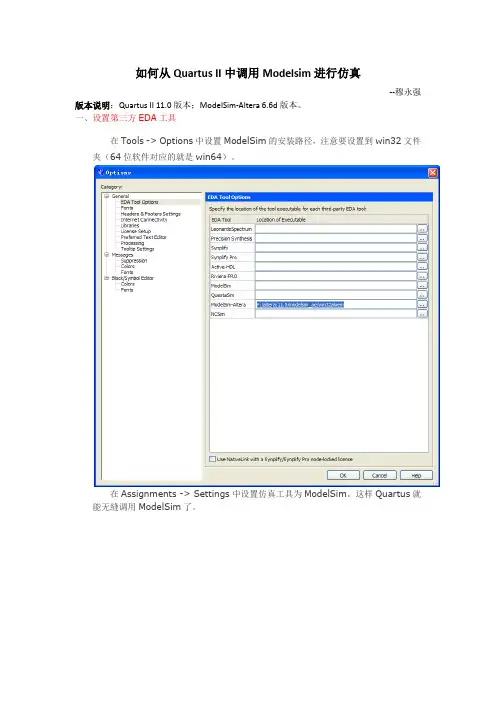

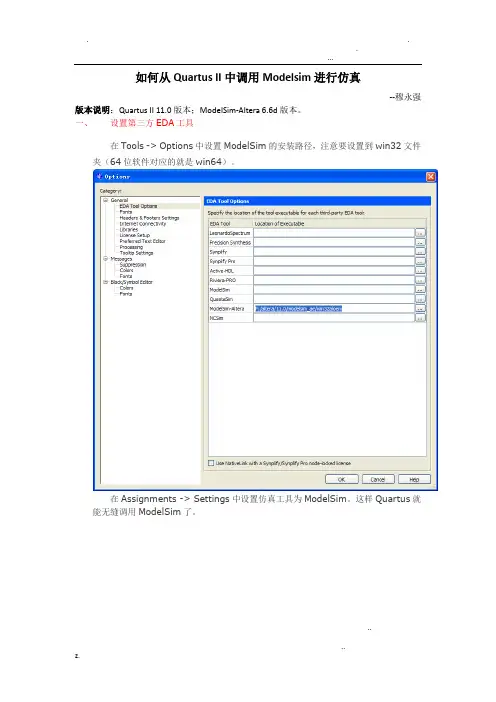

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\modelsim文件夹下的.vt格式文件。

打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

1.首先安装好quartus和modelsim2.复制altera quartus eda sim_lib 中对应芯片的.v文件到modelsim文件夹内3.打开quartus新建工程在第四步eda tool setting 中simulation选项中选择modelsim 语言默认为veillog 后面不打勾4.assignments settings eda stimulation工具选择modelsim 路径选择modelsim安装的路径写到win32这一步点击确定至此准备工作全部完成5.写veillog 程序然后保存编译编译后会在我们的工程目录下生成simulation文件夹,里面又有一个modelsim文件夹。

6.创建或者是编写testbench引导文件简单的可以创建复杂的需要自己编写quartus自己创建不了这是一个端口引导文件目的是建立modelsim和quartus之间的桥梁能够让modelsim创建出我们需要的与quartus中相匹配的端口并且执行相同的功能这些功能执行信息都存放在了testbench引导文件当中7.创建testbench文件过程:Processing->Start->Start Test Bench Template Write这时创建的testbench文件存放在4中所说的modelsim文件夹中以.vt为后缀名以工程名命名8.添加该文件:Assignments->EDA Tool Settings选择Simulation设置仿真环境在NativeLink settings中选择Compile test bench并点击后面的Test Benches 在Test Benches中点击New设置Test Bench属性在Test bench entity栏一定要填写刚刚我们创建的testbench文件的实体名即module top_vlg_tst();中的top_vlg_tst。

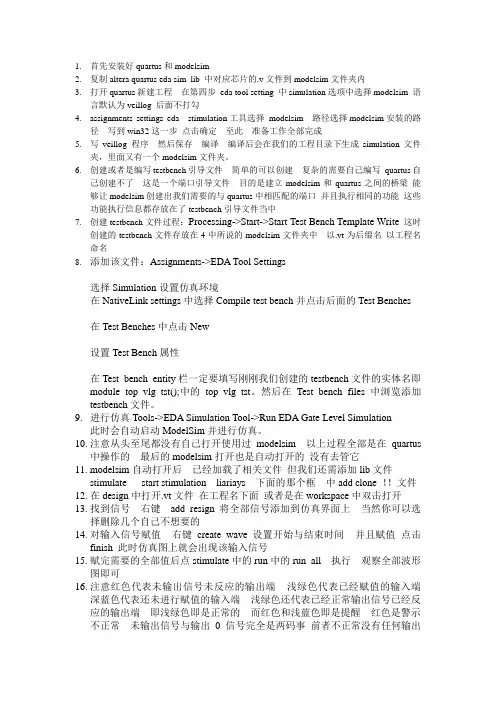

1.撰写testbench激励文件:单击Quartus中的菜单‘Processing’->‘start’->‘Start Test Bench Template Writer’,如图一所示,自动生成激励模板(*.vt)。

打开该模板,并填写完整,保存,编译。

Testbench 常用语:●clk<= not clk after 10 ns;●process beginwait for 10 ns; clk<='1';wait for 10 ns; clk<='0';end process;●en <= '0' after 0 ns,'1' after 50 ns,'0' after 850 ns,'1' after 900 ns;2. Modelsim和Quartus的连接。

单击Quartus中的菜单‘Tools’->‘options’,如图二所示。

随后出现图三所示的窗口,点击左边菜单树下的‘Eda Tool Options’,再将原先modelsim的启动路径拷贝到‘Modelsim’的空白处,或单击右侧的‘。

’选择启动路径。

最后点击Ok,连接生效。

图二图三3. 设置编译信息。

单击Quartus中的菜单‘Assignment’->‘Settings’,如图四所示。

随后进入图五所示的Settings 界面,点击左侧菜单树‘EDA Tool Settings’下的‘Simulation’,右边的窗口出现Simulation 界面,并进行如图五的设置。

其中点中‘Compile test bench’左边的圈圈后,再点击右侧的按钮‘Test Benches。

’进入图六所示的界面,点击右上按钮‘New’进入图七所示的‘New Test Bench Settings’界面,填入相关信息:激励文件名(1),激励文件实体名(2),激励文件中的例化名(3),最大仿真时间(4),和激励文件的具体路劲(5)。

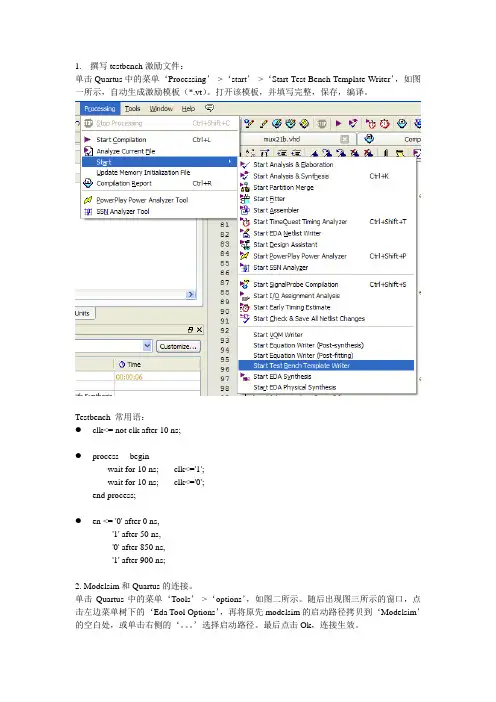

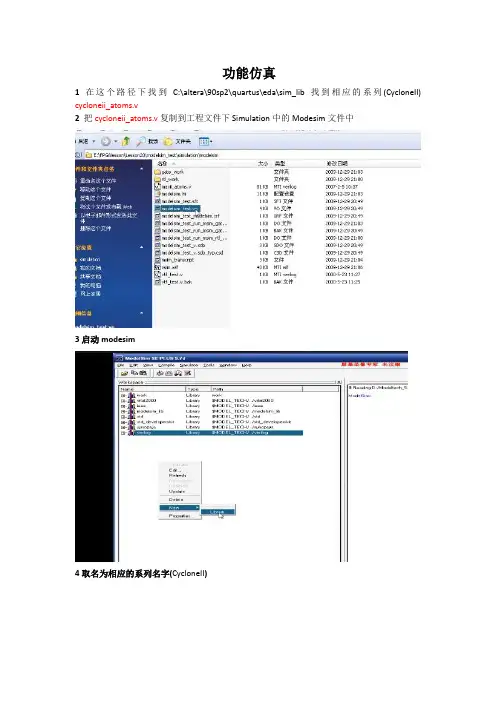

功能仿真1在这个路径下找到C:\altera\90sp2\quartus\eda\sim_lib找到相应的系列(CycloneII)cycloneii_atoms.v2把cycloneii_atoms.v复制到工程文件下Simulation中的Modesim文件中3启动modesim4取名为相应的系列名字(CycloneII)5在生成的新库下编译(选中生成的测试脚本文件和cycloneii_atoms.v,和--------.vo三个文件进行编译)--------------编译完成后,右键refresh6,双击测试脚本文件7 add to wave时序仿真1.退出当前(File—close—dataset--sim)2 新建project工程名:随意.路径在quartus工程中的Simulation中的Modesim文件中默认的库名(CycloneII)3添加已经存在的文件(选中生成的测试脚本文件和cycloneii_atoms.v,和----.vo和---.sdo四个文件)4complie(complie al l)5 编译完成后到library(库名(CycloneII))里refresh6,双击测试脚本文件7 add to wave8这个步骤(可以看到时序的信息)以后,如果又想仅仅看看功能仿真到quartus工程中的Simulation中的Modesim文件中找到上述讲到的----.vo文件,打开后注释掉initial(”……………sto”)这一句,即可又仅仅查看功能信息在重新编译一下complie(complie al l)双击测试脚本文件add to wave此时又能看到功能仿真了。

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\models im文件夹下的.vt格式文件。

打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

如何从Quartus II中调用Modelsim进行仿真--穆永强版本说明:Quartus II 11.0版本;ModelSim-Altera 6.6d版本。

一、设置第三方EDA工具在Tools -> Options中设置ModelSim的安装路径,注意要设置到win32文件夹(64位软件对应的就是win64)。

在Assignments -> Settings中设置仿真工具为ModelSim。

这样Quartus就能无缝调用ModelSim了。

..二、编写Testbench我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\modelsim文件夹下的.vt格式文件。

..打开vt文件后可以看到Quartus已经为我们完成了一些基本工作,包括端口部分的代码和接口变量的声明,我们要做的就是在这个做好的模具里添加我们需要的测试代码。

一个最基本的Testbench包含三个部分,信号定义、模块接口和功能代码。

‘timescale 1ns/ 1ps表示仿真的单位时间为1ns,精度为1ps。

想要进行仿真首先要规定时间单位,而且最好在Testbench里面统一规定时间单位,而不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题,而timescale本身对综合也就是实际电路没有影响。

..其实Testbench本身可以看做一个模块或者设备(本例中的模块名为add_vlg_tst),和你自己编写的模块进行通信。

通过Testbench模块向待测模块输出信号作为激励,同时接收从待测模块输出的信号来查看结果。

因此,在待测模块中的reg型信号在Testbench中就变成了wire,待测模块中的wire型信号在Testbench 中则对应为reg型。

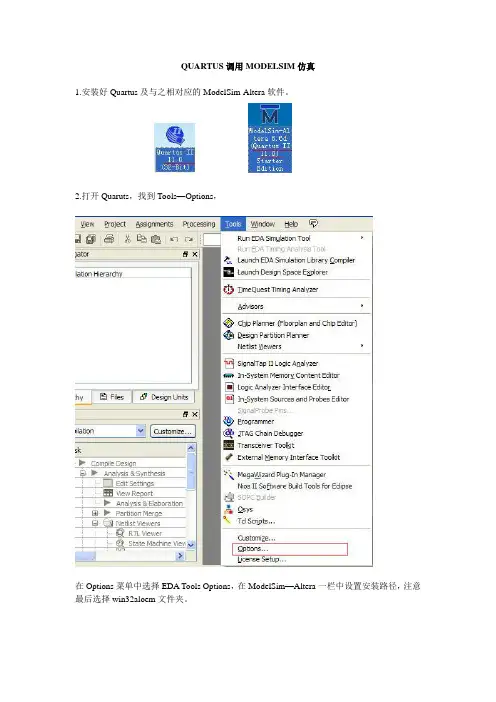

QUARTUS调用MODELSIM仿真

1.安装好Quartus及与之相对应的ModelSim-Altera软件。

2.打开Quaruts,找到Tools—Options,

在Options菜单中选择EDA Tools Options,在ModelSim—Altera一栏中设置安装路径,注意最后选择win32aloem文件夹。

3.打开需要仿真的工程。

在工程—Settings下找到Simulation选项。

按图示设置好相应选项。

4.全编译工程。

完成后在Processing选项下选择Start Test Bench Template Write生成TestBench文件。

TestBench模板存于工程目录下的simulation—modelsim文件夹中,后缀为.vt的文件。

5.打开生成的TestBench文件。

添加必要的激励和复位信号。

6.继续在工程—Settings—Simulaion下设置TestBench路径。

在弹出的对话框中设置,第一栏为testbench文件名,第二栏为tentbench中模块名,

若用verilog编写代码,模板默认生成的模块名后缀为_vlg_tst,可以在此处设置仿真结束时间,最后添加testbench文件。

7.完成后在tools下选择EDA RTL Simulaion,即可调用Modelsim进行功能仿真。

8.Modelsim 自动对文件进行编译,最后生成仿真波形。

QUARTUS II 10.1调用ModelSim-Altera仿真的过程(以上软件在六维空间上面都有,只有QUARTUS需要破解,破解方法在另外一篇文章中详述)。

我是个菜鸟,刚接触这个QUARTUS仿真,以前的版本都是直接利用自带的仿真软件,建立一个波形文件vector wavefile(后来发现这个文件可以在QUARTUS里面直接转化成TESTBENCH文件),现在10.0以后不支持直接这么仿真了,而是建议用外部的仿真器仿真(不知道我理解的对不对)。

害的我费了老大的劲,关键是我是初级的水平,能不能整点容易的。

废话少说,主要是发泄一下我的积怨。

(本文参考“Quartus II 调用ModelSim 仿真”一文)1.建立工程文件,这个我就不多说了。

网上有很多,不过在这里,我想提示一下就是工程文件名称要跟顶层实体名称一致(如果只有一个文件的话,那么工程名要跟MODUEL(Verilog HDL),ENTITY(VHDL)后面的名称一致,还有一个就是这里要跟文件名一致,这个文件是顶层文件),这个名称一致的问题至关重要,在后面还有很多地方要一致,就是大家记住一句话,所有的MODUEL和ENTITY的名称要和文件名一致,我就是后面TESTBENCH 中的MODUEL名称和文件名称不一致导致我出错好久。

2.建立Verilog文件(此处为顶层文件),文件名要和项目名一致,且和MODUEL名一致。

文件如下:在保存之前:保存之后,是自动添加到项目中的,只要文件名一致:3.设置仿真器:Assignments---settings---这里tool name:Format for output netlist:用哪个选哪个,后面的不用改(这个是综合的时候用的,用于生成网表文件),还有个东西就是TESTBENCH 在后面讲。

这里设置完了之后编译源文件就能在那个目录下面生成simulation\modelsim文件夹。

Quartus II调用ModelSim仿真下面是基于在Altera Quartus II下如何调用ModelSim进行仿真的一个实例。

不能否认,Quartus II(我用的7.0)无法像ISE那样方便的直接调用ModelSim,而是需要额外的做一些工作。

这确实给我们的仿真调试带来了一些不便。

特权同学也是在摸索了好久以后才彻底搞定这个问题,下面分享下,力求明白易懂,让大家少走一些弯路。

1、打开Quartus II,新建一个工程,工程代码如下(只是做一个简单的二分频电路):module modelsim_test(clk,rst_n,div);input clk; //系统时钟input rst_n; //复位信号,低有效output div; //2分频信号reg div;always @ (posedge clk or negedge rst_n)if(!rst_n) div <= 1'b0;else div <= ~div;endmodule2、进入菜单栏的AssignmentsÆEDA Tool Settings,进入如下界面:双击“EDA tools”下的“Simulation”选项,弹出如下界面:点击Tool name最右侧的下拉条,选择“ModelSim”,在弹出的界面做如下设置:3、以上设置完成,重新编译工程。

打开工程目录,看到多了一个“simulation”文件夹,再打开该文件夹下的“modelsim”文件夹。

看到有三个文件,其中.vo文件就是我们的代码布局布线信息。

仿真还需要几个文件,我们把它们都拷贝到该目录下。

4、打开“C:\altera\70\quartus\eda\sim_lib”(具体quartus软件安装文件的根目录视您的实际情况而定,大体路径都一样),因为我们用的是MAX II器件,所以把“maxii_atoms.v”拷贝到3中提到的目录下,这个文件是仿真元件库。

在QuartusⅡ中调用ModelSim进行仿真Quartus Ⅱ版本:Quartus Ⅱ10.0 (32-bit);安装路径为D:\Myfiles\QUARTUS_10.0 ModelSim版本:ModelSim SE 6.5;安装路径为D:\Myfiles\ModelsimSE一、Quartus设置(1)在QuartusⅡ中指明仿真工具及其路径(2)在QuartusⅡ中编译所需的元器件库二、建立工程及仿真(1)在QuartusⅡ中建立工程counter,并指明仿真工具(2)顶层文件代码(3)激励文件代码(4)在Quartus中添加testbench文件(5)在Quartus中全编译工程(6)前仿真(7)后仿真一、QuartusⅡ的相关设置(1)在QuartusⅡ中指明仿真工具及其路径在QuartusⅡ中执行Tools\Options,打开EDA Tool Options选项卡。

我们使用ModelSim 进行仿真,所以在ModelSim对应的Location of Executable中选择ModelSim的安装路径D:\Myfiles\ModelsimSE\win32,如图1所示:图1(2)在QuartusⅡ中编译所需的元器件库1)在ModelSim安装路径D:\Myfiles\ModelsimSE中新建文件夹modelsimSE_lib,用于存放编译的文件2)在QuartusⅡ10.0中执行Tools\Launch EAD Simiulation Library Compiler,在打开的界面中Executable location一项选择ModelSim的安装路径D:\Myfiles\ModelsimSE\Win32在Avaliable families中根据自己需要选择可能用的到器件系列,如cyclone、stratix等;在这里可以多选择一些,以备能用到,并且一次编译后,以后就不用再编译了。

Quartus 中调用modelsim的流程1.设定仿真工具assignment→setting→EDA tool setting→simulation选择你需要的工具。

2.自动产生测试激励文件模板:processing→start→Start test bench template writer我们点击之后系统会自动在目录:当前文件夹→simulation →modelsim (这个文件夹名字跟你选的仿真工具有关) 中产生一个测试激励文件xxx.vt(Verilog test bench) 或者xxx.vht(VHDL test bench), 文件名跟你工程中的Top module 的名字一样,后缀为.vt或者.vht。

3.编辑走动生成的test bench文件我们加入自己需要的激励以及初始化语句,这里我们还要修改test bench的模块名字为tb(我们会看到这个名字和后面的设定有联系)。

4.连接test bench,我们需要从Quartus中自动调用仿真工具,所以需要设定Native Link选项。

a)还是在simulation的设置页面里,设定Native Link对话框中的设定。

我们这里因为需要工具自动调用激励所以选中b)点击右边的Test Benches, 我们需要在这里设定一个相关联的test bench.这里会弹出一个让你指定test bench的对话框,因为我们之前没有指定任何的test bench,所以这里是空白的。

c)指定test bench因为我们是第一次产生test bench,点击new.点击New之后会产生一个New Test bench setting的对话框,在这里你将test bench和你的相应的test bench file 进行绑定。

我们这里在Test bench name的对话框中输入一个名字”my_1st_tb”, 我们将看到,在下面的Top level module in test bench对话框中也自动显示”my_1st_tb”. 注意这个名字应该和你的test bench 中的module name一直,我们之前在第3步的时候将test bench的module name已经改成了tb,所以我们这里应该把对话框中的名字改成tb。

系统的仿真方法图1在Quartus II中配置ModelSim-Altera应用第三方软件路径首先,建立工程时,选择仿真软件选ModelSim-Altera,我用的是Verilog硬件描述语言,然后继续内容的编写。

内容编写之后,打开菜单Tool下的Options,在EDA Tool Options中的ModelSim-Altera进行第三方路径的设置,如图1-1 所示,已完成在Quartus II中配置ModelSim-Altera应用第三方软件路径。

如图2 NativeLink settings然后,选择Assignments下的EDA Tool Settings下的Simulation中的NativeLink settings,选择Compile test bench,设置其中的Test Benches,New,然后编辑里头内容,然后具体内容如图 2 所示,然后,Test bench name填入的是设计的顶层文件、Top level module in test bench和Design instance name in test bench是填入仿真的文件的名字,Test bench files填入仿真的文件路径。

最后生成测试文件,选择在Quartus II开发界面菜单栏下Processing下的Start 下面的Start Test Bench Template Writer,提示生成成功。

生成测试仿真文件的大框,里头一些内容还需自己添加。

以下告诉你如何添加内容,在仿真目录下找到为“.vt”的文件,然后打开这个文件,根据需要给以激励和时钟进行编辑。

具体的Test Bench的编写正在附录四中,写完Test Bench之后就可以进行在菜单栏Tools 下的Run EDA Simulation下的EDA RTL Simulation仿真。

一、Quartus 2中仿真环境设置1、设置仿真软件modelsim-altera路径:tools->options->general->eda tool options,弹出对话框:Modelsim-altera:C:\altera\11.0\modelsim_ase\win32aloem(说明:C:\altera\11.0\modelsim_ase\win32aloem为modelsim安装路径)点击:ok2、Assignments->settings->EDA tools settings->simulation,弹出对话框:Tool name:modelsim—altera;Format for output netlist:verilog hdl;设置好后,点击apply和ok;3.测试平台设计(自动生成测试平台模板文件)先将Con_Motor.v文件设置为顶层文件;Processing->start->start test bench template writer,如图:生成的testbench文件路径:项目\simulation\modelsim\顶层文件名.vt,即testbench文件与顶层文件名相同;该例为Con_Motor.vt。

(1)向设计工程添加测试平台文件Con_Motor.vt;(2)打开Con_Motor.vt文件后:先用双斜杠//屏蔽掉@eachvec语句,即//屏蔽掉@eachvec语句;(把@eachvec注释掉才能得到一段很长的波形,不然仿真时间就非常短,如果在它之前有在这个always过程块里规定时钟信号的翻转的话,这个时钟信号也不会翻转。

总之,注释掉它。

)添加激励信号clk和command,修改后的测试平台文件如下:`timescale 1ns/ 1nsmodule Con_Motor_vlg_tst();// constants// general purpose registersreg eachvec;// test vector input registersreg CLK;reg Command;// wireswire CP;// assign statements (if any)Con_Motor i1 (// port map - connection between master ports and signals/registers.CLK(CLK),.CP(CP),.Command(Command));initialbegin// code that executes only once// insert code here --> beginCLK =0;Command =0;#5 Command =1;// --> end$display("Running testbench");endalways// optional sensitivity list// @(event1 or event2 or .... eventn)begin// code executes for every event on sensitivity list// insert code here --> begin#1 CLK <= ~CLK;//@eachvec;// --> endendendmodule(1)向仿真工程添加测试平台文件:Assignments->settings->simulation->compile test bench ,如图:单击“test benches..”,如图:单击“new”,如图:Test bench name:测试平台名,即.vt的文件名;Top level module in test bench:test bench中顶层模块名,即testbench中的待测模块名;注意:Top level module in test bench 必须和testbench中的待测模块名一致;Test bench files栏的File name项:测试平台文件名,和Test bench name相同,即.vt的文件名,单击...进行浏览,找到.vt文件,该.vt文件的浏览图:单击open打开;单击ADD添加后,图:单击ok后,如图:单击“ok”后,如图:单击apply,再单击ok,完成测试平台向仿真工程的添加。