宽带CIC抽取滤波器的一种改进方法

- 格式:pdf

- 大小:553.75 KB

- 文档页数:5

基于CIC抽取滤波器结合串并行的搜索捕获算法贾振东;郭承军;刘赋山【摘要】GPS信号的捕获是GPS接收机的重要环节,其中串行搜索算法,并行码相位算法是GPS信号捕获的常用方法.但随着GPS接收机覆盖我们的生活,对捕获算法的速度要求也就越来越高.提出了一种新的捕获方法,基于CIC抽取滤波器并结合串并行搜索的算法,这种捕获方法在抽取阶段使用CIC滤波器降低频谱混叠的影响,然后在使用并行码相位搜索算法的基础上加入了串行搜索的部分,从而减少了计算量,提高了运算速度.对算法进了仿真,实验结果证明了该方法的有效性和优越性.最后对运算优势进行了分析.【期刊名称】《全球定位系统》【年(卷),期】2016(041)006【总页数】6页(P64-69)【关键词】GPS;捕获;CIC抽取滤波器;结合【作者】贾振东;郭承军;刘赋山【作者单位】电子科技大学电子科学技术研究院,成都611731;电子科技大学电子科学技术研究院,成都611731;电子科技大学电子科学技术研究院,成都611731【正文语种】中文【中图分类】P228.4如今,GPS接收机已应用于各式各样的设备中,用于用户定位等功能。

其中捕获,跟踪以及定位解算等部分是GPS接收机的重要环节。

捕获模块是GPS接收机的第一部分,为了跟踪GPS信号并进行信息解码,就必须先用捕获程序来检测信号的存在[1]。

利用捕获模块得到两个重要的信息,一是C/A码相位信息,另一个是GPS信号多普勒频移后的输入频率。

常用的捕获方法有两种,1)串行搜索捕获算法,2)并行码相位搜索算法。

其中并行码相位搜索算法因为其优越性而应用很广。

本文基于并行码相位搜索捕获算法,对混频前端采样点通过CIC抽取滤波器并结合串行搜索方法对传统捕获方法进行改进,减少其计算量而又不失捕获精度。

串行搜索捕获算法是基于中频信号与本地产生的伪码序列以及本地载波的乘积。

中频信号先和本地伪码序列相乘,然后I,Q通道分别和本地载波信号以及90°相移的本地载波信号相乘,最后积分平方相加得相关结果,原理图如图1所示。

基于FPGA的CIC滤波器的优化设计李怡琳;肖顺文;易欢;杨湲【摘要】针对在数字下变频系统中单独应用CIC滤波器实现抽取滤波时,因高阶CIC滤波器通带衰减过大的问题,在原有的CIC滤波器后级联一补偿滤波器以达到降低采样率,防止频率混叠的目的.仿真结果表明,改进后的CIC滤波器通带波纹数减少,通带衰减降幅明显.%This paper talks about the problem of large passband attenuation caused by the high order of CIC filter when it is individually applied in the DDC system to achieve decimation and filtration.Because of that,a compensation filter is attached to the original CIC filter to reduce the sampling rate and avoid aliasing frequency.The simulation results show that the improved CIC filter has much fewer ripples and the passband attenuation is obviously decreased.【期刊名称】《西华师范大学学报(自然科学版)》【年(卷),期】2017(038)001【总页数】5页(P106-110)【关键词】FPGA;数字下变频;CIC滤波器;ISOP滤波器【作者】李怡琳;肖顺文;易欢;杨湲【作者单位】西华师范大学电子信息工程学院,四川南充 637009;西华师范大学电子信息工程学院,四川南充 637009;西华师范大学电子信息工程学院,四川南充637009;西华师范大学电子信息工程学院,四川南充 637009【正文语种】中文【中图分类】TN92软件无线电中的数字接收机前端所接收到的数字信号由于高频采样,数据量较大,所以对数据进行采样后的处理就显得尤为重要。

改进型CIC抽取滤波器设计与FPGA实现张杰;戴宇杰;张小兴;吕英杰【摘要】为了改善级联积分梳状(CIC)滤波器通带不平和阻带衰减不足的缺点,给出一种改进型CIC滤波器.该滤波器在采用COSINE滤波器提高阻带特性的基础上,级联了一个SINE滤波器,补偿了其通带衰减.硬件实现时,采用新的多相分解方法结合非递归结构,不仅大大减少了存储单元数量,还使电路结构更加规则.经仿真和FPGA 验证,改进型CIC滤波嚣使用较少硬件,实现了阻带衰减100.3 dB,通带衰减仅为0.000 1 dB.【期刊名称】《现代电子技术》【年(卷),期】2009(032)010【总页数】3页(P22-24)【关键词】CIC抽取滤波器;COSINE滤波器;SINE滤波器;设计优化;FPGA【作者】张杰;戴宇杰;张小兴;吕英杰【作者单位】南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071【正文语种】中文【中图分类】TP368.1抽取滤波器是Σ-Δ模/数转换器中的重要组成部分,积分梳状滤波器经常作为第一级滤波器,用以实现抽取和低通滤波[1]。

其优点是实现时不需要乘法器电路,且系数为整数,不需要电路来存储系数,同时通过置换抽取可以使部分电路工作在较低频率,与相同滤波性能的其他FIR滤波器相比,节约了硬件开销[2]。

经过仿真,抽取率为32的一阶积分梳状滤波器第一旁瓣相对于主瓣的衰减最大约为15 dB,这样的阻带衰减根本达不到实用滤波器的设计要求。

为了改变滤波性能,一般采用级联积分梳状滤波器(CIC)[3]。

但经过CIC降频滤波系统降频后会产生信号混叠现象,并且主瓣曲线不平,需要用新的算法或新结构来修正改善这些特性。

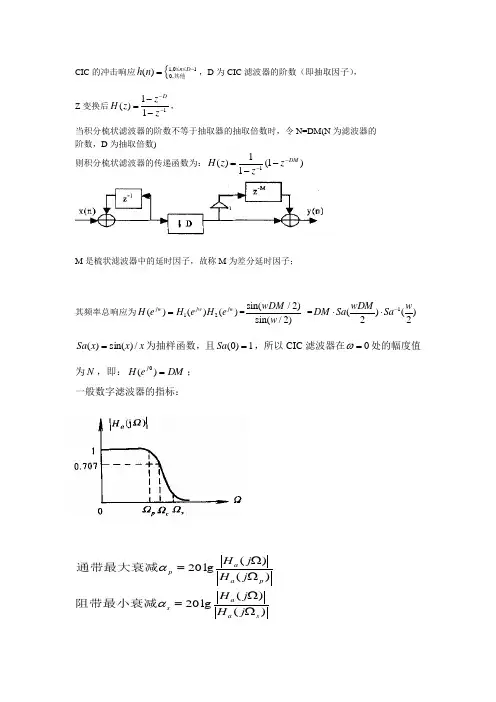

1 CIC抽取滤波器原理经典的抽取滤波器为Hogenauer [3]CIC滤波器,其传输函数表达式为:(1)式中:参数M为降频因子,决定了CIC的通带大小;K为滤波器的阶数,对阻带衰减起到加深作用。

CIC 的冲击响应{1,010,()n D h n ≤≤-=其他,D 为CIC 滤波器的阶数(即抽取因子),Z 变换后11()1Dz H z z ---=-,当积分梳状滤波器的阶数不等于抽取器的抽取倍数时,令N=DM(N 为滤波器的 阶数,D 为抽取倍数)则积分梳状滤波器的传递函数为:)1(11)(1DM z zz H ----=M 是梳状滤波器中的延时因子,故称M 为差分延时因子;其频率总响应为12()()()jw jw jwH e H e H e ==sin(/2)sin(/2)wDM w =1()()22wDM wDM Sa Sa -⋅⋅x x x Sa /)sin()(=为抽样函数,且1)0(=Sa ,所以CIC 滤波器在0=ω处的幅度值为N ,即:DM e H j =)(0; 一般数字滤波器的指标:()20lg()()20lg ()a pa p a s a s H j H j H j H j ααΩ=ΩΩ=Ω通带最大衰减阻带最小衰减即:CIC 幅频特性响应曲线图由其频率响应函数可以看出其主瓣电平最大为D ,旁瓣电平为21.51()sin(3/2)/sin(3/2)sin(3/2)j DMH e DM DM ωπωπππ=⋅==,旁瓣与主瓣的差值 (用dB 数表示)为: dB A DM s 46.1323lg 20lg201===πα 可计算出旁瓣与主瓣的差值约为13.46,意味着阻带衰减很差,单级级联时旁瓣电平很大,为降低旁瓣电平,增加阻带衰减采用级联的方式,N 级频率响应为:)2()2()()2/sin()2/sin()(ωωωωωQ Q Q Qj Q Sa DM Sa DM DM e H -⋅⋅=⎥⎦⎤⎢⎣⎡=, 可得到N 级CIC 的旁瓣抑制 dB Q Q A DM Q Qs )46.13(23lg 20)lg(201⨯=⋅==πα 分析一下发现在Q 级联时多出了Q DM 这个处理增益,因此分析一下尽量减少带容差(通带衰减),即,在通带,幅度应尽量平缓;下面就它的幅平响应曲线来分析:00()20lg ()()20lg()ps j a p jw a j a s jw a H e H eH e H e αα==1、设在红线w1处抽取的信号带宽很窄,为无混叠信号的带宽,能很好的对窄带信号进行滤波,去除掉高频信号噪声;且在绿线w2=2pi/DM-w1处衰减值足够大,则在其信号带宽,红线到绿线,信号给CIC 滤 波器带来的混叠就可以忽略,计算此时阻带衰减:)2/sin()2/sin(lg 20()(lg 2022012w DM w DM e H e H A jw j ==·引入带宽比例因子b=B/(fs/DM ), B 为抽取信号的带宽,D 为抽取因子,M 为延时因子;fs 为输入端采样率,则w1=b*2pi/DM ;带入可化简得:b A lg 201-≈; (假设b=0.01;即fs=100MHz ,D=20,信号带宽为50khz,此时衰减为40dB);可见单级的CIC 滤波器的无混叠信号带宽的阻带衰减能达到40dB;;并不怎么大,适用于较粗略的滤波,适合放在第一级抽取;如果采用级联的方式可以加大无混叠信号带宽;但是满足的通带不够窄;2、在红线w1处幅度不能下降太多,通带幅值容差不能太大,否则会引起高频失真;设该带容差为s δ,则,)()(lg 2010jw j s e H e H =δ将w1带入可简化得)sin(lg 20b bs ππδ≈,当N 级时,其带容差也会增大;由上面分析可知,阻带衰减和带容差,只与带宽比例因子b 有关,Df Bb s /=,分析可知,在信号带宽一定的前提下,应尽可能采用小的抽取因子,或增大输入采样率;故一般把它放在抽取系统的第一级,所以在配置CIC 时,信号带宽,采样率,抽取因子,综合考虑,下面是阻带衰减和通带衰减的一个表:表1:大抽取因子下的通带衰减由CIC频幅响应图可以发现,幅频特性的零点位于1/M处(M取值为整数),这说明差分因子M决定了零点的位置;抽取因子D狭定了抽取后信号的采样频率,它同差分延时因子M一起还决定了主瓣和旁瓣的宽度;级数Q可以用来控制阻带衰减,Q越大阻带衰减越大,通带的混叠就越小,但Q越大,通带主瓣衰减也越大,所以Q不可太大,不宜超过5级。

级联积分梳状(Cascade Integrator Comb,CIC)[1]滤波器结构简单、标准化,是高速抽取器中十分简单有效的抗混叠滤波单元,已被广泛使用于多抽样率信号处理系统中。

其组成只有积分器、加法器、寄存器,没有乘法器,使得CIC滤波器非常适合在具有较强实时性和并行处理能力的FPGA 上实现。

但是其阻带衰减和通带波纹的相互抑制限制了其滤波性能。

锐化级联积分梳状滤波器[2]、CIC 滤波器的部分锐化[3]、在CIC 滤波器级联分解的基础上级联一级余弦滤波器[4]、二级补偿CIC 滤波器( TSC -CIC)[5]、内插二阶多项式级联积分梳状滤波器(ISOP-CIC)[6]都是用来进行CIC滤波器改进的技术。

但上述CIC 滤波器的改进或只是降低了通带衰减,或只是提高了阻带衰减,或同时降低通带衰减、提高阻带衰减,但是占用硬件逻辑资源较多。

1432012年第09期,第45卷 通 信 技 术 Vol.45,No.09,2012总第249期 Communications Technology No.249,Totally高速CIC 插值滤波器的位宽分析与优化﹡聂 阳, 戈 华, 赵鹏宇(集宁师范学院 物理系,内蒙古 集宁 012000 )【摘 要】分析了级联积分-梳状(CIC,Cascaded Integrator Comb)插值滤波器的位宽增长原因,重点研究了CIC 插值滤波器非等值位宽的数据通路设计。

在此基础上利用Matlab 和Xilinx System Generator 开发工具搭建了电路的系统模型,最后通过现场可编程门阵列(FPGA,Field Programmable Gate Array)完成电路的寄存器传输级(RTL,Register Transfer Level)验证,仿真结果表明电路设计具有很高的有效性和可行性。

【关键词】CIC 插值滤波器;位宽;FPGA 【中图分类号】TN911.7 【文献标识码】A 【文章编号】1002-0802(2012)09-0143-03Analysis and Optimization of High-Speed CIC Interpolation Filter WidthNIE Yang, GE Hua, ZHAO Peng-yu(Dept of Physics, Jining Teachers College, Jining Inner Mongolia 012000, China )【Abstract】This paper analyzes the increase of CIC (Cascaded Integrator Comb) interpolation filter width, and focuses on the data path design of non equivalent width. Based on this and with Matlab and Xilinx System Generator development tools, the system model of the circuit is built up, and finally through FPGA (Field Programmable Gate Array) RTL (Register Transfer Level), the verification of the circuit is completed. And simulation indicates the effectiveness and feasibility of circuit design.【Key words】CIC interpolation filter; width; FPGA0 引言随着现代无线通信中数据传输率的增加,在一个信号处理系统中常常需要不同的采样率处理信号以及不同采样率的信号之间相互转换。

cic滤波器群时延一、引言CIC(Cascade Integrator-Coupled)滤波器是一种广泛应用于信号处理、通信系统和控制系统领域的数字滤波器。

它具有低通、高通、带通和带阻等多种滤波特性,且具有较宽的阻带、较高的stopband 抑制和较低的过渡带波动等优点。

然而,CIC滤波器也存在群时延较大的问题,这在某些应用场景下会受到影响。

本文将探讨CIC滤波器的群时延特性,以及如何在不同应用场景下优化其性能。

二、CIC滤波器的原理与特性1.基本原理CIC滤波器是一种级联积分器与耦合器的数字滤波器,其基本结构由多个级联的积分器和耦合器组成。

在每个级联单元中,输入信号与耦合器输出信号相加,再经过一个积分器进行积分,最后得到滤波器的输出信号。

2.群时延特性CIC滤波器的群时延特性是指在不同频率下,滤波器对信号的响应速度。

由于CIC滤波器的结构特点,其群时延在低频段较小,随着频率的增加而逐渐增大,在高频段达到最大。

这种特性使得CIC滤波器在某些应用场景下表现出较大的群时延,从而影响系统性能。

三、CIC滤波器在不同应用场景下的表现1.通信系统在通信系统中,CIC滤波器常用于抑制载波泄漏、解调器输出滤波器等。

由于通信信号频率较高,CIC滤波器的群时延特性对系统性能影响较大。

在这种情况下,可以采用优化结构、调整参数或与其他滤波器结合使用等方法来降低群时延。

2.信号处理在信号处理领域,CIC滤波器常用于滤波、降噪和锐化等处理。

由于信号处理通常对实时性要求较高,CIC滤波器的群时延特性对处理效果具有重要影响。

在这种情况下,可以通过优化滤波器结构、调整参数或与其他滤波器结合使用来改善群时延性能。

3.控制系统在控制系统中,CIC滤波器常用于滤波器设计、状态观测器和控制器等。

由于控制系统对稳定性要求较高,CIC滤波器的群时延特性对系统性能具有重要影响。

在这种情况下,可以采用优化滤波器结构、调整参数或与其他滤波器结合使用等方法来降低群时延。

cic滤波器补偿CIC滤波器补偿CIC(Cascade Integrator-Comb)滤波器是一种数字滤波器,常用于对离散时间信号进行滤波和降采样处理。

然而,CIC滤波器在降采样过程中会引入频率响应失真,这对一些应用来说是不可接受的。

因此,为了解决这个问题,我们需要对CIC滤波器进行补偿。

CIC滤波器的频率响应失真主要包括两个方面:一是由于积分过程引起的低频截断,二是由于差分操作引起的高频增益。

为了解决这些问题,可以采用两种方法来进行补偿:一是预补偿,二是后补偿。

预补偿是在输入信号经过CIC滤波器之前对其进行处理,以抵消CIC滤波器的频率响应失真。

预补偿的方法有很多种,常用的方法包括多通道滤波器和小波变换等。

多通道滤波器可以通过设计一组滤波器来补偿CIC滤波器的频率响应失真,而小波变换则可以通过将信号变换到频率域进行补偿。

这些方法都可以有效地抑制CIC滤波器的频率响应失真,提高滤波器的性能。

后补偿是在输出信号经过CIC滤波器之后对其进行处理,以抵消CIC滤波器的频率响应失真。

后补偿的方法有很多种,常用的方法包括有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器等。

FIR滤波器可以通过设计一组滤波器来补偿CIC滤波器的频率响应失真,而IIR滤波器则可以通过递归计算来补偿。

这些方法都可以有效地抑制CIC滤波器的频率响应失真,提高滤波器的性能。

无论是预补偿还是后补偿,补偿滤波器的设计都是一个关键的问题。

补偿滤波器的设计需要考虑多个因素,包括滤波器的阶数、截止频率、滤波器类型等。

在实际应用中,可以根据实际需求选择适当的补偿滤波器,以实现对CIC滤波器的补偿。

CIC滤波器是一种常用的数字滤波器,但在降采样过程中会引入频率响应失真。

为了解决这个问题,可以采用预补偿和后补偿两种方法进行补偿。

预补偿是在输入信号经过CIC滤波器之前对其进行处理,后补偿是在输出信号经过CIC滤波器之后对其进行处理。

无论是预补偿还是后补偿,补偿滤波器的设计都是一个关键的问题,需要考虑多个因素。

一种性能良好的高效CIC抽取滤波器的设计叶和忠;赵利;彭小卫;周胜源【摘要】针对传统CIC抽取滤波器性能和结构存在的问题,利用一个ISOP滤波器和余弦滤波器对CIC抽取滤波器的通阻带进行优化,使得CIC抽取滤波器幅频特性得到很好的改善.通过应用非递归结构和部分多相分解技术对CIC抽取滤波器的结构进行分解,得出一个能实现任意抽取因子的改进的CIC抽取滤波器的实现结构.最后的仿真表明:该设计方法使得CIC抽取滤波器性能得到改善,实现结构高效,在实际工程中有很大的应用价值.【期刊名称】《桂林电子科技大学学报》【年(卷),期】2010(030)002【总页数】5页(P113-117)【关键词】CIC抽取滤波器;余弦滤波器;ISOP滤波器;递归结构;部分多相结构【作者】叶和忠;赵利;彭小卫;周胜源【作者单位】桂林电子科技大学,信息与通信学院,广西,桂林,541004;桂林电子科技大学,信息与通信学院,广西,桂林,541004;桂林电子科技大学,信息与通信学院,广西,桂林,541004;桂林电子科技大学,信息与通信学院,广西,桂林,541004【正文语种】中文【中图分类】TN911.7数字下变频技术是从宽带高速的数据流中滤除其中需要的窄带信号,可降低数据流速率,以满足后续的 DSP器件处理,其实现的关键是要找到一个高效的抽取滤波器。

CIC(Cascaded Integrator Comb)滤波器[1]只有加法和延迟单元,不必要像一般的FIR滤波器有复杂的乘法计算,是一个很好的选择。

但是,传统CIC抽取滤波器存在通带衰减过大,阻带抑制不够以及实现结构复杂的问题,给工程应用和实现带来不少困难。

1 CIC抽取滤波器的问题与改进方法1.1 传统 CIC抽取滤波器存在的问题CIC滤波器通常由具有递归结构的积分部分和非递归结构的梳状部分组成。

单级积分梳状滤波器的传递函数表达式为其中:D为抽取因子。

传递函数中的系数1/D,是为了保证直流增益为1。

一种改进型CIC抽取滤波器的实现方法谢海霞;孙志雄【摘要】针对传统CIC抽取滤波器处理宽带信号时,阻带衰减满足要求,通带衰减过大的问题,提出了一种改进CIC抽取器的设计方法;在分级抽取滤波器的基础上用锐化技术改善滤波器通阻带衰减,采用内插二阶多项补偿函数对通带进行额外补偿,使带内更平坦,并利用多相分解的方法降低了抽取滤波器采样率;仿真验证了改进型滤波器具有更好的通、阻带特性.最后在FPGA上实现这个改进型CIC滤波器的设计,并进行了时序仿真和综合验证.【期刊名称】《电子设计工程》【年(卷),期】2018(026)014【总页数】5页(P162-166)【关键词】CIC抽取滤波器;内插二阶多项式;多相分解;FPGA【作者】谢海霞;孙志雄【作者单位】海南热带海洋学院电子通信工程学院,海南三亚572022;海南热带海洋学院电子通信工程学院,海南三亚572022【正文语种】中文【中图分类】TN911.72数字上、下变频器所涉及的抽取和内插存在着混叠、镜频等问题,抽取、内插后如何分离出需要的信号,关键在于抽取前和内插后的抗混叠高效数字滤波器设计。

由于CIC滤波器结构只有乘法运算,便于提高实时性和简化硬件,故常用它作为抗混叠高效数字滤波器。

经典CIC抽取器一般用来处理窄带信号,而处理宽带信号时,幅频响应很不理想,满足带外衰减指标时,通带衰减过大,难以满足抗混叠性能要求。

因此,如何更好地增大滤波器的零点抑制同时又不影响其通带性能一直是CIC滤波器研究的热点[1-5]。

1 CIC抽取器的设计CIC抽取器结构简单,主要由积分部分、抽取部分和梳状部分组成[6]。

其结构如图1所示。

图1 单级CIC抽取滤波器框图式(1)为单级CIC抽取器传输函数。

由于单级CIC的过渡带的衰减性能不是很好,所以实际应用中,通常是由多个单级CIC滤波器级联方法来加大过渡带和阻带的衰减。

多级传输函数为式(2):其中,M为大于1的整数,称为抽取因子,决定了CIC的通带大小;K为级联数,对旁瓣抑制比起到加大作用。