集成电路测试 样题28

- 格式:docx

- 大小:134.73 KB

- 文档页数:2

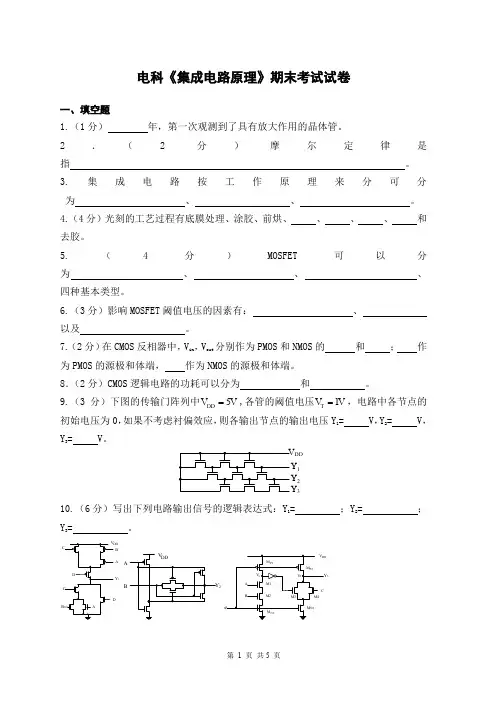

电科《集成电路原理》期末考试试卷一、填空题1.(1分) 年,第一次观测到了具有放大作用的晶体管。

2.(2分)摩尔定律是指 。

3.集成电路按工作原理来分可分为 、 、 。

4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。

5.(4分)MOSFET可以分为 、 、 、 四种基本类型。

6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。

7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 和 ; 作为PMOS 的源极和体端, 作为NMOS 的源极和体端。

8.(2分)CMOS 逻辑电路的功耗可以分为 和 。

9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= V ,Y 2= V ,Y 3= V 。

DD 13210.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。

AB Y 1AB23二、画图题:(共12分)=+的电路图,要求使用的1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CDMOS管最少。

2.(6分)用动态电路级联实现逻辑功能Y ABC=,画出其相应的电路图。

三、简答题:(每小题5分,共20分)1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么?2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么?3.简述静态CMOS 电路的优点。

4.简述动态电路的优点和存在的问题。

四、分析设计题:(共38分1.(12分)考虑标准0.13m μ CMOS 工艺下NMOS 管,宽长比为W/L=0.26/0.13m m μμ,栅氧厚度为2.6ox t nm =,室温下电子迁移率2220/n cm V s μ=,阈值电压T V =0.3V,计算 1.0GS V =V 、0.3DS V =V 和0.9V 时D I 的大小。

1+X集成电路理论测试题及参考答案1、平移式设备芯片检测工艺流程中,上料之后的环节是( )。

A、测试B、分选C、真空包装D、外观检查答案:A平移式分选机设备芯片检测工艺的操作步骤一般为:上料→测试→分选→外观检查→真空包装。

2、转塔式分选机常见故障不包括()。

A、料轨堵塞B、测试卡与测试机调用的测试程序错误C、IC定位错误D、真空吸嘴无芯片答案:C3、利用高能粒子撞击具有高纯度靶材料表面,撞击出的原子最后淀积在硅片上的物理过程是()。

A、电阻加热蒸发B、电子束蒸发C、溅射D、电镀答案:C溅射是在高真空下,利用高能粒子撞击具有高纯度靶材料表面,撞击出的原子最后淀积在硅片上的物理过程。

4、芯片检测工作流程()。

A、确定产品等级、方案编程调试、研读Spe确定测试机、确定机械手、设计测试DUT、批量验证B、确定产品等级、研读Spe确定机械手、设计测试DUT、确定测试机、方案编程调试、批量验证C、确定产品等级、研读Spe确定测试机、确定机械手、设计测试DUT、方案编程调试、批量验证D、确定产品等级、研读Spe确定机械手、确定测试机、设计测试DUT、方案编程调试、批量验证答案:C5、低压化学气相淀积的英文缩写是()。

A、APCVDB、PECVDC、LPCVDD、HDPCVD答案:CAPCVD是常压化学气相淀积;PECVD是等离子体增强型化学气相淀积;LPCVD是低压化学气相淀积;HDPCVD是高密度等离子体化学气相淀积。

6、电子组装业中最通用最广泛的文件格式是()。

A、GerberB、PCBC、ICTD、BOM答案:A7、芯片完成编带并进行清料后,会将完成编带的芯片放在( )上。

A、已检查品货架B、待检查品货架C、待外检货架D、合格品货架答案:B芯片完成编带并进行清料后,将将编带盘、随件单放入对应的中转箱中,并将中转箱放在待检查品货架上等待外观检查。

8、CMP是实现()的一种技术。

A、平滑处理B、部分平坦化C、局部平坦化D、全局平坦化答案:D化学机械抛光(CMP)是通过比去除低处图形快的速度去除高处图形来获得均匀表面,利用化学腐蚀和机械研磨加工硅片和其他衬底材料的凸出部分,实现全局平坦化的一种技术。

第一部分考试试题第0章绪论1.什么叫半导体集成电路?2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写?3.按照器件类型分,半导体集成电路分为哪几类?4.按电路功能或信号类型分,半导体集成电路分为哪几类?5.什么是特征尺寸?它对集成电路工艺有何影响?6.名词解释:集成度、wafer size、die size、摩尔定律?第1章集成电路的基本制造工艺1.四层三结的结构的双极型晶体管中隐埋层的作用?2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。

3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤?4.简述硅栅p阱CMOS的光刻步骤?5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足?6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。

7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。

8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。

第2章集成电路中的晶体管及其寄生效应1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。

2.什么是集成双极晶体管的无源寄生效应?3. 什么是MOS晶体管的有源寄生效应?4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响?5. 消除“Latch-up”效应的方法?6.如何解决MOS器件的场区寄生MOSFET效应?7. 如何解决MOS器件中的寄生双极晶体管效应?第3章集成电路中的无源元件1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些?2.集成电路中常用的电容有哪些。

3. 为什么基区薄层电阻需要修正。

4. 为什么新的工艺中要用铜布线取代铝布线。

5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。

第4章TTL电路1.名词解释电压传输特性 开门/关门电平 逻辑摆幅 过渡区宽度 输入短路电流 输入漏电流静态功耗 瞬态延迟时间 瞬态存储时间 瞬态上升时间 瞬态下降时间瞬时导通时间2. 分析四管标准TTL 与非门(稳态时)各管的工作状态?3. 在四管标准与非门中,那个管子会对瞬态特性影响最大,并分析原因以及带来那些困难。

1+X集成电路理论测试题+参考答案一、单选题(共39题,每题1分,共39分)1.元器件的引线直径与印刷焊盘孔径应有()的合理间隙。

A、0.2~0.4mmB、0.2~0.3mmC、0.1~0.4mmD、0.1~0.3mm正确答案:A2.在半自动探针台进行扎针调试时,当针尖悬于待测点上方,先调节( )旋钮。

A、X轴B、Y轴C、Z轴D、X-Y-Z微调正确答案:B答案解析:在半自动探针台上进行扎针调试时,当针尖悬于待测点上方,先用Y轴旋钮将探针退后少许,再用Z轴旋钮下针,最后用X轴旋钮。

3.点银浆时,银浆的覆盖范围需要()。

A、小于50%B、大于50%C、大于75%D、不小于90%正确答案:C答案解析:引线框架被推至点银浆指定位置后,点胶头在晶粒座预定粘着晶粒的位置点上定量的银浆(银浆覆盖范围>75%)。

4.转塔式分选机设备测试环节的流程是:( )。

A、测前光检→测后光检→测试→芯片分选B、芯片分选→测前光检→测后光检→测试C、测前光检→测试→测后光检→芯片分选D、测前光检→测后光检→芯片分选→测试正确答案:C答案解析:转塔式分选机设备测试环节的流程是:测前光检→测试→测后光检→芯片分选。

5.植球时,球和焊盘金属形成冶金结合,此时形成的焊点为()。

A、第一焊点B、第二焊点C、第三焊点D、芯片焊点正确答案:A答案解析:劈刀下降到芯片焊点表面,加大压力和功率,使球和焊盘金属形成冶金结合,形成第一焊点。

6.管装包装时,将真空包装的编带盘放入内盒、合上盖子后,需要在内盒的封口边( )处贴上“合格”标签。

A、左侧B、右侧C、中央D、任意位置正确答案:C答案解析:管装包装时,将真空包装的编带盘放入内盒、合上盖子后,需要在内盒的封口边中央处贴上“合格”标签。

7.下列关于重力式分选设备描述错误的是()。

A、装料时不需要注意芯片方向和管脚朝向B、重力式分选机手动上料的步骤分为两步,装料和上料夹具夹持C、手动装料需要操作人员取下待测料管一端的塞钉,并将料管整齐地摆放在操作台D、自动装料减少了人工补料的次数,节省了取塞钉与摆放料管的时间,降低了人工成本正确答案:A8.封装工艺中,()工序后的合格品进入塑封工序。

XXX 职业技能鉴定中心题库集成电路芯片制造工艺员 XXX 工理论知识试卷注 意 事 项 1、考试时间:120分钟。

2、请首先按要求在试卷的标封处填写您的姓名、准考证号和所在单位的名称。

3、请仔细阅读各种题目的回答要求,在规定的位置填写您的答案。

4、不要在试卷上乱写乱画,不要在标封区填写无关的内容。

1. 在扩散之前在硅表面先沉积一层杂质,在整个过程中这层杂质作为扩散的杂质源,不再有新的杂质补充,这种扩散方式称为: 恒定表面源扩散 ;2. 对标准单元设计EDA 系统而言,标准单元库应包含以下内容: 逻辑单元符号库 和 功能单元库 、 拓扑单元库 、 版图单元库 。

3. 在一个晶圆上分布着许多块集成电路,在封装时将各块集成电路切开时的切口叫划片槽 。

4. 全定制、半定制版图设计中用到的单元库包含 符号图 、 抽象图 、 线路图 和 版图 。

5. 半导体材料有两种载流子参加导电,具有两种导电类型。

一种是 电子 ,另一种是 空穴 。

6. 半导体材料可根据其性能、晶体结构、结晶程度、化学组成分类。

比较通用的则是根据其化学组成可分为 元素 半导体、 化合物 半导体、固溶半导体三大类。

7. 半导体材料的主要晶体结构有 金刚石 型、 闪锌矿型、 纤锌矿 型。

8. 抛光片的质量检测项目包括:几何参数: 直径 、 厚度 、主参考面、副参考面、平整度、 弯曲度等;电学参数 :电阻率,载流子浓度 ,迁移率等;以及晶体质量,晶向,位错密度。

9. 外延生长方法比较多,其中主要的有 化学气相 外延、 液相 外延、 金属有机化学气相 外延、 分子束 外延、 原子束 外延、 固相 外延等。

10. 离子注入是借其 动能 强行进入靶材料中的一个 非平衡 物理过程。

11. 半导体中的离子注入掺杂是把掺杂剂 离子 加速到的需要的 能量 ,直接注入到 半导体晶片 中,并经适当温度的 退火处理 。

1.12.空气中的一个小尘埃将影响整个芯片的完整性、成品率,并影响其电学性能和可靠性,所以半导体芯片制造工艺需在超净厂房内进行。

集成电路设计练习题20091、说明一个半导体集成电路成本的组成。

、说明一个半导体集成电路成本的组成。

2、简述CMOS 工艺流程。

简述CMOS 集成电路制造的过程中需要重复进行的工艺步骤。

集成电路制造的过程中需要重复进行的工艺步骤。

3、描述你对集成电路工艺的认识。

列举几种集成电路典型工艺。

工艺上常提到0.25,0.18指的是什么?简述CMOS 工艺技术的发展趋势。

工艺技术的发展趋势。

4、你知道的集成电路设计的表达方式有哪几种?、你知道的集成电路设计的表达方式有哪几种?5、现有一用户需要一种集成电路产品,要求该产品能够实现如下功能:y=lnx 其中,x 为4位二进制整数输入信号。

制整数输入信号。

y 为二进制小数输出,要求保留两位小数。

电源电压为3~5v 假设公司接到该项目后,交由你来负责该产品的设计,试讨论该产品的设计全程。

6、请谈谈对一个系统设计的总体思路。

针对这个思路,你觉得应该具备哪些方面的知识?7、描述你对集成电路设计流程的认识。

、描述你对集成电路设计流程的认识。

8、集成电路前端设计流程,后端设计流程,相关的工具。

9、从RTL synthesis 到tape out 之间的设计flow ,并列出其中各步使用的tool. 1010、简述、简述FPGA 等可编程逻辑器件设计流程。

1111、简述半定制数字电路的设计流程。

、简述半定制数字电路的设计流程。

、简述半定制数字电路的设计流程。

1212、简要说明并比较数字集成电路几种不同的实现方法。

、简要说明并比较数字集成电路几种不同的实现方法。

1313、什么是集成电路的设计规则。

、什么是集成电路的设计规则。

、什么是集成电路的设计规则。

1414、同步电路和异步电路的区别是什么?、同步电路和异步电路的区别是什么?、同步电路和异步电路的区别是什么?1515、画出、画出CMOS 电路的晶体管级电路图,实现Y=AB+C(D+E) 1616、在、在CMOS 电路中,电路中,要有一个单管作为开关管精确传递模拟低电平,要有一个单管作为开关管精确传递模拟低电平,要有一个单管作为开关管精确传递模拟低电平,这个单管你会用这个单管你会用P 管还是N 管,为什么?管,为什么?1717、硅栅、硅栅COMS 工艺中N 阱中做的是P 管还是N 管,N 阱的阱电位的连接有什么要求?阱的阱电位的连接有什么要求?1818、名词解释:、名词解释:VLSI, CMOS, EDA, VHDL, DRC, LVS, DFT, STA 1919、画出、画出CMOS 与非门的电路,并画出波形图简述其功能。

1+X集成电路理论知识试题+答案1、晶圆越大,晶圆的制造成本越高。

A、正确B、错误答案:B晶圆越大,晶圆的制造成本越低,但对材料技术和生产技术的要求更高。

2、输入引线一定要尽量短,而且尽量用最上层的金属设计,且输入输出引线尽量远离,尽量不要交叉。

A、正确B、错误答案:A3、防静电点检在刷员工上岗证时,需要站在地上保持接,身份证通过后,开始检测静电。

A、正确B、错误答案:B防静电点检时,双脚站在防静电测试仪指定位置,在刷卡位置刷员工上岗证,此时系统会对人员身份进行自动识别。

刷员工上岗证时,双脚需要站在防静电测试仪的指定位置,不能直接站在地上。

4、测试夹具的日常维护时,测试夹具若长时间不使用,请及时从设备上取下,用防静电袋包裹好,归类存放于干燥、阴凉处,以免发生氧化、受潮。

()A、正确B、错误答案:A5、晶圆研磨和晶圆切割前都需要在晶圆背面进行覆膜。

A、正确B、错误答案:B晶圆蓝膜专为晶圆研磨、切割而设计,它具有高黏着力,使晶圆在研磨、切割过程中不脱落、不飞散,从而能被确实地研磨或切割。

其中晶圆研磨是对晶圆背面进行研磨,故需要在晶圆的正面覆上蓝膜;而晶圆切割是在其正面进行切割,所以需要在晶圆的背面覆上蓝膜。

6、芯片检测工艺中,由于芯片上有印章且盖带透明,所以在编带完成后不需要在编带盘上贴小标签。

A、正确7、转塔式分选机进行测前光检时,会在光检显示区显示光检结果,其中进行方向判断时,会在界面上显示的角度360度。

A、正确B、错误答案:B转塔式分选机设备进行测前光检时,光检显示区的角度说明有:0°、90°、180°、270°,没有360°。

8、金属钨常常采用CVD法来制备。

A、正确B、错误答案:A金属钨常常采用化学气相沉积CVD法来制备。

9、晶圆具有各向异性特点,切片时要按照一定的方向进行。

A、正确B、错误答案:A10、作为与加工线之间的接口文件,制版文件主要内容包括芯片的基本信息和工艺层次等。

集成电路试题二、选择题(14分,每小题2分)1、集成运放的输入级采用差分放大电路是因为可以()。

A 减小温漂B 增大放大倍数C 提高输入电阻2、为提高集成运放的放大倍数,集成运放的中间级多采用()。

A 共射极放大电路B 共集放大电路C 共基放大电路3、现有电路:A 反相运算电路B同相运算电路 C 积分运算电路D微分运算电路 E 加法运算电路F乘方运算电路(1)欲将正弦波电压转换成二倍频电压,应选用()。

(2)欲将正弦波电压叠加上一个直流量,应选用()。

(3)欲实现Au=-100的放大电路,应选用()。

(4)欲将方波电压转换成三角波电压,应选用()。

(5)欲将方波电压转换成尖顶波电压,应选用()。

下列关于74LS245的用途,不正确的说法是()A.常用于数据锁存B.常用于数据双向传送C.常用于数据驱动D.常用于数据缓冲RS-232C标准的电气特性中数据"0"规定为()A.-3~-15VB.-5~0VC.0~+5VD.+3~+15V一、选择题;1 一个理想运放的基本条件是( )。

(a) A ud=∞ ;(b) r od=∞ ;(c) r id=0 ;(d) K CMRR=0。

2集成运放在应用中出现自激,这一般是由于下述原因之一所致( )。

(a) 退耦电容太大;(b) 分布电容太小;(c) 负载电容太大;(d) 耦合电容太大。

3 在下列几种典型的积分电路中,哪个是比较积分电路?( )。

4模拟电路的非线性应用之一是( )。

(a)比例放大;(b)求和放大;(c)积分器;(d)对数器。

5模例乘法器的应用电路之一是( )。

(a)加法器;(b)减法器;(c)整流器;(d)鉴频器。

6在下例比较器中,抗干扰能力最强的是( )。

(a)单门限比较器;(b)迟滞比较器;(c)窗口比较器;(d)三态比较器。

7在集成变换器中,属于周期性变换器的是( )。

(a)U/I变换器;(b)I/U变换器;(c)U/F变换器;(d)阻抗变换器。

集成电路设计基础(工艺、版图、流程、器件)1、什么叫Latchup,如何预防闩锁效应?(仕兰、科广试题)Q1为一纵向PNP BJT, 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;Q2是一横向的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;Rwell是nwell的寄生电阻;Rsub是substrate电阻。

以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT 处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。

当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,Latch up由此而产生。

产生Latch up 的具体原因:• 芯片一开始工作时VDD变化导致nwell和P substrate间寄生电容中产生足够的电流,当VDD变化率大到一定地步,将会引起Latch up。

• 当I/O的信号变化超出VDD-GND(VSS)的范围时,有大电流在芯片中产生,也会导致SCR的触发。

• E SD静电加压,可能会从保护电路中引入少量带电载子到well或substrate中,也会引起SCR的触发。

• 当很多的驱动器同时动作,负载过大使power和gnd突然变化,也有可能打开SCR的一个BJT。

• Well 侧面漏电流过大。

消除“Latch-up”效应的方法:版图设计时:①为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;②避免source和drain的正向偏压;③使用Guard ring: P+ ring环绕nmos并接GND;N+ ring环绕pmos并接VDD,一方面可以降低Rwell和Rsub的阻值,另一方面可阻止载流子到达BJT的基极。

半导体集成电路典型试题绪论1、什么叫半导体集成电路?【答案:】通过一系列的加工工艺,将晶体管,二极管等有源器件和电阻,电容等无源元件,按一定电路互连。

集成在一块半导体基片上。

封装在一个外壳内,执行特定的电路或系统功能。

2、按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写【答案:】小规模集成电路(SSI),中规模集成电路(MSI),大规模集成电路(VSI),超大规模集成电路(VLSI),特大规模集成电路(ULSI),巨大规模集成电路(GSI)3、按照器件类型分,半导体集成电路分为哪几类?【答案:】双极型(BJT)集成电路,单极型(MOS)集成电路,Bi-CMOS型集成电路。

4、按电路功能或信号类型分,半导体集成电路分为哪几类?【答案:】数字集成电路,模拟集成电路,数模混合集成电路。

5、什么是特征尺寸?它对集成电路工艺有何影响?【答案:】集成电路中半导体器件的最小尺寸如MOSFET的最小沟道长度。

是衡量集成电路加工和设计水平的重要标志。

它的减小使得芯片集成度的直接提高。

6、名词解释:集成度、wafer size、die size、摩尔定律?【答案:】7、分析下面的电路,指出它完成的逻辑功能,说明它和一般动态组合逻辑电路的不同,分析它的工作原理。

【答案:】该电路可以完成NAND逻辑。

与一般动态组合逻辑电路相比,它增加了一个MOS管M kp,它可以解决一般动态组合逻辑电路存在的电荷分配的问题。

对于一般的动态组合逻辑电路,在评估阶段,A=“H” B=“L”, 电荷被OUT处和A处的电荷分配,整体的阈值下降,可能导致OUT的输出错误。

该电路增加了一个MOS管M kp,在预充电阶段,M kp导通,对C点充电到V dd。

在评估阶段,M kp截至,不影响电路的正常输出。

8、延迟时间【答案:】时钟沿与输出端之间的延迟第1章集成电路的基本制造工艺1、四层三结的结构的双极型晶体管中隐埋层的作用【答案:】减小集电极串联电阻,减小寄生PNP管的影响2、在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响【答案:】电阻率过大将增大集电极串联电阻,扩大饱和压降,若过小耐压低,结电容增大,且外延时下推大3、简单叙述一下pn结隔离的NPN晶体管的光刻步骤【答案:】第一次光刻:N+隐埋层扩散孔光刻第二次光刻:P隔离扩散孔光刻第三次光刻:P型基区扩散孔光刻第四次光刻:N+发射区扩散孔光刻第五次光刻:引线孔光刻第六次光刻:反刻铝4、简述硅栅p阱CMOS的光刻步骤【答案:】P阱光刻,光刻有源区,光刻多晶硅,P+区光刻,N+区光刻,光刻接触孔,光刻铝线5、以p阱CMOS工艺为基础的BiCMOS的有哪些不足【答案:】NPN晶体管电流增益小,集电极串联电阻大,NPN管的C极只能接固定电位6、以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法【答案:】首先NPN具有较薄的基区,提高了其性能:N阱使得NPN管C极与衬底断开,可根据电路需要接任意电位。

1 第三部分集成电路测试

一、比赛要求

比赛现场下发若干块集成电路芯片、配套的焊接套件及相关技术资料(芯片手册、焊接套件清单等)。

参赛选手在规定时间内,按照相关电路原理与电子装接工艺,设计、焊接、调试集成电路功能测试工装板,完成相应测试要求,填写测试报告。

二、比赛内容

任务一:数字集成电路测试

CD4510是一种可预置数的二一十进制加/减可逆计数器,它具有加计数、减计数、预置数和清0功能。

它有3个控制端:加/减转换控制端UlD 、预置端PE 和复位端R ;有4个预置数端D1~D4;有4个输出端oi ~Q4。

另有一个进位输入端CI 和一个进位输出端Qa)。

1、开短路测试,输出高低电平测试,要求:将输出高低电平显示在上位机上。

2、芯片功能测试要求:

预置数为0101,进行一次加计数,将输出结果显示在上位机上

设置预置数为1001,进行一次加计数时,将对应的输出结果显示在上位机上。

设置预置数为0001,进行一次减计数时,将对应的输出结果显示在上位机上。

并在所有输出完成之后对计数器进行复位,将所有输出端的结果显示在上位机上 参赛选手根据以上测试条件编写测试程序,判断CD4510的功能是否正常。

任务二:模拟集成电路测试

参赛选手利用TL084芯片按照下列要求,完成测试工装板的设计及装配,要求如下:

(1)共模抑制比,输入失调电压。

(2)根据给定要求和提供的元器件,

完成运算放大器应用电路设计及装配,。

第三部分集成电路测试

一、比赛要求

比赛现场下发若干块集成电路芯片、配套的焊接套件及相关技术资料(芯片手册、焊接套件清单等)。

参赛选手在规定时间内,按照相关电路原理与电子装接工艺,设计、焊接、调试集成电路功能测试工装板,完成相应测试要求,填写测试报告。

二、比赛内容

任务一:数字集成电路测试

74LS373是三态输出的八D锁存器。

373 的输出端Q0~Q7 可直接与总线相连。

当锁存允许端LE为高电平时,Q 随数据D而变。

(1)开短路测试,要求:对地开路测试电流设为-100uA。

(2)噪声容限测试。

(3)芯片功能测试要求:并对输入端输入的10101010进行锁存显示。

1。