(整理)PNP双极型晶体管的设计.

- 格式:doc

- 大小:999.50 KB

- 文档页数:30

双极型晶体管设置静态工作点的方法解释说明1. 引言1.1 概述双极型晶体管作为一种重要的电子元件,广泛应用于各种电子设备中。

在实际应用中,为了保证晶体管的正常工作和性能稳定,我们需要设置静态工作点。

静态工作点是指晶体管在无输入信号时的直流偏置点,是确保晶体管处于最佳工作状态的重要参数之一。

本文将介绍双极型晶体管的工作原理,并详细解释常用的设置静态工作点的方法。

1.2 文章结构本文分为五个部分。

首先,在引言部分,我们将简要介绍文章的背景和目的。

其次,在第二部分,我们将深入探讨双极型晶体管的工作原理,包括NPN型和PNP 型晶体管区别以及其基本特性。

然后,在第三部分,我们将阐述静态工作点的重要性,并讨论定义与意义、影响因素及测量方法以及设计目标与要求。

接下来,在第四部分,我们将详细介绍设置静态工作点的三种常见方法:固定偏置电流法、自动偏置电流法(负反馈法)以及温度稳定法及其他方法。

最后,在第五部分,我们将总结本文的主要内容,并展望未来可能的研究方向。

1.3 目的本文的目的是通过对双极型晶体管设置静态工作点方法的解释说明,使读者更加深入地了解双极型晶体管的工作原理及其重要性。

同时,我们希望能够为相关领域的研究和应用提供参考和借鉴,促进技术发展和创新。

总之,通过本文的阐述,读者将能够全面了解双极型晶体管设置静态工作点的方法及其在电子设备中的应用意义。

2. 双极型晶体管工作原理:2.1 简介双极型晶体管:双极型晶体管是一种三端半导体器件,由三个区域组成:基区(Base Region)、发射区(Emitter Region)和集电区(Collector Region)。

根据接入方式的不同,双极型晶体管可以分为NPN型和PNP型两种类型。

2.2 NPN型和PNP型晶体管区别:NPN型和PNP型晶体管的主要区别在于材料的选择和掺杂方式。

对于NPN型晶体管,基区是由P型材料构成,而发射区为N型材料;PNP型晶体管则相反,基区是由N型材料构成,发射区为P型材料。

《晶体管电路设计(上)》一、晶体管基础知识1. 晶体管的分类与结构晶体管是一种半导体器件,按照结构和工作原理的不同,可分为两大类:双极型晶体管(BJT)和场效应晶体管(FET)。

双极型晶体管包括NPN型和PNP型,而场效应晶体管主要包括增强型MOS管和结型场效应管。

2. 晶体管的工作原理(1)双极型晶体管(BJT)工作原理:当在基极与发射极之间施加适当的正向电压,基区内的少数载流子会增多,导致集电极与发射极之间的电流增大,从而实现放大作用。

(2)场效应晶体管(FET)工作原理:通过改变栅极电压,控制源极与漏极之间的导电通道,实现电流的放大。

3. 晶体管的特性参数(1)直流参数:包括饱和压降、截止电流、放大系数等。

(2)交流参数:包括截止频率、增益带宽积、输入输出阻抗等。

二、晶体管放大电路设计1. 放大电路的基本类型(1)反相放大电路:输入信号与输出信号相位相反。

(2)同相放大电路:输入信号与输出信号相位相同。

(3)电压跟随器:输出电压与输入电压基本相等。

2. 放大电路的设计步骤(1)确定电路类型:根据实际需求选择合适的放大电路类型。

(2)选择晶体管:根据电路要求,选取合适的晶体管型号。

(3)计算电路参数:包括偏置电阻、负载电阻、耦合电容等。

(4)电路仿真与调试:利用电路仿真软件进行仿真,并根据实际效果调整电路参数。

三、晶体管开关电路设计1. 开关电路的基本原理晶体管开关电路利用晶体管的截止和饱和状态,实现电路的通断控制。

当晶体管处于截止状态时,开关断开;当晶体管处于饱和状态时,开关闭合。

2. 开关电路的设计要点(1)选择合适的晶体管:确保晶体管在截止和饱和状态下都能满足电路要求。

(2)优化电路参数:合理设置驱动电流、开关速度等参数,以提高开关电路的性能。

(3)考虑开关损耗:在设计过程中,尽量降低开关过程中的能量损耗,提高电路效率。

《晶体管电路设计(上)》四、晶体管稳压电路设计1. 稳压电路的作用与分类稳压电路的主要作用是保证输出电压在一定范围内稳定不变,不受输入电压和负载变化的影响。

npn双极型晶体管的结构[PNP双极型晶体管的结构]晶体管是一种主要用于放大、开关和调节电流的半导体器件。

其中,双极型晶体管是最常用的一种类型。

双极型晶体管分为NPN型和PNP型两种,本文将以PNP型双极型晶体管为例,详细介绍其结构和工作原理。

第一部分:晶体管的构造PNP型双极型晶体管由三个不同掺杂的半导体材料组成:N型半导体(N 区)、P型半导体(P区)和再次掺杂的N型半导体(N区)。

下面将详细介绍每个区域及其构造。

1. P区:P区是PNP晶体管的基区,也称为P型基底区。

它是P型半导体材料,通过硼或镓的掺杂来实现。

基区通常具有较高的电阻,确保电流在其内部流过时发生变化。

2. N区:N区是PNP晶体管的发射极和集电极,也称为N型射极和N型集电区。

它是由砷或磷等杂质掺杂的N型半导体材料构成。

在N区的两侧有两个N型电极,分别称为射极和集电极。

3. N区:PNP晶体管的基区和发射极之间还有一块N型区域,称为N型基区(小基区)。

它的作用是形成一个PN结,控制电流的流动。

第二部分:晶体管的工作原理PNP双极型晶体管主要通过控制基区中P-N结的极化状态来控制电流的流动。

下面将详细介绍三种工作状态:截止状态、饱和状态和放大状态。

1. 截止状态:当没有输入信号时,基区的P-N结处于正向偏置状态,射极和基区之间没有电流流动。

此时,晶体管处于截止状态,无法传导电流。

2. 饱和状态:当有足够的输入信号通过基极与射极之间的电阻分配器流过时,基区的P-N结会逆向偏置,此时电流可流经射极。

这使得整个晶体管处于饱和状态,并使得电流流过集电极。

3. 放大状态:当输入信号较小时,基极电流较小,无法逆向偏置基区的P-N结。

在这种情况下,晶体管处于放大状态。

基区中的小电流通过P-N 结并通过整个晶体管流过,放大为集电极电流。

第三部分:晶体管的应用PNP型双极型晶体管由于其结构特性和功能,广泛应用于各种电子设备中。

其主要应用包括放大电路、开关电路和稳压电路等。

双极型晶体管和三极管双极型晶体管(Bipolar Junction Transistor,BJT)和三极管(Field-Effect Transistor,FET)都是广泛用于电子设备中的半导体器件,用于放大电信号、开关电路和其他电子应用。

它们在工作原理和结构上有一些显著的差异。

双极型晶体管(BJT):结构:BJT有三个区域,分别是发射极(Emitter)、基极(Base)和集电极(Collector)。

BJT主要分为NPN型和PNP型两种。

工作原理:BJT的工作基于少数载流子在不同区域的运动。

在NPN型BJT 中,电流由发射极注入基极,再由基极注入集电极。

在PNP型中则相反。

这种少数载流子的注入和扩散导致了电流的放大。

放大特性:BJT可以提供较高的电流放大,适用于放大信号的应用。

它的输出特性受到输入信号的影响,因此是一种双极性的放大器。

三极管(FET):结构:FET有源极(Source)、栅极(Gate)和漏极(Drain)三个区域。

主要分为N型场效应晶体管(N-channel FET)和P型场效应晶体管(P-channel FET)。

工作原理:FET的工作基于电场效应。

通过调节栅极电压,可以控制源漏间的电流。

在N-channel FET中,电子在源漏之间移动;在P-channel FET中,空穴在源漏之间移动。

放大特性:FET对输入信号的响应主要取决于电场控制,因此它在放大信号时不受输入信号的影响,是一种单极性放大器。

比较:电流控制vs 电场控制:BJT是电流控制器,其输出电流受到输入电流的控制。

而FET是电场控制器,其输出电流受到输入电压的影响。

放大类型:BJT是双极型放大器,对正负信号都能放大。

FET是单极型放大器,主要放大正信号或负信号。

输入电阻:BJT的输入电阻相对较低,而FET的输入电阻相对较高。

应用:BJT广泛用于模拟电路、功率放大器等领域,而FET在数字电路、高频应用等方面更为常见。

pnp中功率晶体管

PNP(正-负-正)型功率晶体管是一种常见的双极型晶体管,用于放大和控制电流。

它由P型半导体、N型半导体和P型半导体三层结构组成。

PNP型功率晶体管通常用于低至中功率的放大和开关电路中。

首先,让我们从结构和工作原理的角度来看。

PNP型功率普通晶体管的结构由两个P型半导体夹一个N型半导体组成。

当正极电压施加在基极上时,它将吸引N型区的自由电子,从而形成一个电流从集电极到发射极。

这种电流控制机制使得PNP型功率晶体管可以用作放大器或开关。

其次,我们可以从应用领域来探讨。

PNP型功率晶体管通常用于电源管理、电机驱动、音频放大和各种电子设备中。

例如,它们可以用于电源逆变器、音频放大器和开关电源等应用。

此外,让我们从优点和缺点的角度来分析。

PNP型功率晶体管的优点包括较高的开关速度、较低的饱和压降和较高的工作温度。

然而,它们也存在一些缺点,如较低的电流增益和较高的噪声。

最后,我们可以讨论一下PNP型功率晶体管的未来发展趋势。

随着电子技术的不断发展,PNP型功率晶体管可能会在集成电路、

功率电子设备和新能源领域等方面得到更广泛的应用,同时也可能

会不断改进其性能和特性,以满足不断变化的市场需求。

总的来说,PNP型功率晶体管在电子领域中扮演着重要的角色,它们的结构、工作原理、应用领域、优缺点以及未来发展趋势都是

我们需要全面了解的内容。

希望这些信息能够帮助你更好地理解

PNP型功率晶体管。

双极型晶体管bpt

【实用版】

目录

1.双极型晶体管的概念与结构

2.双极型晶体管的工作原理

3.双极型晶体管的基本放大电路

4.双极型晶体管的特点与应用

正文

双极型晶体管(Bipolar Transistor)是一种三极管,由两个背靠背的 p-n 结构组成,用于获得电压、电流或信号增益。

它主要有三个区域:发射区、基区和集电区。

双极型晶体管可以分为 npn 型和 pnp 型两种类型。

双极型晶体管的工作原理主要包括放大和开关两个方面。

在放大状态时,通过改变基极电流,可以控制集电极电流,实现信号的放大。

在开关状态时,双极型晶体管可以处于截止或者饱和状态,相当于开关的断开或者闭合。

双极型晶体管的基本放大电路主要包括共发射极放大电路、共基极放大电路和共集极放大电路。

其中,共发射极放大电路是最常见的一种,通过调整电阻可以实现对电压、电流的放大。

双极型晶体管具有一些独特的特点,例如:它具有较大的电流增益,可以承受较高的功率,同时也有较好的温度稳定性。

因此,双极型晶体管广泛应用于低频放大、开关和调制等电路中。

然而,双极型晶体管也存在一些缺点,例如:它的输入电阻较低,输出电阻较高,导致信号在传输过程中会有较大的损失。

此外,双极型晶体管的制造工艺较为复杂,也限制了它的应用范围。

总的来说,双极型晶体管是一种重要的半导体器件,它在电子技术中有着广泛的应用。

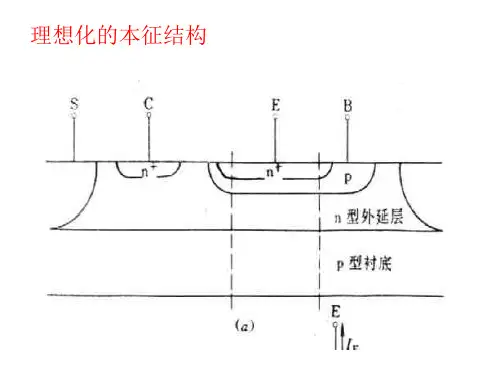

目录1.课程设计目的与任务 (2)2.设计的内容 (2)3.设计的要求与数据 (2)4.物理参数设计 (3)4.1 各区掺杂浓度及相关参数的计算 (3)4.2 集电区厚度Wc的选择 (6)4.3 基区宽度WB (6)4.4 扩散结深 (10)4.5 芯片厚度和质量 (10)4.6 晶体管的横向设计、结构参数的选择 (10)5.工艺参数设计 (11)5.1 工艺部分杂质参数 (11)5.2 基区相关参数的计算过程 (11)5.3 发射区相关参数的计算过程 (13)5.4 氧化时间的计算 (14)6.设计参数总结 (16)7.工艺流程图 (17)8.生产工艺流程 (19)9.版图 (28)10.心得体会 (29)11.参考文献 (30)PNP 双极型晶体管的设计1、课程设计目的与任务《微电子器件与工艺课程设计》是继《微电子器件物理》、《微电子器件工艺》和《半导体物理》理论课之后开出的有关微电子器件和工艺知识的综合应用的课程,使我们系统的掌握半导体器件,集成电路,半导体材料及工艺的有关知识的必不可少的重要环节。

目的是使我们在熟悉晶体管基本理论和制造工艺的基础上,掌握晶体管的设计方法。

要求我们根据给定的晶体管电学参数的设计指标,完成晶体管的纵向结构参数设计→晶体管的图形结构设计→材料参数的选取和设计→制定实施工艺方案→晶体管各参数的检测方法等设计过程的训练,为从事微电子器件设计、集成电路设计打下必要的基础。

2、设计的内容设计一个均匀掺杂的pnp 型双极晶体管,使T=300K 时,β=120,V CEO =15V,V CBO =80V.晶体管工作于小注入条件下,最大集电极电流为I C =5mA 。

设计时应尽量减小基区宽度调制效应的影响。

3、设计的要求与数据(1)了解晶体管设计的一般步骤和设计原则。

(2)根据设计指标设计材料参数,包括发射区、基区和集电区掺杂浓度N E , N B , 和N C ,根据各区的掺杂浓度确定少子的扩散系数,迁移率,扩散长度和寿命 等。

(3)根据主要参数的设计指标确定器件的纵向结构参数,包括集电区厚度W c , 基本宽度W b ,发射区宽度W e 和扩散结深X jc ,发射结结深X je 等。

(4)根据扩散结深X jc ,发射结结深X je 等确定基区和发射区预扩散和再扩散的扩 散温度和扩散时间;由扩散时间确定氧化层的氧化温度、氧化厚度和氧化 时间。

(5)根据设计指标确定器件的图形结构,设计器件的图形尺寸,绘制出基区、 发射区和金属接触孔的光刻版图。

(6)根据现有工艺条件,制定详细的工艺实施方案。

4、物理参数设计4.1 各区掺杂浓度及相关参数的计算击穿电压主要由集电区电阻率决定。

因此,集电区电阻率的最小值由击穿电压决定,在满足击穿电压要求的前提下,尽量降低电阻率,并适当调整其他参量,以满足其他电学参数的要求。

对于击穿电压较高的器件,在接近雪崩击穿时,集电结空间电荷区已扩展至均匀掺杂的外延层。

因此,当集电结上的偏置电压接近击穿电压V 时,集电结可用突变结近似,对于Si 器件击穿电压为4313106-⨯=)(BC B N V , 由此可得集电区杂质浓度为:34133413)1106106CEOn CBOC BV BV N β+⨯=⨯=()(由设计的要求可知C-B 结的击穿电压为: V BV CBO 80= 根据公式,可算出集电区杂质浓度:3153413341310814.6)80106106-⨯=⨯=⨯=cm BV N CBO C ()(一般的晶体管各区的浓度要满足NE>>NB>NC ,根据以往的经验可取:B EC B N N N N 100,10==即各区的杂质溶度为:31831631510814.610814.610814.6---⨯=⨯=⨯=cm N cm N cm N E B C ,,图1 室温下载流子迁移率与掺杂浓度的函数关系(器件物理P55)根据图1,得到少子迁移率:s V cm ⋅==/13002n C μμ s V cm P B ⋅==/3302μμ s V cm N E ⋅==/1502μμ根据公式可得少子的扩散系数:scm q kT D scm q kT D s cm q kTD E E B B C C /90.3150026.0/58.8330026.0/8.331300026.0222=⨯===⨯===⨯==μμμ图2 掺杂浓度与电阻率的函数关系(器件物理P59)根据图2,可得到不同杂质浓度对应的电阻率:cm C ⋅Ω=17.1ρ cm B ⋅Ω=1.0ρ cm E ⋅Ω=014.0ρ图3 少子寿命与掺杂浓度的函数关系(半导体物理P177)根据图3,可得到各区的少子寿命E B C τττ和、sC 6105.3-⨯=τ s B 7109-⨯=τs E 6101.1-⨯=τ根据公式得出少子的扩散长度:cmD L cmD L cm D LE E E B B B C C C 3637261007.2101.190.31078.2100.958.81009.1105.38.33------⨯≈⨯⨯==⨯≈⨯⨯==⨯≈⨯⨯==τττ4.2 集电区厚度Wc 的选择根据公式求出集电区厚度的最小值为:um 91.3101.39]10814.6106.1808.111085.82[]2[521151914210=⨯≈⨯⨯⨯⨯⨯⨯⨯==〉---cm qN BV X W C CBO S mBC εεW C 的最大值受串联电阻r cs 的限制。

增大集电区厚度会使串联电阻r cs 增加,饱和压降V CES 增大,因此W C 的最大值受串联电阻限制。

综合考虑这两方面的因素,故选择W C =8μm 4.3 基区宽度WB (1)基区宽度的最大值对于低频管,与基区宽度有关的主要电学参数是,因此低频器件的基区宽度最大值由确定。

当发射效率γ≈1时,电流放大系数][122nbB L W λβ=,因此基区宽度的最大值可按下式估计:212][βλnb B L W <为了使器件进入大电流状态时,电流放大系数仍能满足要求,因而设计过程中取λ=4。

根据公式,求得低频管的基区宽度的最大值为:()um08.51008.51201078.24][423212mas =⨯≈⨯⨯==--cm L W nb B βλ,由公式可看出,电流放大系数β要求愈高,则基区宽度愈窄。

为提高二次击穿耐量,在满足β要求的前提下,可以将基区宽度选的宽一些,使电流在传输过程中逐渐分散开,以提高二次击穿耐性。

(2)基区宽度的最小值为了保证器件正常工作,在正常工作电压下基区绝对不能穿通。

因此,对于高耐压器件,基区宽度的最小值由基区穿通电压决定,此处V BV CBO 80=,对于均匀基区晶体管,当集电结电压接近雪崩击穿时,基区一侧的耗尽层宽度为:()()um373.010373.0]8010814.610814.610814.610814.6106.11085.88.112[]2[]2[421151615161914210210min ,=⨯≈⨯⨯+⨯⨯⨯⨯⨯⨯⨯⨯⨯=+=+=---cm BV N N N qN BV N N N qN X CBO C B C B S CBO A D AD S B εεεε 在高频器件中,基区宽度的最小值往往还受工艺的限制。

则由上述计算可知基区的范围为:m W m B μμ08.5373.0<<(3)基区宽度的具体设计与PN 结二极管的分析类似,在平衡和标准工作条件下,BJT 可以看成是由两个独立的PN 结构成,它在平衡时的结构图如下所示:图4 平衡条件下的PNP 三极管的示意图具体来说,由于B E N N >>,所以E-B 耗尽区宽度(EB W )可近视看作全部位于基区内,又由C B N N >,得到大多数C-B 耗尽区宽度(CB W )位于集电区内。

因为C-B 结轻掺杂一侧的掺杂浓度比E-B 结轻掺杂一侧的浓度低,所以CB W >EB W 。

另外注意到B W 是基区宽度,W 是基区中准中性基区宽度;也就是说,对于PNP 晶体管,有:nCB nEB B x x W W ++=其中nEB x 和nCB x 分别是位于N 型区内的E-B 和C-B 耗尽区宽度,在BJT 分析中W 指的就是准中性基区宽度。

E-B 结的内建电势为:V n N N q kT V i B E biEB938.0)10(10814.610814.6ln 026.0ln 21016182=⨯⨯⨯⨯== C-B 结的内建电势为:V n N N q kT V i B C biCB758.0)10(10814.610814.6ln 026.0ln 21016152=⨯⨯⨯⨯== 根据公式,E-B 结在基区一边的耗尽层宽度nEB x 为: ∵B E N N >> ,可以当成单边突变结处理()2121022⎥⎦⎤⎢⎣⎡≈⎥⎦⎤⎢⎣⎡+=biEB B o s biEB B E B ES nEB V qN K V N N N N q K X εεum 134.01034.110814.6106.1938.01085.88.112521161914=⨯≈⎥⎦⎤⎢⎣⎡⨯⨯⨯⨯⨯⨯⨯=---cmC-B 结在基区一边的耗尽层厚度nCB x 为:()210)-(2⎥⎦⎤⎢⎣⎡+=CB biEB B C B CS nCB V V N N N N q K X ε0W n n =--=CB EB B X X W ,则穿通时有()()V N N N N q K X WV V B C B CS EB B CB CB242.1444614447758.02-02n max ,bi -=-=+-=⇒εCBO CB V V >>则 ()2102⎥⎦⎤⎢⎣⎡+=biEB B C B C S nCBV N N N N q K X ε所以有()um0363.010363.0758.010814.610814.610814.610814.6106.11085.88.112521161516151914=⨯≈⎥⎦⎤⎢⎣⎡⨯⨯+⨯⨯⨯⨯⨯⨯⨯⨯⨯=---cm对于准中性基区宽度W ,取基区宽度um 5.3=B W ,则 um X X W W CB EB B 33.30363.0-134.0-5.3n n ==--= 验证其取值的准确性,根据公式有:2211⎪⎪⎭⎫⎝⎛+=B E E B B E dc L W L W N N D D β1261078.21033.3211007.21033.310814.610814.658.89.31234341816≈⎪⎪⎭⎫ ⎝⎛⨯⨯⨯+⨯⨯⨯⨯⨯⨯=----解得的β接近于设计的要求,符合设计指标,所以基区宽度为m W B μ5.3=, 满足条件m W m B μμ08.5373.0<<。