简易数字逻辑分析仪的程序设计.

- 格式:ppt

- 大小:1.51 MB

- 文档页数:10

2008年10月第10期电子测试EL ECTRONIC TEST Oct.2008No.10简易逻辑分析仪设计贾 奕,黄劲松,沈鹏程,田开坤(1湖北师范学院物理与电子科学学院 黄石 4350022湖北师范学院电工电子实验教学示范中心 黄石 435002) 摘 要:本系统是以STC89C52单片机和复杂可编程逻辑器件CPLD 的组合电路为核心,利用锁存器在时钟上升沿将输入端的数据锁存的原理,构建了一个基于实时采样和直接数据存储器存储(DMA )的简易逻辑分析仪。

系统由五部分组成:按键模块、CPLD 模块、DDS 采样时钟发生模块、L CD 显示模块、DMA 数据采集模块。

相比于市场上的逻辑分析仪,本系统结构简单,易制作,成本低,可同时测量8路T TL 信号。

本系统可以用来分析数字逻辑电路中的时序逻辑关系,本文还用该逻辑分析仪研究了51单片机对外部地址读写操作的时序,得到与单片机数据手册一致的波形时序图。

关键词:逻辑分析仪;DMA ;CPLD ;DDS 中图分类号:TP399 文献标识码:BDesign of simple logic analyzerJia Y i ,Huang Jinsong ,Shen Pengcheng ,Tian Kaikun(1College of Physics and Electronic Science ,Hubei Normal University ,Huangshi 435002,China ;2Electricaland Electronic experimental teaching centres of excellence ,Hubei Normal University ,Huangshi 4350020,China )Abstract :A simple logic analyzer based on a real 2time sampling and DMA has been designed by using STC89C52SCM and CPLD circuit as t he p rimary component s.It operates by a latch which can latch t he data coming from t he inp ut port o n t he outp ut port by means of latching t he rising edge of a clock p ulse.The system includes five basic component s :a button control mod 2ule ,t he CPLD module ,a DDS sampling clock p ulse generation module ,an L CD module ,and t he DMA pared to t he existing logic analyzer ,t he system can measure synchro 2nously 8T TL signals ,and t he circuit is simple and can be constructed easily wit h low cost s.The system can be used as a tool t hat measures t he logic relations of t he digital circuit.An ex 2ample has been given t hat shows how t he time is measured when a 51SCM reads or writes so me data to t he o ut side address ,SCM manual data are consistent wit h t he wave timing map.K eyw ords :logic analyzer ;DMA ;CPLD ;DDS测试工具与解决方案2008.100 引 言在数字电路的研究中,往往要对电路的时序进行分析,在这种情况下,很多学生或工程师通常会选择示波器,而忽略了逻辑分析仪。

本科生毕业设计报告学院物理与电子工程学院专业电子信息工程设计题目:基于51单片机的简易逻辑分析仪设计学生姓名指导教师(姓名及职称)班级学号完成日期:年月基于51单片机的简易逻辑分析仪设计物理与电子工程学院电子信息工程[摘要]本设计完成了一种能进行数字电路中多路数据测试的简易逻辑分析仪。

它以51单片机控制核心,数模转换器为逻辑信号门限电平控制电路,用按键和 12864LCD作为人机交互界面,采用C51进行模块化编程,实现了四路信号的测试,具有成本低,使用方便等特点。

[关键词]数字电路单片机数模转换器逻辑分析仪1 设计任务与要求本设计的主要任务及参数指标是:数据位数4位,存储深度80字;数据速率最高1kHz;输入阻抗大于50kΩ;逻辑信号门限电平在1.0V~4.0V 范围内按8级任意设定。

2 设计方案本系统采用51单片机为控制核心,系统由单片机系统、逻辑电平控制、按键、LCD显示、系统电源等模块构成。

被测数据输入到逻辑电平控制模块,然后进行单片机进行测试,按键用于控制逻辑信号门限电平的大小,系统电源为各模块供电,各模块的供电电压为5V。

图1 系统框图3 设计原理分析3.1 单片机系统电路设计图2 单片机系统电路单片机系统为逻辑分析仪的核心,负责控制逻辑分析仪的逻辑电平、检测按键并驱动LCD 进行显示。

单片机系统电路如图2所示,由晶体振荡器Y1、电容C3和C4构成振荡器电路,为单片机提供时钟信号。

电容C1、电阻R2和R1、按键KEY1构成单片机复位电路,高电平复位,当按键KEY1按下的时间超过2个机器周期以上时,单片机就执行复位操作。

EA 接高电平,单片机首先访问内部程序存储器。

J1为1KΩ的排阻,作为P0口的外部上拉电阻。

在硬件制作时为了方便单片机的测试和功能的扩展,把所有的I/O 口均通过排针引出。

EA/VP 31X119X218RESET 9RD 17WR 16INT012INT113T014T115P101P112P123P134P145P156P167P178P0039P0138P0237P0336P0435P0534P0633P0732P2021P2122P2223P2324P2425P2526P2627P2728PSEN29ALE/P 30TXD 11RXD 10U1P10P11P12P13P14P15P16P17P00P01P02P03P04P05P06P07P20P21P22P23P24P25P26P27123456789J11KY112M+5RXD TXDRD WRT0T1INT0INT1C322p FC422p FR28.2KC110u F+512J6CON2KEY1SW2R1100..3.2 人机界面电路设计..图3 按键控制电路按键控制电路如图3所示,用于控制逻辑分析仪的工作状态,如采样率改变、逻辑电平的调整等等,单片机通过检测按键对应的I/O 口是否为低电平来判断按键是否按键,为了防止干扰,应在单片机的按键检测程序中加入延时函数。

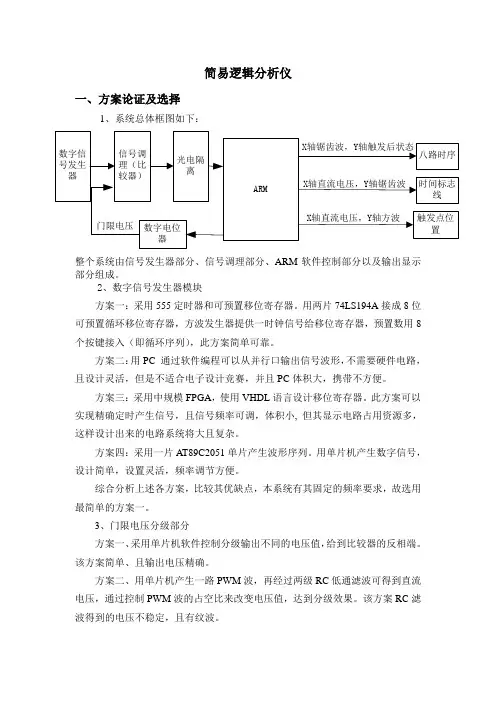

简易逻辑分析仪一、方案论证及选择1、系统总体框图如下:整个系统由信号发生器部分、信号调理部分、ARM软件控制部分以及输出显示部分组成。

2、数字信号发生器模块方案一:采用555定时器和可预置移位寄存器。

用两片74LS194A接成8位可预置循环移位寄存器,方波发生器提供一时钟信号给移位寄存器,预置数用8个按键接入(即循环序列),此方案简单可靠。

方案二:用PC 通过软件编程可以从并行口输出信号波形,不需要硬件电路,且设计灵活,但是不适合电子设计竞赛,并且PC体积大,携带不方便。

方案三:采用中规模FPGA,使用VHDL语言设计移位寄存器。

此方案可以实现精确定时产生信号,且信号频率可调,体积小, 但其显示电路占用资源多,这样设计出来的电路系统将大且复杂。

方案四:采用一片AT89C2051单片产生波形序列。

用单片机产生数字信号,设计简单,设置灵活,频率调节方便。

综合分析上述各方案,比较其优缺点,本系统有其固定的频率要求,故选用最简单的方案一。

3、门限电压分级部分方案一、采用单片机软件控制分级输出不同的电压值,给到比较器的反相端。

该方案简单、且输出电压精确。

方案二、用单片机产生一路PWM波,再经过两级RC低通滤波可得到直流电压,通过控制PWM波的占空比来改变电压值,达到分级效果。

该方案RC滤波得到的电压不稳定,且有纹波。

方案三、直流电源供5V电压,采用电阻、电位器进行一级一级的分压,以实现分级效果。

该方案电路复杂,且电位器调节比较难。

方案四、采用数字式电位器,由单片机结合相应的外围电路进行控制,以实现分压。

采用程控方式,得到的电压精确且稳定。

鉴于本系统软件程序较多,ARM内部仅两个DA,故选择方案四以避免使用单片机内部DA。

二、硬件部分单元电路1、数字信号发生器电路该部分采用了555定时器产生一定频率的时钟信号,通过改变滑动变阻器阻值可实现频率在一定范围内可变,定时器后接一个非门以增强后级驱动能力。

定时器产生的方波信号作为双向移位寄存器74LS194的输入时钟,利用74LS194的两个控制端(S0,S1)来产生八路可预置的循环移位逻辑信号序列。

简易逻辑分析仪设计报告1.引言1.1 概述概述:简易逻辑分析仪是一种用于检测数字电路中逻辑信号的仪器,能够实时监测和分析数字电路中的信号波形和逻辑状态。

本设计报告将介绍一种基于FPGA的简易逻辑分析仪的设计方案,包括其设计原理、硬件设计和软件设计。

通过该设计,可以实现对数字电路中逻辑信号的实时观测和分析,为数字电路的调试和优化提供有力支持。

本报告将详细介绍该简易逻辑分析仪的设计过程和实现原理,以及展望未来在数字电路测试领域的应用前景。

1.2文章结构文章结构部分的内容应该是对整篇文章的结构进行简要概括,包括各个章节的主要内容和重点讨论的部分。

可以按照下面的内容编写:文章结构部分:本文主要包括三个部分,即引言、正文和结论。

在引言部分,将对简易逻辑分析仪的概述、文章结构和研究目的进行介绍。

正文部分包括设计原理、硬件设计和软件设计三个方面的内容,其中设计原理将解析简易逻辑分析仪的工作原理,硬件设计将详细介绍分析仪的硬件组成和设计要点,软件设计则会讨论分析仪的相关软件开发情况。

在结论部分,将对整个设计报告的结果进行总结、设计的优点进行分析,并对未来的发展进行展望。

整篇文章的结构清晰,内容充实,将全面展示简易逻辑分析仪的设计过程和成果。

1.3 目的本报告的目的是设计一种简易逻辑分析仪,用于对数字逻辑电路进行分析和测试。

通过该逻辑分析仪,可以实现对逻辑电路中信号的捕获、显示和分析,从而帮助工程师和技术人员更好地理解和调试数字电路。

同时,设计该逻辑分析仪旨在提高测试效率、降低成本,并且具有一定的实用性和推广性。

基于以上目的,本报告将从设计原理、硬件设计和软件设计三个方面展开介绍和分析。

2.正文2.1 设计原理设计原理部分的内容应该包括对逻辑分析仪的工作原理进行详细介绍。

这包括逻辑分析仪的基本功能和原理,例如数据采集、信号分析和显示等。

此外,还应该介绍如何通过逻辑分析仪实现对数字信号的采集、存储和分析,以及逻辑分析仪的工作流程和主要原理。

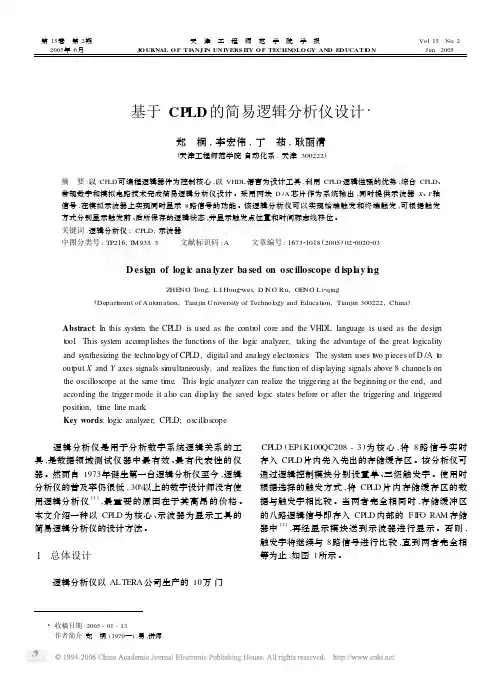

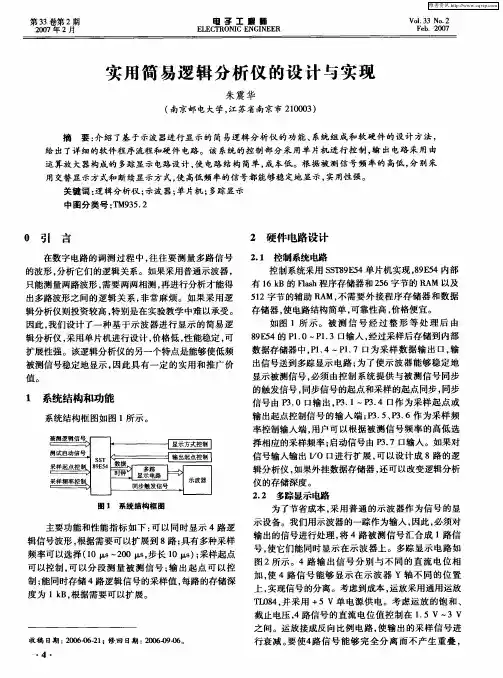

第15卷 第2期2005年6月天 津 工 程 师 范 学 院 学 报JO URNAL O F T I ANJ I N UN I VERS I TY O F TECHNOLO GY AND ED UCAT I O N Vol .15 No .2Jun .2005基于CP LD 的简易逻辑分析仪设计3郑 桐,李宏伟,丁 茹,耿丽清(天津工程师范学院自动化系,天津300222)摘 要:以CP LD 可编程逻辑器件为控制核心,以VHDL 语言为设计工具,利用CP LD 逻辑性强的优势,综合CP LD 、常规数字和模拟电路技术完成简易逻辑分析仪设计。

采用两块D /A 芯片作为系统输出,同时提供示波器X 、Y 轴信号,在模拟示波器上实现同时显示8路信号的功能。

该逻辑分析仪可以实现始端触发和终端触发,可根据触发方式分别显示触发前、后所保存的逻辑状态,并显示触发点位置和时间标志线移位。

关键词:逻辑分析仪;CP LD;示波器中图分类号:TP216;T M935.3 文献标识码:A 文章编号:167321018(2005)022*******D esi gn of log i c ana lyzer ba sed on osc illoscope d ispl ay i n gZHE NG T ong,L I Hong 2wei,D I N G Ru,GE NG L i 2qing(Depart m ent of Aut omati on,Tianjin University of Technol ogy and Educati on,Tianjin 300222,China )Abstract :I n this system the CP LD is used as the contr ol core and the VHDL language is used as the design t ool .This system accomp lishes the functions of the logic analyzer,taking the advantage of the great l ogicality and synthesizing the technol ogy of CPLD,digital and anal ogy electr onics .The system uses t wo p ieces of D /A to out put X and Y axes signals si multaneously,and realizes the function of dis p laying signals above 8channels on the oscilloscope at the same ti me .This logic analyzer can realize the triggering at the beginning or the end,and according the trigger mode it als o can dis p lay the saved l ogic states before or after the triggering and triggered positi on,ti me line mark .Key words :logic analyzer;CP LD;oscilloscope 逻辑分析仪是用于分析数字系统逻辑关系的工具,是数据领域测试仪器中最有效、最有代表性的仪器。

简易逻辑分析仪的设计毕业设计 [论⽂] 题⽬:简易逻辑分析仪的设计系别:电⽓与电⼦⼯程系专业:电⽓⼯程及其⾃动化姓名:学号:指导教师:平顶⼭⼯学院2008 年05 ⽉28 ⽇⽬录⽬录 (1)摘要 (2)Abstract (3)简易逻辑分析仪..................................... 错误!未定义书签。

第⼀章绪论.. (4) 1.1 选题的⽬的和意义 (4)1.2 逻辑分析仪的基本组成原理 (4)1.3 逻辑分析仪的主要技术指标及发展趋势 (6)第⼆章⽅案论证与⽐较 (7)2.1 数字信号发⽣器模块 (7)2.2 逻辑分析仪模块 (8)第三章信号发⽣器实现⽅案 (11)3.1 硬件组成 (11)3.2 软件组成 (14)第四章简易逻辑分析仪⽅案实现 (15)4.1 结构组成 (15)4.2 数据采集和存储部分 (16)4.3 逻辑状态与波形显⽰部分 (17)4.4 简易逻辑分析仪的软件流程 (23)4.5 实时波形存储与上下翻页 (24)第五章:操作说明 (26)5.1 数字信号发⽣器操作⽅法 (26)5.2 逻辑分析仪操作⽅法 (26)第六章附录 (28)第七章总结 (42)致谢 (43)摘要本系统由8位可预置的循环移位数字信号发⽣器、简易逻辑分析仪两部分组成。

循环移位数字信号发⽣器由51单⽚机控制,可以产⽣8位可预置逻辑信号序列和时钟信号波形。

其中⼀路输出电平可在0~5V 内调节。

采⽤16×2液晶显⽰各设置参数,显⽰直观,设置⽅便。

简易逻辑分析仪采⽤双单⽚机协同⼯作的⽅式:其中⼀⽚单⽚机作输⼊控制、数据存储、数据显⽰及各控制参设置;另⼀⽚单⽚机控制D/A转换器输出波形到⽰波器。

两单⽚机之间采⽤串⾏⽅式进⾏通信。

我们采⽤XY扫描⽅式的显⽰⽅法。

X轴的锯齿波信号由D/A转换器产⽣,由于要同时显⽰8路信号,所以Y轴的信号由被测信号、时标信号和参考电平相加得到,在软件配合下,可以⽐较⽅便实现8路信号的稳定显⽰,同时也可显⽰时间标志线和触发点位置。

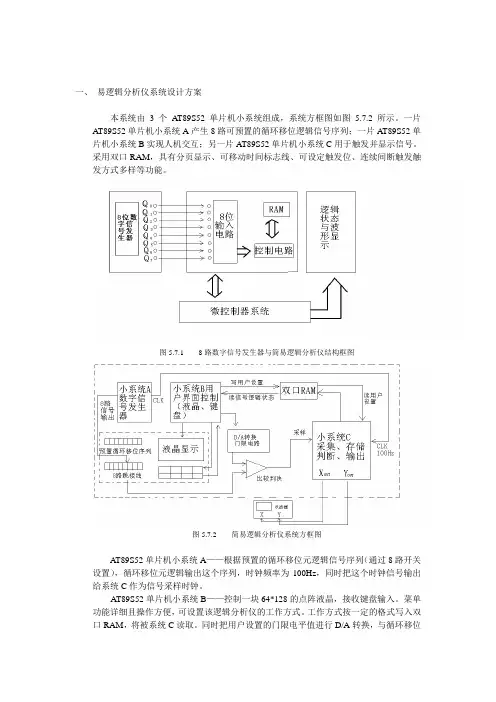

一、易逻辑分析仪系统设计方案本系统由3个AT89S52单片机小系统组成,系统方框图如图 5.7.2所示。

一片AT89S52单片机小系统A产生8路可预置的循环移位逻辑信号序列;一片A T89S52单片机小系统B实现人机交互;另一片A T89S52单片机小系统C用于触发并显示信号。

采用双口RAM,具有分页显示、可移动时间标志线、可设定触发位、连续间断触发触发方式多样等功能。

图5.7.1 8路数字信号发生器与简易逻辑分析仪结构框图图5.7.2 简易逻辑分析仪系统方框图AT89S52单片机小系统A——根据预置的循环移位元逻辑信号序列(通过8路开关设置),循环移位元逻辑输出这个序列,时钟频率为100Hz,同时把这个时钟信号输出给系统C作为信号采样时钟。

AT89S52单片机小系统B——控制一块64*128的点阵液晶,接收键盘输入。

菜单功能详细且操作方便,可设置该逻辑分析仪的工作方式。

工作方式按一定的格式写入双口RAM,将被系统C读取。

同时把用户设置的门限电平值进行D/A转换,与循环移位元逻辑输入信号相比较。

工作方式设置完毕后,可从双口RAM读时间标志线所对应时刻的8路输入信号的逻辑状态,并在液晶屏上显示。

AT89S52单片机小系统C——根据单片机A送来的100Hz信号采样时钟对比较器输出的信号序列进行采样,读取双口RAM的工作方式设置,判断触发点,向双口RAM 写时钟RAM写时钟标志线对应时刻的输入信号逻辑状态。

一、电路数字信号发生器电路设计通过8路开关设置循环移位元逻辑信号序列,输入AT89S52单片机小系统A的PI口,由89S52内部定时器在P3.7产生100HZ的时钟信号,在P3.2输出预置波形,通过移位寄存器74HC164产生8路循环移位序列信号。

8路循环移位序列信号产生电路[4]如图5.7.3所示。

移位寄存器74HC164的内部结构如图5.7.4所示。

74HC164 引脚端功能表如表5.7.1所列。

摘要逻辑分析仪是一种新型的数字测试仪器。

它应用于微机等数字系统的软件、硬件调试,故障检查,性能分析等过程中。

它可以监测硬件电路工作时的逻辑电平,并加以存储,用图形的方式直观地表达出来,便于用户检测,分析电路设计中的错误。

在数字电路调试中,往往要测试多路信号波形,分析其逻辑关系。

普通示波器最多只能测试两路信号波形,而逻辑分析仪价格较高,我们设计的简易逻辑分析仪造价低、性能高,具有一定的推广价值。

本系统采用单片机和CPLD结合的方式。

用CPLD制作信号发生和采集装置,产生8路信号及数据采集。

信号发生器的序列时钟频率可高于100HZ 。

系统触发方式具有单级触发字和三级逻辑状态分析触发功能。

其中触发字可以通过键盘任意设定,触发位置可调。

此逻辑分析仪能够在示波器上清晰稳定地显示所采集到的8路信号波形和时间标志线,并显示触发点的位置。

单片机输出可在上位机上显示,能同时看到八路信号的波形和同一时刻不同信号的逻辑状态。

系统利用单片机来完成人机界面控制,信号触发、分析、处理与变换。

8位输入电路的输入阻抗大于50kΩ,门限电压16级可调。

每通道的存储深度可达到32bit。

单片机与CPLD的结合简化了外围硬件电路的设计,增加了系统的稳定性和可靠性。

关键字单片机;CPLD;逻辑分析仪;示波器;信号发生器AbstractThe logical analyzer is one kind of new numeral measuring instrument. It applies in number system and so on the microcomputer softwares, the hardware debugging, the malfunction finding, processes and so on in performance analysis. It may monitor the hardware electric circuit to work the time logical level, and saves, expressesintuitively with the graph way, is advantageous for the user examination, analyzes in the circuit design the mistake. In the digital circuit debugging, often must test themulti-channel waveform, analyzes its logical relations. The ordinary oscilloscope are most only can test two group waveforms, but the logical analyzer price is high, we design the simple logical analyzer construction cost low, the performance is high, has certain promoted value. This system uses the monolithic integrated circuit and the CPLD union way.Manufactures the signal with CPLD to occur with the gathering installment, produces 8 groups signals and the data acquisitions. The signal generating device sequence clock frequency may be higher than 100HZ.The system triggering way has the single stage triggering character and three level of logic state analysis triggering function. Triggering character may establish willfully through the keyboard, triggers the position adjustable.This logical analyzer can on the oscilloscope stably demonstrate clearly gathers 8 group waveforms and the time scribe mark, and demonstrate the trigger point the position. The monolithic integrated circuit outputs may demonstratein on position machine that, can simultaneously see the Chinese red army soldier signal the profile and the identical time different signal logical condition. The system completes the man-machine contact surface control using the monolithic integrated circuit, signal triggering, the analysis, processing and the transformation. 8 inputcircuit input impedance is bigger than 50kΩ, threshold voltage 16 levels adjustable. Each channel memory depth may achieve 32bit.The monolithic integrated circuit and the CPLD union simplified the periphery hardware electric circuit design, increased the system stability and the reliability.Keywords Single-chip Microcomputer CPLD;Logical analyzer; Oscillograph; Signal generator目录摘要 - - - - - - - - - - - - - - - - - - - - - - - - - - -ⅠAbstract - - - - - - - - - - - - - - - - - - - - - - - - - - -Ⅱ第1章绪论 - - - - - - - - - - - - - - - - - - - - - - - - - 2第2章总体方案设计 - - - - - - - - - - - - - - - - - - - - - - 32.1 方案比较与选择 - - - - - - - - - - - - - - - - - -- - --32.2 系统设计方案 - - - - - - - - - - - - - - - - - - -- - --3第3章电路分析与设计- - - - - - - - - - - - - - - - - - - -53.1 信号发生器 - - - - - - - - - - - - - - - - - - - -- - --53.2 输入电路- - - - - - - - - - - - - - - - - - - - - - - - 63.3 采集与存储电路- - - - - - - - - - - - - - - - - - - - - 73.4 显示控制电路- - - - - - - - - - - - - - - - - - - -- - - 73.5 利用示波器显示- - - - - - - - - - - - - - - - - - -- - -93.6 电源 - - - - - - - - - - - - - - - - - - - - - -- - -103.7 示波器显示的方法- - - - - - - - - - - - - - - - -- -11第4章软件设计- - - - - - - - - - - - - - - - - - - - - - - - -13第5章系统测试分析- - - - - - - - - - - - - - - - - - -- - -155.1 测试仪器- - - - - - - - - - - - - - - - - - - - - - - - -155.2 调试方法和过程- - - - - - - - - - - - - - - - - - - - - -15结论- - - - - - - - - - - - - - - - - - - - - - - - - -- - -18致谢 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 19参考文献- - - - - - - - - - - - - - - - - - - - - - - - - - - - -20简易逻辑分析仪的设计第1章绪论在工作中只要有数字逻辑信号,就能有机会使逻辑分析仪电子化。

基于单片机的简易逻辑分析仪设计前言信息时代是数字化的时代,数字技术的高速发展,出现了以高性能计算机为核心的数字通信、数字测量的数字系统。

在研究这些数字系统产品的应用性能的同时也必须研究在设计、生产和维修他们的过程中,如何验证数字电路设计的合理性、如何协调硬件及其驱动应用软件的工作、如何测量其技术指标以及如何评价其性能。

逻辑分析仪的出现,为解决这些问题提供了可能。

随着数字系统复杂程序的增加,尤其是微处理器的高速发展,用示波器测试己显得有些无能为力。

1973年在美国应运而生的逻辑分析仪(Logic Analyzer),能满足数字域测试的各种要求。

它属于总线分析仪一类的数据域测试仪器主要用于查找总线(或多线)相关故障.同时对于数据有很强的选择能力和跟踪能力,因此,逻辑分析汉在数字系统的测试中获得了广泛的应用。

逻辑分析仪(Logic Analyzer)是以逻辑信号为分析对象的测量仪器。

是一种数据域仪器,其作用相当于时域测量中的示波器。

正如在模拟电路错误分析中需要示波器一样,在数字电路故障分析中也需要一种仪器,它适应了数字化技术的要求,是数字、逻辑电路、仪器、设备的设计、分析及故障诊断工作中不可按少的工具。

在测试数字电路、研制和维修电子计算机、微处理器以及各种集成化数字仪表和装置中具有广泛的用途;还是数字系统设计、侦错、软件开发和仿真的必备仪器;作为硬件设计中必不可少的检测工具,还可将其引入实验教学中,建立直观感性的印象,提升学生的硬件设计能力,可以全面提高教学质量;随着科技的发展,LA在多通道、大存储量、高采样速率、多触发功能方面得到更快的发展,在航天、军事、通信等数字系统领域得到越来越广泛的应用。

我们从上面可以看出逻辑分析仪在各个领域的广泛应用。

那么我们在学习、应用的同时设计并制作一个简易的逻辑分析仪就显的意义重大了,这样这个过程既可以让我们更加深入理解其原理,又可以提高动手设计并制作整个系统电路的能力,还可以将其作为简易仪器应用于以后的实验中。

简易逻辑分析仪设计

一、实验目的

进一步熟悉QuartusII及LPM-RAM宏模块与FPGA硬件资源的使用方法。

二、实验设备

计算机、和软件QuartusII

三、试验内容

设计一个8通道深度为1024的简易逻辑分析仪

四、试验原理

打开QuartusII软件,在连接试验电路之前调入LPM-RAM-DQ宏模块,PLM-COUNER模块和74244芯片,再连接电路图,试验原理设计图如下:

图1-1逻辑数据采样电路顶层设计

五、实验结果

试验结果图如下:

图1-2综合后的RTL

图1-3仿真波形图

六、试验小节

本次试验成功的关键是要做好每一个步骤,并且确保每一个步骤的正确性,要求我们有耐心和细心。

学会查找错误,改正错误。

这么多次试验后,我感觉做起试验已经不怎么费劲了,好像找到了运用QuartusII技巧了,不过有时候还是会犯一些小错误。

不

过谁能无过呢?我有信心学好QuartusII,做好实验!。