算术逻辑运算实验

- 格式:doc

- 大小:139.50 KB

- 文档页数:3

算术逻辑运算实验总结一、引言在现代社会中,算术逻辑运算是一项基本且必不可少的能力。

它们不仅在日常生活中起着重要作用,也广泛应用于各个领域的科学和工程。

为了提高算术逻辑运算的能力,我进行了几项实验,并总结了一些重要的经验和教训。

二、实验一:基本算术运算在这个实验中,我进行了一系列的基本算术运算,如加法、减法、乘法和除法。

通过这些运算,我更加熟悉了数字和运算的关系,并且提高了我的计算速度和准确性。

通过这个实验,我发现了一些有趣的现象。

首先,我发现加法和减法是最简单的运算,因为它们只涉及到数字的简单相加或相减。

而乘法和除法则需要更多的思考和推理,因为它们涉及到数字的相对大小和关系。

除此之外,在进行算术运算时,我还体会到了一些技巧和方法。

例如,在进行长数列的相加时,可以将它们分成多个小段,然后分别相加,最后再将结果相加。

这样可以降低错误的可能性,同时提高计算的效率。

三、实验二:逻辑运算逻辑运算是另一种重要的运算方式。

在这个实验中,我学习了逻辑运算的基本原理和方法,并进行了一些实际的应用。

首先,我学习了与运算、或运算和非运算的基本规则。

通过这些规则,我可以判断一个命题的真假,或者从若干个命题中得出一个新的结论。

这是在科学和工程中经常用到的一种思维方式。

其次,我了解了逻辑运算在算法设计和编程中的重要性。

在编写程序时,逻辑运算用于判断条件和控制程序的流程。

通过合理地使用逻辑运算,可以使程序更加高效和精确。

实验中,我发现了一些常见的逻辑谬误。

例如,德摩根定律的错误应用会导致逻辑矛盾和错误的结果。

因此,在进行逻辑运算时,我要特别注意各种规则和定律的正确使用。

四、实验三:复杂算术逻辑运算在这个实验中,我尝试了一些更加复杂的算术逻辑运算,如平方根运算、对数运算和三角函数运算。

通过这些运算,我更深入地了解了数学的奥秘和复杂性。

在进行这些运算时,我遇到了一些困难和挑战。

首先,一些运算需要使用特殊的方法和技巧,我要仔细学习和掌握这些技术。

信息工程学院实验报告课程名称:计算机组成基础Array实验项目名称:算术逻辑运算实验实验时间:班级:141 姓名:王炳地学号:201411401121一、实验目的(1) 了解运算器的组成结构。

(2) 掌握运算器的工作原理。

二、实验设备PC机一台,TD-CMA实验系统一套。

三、实验原理本实验的原理如图1-1-1所示。

运算器内部含有三个独立运算部件,分别为算术、逻辑和移位运算部件,要处理的数据存于暂存器A 和暂存器B,三个部件同时接受来自A和B的数据(有些处理器体系结构把移位运算器放于算术和逻辑运算部件之前,如ARM),各部件对操作数进行何种运算由控制信号S3…S0和CN来决定,任何时候,多路选择开关只选择三部件中一个部件的结果作为ALU的输出。

如果是影响进位的运算,还将置进位标志FC,在运算结果输出前,置ALU零标志。

ALU中所有模块集成在一片CPLD中。

逻辑运算部件由逻辑门构成,较为简单,而后面又有专门的算术运算部件设计实验,在此对这两个部件不再赘述。

移位运算采用的是桶形移位器,一般采用交叉开关矩阵来实现,交叉开关的原理如图1-1-2所示。

图中显示的是一个4X4的矩阵(系统中是一个8X8的矩阵)。

每一个输入都通过开关与一个输出相连,把沿对角线的开关导通,就可实现移位功能,即:(1) 对于逻辑左移或逻辑右移功能,将一条对角线的开关导通,这将所有的输入位与所使用的输出分别相连,而没有同任何输入相连的则输出连接0。

(2) 对于循环右移功能,右移对角线同互补的左移对角线一起激活。

例如,在4位矩阵中使用‘右1’和‘左3’对角线来实现右循环1位。

(3) 对于未连接的输出位,移位时使用符号扩展或是0填充,具体由相应的指令控制。

使用另外的逻辑进行移位总量译码和符号判别。

图1-1-1 运算器原理图运算器部件由一片CPLD 实现。

ALU 的输入和输出通过三态门74LS245连到CPU 内总线上,另外还有指示灯标明进位标志FC 和零标志FZ 。

实验2 算术逻辑运算实验一、实验目的1.掌握简单运算器的组成以及数据传送通路2.验证运算功能发生器(74LS181)的组合功能二、实验设备74LS181(两片),74LS273(两片), 74LS245(一片),开关若干,灯泡若干,单脉冲一片三、实验原理实验中的运算器由两片74LS181以并/串形式构成8位字长的ALU。

运算器的输出经过一个三态门(74LS245)和数据总线相连,运算器的两个数据输入端分别由两个锁存器(74LS373)锁存,锁存器的输入连至数据总线,数据开关用来给出参与运算的数据(A和B),并经过一个三态门(74LS245)和数据显示灯相连,显示结果。

74LS181:完成加法运算74LS273:输入端接数据开关,输出端181。

在收到上升沿的时钟信号前181和其输出数据线之间是隔断的。

在收到上升沿信号后,其将输出端的数据将传到181,同时,作为触发器,其也将输入的数据进行保存。

因此,通过增加该芯片,可以通过顺序输入时钟信号,将不同寄存器中的数据通过同一组输出数据线传输到181芯片的不同引脚之中74LS245:相当于181的输出和数据显示灯泡组件之间的一个开关,在开始实验后将其打开,可以使181的运算结果输出并显示到灯泡上四、实验步骤1. 选择实验设备:根据实验原理图,将所需要的组件从组件列表中拖到实验设计流程栏中。

2. 搭建实验流程:将已选择的组件进行连线(鼠标从一个引脚的端点拖动到另一组件的引脚端,即完成连线)。

搭建好的实验流程图如图2所示。

具体操作如下:①将74LS273芯片的0-7号引脚(数据端从低到高)及9号引脚(复位端)接到开关上,8号引脚接至单脉冲组件,左右两个74LS273芯片分别保存参与运算的数据A和B。

接着把两个74LS273组件的11-14号引脚(数据的低四位)分别接到74LS181组件(左)的0-7号引脚上,其中0-3号引脚为A的低四位,4-7号引脚为B的低四位。

实验2 算术与逻辑运算指令实验一、实验目的1. 学习算术与逻辑运算的原理及指令的用法;2. 进一步学习emu8086调试程序的用法,并学会emu8086下编写简单应用程序的方法;3. 掌握BCD码加、减法以及ASCII码加减法。

二、实验内容1. 用emu8086执行各加减法指令以及不同编码方式的运算方法,记录执行结果,进行分析、比较,掌握各功能类似的指令之间的差别。

2. 用emu8086编写一个COM文件,其功能是检查自身的长度以及代码检查和。

如果自身的长度改变或检查和改变,则显示“VIRUS”,否则显示“OK”。

三、实验步骤(一) 加法、减法以及逻辑运算指令练习1. 启动emu8086;2. 用单步按钮命令调试以下程序段(分号后注释部分不用输入);-Axxxx:0100 XOR AX,AX ;AX= , C=____, Z=____xxxx:0102 MOV AX,89AB ;AX= , C=____, Z=____xxxx:0105 MOV BX,AX ;BX=xxxx:0107 INC AX ;AX= , C=____, Z=____xxxx:0108 DEC AX ;AX= , C=____, Z=____xxxx:0109 ADD AX,SI ;AX= , C=____, Z=____xxxx:010B SUB AX,SI ;AX= , C=____, Z=____xxxx:010D ADC AX,SI ;AX= , C=____, Z=____xxxx:010F SBB AX,SI ;AX= , C=____, Z=____xxxx:0111 NOPxxxx:0112 MOV AX,0808xxxx:0115 MOV BX,0080xxxx:0118 MOV CX,0880 ;CX=___________xxxx:011B OR AX,BX ;AX=___________ , C=____, OV=____xxxx:011D MOV AX,0808 ;AX=___________, BX=___________xxxx:0120 AND AX,CX ;AX=___________, C=____, S=____xxxx:0122 MOV AX,0808 ;AX=___________, CX=___________xxxx:0125 XOR AX,BX ;AX=___________, BX=___________xxxx:0127 NOT AX ;AX=___________xxxx:0129 NEG AX ;AX=___________xxxx:012B3. 分析上述程序段,用铅笔填写指令依次执行后寄存器和标志位的值,观察它们的变化。

福建农林大学计算机与信息学院信息工程类实验报告课程名称:计算机组成原理姓名:系:计算机专业:计算机科学与技术年级:09级学号:指导教师:职称:2010年12月29日实验项目列表福建农林大学计算机与信息学院信息工程类实验报告系:计算机专业:计算机科学与技术年级: 09 姓名:学号:实验课程:实验室号:____509 实验设备号:试验台8 实验时间:指导教师签字:成绩:实验名称算术逻辑运算实验1.实验目的和要求1.掌握简单运算器的组成以及数据传送通路;2.验证运算功能发生器(74ls181)的组合功能。

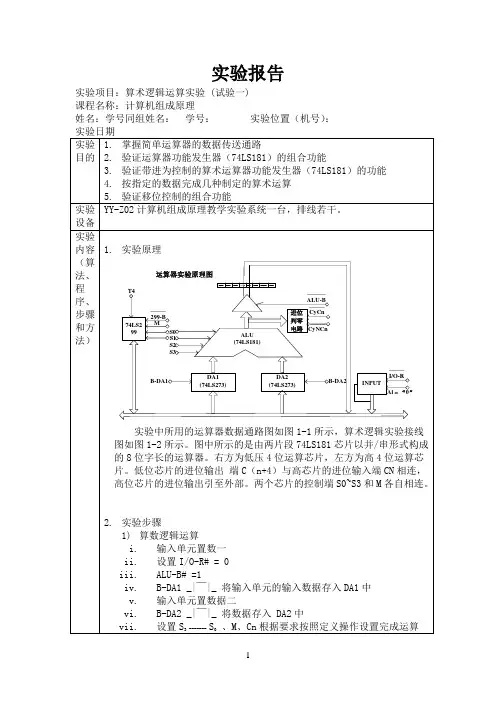

2.实验原理实验中所用的运算器数据通路如图1-1所示。

其中运算器由两片74LS181,以并/串形式构成8位字长的ALU。

运算器的两个数据输入端分别由两个锁存器(74LS273)锁存,锁存器的输入连至数据总线,数据输入开关用来给出参与运算的数据,并经过—三态门(74LS245)和数据总线相连。

运算器的输出经过一个三态门(74LS245)和数据总线相连。

数据显示灯已和数据总线相连,用来显示数据总线内容。

图1-1 运算器数据通路图图1-2中已将实验需要连接的控制信号用箭头标明。

其中除T4为脉冲信号,其他均为脉冲控制信号。

实验电路中的控制时序信号均已内部连至引出端,进行实验时,还需将S3、S2、S1、S0、Cn、LDDR1、LDDR2、ALU_G、SW_G各电平控制信号与开关单元中的二进制数据开关进行跳线连接。

其中ALU_G、SW_G为低电平有效,LDDR1、LDDR2为高电平有效。

图1-2 算术逻辑运算实验接线图3.主要仪器设备(实验用的软硬件环境)ZYE1603B计算机组成原理及系统结构教学实验箱一台,排线若干。

4.操作方法与实验步骤1.按图1-2连接实验线路,仔细检查无误后,接通电源。

2.用输入单元的二进制数据开关的寄存器DR1和DR2置数,数据开关的内容可以用与开关对应的指示灯来观察,灯亮表示开关量为“1”,灯灭表示开关量为“0”。

实验一8位算术逻辑运算实验一、实验目的1、掌握算术逻辑运算器单元ALU(74LS181)的工作原理2、掌握简单运算器的数据传送通路组成原理。

2、验证算术逻辑运算功能发生器74LSl8l的组合功能。

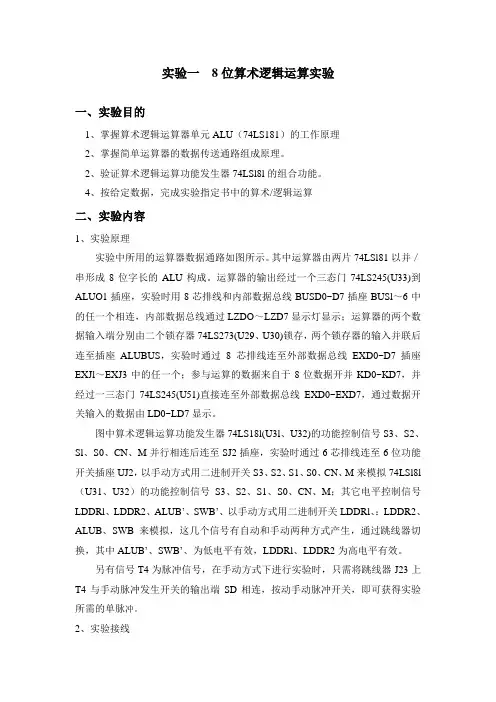

4、按给定数据,完成实验指定书中的算术/逻辑运算二、实验内容1、实验原理实验中所用的运算器数据通路如图所示。

其中运算器由两片74LSl81以并/串形成8位字长的ALU构成。

运算器的输出经过一个三态门74LS245(U33)到ALUO1插座,实验时用8芯排线和内部数据总线BUSD0~D7插座BUSl~6中的任一个相连,内部数据总线通过LZDO~LZD7显示灯显示;运算器的两个数据输入端分别由二个锁存器74LS273(U29、U30)锁存,两个锁存器的输入并联后连至插座ALUBUS,实验时通过8芯排线连至外部数据总线EXD0~D7插座EXJl~EXJ3中的任一个;参与运算的数据来自于8位数据开并KD0~KD7,并经过一三态门74LS245(U51)直接连至外部数据总线EXD0~EXD7,通过数据开关输入的数据由LD0~LD7显示。

图中算术逻辑运算功能发生器74LS18l(U3l、U32)的功能控制信号S3、S2、Sl、S0、CN、M并行相连后连至SJ2插座,实验时通过6芯排线连至6位功能开关插座UJ2,以手动方式用二进制开关S3、S2、S1、S0、CN、M来模拟74LSl8l (U31、U32)的功能控制信号S3、S2、S1、S0、CN、M;其它电平控制信号LDDRl、LDDR2、ALUB’、SWB’、以手动方式用二进制开关LDDRl、:LDDR2、ALUB、SWB来模拟,这几个信号有自动和手动两种方式产生,通过跳线器切换,其中ALUB’、SWB’、为低电平有效,LDDRl、LDDR2为高电平有效。

另有信号T4为脉冲信号,在手动方式下进行实验时,只需将跳线器J23上T4与手动脉冲发生开关的输出端SD相连,按动手动脉冲开关,即可获得实验所需的单脉冲。

算术逻辑运算单元实验一、实验目的1、掌握简单运算器的数据传输方式2、掌握74LS181的功能和应用二、实验要求完成不带进位位算术、逻辑运算实验。

按照实验步骤完成实验项目,了解算术逻辑运算单元的运行过程。

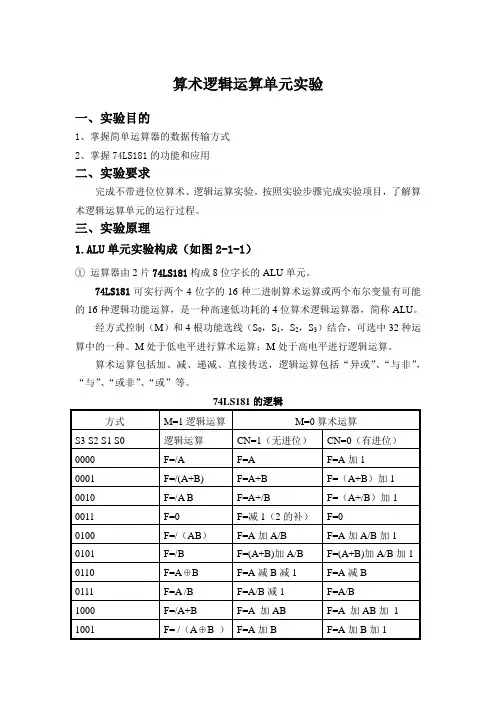

三、实验原理1.ALU单元实验构成(如图2-1-1)①运算器由2片74LS181构成8位字长的ALU单元。

74LS181可实行两个4位字的16种二进制算术运算或两个布尔变量有可能的16种逻辑功能运算,是一种高速低功耗的4位算术逻辑运算器,简称ALU。

经方式控制(M)和4根功能选线(S0,S1,S2,S3)结合,可选中32种运算中的一种。

M处于低电平进行算术运算;M处于高电平进行逻辑运算。

算术运算包括加、减、递减、直接传送,逻辑运算包括“异或”、“与非”,“与”、“或非”、“或”等。

说明:“加”指算术加,运算时考虑进位;“+”指逻辑加,不考虑进位②2片74LS374作为2个数据锁存器(DR1、DR2)。

8芯插座ALU-IN作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。

③运算器的数据输出由一片74LS244(输出缓冲器)来控制。

8芯插座ALU-OUT作为数据输出端,可通过短8芯扁平电缆把数据输出端连接到数据总线上。

74LS244:为3态8位缓冲器,一般用作总线驱动器。

图2-1-12.ALU单元的工作原理数据输入锁存器DR1的EDR1为低电平,并且D1CK有上升沿时,把来自数据总线的数据打入锁存器DR1。

同样使EDR2为低电平、D2CK有上升沿时把数据总线上的数据打入数据锁存器DR2。

算术逻辑运算单元的核心是由2片74LS181组成,它可以进行2个8位二进制数的算术逻辑运算,74LS181的各种工作方式可通过设置其控制信号来实现(S0、S1、S2、S3、M、CN)。

当正确设置了74LS181的各个控制信号,74LS181会运算数据锁存器DR1、DR2内的数据。

输出缓冲器采用74LS244,当控制信号ALU-O为低电平时,74LS244导通,把74LS181的运算结果输出到数据总线;当ALU-O为高电平时,74LS244的输出为高阻。

计算机组成原理实验报告专业:计算机+自动化姓名:桑超强(201126100416)陆黎明(201126100412)实验二算术逻辑运算实验一、实验目的:·了解运算器的组成结构·掌握运算器的工作原理·掌握简单运算器的数据传输通路·验证运算功能发生器74LS181的组合功能二、实验设备•TDN-CM++教学实验系统一套三、实验原理1、运算器芯片(74LS181)的逻辑功能74LS181 是一种数据宽度为4个二进制的多功能运算器芯片,封装在24引脚的封装壳中,封装型式如图2.1所示。

图2.1 74LS181封装图主要引脚有:(1)A0-A3:第一组操作数据输入端。

(2)B0-B3:第二组操作数据输入端。

(3)F0-F3:操作结果数据输出端。

(4)S0-S3:操作功能控制端。

(5)Cn :低端进位接收端。

(6)4Cn :高端进位输出端。

(7)M :算术/逻辑功能控制端。

芯片的逻辑功能见表2.1。

从表中可看到当控制端S0-S3为1001、M 为0、Cn 为1时,操作结果数据输出端F0-F3上的数据等于第一组操作数据输入端A0-A3上的数据加第二组操作数据输入端B0-B3上的数据。

当S0-S3、M 、Cn 上的控制信号电平不同时,74LS181芯片完成不同功能的逻辑运算操作或算术逻辑运算。

在加法运算操作时,Cn 、4Cn 进位信号低电平有效;减法运算操作时,Cn 、4Cn 借位信号高电平有效;而逻辑运算操作时,Cn 、4Cn 进位信号无意义。

图2.1数据逻辑运算部件原理图2、运算器实验逻辑电路试验台运算器实验逻辑电路中,两片74LS181芯片构成一个长度为8位的运算器,两片74LS373分别作为第一操作数据寄存器和第二操作数据寄存器,一片74LS245作为操作结果数据输出缓冲器,逻辑结构如图2.2所示。

图中算术逻辑操作时仅为Cy 判别进位只是电路;判零Zi 和零标志电路指示电路。

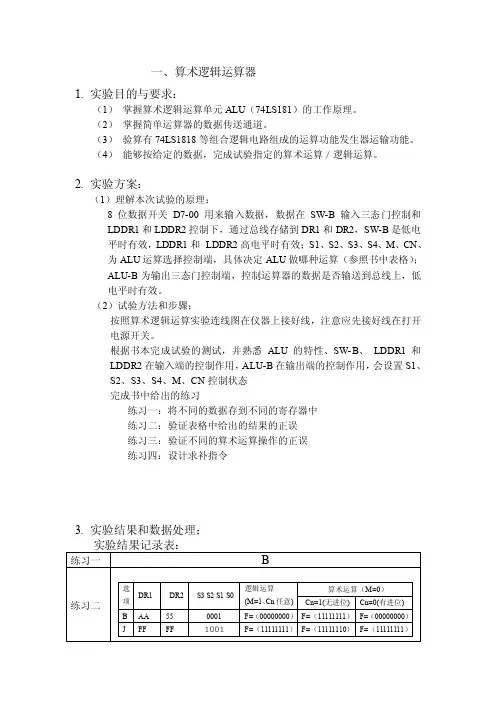

一、算术逻辑运算器1.实验目的与要求:(1)掌握算术逻辑运算单元ALU(74LS181)的工作原理。

(2)掌握简单运算器的数据传送通道。

(3)验算有74LS1818等组合逻辑电路组成的运算功能发生器运输功能。

(4)能够按给定的数据,完成试验指定的算术运算/逻辑运算。

2.实验方案:(1)理解本次试验的原理:8位数据开关D7-00用来输入数据,数据在SW-B输入三态门控制和LDDR1和LDDR2控制下,通过总线存储到DR1和DR2,SW-B是低电平时有效,LDDR1和LDDR2高电平时有效;S1、S2、S3、S4、M、CN、为ALU运算选择控制端,具体决定ALU做哪种运算(参照书中表格);ALU-B为输出三态门控制端,控制运算器的数据是否输送到总线上,低电平时有效。

(2)试验方法和步骤:按照算术逻辑运算实验连线图在仪器上接好线,注意应先接好线在打开电源开关。

根据书本完成试验的测试,并熟悉ALU的特性、SW-B、LDDR1和LDDR2在输入端的控制作用,ALU-B在输出端的控制作用,会设置S1、S2、S3、S4、M、CN控制状态完成书中给出的练习练习一:将不同的数据存到不同的寄存器中练习二:验证表格中给出的结果的正误练习三:验证不同的算术运算操作的正误练习四:设计求补指令3.实验结果和数据处理:4.结论(1)S1、S2、S3、S4、M、CN控制了ALU实现的运算功能/逻辑功能。

00001任意时实现了对DR1逻辑非的功能,而01011时则实现了对DR2的逻辑非的功能。

(2)当M为高电位时实现逻辑运算,M为低电位时实现算术运算。

(3)通过不同电路的配合,ALU能实现原来没有的功能。

比如求原码的补码等。

5.问题与讨论及实验总结问题:ALU(74LS181)的算术操作都是无符号的运算,对于带符号的操作,应该怎样实现通过做本次试验,我了解到ALU有了的工作原理及其基本操作,会用ALU实现一些不同的功能,并且了解了一些数据传送通道的知识,基本达到了本次试验目的。

班级:学号:姓名:实验项目一:算术逻辑运算实验一、实验目的:1.掌握简单运算器的组成以及数据传送通路。

2.验证运算功能发生器(74LS181)的组合功能。

3.按给定的数据完成几种指定的算术逻辑运算。

二、实验重点:1.数据的传送2.运算功能发生器(74LS181)的引脚功能的应用三、实验难点:1.工作过程的理解四、实验任务:1.计算74(加)262.计算74(减)263.计算-74(加)264.计算74(减)-265.计算74(与)266.计算74(或)26*7.完成《实验指导书》P7表1-2中指定的运算(选做)五、实验原理:实验中所用的运算器数据通路如上图所示。

其中运算器由两片74LS181以并/串形式构成8位字长的ALU。

运算器的两个数据输入端分别由两个锁存器(74LS273)锁存,锁存器的输入连至数据总线,数据输入开关用来给出参与运算的数据,并经过一三态门(74LS245)和数据总线相连。

运算器的输出经过一个三态门(74LS245)和数据总线相连。

数据显示灯已和数据总线相连,用来显示数据总线内容。

表1-1 74LS181功能表任务1:①连线:②开关复位:③打开电源,启动:待连线与开关复位都做好后,打开电源,启动④初始化:SW_G=1,CLR=1,ALU_G=1,S0=S1=S2=S3=M=CN=1,LDDR1=LDDR2=0⑤输入数据A:在输入单元输入01001010,将SW_G置为0,观察总线指示灯是否显示为01001010,然后将LDDR1置为1,并按下控制台单元的START按键,接着把LDDR1还原为0,SW_G还原为1⑥输入数据B:在输入单元输入00011010,将SW_G置为0,观察总线指示灯是否显示为00011010,然后将LDDR2置为1,并按下控制台单元的START按键,接着把LDDR2还原为0,SW_G还原为1⑦计算:将S0、S1、S2、S3、M、CN分别置为1、0、0、1、0、1,再将ALU_G置为0,观察总线指示灯的显示结果⑧输出结果:总线指示灯的显示结果为01100100,与实际结果相符任务2:①②③④同上⑤输入数据A:在输入单元输入01001010,将SW_G置为0,观察总线指示灯是否显示为01001010,然后将LDDR1置为1,并按下控制台单元的START按键,接着把LDDR1还原为0,SW_G还原为1⑥输入数据B:在输入单元输入11100110,将SW_G置为0,观察总线指示灯是否显示为11100110,然后将LDDR2置为1,并按下控制台单元的START按键,接着把LDDR2还原为0,SW_G还原为1⑦计算:将S0、S1、S2、S3、M、CN分别置为1、0、0、1、0、1,再将ALU_G置为0,观察总线指示灯的显示结果⑧输出结果:总线指示灯的显示结果为00110000,与实际结果相符任务3:①②③④同上⑤输入数据A:在输入单元输入10110110,将SW_G置为0,观察总线指示灯是否显示为10110110,然后将LDDR1置为1,并按下控制台单元的START按键,接着把LDDR1还原为0,SW_G还原为1⑥输入数据B:在输入单元输入00011010,将SW_G置为0,观察总线指示灯是否显示为00011010,然后将LDDR2置为1,并按下控制台单元的START按键,接着把LDDR2还原为0,SW_G还原为1⑦计算:将S0、S1、S2、S3、M、CN分别置为1、0、0、1、0、1,再将ALU_G置为0,观察总线指示灯的显示结果⑧输出结果:总线指示灯的显示结果为11010000,与实际结果相符任务4:①②③④同上⑤输入数据A:在输入单元输入01001010,将SW_G置为0,观察总线指示灯是否显示为01001010,然后将LDDR1置为1,并按下控制台单元的START按键,接着把LDDR1还原为0,SW_G还原为1⑥输入数据B:在输入单元输入00011010,将SW_G置为0,观察总线指示灯是否显示为00011010,然后将LDDR2置为1,并按下控制台单元的START按键,接着把LDDR2还原为0,SW_G还原为1⑦计算:将S0、S1、S2、S3、M、CN分别置为1、0、0、1、0、1,再将ALU_G置为0,观察总线指示灯的显示结果⑧输出结果:总线指示灯的显示结果为01100100,与实际结果相符任务5:①②③④同上⑤输入数据A:在输入单元输入01001010,将SW_G置为0,观察总线指示灯是否显示为01001010,然后将LDDR1置为1,并按下控制台单元的START按键,接着把LDDR1还原为0,SW_G还原为1⑥输入数据B:在输入单元输入00011010,将SW_G置为0,观察总线指示灯是否显示为00011010,然后将LDDR2置为1,并按下控制台单元的START按键,接着把LDDR2还原为0,SW_G还原为1⑦计算:将S0、S1、S2、S3、M分别置为1、1、0、1、1,再将ALU_G置为0,观察总线指示灯的显示结果⑧输出结果:总线指示灯的显示结果为00001010,与实际结果相符任务6:①②③④同上⑤输入数据A:在输入单元输入01001010,将SW_G置为0,观察总线指示灯是否显示为01001010,然后将LDDR1置为1,并按下控制台单元的START按键,接着把LDDR1还原为0,SW_G还原为1⑥输入数据B:在输入单元输入00011010,将SW_G置为0,观察总线指示灯是否显示为00011010,然后将LDDR2置为1,并按下控制台单元的START按键,接着把LDDR2还原为0,SW_G还原为1⑦计算:将S0、S1、S2、S3、M分别置为0、1、1、1、1,再将ALU_G置为0,观察总线指示灯的显示结果⑧输出结果:总线指示灯的显示结果为01011010,与实际结果相符七、实验总结:—开始实验的时候,对设备不熟练,不了解各控制端的作用,在听了老师的讲解,初步了解设备各部分的功能,再结合PPT上的实验操作步骤,才成功连接好了线路。

算术逻辑运算实验报告

《算术逻辑运算实验报告》

在这个数字时代,算术和逻辑运算已经成为我们生活中不可或缺的一部分。

无论是在日常生活中做出购物决策,还是在工作中处理数据和信息,都需要进行各种形式的算术和逻辑运算。

因此,我们进行了一项实验,以探究算术逻辑运算在现代社会中的重要性和应用。

实验的第一部分是针对算术运算的。

我们邀请了一些参与者来完成一系列简单的算术运算,包括加法、减法、乘法和除法。

结果显示,参与者们在进行这些算术运算时,大部分都能够迅速而准确地完成,表明他们对基本的算术运算有着较高的掌握能力。

接着,我们进行了逻辑运算的实验。

参与者们需要解决一系列逻辑问题,包括推理、判断和排列等。

结果显示,参与者们在处理这些逻辑问题时,表现出了较高的逻辑思维能力和解决问题的能力。

在实验的最后,我们进行了一些结合算术和逻辑运算的综合实验。

参与者们需要在规定的时间内完成一系列复杂的算术逻辑运算题目。

结果显示,大部分参与者们都能够在规定的时间内完成题目,并且在准确率上也表现出了较高的水平。

通过这次实验,我们可以得出结论:算术和逻辑运算在现代社会中具有重要的意义和应用。

无论是在个人生活中,还是在工作和学习中,良好的算术和逻辑运算能力都能够帮助我们更好地处理信息和解决问题。

因此,我们应该重视算术和逻辑运算的学习和训练,以提升自己的综合能力和竞争力。

同时,也需要在教育和培训中加强对算术和逻辑运算的培养,以培养更多具有良好算术和逻

辑思维能力的人才。

实验三16位算术逻辑运算实验实验三16位算术逻辑运算实验⼀、实验⽬的1、掌握16位算术逻辑运算数据传送通路组成原理。

2、进⼀步验证算术逻辑运算功能发⽣器74L S181的组合功能。

⼆、实验内容1、实验原理实验中所⽤16位运算器数据通路如图3-3所⽰。

其中运算器由四⽚74L S181以并/串形成16位字长的A L U构成。

低8位运算器的输出经过⼀个三态门74L S245(U33)到内部总线,低8位数据总线通过L Z D0~L Z D7显⽰灯显⽰;⾼8位运算器的输出经过⼀个三态门74L S245(U33`)到A L U O1`插座,实验时⽤8芯排线和⾼8位数据总线B U S D8~D15插座K B U S1或K B U S2相连,⾼8位数据总线通过L Z D8~L Z D15显⽰灯显⽰;参与运算的四个数据输⼊端分别由四个锁存器74L S273(U29、U30、U29`、U30、)锁存,实验时四个锁存器的输⼊并联连⾄内部数据总线再⽤8芯线连接到外部数据总线E X D0~D7插座E X J1~E X J3中的任⼀个;参与运算的数据源来⾃于8位数据开并K D0~K D7,并经过⼀三态门74L S245(U51)直接连⾄外部数据总线E X D0~E X D7,输⼊的数据通过L D0~L D7显⽰。

2、实验接线本实验⽤到6个主要模块:⑴低8位运算器模块,⑵数据输⼊并显⽰模块,⑶数据总线显⽰模块,⑷功能开关模块(借⽤微地址输⼊模块),⑸⾼8位运算器模块,⑹⾼8位(扩展)数据总线显⽰模块。

根据实验原理详细接线如下:1、J20,J21,J22,接上短路⽚,图3-1.J20,J21,J22接上短路⽚2、J24,J25,J26接左边;图3-2.J24,J25,J26接左边3、J27,J28 左边图3-3.J27,J28接左边4、J23 置右边T4选“SD”图3-4.J23接右边5、JA5 置“接通”;图3-5.JA5置上⽅“接通”6、JA6 置“⼿动”;图3-6.JA6置下边“⼿动”7、JA3 置“接通”;图3-7.JA3置右边“接通”8、JA1,JA2,JA4置“⾼阻”;图3-8.JA1、JA2接下边“⾼阻”图3-9.JA4置左边“⾼阻”9、JA8 置上⾯“微地址”图3-10.JA8置上⾯“微地址”10、EXJ1接BUS3图3-11.EXJ1接BUS3 11、ALO1'接KBUS1图3-12.ALO1接KBUS1 12、开关CE 、AR 置1图3-13.CE与AR各⾃置113、ZI2,CN4,CN0接上短路⽚图3-14.Z12,CN4和CN0都接上短路⽚3、实验步骤⑴连接线路,仔细查线⽆误后,接通电源。

算术逻辑运算实验报告算术逻辑运算实验报告一、引言算术逻辑运算是数学中的重要分支,它研究数字和符号之间的关系以及它们之间的运算规则。

在日常生活中,我们经常进行算术逻辑运算,比如加减乘除、逻辑与或非等。

本实验旨在通过一系列实验,探索算术逻辑运算的规律和特点。

二、实验一:加法与减法1. 实验目的通过加法和减法实验,观察数字之间的相互关系,并分析运算规律。

2. 实验步骤首先,我们随机选择两个数字进行加法运算,记录结果。

然后,再选择两个数字进行减法运算,同样记录结果。

3. 实验结果与分析我们发现,在加法运算中,两个正数相加的结果仍然是正数,而两个负数相加的结果仍然是负数。

而正数与负数相加,则会根据绝对值的大小决定结果的正负性。

在减法运算中,两个正数相减的结果可能是正数或零,而两个负数相减的结果可能是负数或零。

正数与负数相减,则会根据绝对值的大小决定结果的正负性。

三、实验二:乘法与除法1. 实验目的通过乘法和除法实验,观察数字之间的相互关系,并分析运算规律。

2. 实验步骤我们选择两个数字进行乘法运算,记录结果。

然后,再选择两个数字进行除法运算,同样记录结果。

3. 实验结果与分析我们发现,在乘法运算中,两个正数相乘的结果仍然是正数,而两个负数相乘的结果则变为正数。

正数与负数相乘,则会根据负数的个数决定结果的正负性。

在除法运算中,两个正数相除的结果仍然是正数,而两个负数相除的结果则变为正数。

正数与负数相除,则会根据负数的个数决定结果的正负性。

四、实验三:逻辑与与逻辑或1. 实验目的通过逻辑与和逻辑或实验,观察逻辑运算的结果,并分析运算规律。

2. 实验步骤我们随机选择两个命题进行逻辑与运算,记录结果。

然后,再选择两个命题进行逻辑或运算,同样记录结果。

3. 实验结果与分析逻辑与运算的结果只有在两个命题都为真时才为真,否则为假。

逻辑或运算的结果只有在两个命题都为假时才为假,否则为真。

五、实验四:逻辑非1. 实验目的通过逻辑非实验,观察逻辑运算的结果,并分析运算规律。

实验报告一、实验名称运算器实验—算术逻辑运算实验二、实验目的1、了解运算器的组成原理。

2、掌握运算器的工作原理。

3、掌握简单运算器的数据传送通路。

4、验证运算功能发生器(74LS181)的组合功能。

三、实验设备TDN-CM++计算机组成原理教学实验系统一套,导线若干。

四、实验原理实验中所用的运算器数据通路如图1-1所示。

其中两片74LSl81以串行方式构成8位字长的ALU,ALU的输出经过一个三态门(74LS245)和数据总线相连。

三态门由ALU-R控制,控制运算器运算的结果能否送往总线,低电平有效。

为实现双操作数的运算,ALU的两个数据输入端分别由二个锁存器DR1、DR2(由74LS273实现)锁存数据。

要将数据总线上的数据锁存到DRl、DR2中,锁存器的控制端LDDR1和DDR2必须为高电平,同时由T4脉冲到来。

数据开关(“INPUT DEVICE")用来给出参与运算的数据,经过三态(74LS245)后送入数据总线,三态门由SW—B控制,低电平有效。

数据显示灯(“BUS UNIT")已和数据总线相连,用来显示数据总线上的内容。

图中已将用户需要连接的控制信号用圆圈标明(其他实验相同,不再说明),其中除T4为脉冲信号外,其它均为电平信号。

由于实验电路中的时序信号均已连至“W/R UNIT”的相应时序信号引出端,因此,在进行实验时,只需将“W /R UNIT"的T4接至“STATE UNIT”的微动开关KK2的输入端,按动微动开关,即可获得实验所需的单脉冲。

ALU运算所需的电平控制信号S3、S2、S1、S0 、Cn、M、LDDRl、LDDR2、ALU-B、SW-B均由“SWITCH UNIT ”中的二进制数据开关来模拟,其中Cn、ALU—B、SW一B为低电平有效LDDR1、LDDR2为高电平有效。

对单总线数据通路,需要分时共享总线,每一时刻只能由一组数据送往总线。

五、实验内容1.输入数据通过三态门74LS245后送往数据总线,在数据显示灯和数码显示管LED上显示。