Arduino 学习笔记 _74HC595

- 格式:pdf

- 大小:336.08 KB

- 文档页数:3

74HC595 详解

工作电压2-6V,推荐5V。

14 脚串行输入:595 的数据来源只有这一个口,一次只能输入一个位,那

幺连续输入8 次,就可以积攒为一个字节了。

13 脚OE 输出使能控制脚:如果它不工作,那幺595 的输出就是高阻态,595 就不受我们程序控制了,这显然违背我们的意愿。

OE 的上面画了一条线,表示他是低电平有效。

于是我们将他接GND。

10 脚SRCLR 位移寄存器清空脚:他的作用就是将位移寄存器中的数据

全部清空,这个很少用到,所以我们一般不让他起作用,也是低电平有效,于是我们给他接VCC。

12 脚RCLK 存储寄存器:数据从位移寄存器转移到存储寄存器,也是需要

时钟脉冲驱动的,这就是12 脚的作用。

它也是上升沿有效。

11 脚SRCLK 移位寄存器时钟输入:当一个新的位数据要进来时,已经进

入的位数据就在移位寄存器时钟脉冲的控制下,整体后移,让出位置。

分析下数据输入和输出过程:

假如,我们要将二进制数据0111 1111 输入到595 的移位寄存器中,下面。

74HC595完整中文资料74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持第二步:目的:将位数据逐位移入74HC595,即数据串入方法:P1.2产生一上升沿,将P1.0上的数据移入74HC595中.从低到高。

74HC595是硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

74 HC595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位(MR’),存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

特点8位串行输入/8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率输出能力并行输出,总线驱动;串行输出;标准中等规模集成电路595移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

参考数据CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压引脚说明符号引脚描述Q0…Q7 15,1,7 并行数据输出GND 8 地Q7’ 9 串行数据输出MR 10 主复位(低电平)SHCP 11 移位寄存器时钟输入STCP 12 存储寄存器时钟输入OE 13 输出有效(低电平)DS 14 串行数据输入VCC 16 电源功能表输入输出功能SHCP STCP OE MR DS Q7’ Qn× × L ↓ × L NC MR为低电平时仅仅影响移位寄存器× ↑ L L × L L 空移位寄存器到输出寄存器××H L ×L Z 清空移位寄存器,并行输出为高阻状态↑ × L H H Q6 NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

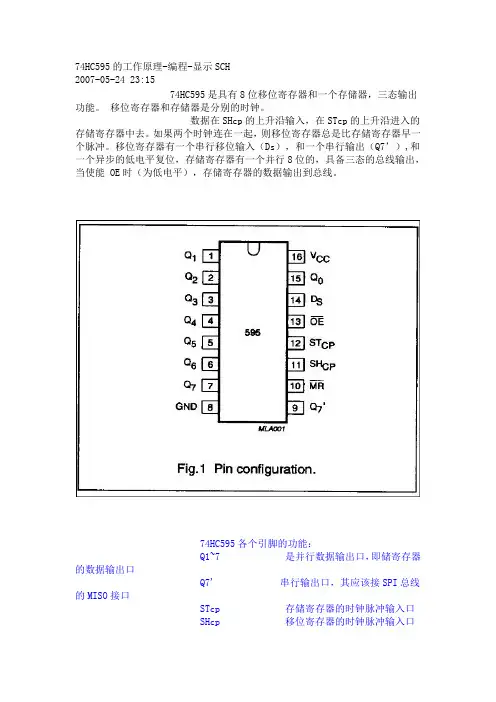

74HC595的工作原理-编程-显示SCH2007-05-24 23:1574HC595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能 OE时(为低电平),存储寄存器的数据输出到总线。

74HC595各个引脚的功能:Q1~7 是并行数据输出口,即储寄存器的数据输出口Q7' 串行输出口,其应该接SPI总线的MISO接口STcp 存储寄存器的时钟脉冲输入口SHcp 移位寄存器的时钟脉冲输入口OE的非输出使能端MR的非芯片复位端Ds 串行数据输入端程序说明:每当SHcp上升沿到来时,DS引脚当前电平值在移位寄存器中左移一位,在下一个上升沿到来时移位寄存器中的所有位都会向左移一位,同时Q7'也会串行输出移位寄存器中高位的值,这样连续进行8次,就可以把数组中每一个数(8位的数)送到移位寄存器;然后当STcp上升沿到来时,移位寄存器的值将会被锁存到锁存器里,并从Q1~7引脚输出。

//74HC595串行输出数据void outdisp(unsigned char num){unsigned char i;for (i=0;i<8;i++ ){DS=num;SHCP=1;SHCP=0;num<<=1;}}设计显示PCB板(595一为传送位选信号,一为传送代码段信号)。

最详细的74HC595芯片使用方法介绍2010-01-17 00:07:05 来源: 电子工程师论坛Arduino采用的ATmega168芯片带12个数字I/O管脚,其中每个都可以对一个数字量进行控制,从而实现类似于点亮一个发光二极管这样的功能。

在实际的工程应用里,有时我们可能会遇到需要对更多的数字量进行控制的场合,比如同时控制16个发光二极管,这时Arduino自带的数字I/O管脚就不够用了,必须进行相应的扩展。

其中一种可行的办法就是借助74HC595这样一个8位串入并出移位寄存器,这个芯片能够多个级连起来一起使用,因此理论上能够通过Arduino上有限的几个管脚(最少三个)产生任意多个的数字输出。

74HC595同数据相关的引脚可以分为三类:DS:串行数据输入,接Arduino的某个数字I/O引脚。

Q0~Q7:8位并行数据输出,可以直接控制8个LED,或者是七段数码管的8个引脚。

Q7′:级联输出端,与下一个74HC595的DS相连,实现多个芯片之间的级联。

74HC595同控制相关的引脚一共有四个:SH_CP:移位寄存器的时钟输入。

上升沿时移位寄存器中的数据依次移动一位,即Q0中的数据移到Q1中,Q1中的数据移到Q2中,依次类推;下降沿时移位寄存器中的数据保持不变。

ST_CP:存储寄存器的时钟输入。

上升沿时移位寄存器中的数据进入存储寄存器,下降沿时存储寄存器中的数据保持不变。

应用时通常将ST_CP置为低点平,移位结束后再在ST_CP端产生一个正脉冲更新显示数据。

MR:重置(RESET),低电平时将移位寄存器中的数据清零,应用时通常将它直接连高电平(VCC)。

OE:输出允许,高电平时禁止输出(高阻态)。

引脚不紧张的情况下可以用Arduino的一个引脚来控制它,这样可以很方便地产生闪烁和熄灭的效果。

实际应用时可以将它直接连低电平(GND)。

对于一个最简单的74HC595应用来讲,可以用Arduino的三个数字I/O端口分别控制DS、SH_CP和ST_CP,然后将MR和OE分别接VCC和地。

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

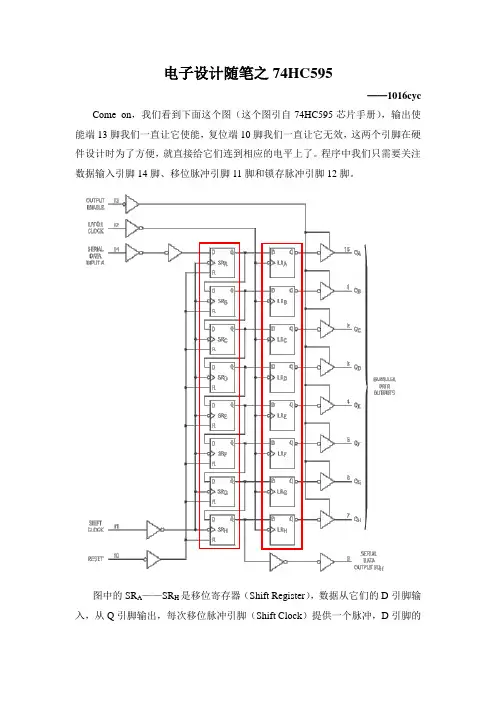

电子设计随笔之74HC595——1016cyc Come on,我们看到下面这个图(这个图引自74HC595芯片手册),输出使能端13脚我们一直让它使能,复位端10脚我们一直让它无效,这两个引脚在硬件设计时为了方便,就直接给它们连到相应的电平上了。

程序中我们只需要关注数据输入引脚14脚、移位脉冲引脚11脚和锁存脉冲引脚12脚。

图中的SR A——SR H是移位寄存器(Shift Register),数据从它们的D引脚输入,从Q引脚输出,每次移位脉冲引脚(Shift Clock)提供一个脉冲,D引脚的数据就会输出并保持到Q引脚,因为这里的移位脉冲引脚(Shift Clock)是连到每一个SR上的,所以自然每次给一个移位脉冲的时候,所有的数据都向后移动了一位。

这里我们注意到,SR A的D脚连接的是串行数据输入,也就是我们的数据引脚。

所以每次给脉冲移位之前,我们需要准备好该引脚的值,因为每次给一个脉冲,它的数据就会移入后方。

很直观的看到,我们给几个脉冲,数据引脚就会有几次被移入移位寄存器,并且这些值会保持在各个SR的Q脚。

所以假设我们要将一个字节移入移位寄存器,因为1个字节是8位的,所以我们需要给出8个脉冲,那么SR A——SR H的Q脚就保持了这8位值,再看看这8位值,它是先在数据引脚输出的值就会走得越远,所以如果我们先输出数据高位的话,最高位在8个脉冲后就会跑到SR H 的Q脚。

这就像我们排队一样,一个寄存器里面有8个位置,每次给一个脉冲就好比一次呼叫:“大家可以往前移一位了!”就这样,队伍不断得往前移,很简单吧!然后我们看到LR A——LR H,它们是锁存寄存器(Latch Register),每次锁存脉冲引脚(Latch Clock)给一个脉冲,Q脚就会输出并保持D脚的值。

其实聪明的人肯定会看出来了,LR和SR其实是差不多的功能,只是SR多了个复位脚。

我们可以把LR看成是照相机,锁存脉冲引脚就相当于是照相机的快门,我们给一个锁存脉冲,那么数据就被锁存在了对应的Q脚。

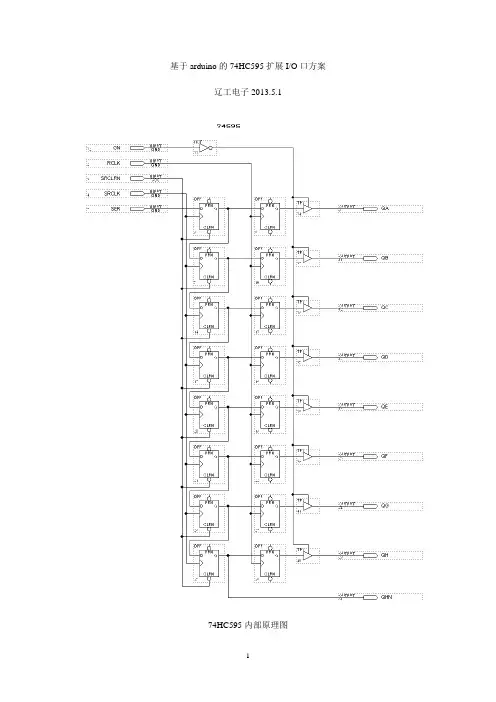

基于arduino的74HC595扩展I/O口方案辽工电子2013.5.174HC595内部原理图图注:G在实际使用中可以悬空,但将导致输出电压不稳。

可以常为低电平,即开通状态。

图示时序图传送的数据是“010”,两种时序图其结果是一样的,因为74595是上升沿读数的。

在arduino上的程序为(蓝色字体代码固定,可做循环):#define CLK 12//NO.11#define SER 13//NO.14#define RCK 11//NO.12#define G 10//NO.13#define RCLR 9//NO.10void setup() {pinMode(CLK, OUTPUT);pinMode(SER, OUTPUT);pinMode(RCK, OUTPUT);pinMode(G, OUTPUT);pinMode(RCLR, OUTPUT);}void loop() {digitalWrite(RCLR, HIGH); //un use it digitalWrite(G, HIGH); //close itdigitalWrite(RCK, LOW); //twice clkis still low//begin send itdigitalWrite(CLK, LOW);digitalWrite(SER, LOW);delay(1);digitalWrite(CLK, HIGH);delay(1); //1digitalWrite(CLK, LOW);digitalWrite(SER, HIGH);delay(1);digitalWrite(CLK, HIGH);delay(1); //2digitalWrite(CLK, LOW);digitalWrite(SER, LOW);delay(1);digitalWrite(CLK, HIGH);delay(1); //3//end itdigitalWrite(G, LOW); //open itdigitalWrite(RCK, HIGH); //give oneanotherdelay(1);digitalWrite(RCK, LOW); //return itwhile(1);//it's real end}这样输出的结果为0100,0000。

74hc595的用法

74HC595是一种常见的8位串行输入/输出寄存器,具有存储器寄存器、移位寄存器和透明锁存器等功能。

以下是74HC595的基本用法:

1. 引脚排列:74HC595有16个引脚,分为三个部分:数据输入(3个)、数据输出(3个)、控制信号(10个)。

2. 工作原理:当使能信号(OE和SCK)为低电平时,数据从DS端输入到

内部寄存器。

当OE信号为高电平时,数据从Q0到Q7端输出。

通过时钟

信号(SCK)控制数据的移位操作。

3. 数据传输:通过将数据输入到DS端,然后使用时钟信号(SCK)逐位地读取或写入数据。

OE信号用于控制数据的输出。

当OE为低时,数据从Q0到Q7端输出;当OE为高时,输出被禁止。

4. 存储器寄存器:74HC595具有一个8位的存储器寄存器,可以在OE信

号的上升沿将数据从移位寄存器复制到存储器寄存器中。

这样可以实现数据的保持功能。

5. 移位寄存器:74HC595具有一个8位的移位寄存器,可以在时钟信号(SCK)的控制下逐位地读取或写入数据。

通过将数据从DS端输入,然后

使用SCK信号逐位地读取或写入数据。

6. 透明锁存器:74HC595具有一个透明锁存器,可以在时钟信号(SCK)

的控制下对数据进行锁存。

当OE信号为低时,锁存器处于透明状态,输入

的数据可以直接传输到输出端;当OE信号为高时,锁存器处于锁存状态,输入的数据被锁存起来,不会影响输出端的数据。

以上是74HC595的基本用法,可以通过查阅相关资料了解更多高级用法和注意事项。

74HC595完整中文资料74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:管脚编号管脚名管脚定义功能1、2、3、4、5、6、7、15QA—QH 三态输出管脚8 GND 电源地9 SQH 串行数据输出管脚10 SCLR 移位寄存器清零端11 SCK 数据输入时钟线12 RCK 输出存储器锁存时钟线13 OE 输出使能14 SI 数据线15 VCC 电源端真值表:输入管脚输出管脚SI SCK SCLR RCK OEX X X X H QA—QH 输出高阻X X X X L QA—QH 输出有效值X X L X X 移位寄存器清零L 上沿H X X 移位寄存器存储LH 上沿H X X 移位寄存器存储HX 下沿H X X 移位寄存器状态保持X X X 上沿X 输出存储器锁存移位寄存器中的状态值X X X 下沿X 输出存储器状态保持74595的数据端:QA--QH: 八位并行输出端,可以直接控制数码管的8个段。

74HC595芯片是一种串入并出的芯片,在电子显示屏制作当中有广泛的应用。

74HC595是8位串行输入/输出或者并行输出移位寄存器,具有高阻、关、断状态。

三态。

特点 8位串行输入 8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除 100MHz的移位频率输出能力并行输出,总线驱动串行输出;标准中等规模集成电路应用串行到并行的数据转换 Remote contr ol holding register. 描述 595是告诉的硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp 的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

CPD决定动态的能耗, PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容 f0=输出频率(MHz) Vcc=电源电压引脚说明符号引脚描述内部结构结合引脚说明就能很快理解 595的工作情况引脚功能表:真值表:74595的控制端说明:/SRCLR(10脚): 低点平时将移位寄存器的数据清零。

通常我将它接Vcc。

SCK(11脚):上升沿时数据寄存器的数据移位。

QA-->QB-->QC-->...-->QH;下降沿移位寄存器数据不变。

(脉冲宽度:5V时,大于几十纳秒就行了。

我通常都选微秒级)RCK(12脚):上升沿时移位寄存器的数据进入数据存储寄存器,下降沿时存储寄存器数据不变。

(通常我将RCK置为低电平,) 当移位结束后,在RCK端产生一个正脉冲(5V时,大于几十纳秒就行了。

Arduino 入门到精通例程1774HC595实验74HC595 简单说来就是具有8 位移位寄存器和一个存储器,以及三态输出功能。

这里我们用它来控制8 个LED 小灯。

我们为什么要用74HC595 来控制小灯呢?一定会有很多朋友会问这个问题,我想问的是我们要是单纯的用Arduino 控制8 个小灯的话要占用多少个I/O 呢?答案是8 个,但是我们的Arduino 168 有几个I/O 口呢?加上模拟接口也就20 个吧,这8 个小灯占用了太多的资源了,我们用74HC595 的目的就是减少I/O 口的使用数量。

用74HC595 以后我们可以用3 个数字I/O 口控制8 个LED 小灯岂不美哉。

下面是我们要准备的元器件。

74HC595 直插芯片*1红色M5 直插LED*4绿色M5 直插LED*4220Ω直插电阻*8面包板*1面包板跳线*1 扎准备好元件我们就按下面的原理图连接电路。

此电路图看似复杂,我们仔细分析以后再结合参考实物就会发现很简单。

下面是参考源程序:int data = 2;int clock = 4;int latch = 5;int ledState = 0;const int ON = HIGH; const int OFF = LOW; void setup(){pinMode(data, OUTPUT); pinMode(clock, OUTPUT); pinMode(latch, OUTPUT); }void loop(){int delayTime = 100;for(int i = 0; i < 256; i++) {updateLEDs(i);delay(delayTime);}}void updateLEDs(int value){digitalWrite(latch, LOW);shiftOut(data, clock, MSBFIRST, value); digitalWrite(latch, HIGH);}void updateLEDsLong(int value){digitalWrite(latch, LOW);for(int i = 0; i < 8; i++){int bit = value & B10000000;value = value << 1;if(bit == 128){digitalWrite(data, HIGH);} else{digitalWrite(data, LOW);} digitalWrite(clock, HIGH);delay(1);digitalWrite(clock, LOW);}digitalWrite(latch, HIGH);}int bits[]={B00000001, B00000010, B00000100, B00001000,B00010000, B00100000,B01000000, B10000000};int masks[] ={B11111110, B11111101, B11111011, B11110111, B11101111, B11011111,B10111111, B01111111};void changeLED(int led, int state){ledState = ledState & masks[led];if(state == ON){ledState = ledState | bits[led];}updateLEDs(ledState);}下载完程序大家就可以看到8 个小灯闪烁的美妙场景了。

74hc595 工作原理

74HC595是一种集成电路芯片,它提供了一个8位的移位寄存器和一个串行输入/串行并行输出功能。

该芯片的工作原理如下:

1. 时钟信号:74HC595通过外部提供的时钟信号进行工作。

时钟信号用于同步数据的移位操作。

2. 数据输入:通过串行输入引脚SER输入数据。

当时钟信号的上升沿到达时,输入数据被移入移位寄存器中的第一个位。

之后,每个时钟信号的上升沿,数据将向左依次移位,直到移位寄存器中的最后一个位。

3. 移位寄存器:移位寄存器是由8个触发器组成,每个触发器都可以存储一个位的值(0或1)。

在数据输入完成后,每个触发器存储了相应的数据位。

4. 数据输出:在并行输出模式下,通过并行输出引脚Q0-Q7输出存储在移位寄存器中的数据。

这意味着可以同时输出8个位的数据。

在串行输出模式下,通过引脚Q7'S(又称为Q7'引脚)输出最后一个位的数据。

5. 存储寄存器:存储寄存器用于保存通过移位寄存器移入的数据,以便在输出时能够固定显示。

通过上述过程,74HC595实现了将串行输入的数据移位并以

并行输出的形式存储,从而实现数据的并行输出。

这使得它在需要同时控制多个设备的应用中非常有用,如LED显示、数码管、驱动器等。

⽤Tinkercad学arduino之74HC595寄存器控制8个led跑马灯// Arduino Pattern Creator by PhilCam//http://my.free.time.free.fr/// Use with Uno R3 + 74HC595 + 8 ledsint dataPin = 2;int latchPin = 3;int clockPin = 4;int seq[] = {128, 192, 224, 240, 248, 252, 254, 255, 127, 63, 31, 15, 7, 3, 1, 0, 1, 3, 7, 15, 31, 63, 127, 255, 254, 252, 248, 240, 224, 192, 128, 0};void setup(){pinMode(dataPin, OUTPUT);pinMode(latchPin, OUTPUT);pinMode(clockPin, OUTPUT);}void loop(){for (int n = 0; n < 32; n++){digitalWrite(latchPin, LOW); //Pull latch LOW to start sending datashiftOut(dataPin, clockPin, MSBFIRST, seq[n]); //Send the datadigitalWrite(latchPin, HIGH); //Pull latch HIGH to stop sending datadelay(100);}}如果需要做8个LED灯或者16个LED灯的跑马灯效果时,数字引脚(Digital Pin)明显会不够⽤;这时我们可以使⽤来实现数字引脚的扩充,这⾥使⽤了这个型号的位移缓存器进⾏实验。

先看下74HC595的引脚说明,共16个引脚,8个输出引脚对应可以控制8个LED,详情参考下图:Q0 - Q7(第15脚,第1-7脚):8位并⾏数据输出GND(第8引脚):地Q7’(第9引脚):串⾏数据输出MR(第10引脚):主复位(低电平)SHCP(第11引脚):数据输⼊时钟线STCP(第12引脚):输出存储器锁存时钟线OE(第13引脚):输出有效(低电平)DS(第14引脚):串⾏数据输⼊VCC(第16引脚):电源74HC595寄存器可以简单的理解为是⼀组8个的开关组,如上图(8个开关控制LED),这组开关的开关⽤0和1来控制,0为关,1为开。

74HC59574HC5951 、描述74HC595是硅结构的CMOS器件,兼容低电压TTL电路,遵守JE DEC标准。

74HC595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SCHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能O E时(为低电平),存储寄存器的数据输出到总线。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

2、特点:8位串行输入/8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率3、输出能力:并行输出,总线驱动;串行输出;标准中等规模集成电路595移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE 时(为低电平),存储寄存器的数据输出到总线。

4、参考数据:CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0)F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压5、引脚说明符号引脚描述Q0…Q7 15,1,7 并行数据输出GND 8 地Q7’ 9 串行数据输出MR 10 主复位(低电平)SHCP 11 移位寄存器时钟输入STCP 12 存储寄存器时钟输入OE 13 输出有效(低电平)DS 14 串行数据输入VCC 16 电源6、功能表输入输出功能SHCP STCP OE MR DS Q7’ Qn××L ↓×L NC MR为低电平时仅仅影响移位寄存器×↑L L ×L L 空移位寄存器到输出寄存器××H L ×L Z 清空移位寄存器,并行输出为高阻状态↑×L H H Q6 NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

扩展Arduino:数字输出端口3 Comments· Posted by flamingoeda in Arduino随着你对Arduino的深入理解和应用,相信很快就会遇到Arduino端口不够用的情况了。

比如你可能需要在你的项目里控制更多的LED或者继电器,但却发现12似乎是一个很难超越的数字;或者你的声音项目里需要更多的电位器,但是Arduino板上6个模拟输入接口的限制却让你捉襟见肘。

如果此时Arduino的处理能力还尚能满足你的要求,只是接口数目不够,能够采用的一种办法就是对Arduino的数字端口和模拟端口进行扩展。

下图就是一个Arduino数字输出端口扩展板,利用它原理上你可以将Arduino上的3个数字输出端口扩展成8个数字输出端口,通俗说来就是3个换8 个;-)实验这块板最简单的办法是用三根数字连接线,分别将该扩展板上的SCK,RCK和SER引脚与传感器扩展板上的数字I/O的8、9和10号引脚相连接:相应的测试代码如下所示:int dataPin = 8; // SERint latchPin = 9; // RCKint clockPin = 10; // SCKvoid setup() {pinMode(latchPin, OUTPUT);pinMode(clockPin, OUTPUT);pinMode(dataPin, OUTPUT);}void loop() {for (int j = 0; j < 255; j++) {// start transmit datadigitalWrite(latchPin, LOW);shiftOut(dataPin, clockPin, MSBFIRST, j);// end transmit datadigitalWrite(latchPin, HIGH);delay(500);}}上述代码中最核心的是对函数shiftOut()的调用,它的作用往扩展板上的8个数字引脚上写一个字节,该字节的每一位分别对应扩展板上8个数字输出I/O引脚中的一个。