msp头文件

- 格式:doc

- 大小:135.00 KB

- 文档页数:27

IAR部分1.新建工作空间2.新建工程,配置工程属性,参考下面说明3.新建文件,例如mytest1.c,注意此时文件并没有添加到工程中,需要手动点击4.右键点击工程,选择ADD,file,然后找到你刚才写的mytest1.c添加进去即可。

5.点击make按钮,生产所需的文件注意:对于MSP430仿真,主要是头文件和输出文件的形式问题1.头文件写#include “io430.h”,不用写具体的型号,这是因为这个文件是条件编译文件,具体的芯片信号是设置工程属性时决定的#include "io430.h"int main (void){volatile unsigned int i;volatile unsigned int count=0;WDTCTL = WDTPW+WDTHOLD; // Stop WDTP4DIR |= BIT4 + BIT5 + BIT6; // P4.4,P4.5,P4.6 set as outputwhile(1) // continuous loop{P4OUT ^= BIT4 + BIT5 + BIT6; // XOR P4.4,P4.5,P4.6for(i=20000;i>0;i--); // Delay}}2.输出文件形式,就是配置工程属性里面决定的。

右键工程,现在option,先配置仿真芯片信号,这个属性决定了IO430.h头文件会选取那个芯片的头文件进行条件编译,主要是存储空间地址问题,如下图所示配置输出文件,输出HEX文件,配置编译器等。

第二部分proteus1。

建立工程,选择芯片2. 连接电路3. 给芯片装载程序,即16进制文件4. 仿真注:芯片型号要与程序对应的IAR调试的程序芯片一致,否则会报错,主要是因为各个芯片的存储器地址不一样,仿真器无法运行。

这种方法使加载第三方开发的程序,生成16进制文件,然后装载仿真器进行仿真方法二,利用Proteus自带的编译器进行仿真新建工程,选择芯片MSP430,选择编译器,选择GCC MSP430编译器然后就可以在PROTEUS中建立c编译后自动加载到芯片中进行仿真。

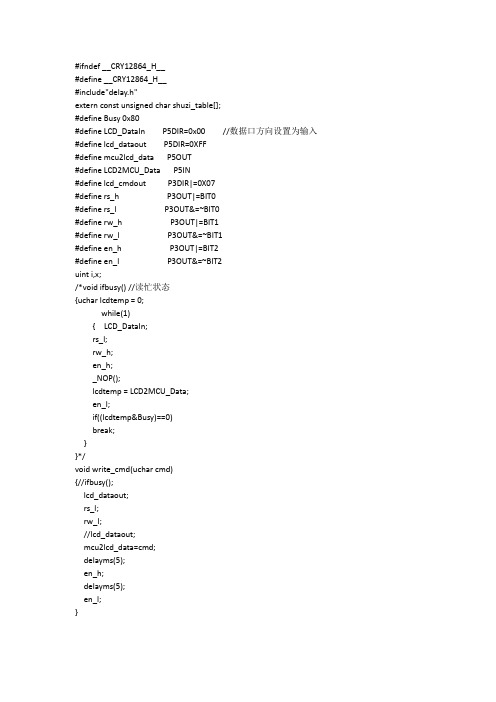

#ifndef __CRY12864_H__#define __CRY12864_H__#include"delay.h"extern const unsigned char shuzi_table[];#define Busy 0x80#define LCD_DataIn P5DIR=0x00 //数据口方向设置为输入#define lcd_dataout P5DIR=0XFF#define mcu2lcd_data P5OUT#define LCD2MCU_Data P5IN#define lcd_cmdout P3DIR|=0X07#define rs_h P3OUT|=BIT0#define rs_l P3OUT&=~BIT0#define rw_h P3OUT|=BIT1#define rw_l P3OUT&=~BIT1#define en_h P3OUT|=BIT2#define en_l P3OUT&=~BIT2uint i,x;/*void ifbusy() //读忙状态{uchar lcdtemp = 0;while(1){ LCD_DataIn;rs_l;rw_h;en_h;_NOP();lcdtemp = LCD2MCU_Data;en_l;if((lcdtemp&Busy)==0)break;}}*/void write_cmd(uchar cmd){//ifbusy();lcd_dataout;rs_l;rw_l;//lcd_dataout;mcu2lcd_data=cmd;delayms(5);en_h;delayms(5);en_l;}void write_data(uchar dat){lcd_dataout;//ifbusy();rs_h;mcu2lcd_data=dat;delayms(5);en_h;delayms(5);en_l;}/******************************************* 函数名称:Ini_Lcd功能:初始化液晶模块参数:无返回值:无********************************************/ /*void Ini_Lcd(void){LCD_CMDOut; //液晶控制端口设置为输出// Delay_Nms(500);Write_Cmd(0x30); //基本指令集Delay_1ms();Write_Cmd(0x02); // 地址归位Delay_1ms();Write_Cmd(0x0c); //整体显示打开,游标关闭Delay_1ms();Write_Cmd(0x01); //清除显示Delay_1ms();Write_Cmd(0x06); //游标右移Delay_1ms();Write_Cmd(0x80); //设定显示的起始地址}*/void init(){en_l;write_cmd(0x30);write_cmd(0x0c);write_cmd(0x01);}void initina2(void) //LCD显示图片(扩展)初始化程序{write_cmd(0x36); //Extended Function Set RE=1: extended instructiondelayms(1); //大于100uS的延时程序write_cmd(0x36); //Extended Function Set:RE=1: extended instruction setdelayms(1); ////大于37uS的延时程序write_cmd(0x3E); //EXFUNCTION(DL=8BITS,RE=1,G=1)delayms(1); //大于100uS的延时程序write_cmd(0x01); //CLEAR SCREENdelayms(1); //大于100uS的延时程序}/*******************************************函数名称:Clear_GDRAM功能:清除液晶GDRAM中的随机数据参数:无返回值:无********************************************/void Clear_GDRAM(void){uchar i,j,k;write_cmd(0x34); //打开扩展指令集i = 0x80;for(j = 0;j < 32;j++){write_cmd(i++);write_cmd(0x80);for(k = 0;k < 16;k++){write_data(0x00);}}i = 0x80;for(j = 0;j < 32;j++){write_cmd(i++);write_cmd(0x88);for(k = 0;k < 16;k++){write_data(0x00);}}write_cmd(0x30); //回到基本指令集}/*******************************************函数名称:Disp_HZ功能:控制液晶显示汉字参数:addr--显示位置的首地址pt--指向显示数据的指针num--显示字符个数返回值:无********************************************/void Disp_HZ(uchar addr,const uchar * pt,uchar num){uchar i;write_cmd(addr);for(i = 0;i < (num*2);i++){write_data(*(pt++));delayms(1);}}/*******************************************函数名称:Draw_TX功能:显示一个16*16大小的图形参数:Yaddr--Y地址Xaddr--X地址dp--指向图形数据存放地址的指针返回值:无********************************************/void Draw_TX(uchar Yaddr,uchar Xaddr,const uchar * dp) {uchar j;uchar k=0;// Write_Cmd(0x01); //清屏,只能清除DDRAMwrite_cmd(0x34); //使用扩展指令集,关闭绘图显示for(j=0;j<16;j++){write_cmd(Yaddr++); //Y地址write_cmd(Xaddr); //X地址write_data(dp[k++]);write_data(dp[k++]);}write_cmd(0x36); //打开绘图显示// Write_Cmd(0x30); //回到基本指令集模式}/*******************************************函数名称:DisplayGraphic功能:在整个液晶屏幕上画图参数:无返回值:无********************************************/void DisplayGraphic(const uchar *adder){int i,j;//*******显示上半屏内容设置for(i=0;i<32;i++) //{write_cmd(0x80 + i); //SET 垂直地址VERTICAL ADDwrite_cmd(0x80); //SET 水平地址HORIZONTAL ADDfor(j=0;j<16;j++){write_data(*adder);adder++;}}//*******显示下半屏内容设置for(i=0;i<32;i++) //{write_cmd((0x80 + i)); //SET 垂直地址VERTICAL ADDwrite_cmd(0x88); //SET 水平地址HORIZONTAL ADDfor(j=0;j<16;j++){write_data(*adder);adder++;}}write_cmd(0x36); //打开绘图显示}#endif。

msp430 如何选择头文件?怎么添加?

使用iar,如果没有头文件,编译肯定通不过,更加不用说继续设计

了,本人使用IAR 进行msp430 开发,选择原因是因为ccs 所需内存太大

了,keil 已经无法满足MSP430 的某些功能了,对于IAR 集成开发环境,我

们从事一个项目开发,首先就是要添加头文件,头文件相信大家都不陌生,

使用C 语言开发的时候我们见到过无数的#include《》和#include 都可以添

加头文件,说明一下:放在自己工程目录下的头文件要用#include

msp430g2553.h ,系统目录下的头文件才用#include《iomsp430g2553.h》,当然你自定义的头文件可以在系统头文件库里面的。

再次使用时新版本的IAR5.31 时发现又不会添加头文件了,想想当时

用的时候也遇到过类似问题,最后也不知是如何解决的,在利用workspace

栏添加时,倒也能添加,只是不再main 分目录下,即便包含了xxx.h 文件,

编译时仍然会提示can no find xxx.h。

有关IAR 教程并总结出两种解决方法。

方法一:将头文件xxx.h 保存在当前工程目录下,通常和main.c 放在

同一个目录。

此时,无需在workspace 里面手工添加,只需要在main.c 或者

在对应的xxx.c 文件中#include xxx.h,编译成功完成后会自动出现在相应的.c。

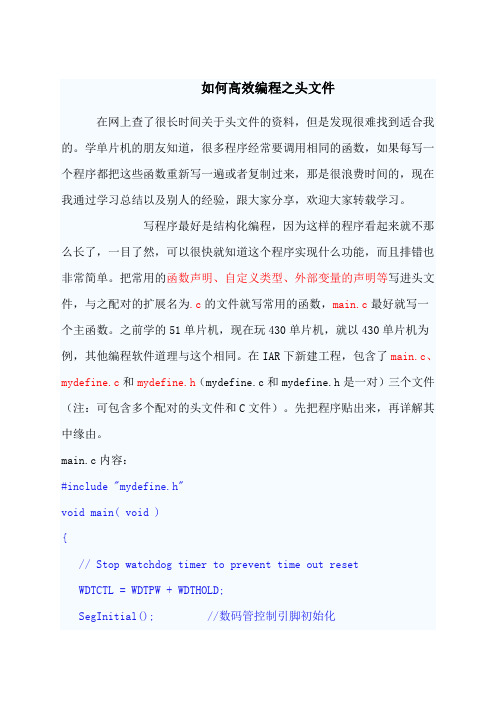

如何高效编程之头文件在网上查了很长时间关于头文件的资料,但是发现很难找到适合我的。

学单片机的朋友知道,很多程序经常要调用相同的函数,如果每写一个程序都把这些函数重新写一遍或者复制过来,那是很浪费时间的,现在我通过学习总结以及别人的经验,跟大家分享,欢迎大家转载学习。

写程序最好是结构化编程,因为这样的程序看起来就不那么长了,一目了然,可以很快就知道这个程序实现什么功能,而且排错也非常简单。

把常用的函数声明、自定义类型、外部变量的声明等写进头文件,与之配对的扩展名为.c的文件就写常用的函数,main.c最好就写一个主函数。

之前学的51单片机,现在玩430单片机,就以430单片机为例,其他编程软件道理与这个相同。

在IAR下新建工程,包含了main.c、mydefine.c和mydefine.h(mydefine.c和mydefine.h是一对)三个文件(注:可包含多个配对的头文件和C文件)。

先把程序贴出来,再详解其中缘由。

main.c内容:#include "mydefine.h"void main( void ){// Stop watchdog timer to prevent time out resetWDTCTL = WDTPW + WDTHOLD;SegInitial(); //数码管控制引脚初始化long m = 0;while(1){disp(m); //显示m的值delay(10);m++;if(m == 1000000)m = 0;}}mydefine.h的内容#ifndef _MYDEFINE_H#define _MYDEFINE_H#include "msp430x14x.h"typedef unsigned int uint;typedef unsigned char uchar;void write_595(uchar dat);void SegInitial(void);void disp(long num);void delays(uint x);void delay(uint x);#endifmydefine.c的内容#include "mydefine.h"#include "msp430x14x.h"/*********************************流水灯74hc595各引脚定义*********************************/#define CLK0 P2OUT &= ~BIT4#define CLK1 P2OUT |= BIT4#define STB0 P2OUT &= ~BIT2#define STB1 P2OUT |= BIT2#define DS0 P2OUT &= ~BIT5#define DS1 P2OUT |= BIT5#define LEDOFF P5OUT = 0x00uchar dis_num[]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90,0x88,0x83,0xc6,0xa1,0x86,0x8e};//数码管0~F共阳编码uchar bitnum[]={0x01,0x02,0x04,0x08,0x10,0x20}; //数码管位选uchardispbuf[6];//数码管显示缓冲区//以下是延时函数void delay(uint x){uint a,b;for(a=x;a>0;a--)for(b=10000;b>0;b--);}//控制流水灯,使用P2.2(STB),P2.4(CLK),P2.5(DS) void write_595(uchar dat){uint n;for(n = 0;n<8;n++){if((dat&0x80) == 0x80)DS1;elseDS0;dat <<= 1;CLK0;CLK1;}STB1;STB0;}/*****************************************数码管显示初始化函数*****************************************/ void SegInitial(void){P5DIR = 0XFF;P4DIR = 0XFF;P5OUT = 0X00;P4OUT = 0X00;}/****************************************数码管防重影延时函数*****************************************/ void delays(uint x){for(;x>0;x--);}/*****************************************数码管显示函数位选 P5.0~P5.5段选 P4*****************************************/void disp(long num){uint i;dispbuf[0] = num%10;dispbuf[1] = num/10%10;dispbuf[2] = num/100%10;dispbuf[3] = num/1000%10;dispbuf[4] = num/10000%10;dispbuf[5] = num/100000%10;for(i=0;i<6;i++){P4OUT = dis_num[dispbuf[i]];P5OUT = bitnum[i];delays(400);P5OUT=0X00;}}首先看main.c里面就写了一个主函数,它告诉读者该程序的主要功能。

![[最新]msp430头文件说明说明](https://img.taocdn.com/s1/m/57f048d8a0c7aa00b52acfc789eb172ded6399f7.png)

msp430头文件解释说明//1MSP430F149祥解对头文件做了比较详细的注释,记不清寄存器的人可以看看#ifndef __msp430x14x#define __msp430x14x/********************************************************** *** STANDARD BITS*********************************************************** */#define BIT0 0x0001#define BIT1 0x0002#define BIT2 0x0004#define BIT3 0x0008#define BIT4 0x0010#define BIT5 0x0020#define BIT6 0x0040#define BIT7 0x0080#define BIT8 0x0100#define BIT9 0x0200#define BITA 0x0400#define BITB 0x0800#define BITC 0x1000#define BITD 0x2000#define BITE 0x4000#define BITF 0x8000/********************************************************** *** STATUS REGISTER BITS*********************************************************** */#define C 0x0001#define Z 0x0002#define N 0x0004#define V 0x0100#define GIE 0x0008#define CPUOFF 0x0010#define OSCOFF 0x0020#define SCG0 0x0040#define SCG1 0x0080/* Low Power Modes coded with Bits 4-7 in SR */#ifndef __IAR_SYSTEMS_ICC /* Begin #defines for assembler */#define LPM0 CPUOFF#define LPM1 SCG0+CPUOFF#define LPM2 SCG1+CPUOFF#define LPM3 SCG1+SCG0+CPUOFF#define LPM4 SCG1+SCG0+OSCOFF+CPUOFF/* End #defines for assembler */#else /* Begin #defines for C */#define LPM0_bits CPUOFF#define LPM1_bits SCG0+CPUOFF#define LPM2_bits SCG1+CPUOFF#define LPM3_bits SCG1+SCG0+CPUOFF#define LPM4_bits SCG1+SCG0+OSCOFF+CPUOFF#include <In430.h>#define LPM0 _BIS_SR(LPM0_bits) /* Enter Low Power Mode 0 */#define LPM0_EXIT _BIC_SR(LPM0_bits) /* Exit Low Power Mode 0 */#define LPM1 _BIS_SR(LPM1_bits) /* Enter Low Power Mode 1 */#define LPM1_EXIT _BIC_SR(LPM1_bits) /* Exit Low Power Mode 1 */#define LPM2 _BIS_SR(LPM2_bits) /* Enter Low Power Mode 2 */#define LPM2_EXIT _BIC_SR(LPM2_bits) /* Exit Low Power Mode 2 */#define LPM3 _BIS_SR(LPM3_bits) /* Enter Low Power Mode 3 */#define LPM3_EXIT _BIC_SR(LPM3_bits) /* Exit Low Power Mode 3 */#define LPM4 _BIS_SR(LPM4_bits) /* Enter Low Power Mode 4 */#define LPM4_EXIT _BIC_SR(LPM4_bits) /* Exit Low Power Mode 4 */#endif /* End #defines for C *//********************************************************** *** PERIPHERAL FILE MAP*********************************************************** *//********************************************************** *** 特殊功能寄存器地址和控制位*********************************************************** *//*中断使能1*/#define IE1_ 0x0000sfrb IE1 = IE1_;#define WDTIE 0x01 /*看门狗中断使能*/#define OFIE 0x02 /*外部晶振故障中断使能*/#define NMIIE 0x10 /*非屏蔽中断使能*/#define ACCVIE 0x20 /*可屏蔽中断使能/flash 写中断错误*/#define URXIE0 0x40 /*串口0接收中断使能*/#define UTXIE0 0x80 /*串口0发送中断使能*//*中断标志1*/#define IFG1_ 0x0002sfrb IFG1 = IFG1_;#define WDTIFG 0x01 /*看门狗中断标志*/#define OFIFG 0x02 /*外部晶振故障中断标志*/ #define NMIIFG 0x10 /*非屏蔽中断标志*/#define URXIFG0 0x40 /*串口0接收中断标志*/#define UTXIFG0 0x80 /*串口0发送中断标志*//* 中断模式使能1 */#define ME1_ 0x0004sfrb ME1 = ME1_;#define URXE0 0x40 /* 串口0接收中断模式使能 */#define USPIE0 0x40 /* 同步中断模式使能*/#define UTXE0 0x80 /* 串口0发送中断模式使能 *//* 中断使能2 */#define IE2_ 0x0001sfrb IE2 = IE2_;#define URXIE1 0x10 /* 串口1接收中断使能*/#define UTXIE1 0x20 /* 串口1发送中断使能*//* 中断标志2 */#define IFG2_ 0x0003sfrb IFG2 = IFG2_;#define URXIFG1 0x10 /* 串口1接收中断标志*/#define UTXIFG1 0x20 /* 串口1发送中断标志*//* 中断模式使能2 */#define ME2_ 0x0005sfrb ME2 = ME2_;#define URXE1 0x10 /* 串口1接收中断模式使能 */#define USPIE1 0x10 /* 同步中断模式使能*/#define UTXE1 0x20 /* 串口1发送中断模式使能 *//********************************************************** *** 看门狗定时器的寄存器定义*********************************************************** */#define WDTCTL_ 0x0120sfrw WDTCTL = WDTCTL_;#define WDTIS0 0x0001 /*选择WDTCNT的四个输出端之一*/#define WDTIS1 0x0002 /*选择WDTCNT的四个输出端之一*/#define WDTSSEL 0x0004 /*选择WDTCNT的时钟源*/#define WDTCNTCL 0x0008 /*清除WDTCNT端: 为1时从0开始计数*/#define WDTTMSEL 0x0010 /*选择模式 0: 看门狗模式; 1: 定时器模式*/#define WDTNMI 0x0020 /*选择NMI/RST 引脚功能 0:为 RST; 1:为NMI*/#define WDTNMIES 0x0040 /*WDTNMI=1时.选择触发延 0:为上升延 1:为下降延*/#define WDTHOLD 0x0080 /*停止看门狗定时器工作 0:启动;1:停止*/#define WDTPW 0x5A00 /* 写密码:高八位*//* SMCLK= 1MHz定时器模式 */#define WDT_MDLY_32 WDTPW+WDTTMSEL+WDTCNTCL /* TSMCLK*2POWER15=32ms 复位状态 */#define WDT_MDLY_8 WDTPW+WDTTMSEL+WDTCNTCL+WDTIS0 /* TSMCLK*2POWER13=8.192ms " */#define WDT_MDLY_0_5 WDTPW+WDTTMSEL+WDTCNTCL+WDTIS1 /* TSMCLK*2POWER9=0.512ms " */#define WDT_MDLY_0_064WDTPW+WDTTMSEL+WDTCNTCL+WDTIS1+WDTIS0 /*TSMCLK*2POWER6=0.512ms " *//* ACLK=32.768KHz 定时器模式*/#define WDT_ADLY_1000 WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL /* TACLK*2POWER15=1000ms " */#define WDT_ADLY_250WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS0 /*TACLK*2POWER13=250ms " */#define WDT_ADLY_16WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS1 /*TACLK*2POWER9=16ms " */#define WDT_ADLY_1_9WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS1+WDTIS0 /*TACLK*2POWER6=1.9ms " *//* SMCLK=1MHz看门狗模式 */#define WDT_MRST_32 WDTPW+WDTCNTCL /* TSMCLK*2POWER15=32ms 复位状态 */#define WDT_MRST_8 WDTPW+WDTCNTCL+WDTIS0 /* TSMCLK*2POWER13=8.192ms " */#define WDT_MRST_0_5 WDTPW+WDTCNTCL+WDTIS1 /* TSMCLK*2POWER9=0.512ms " */#define WDT_MRST_0_064 WDTPW+WDTCNTCL+WDTIS1+WDTIS0 /* TSMCLK*2POWER6=0.512ms " *//* ACLK=32KHz看门狗模式 */#define WDT_ARST_1000 WDTPW+WDTCNTCL+WDTSSEL /* TACLK*2POWER15=1000ms " */#define WDT_ARST_250 WDTPW+WDTCNTCL+WDTSSEL+WDTIS0 /* TACLK*2POWER13=250ms " */#define WDT_ARST_16 WDTPW+WDTCNTCL+WDTSSEL+WDTIS1 /* TACLK*2POWER9=16ms " */#define WDT_ARST_1_9WDTPW+WDTCNTCL+WDTSSEL+WDTIS1+WDTIS0 /*TACLK*2POWER6=1.9ms " *//************************************************************硬件乘法器的寄存器定义************************************************************/#define MPY_ 0x0130 /* 无符号乘法 */sfrw MPY = MPY_;#define MPYS_ 0x0132 /* 有符号乘法*/sfrw MPYS = MPYS_;#define MAC_ 0x0134 /* 无符号乘加 */sfrw MAC = MAC_;#define MACS_ 0x0136 /* 有符号乘加 */sfrw MACS = MACS_;#define OP2_ 0x0138 /* 第二乘数 */sfrw OP2 = OP2_;#define RESLO_ 0x013A /* 低6位结果寄存器 */sfrw RESLO = RESLO_;#define RESHI_ 0x013C /* 高6位结果寄存器 */sfrw RESHI = RESHI_;#define SUMEXT_ 0x013E /*结果扩展寄存器 */const sfrw SUMEXT = SUMEXT_;/********************************************************** *** DIGITAL I/O Port1/2 寄存器定义有中断功能*********************************************************** */#define P1IN_ 0x0020 /* P1 输入寄存器 */const sfrb P1IN = P1IN_;#define P1OUT_ 0x0021 /* P1 输出寄存器 */sfrb P1OUT = P1OUT_;#define P1DIR_ 0x0022 /* P1 方向选择寄存器 */sfrb P1DIR = P1DIR_;#define P1IFG_ 0x0023 /* P1 中断标志寄存器*/sfrb P1IFG = P1IFG_;#define P1IES_ 0x0024 /* P1 中断边沿选择寄存器*/sfrb P1IES = P1IES_;#define P1IE_ 0x0025 /* P1 中断使能寄存器 */sfrb P1IE = P1IE_;#define P1SEL_ 0x0026 /* P1 功能选择寄存器*/ sfrb P1SEL = P1SEL_;#define P2IN_ 0x0028 /* P2 输入寄存器 */const sfrb P2IN = P2IN_;#define P2OUT_ 0x0029 /* P2 输出寄存器 */sfrb P2OUT = P2OUT_;#define P2DIR_ 0x002A /* P2 方向选择寄存器 */sfrb P2DIR = P2DIR_;#define P2IFG_ 0x002B /* P2 中断标志寄存器 */sfrb P2IFG = P2IFG_;#define P2IES_ 0x002C /* P2 中断边沿选择寄存器*/sfrb P2IES = P2IES_;#define P2IE_ 0x002D /* P2 中断使能寄存器 */sfrb P2IE = P2IE_;#define P2SEL_ 0x002E /* P2 功能选择寄存器 */ sfrb P2SEL = P2SEL_;/********************************************************** *** DIGITAL I/O Port3/4寄存器定义无中断功能*********************************************************** */#define P3IN_ 0x0018 /* P3 输入寄存器 */const sfrb P3IN = P3IN_;#define P3OUT_ 0x0019 /* P3 输出寄存器 */sfrb P3OUT = P3OUT_;#define P3DIR_ 0x001A /* P3 方向选择寄存器 */sfrb P3DIR = P3DIR_;#define P3SEL_ 0x001B /* P3 功能选择寄存器*/ sfrb P3SEL = P3SEL_;#define P4IN_ 0x001C /* P4 输入寄存器 */const sfrb P4IN = P4IN_;#define P4OUT_ 0x001D /* P4 输出寄存器 */sfrb P4OUT = P4OUT_;#define P4DIR_ 0x001E /* P4 方向选择寄存器 */sfrb P4DIR = P4DIR_;#define P4SEL_ 0x001F /* P4 功能选择寄存器 */ sfrb P4SEL = P4SEL_;/********************************************************** *** DIGITAL I/O Port5/6 I/O口寄存器定义PORT5和6 无中断功能*********************************************************** */#define P5IN_ 0x0030 /* P5 输入寄存器 */const sfrb P5IN = P5IN_;#define P5OUT_ 0x0031 /* P5 输出寄存器*/sfrb P5OUT = P5OUT_;#define P5DIR_ 0x0032 /* P5 方向选择寄存器*/sfrb P5DIR = P5DIR_;#define P5SEL_ 0x0033 /* P5 功能选择寄存器*/ sfrb P5SEL = P5SEL_;#define P6IN_ 0x0034 /* P6 输入寄存器 */const sfrb P6IN = P6IN_;#define P6OUT_ 0x0035 /* P6 输出寄存器*/sfrb P6OUT = P6OUT_;#define P6DIR_ 0x0036 /* P6 方向选择寄存器*/sfrb P6DIR = P6DIR_;#define P6SEL_ 0x0037 /* P6 功能选择寄存器*/ sfrb P6SEL = P6SEL_;//2/********************************************************** *** USART 串口寄存器"UCTL","UTCTL","URCTL"定义的各个位可串口1 串口2公用*********************************************************** *//* UCTL 串口控制寄存器*/#define PENA 0x80 /*校验允许位*/#define PEV 0x40 /*偶校验为0时为奇校验*/#define SPB 0x20 /*停止位为2 为0时停止位为1*/#define CHAR 0x10 /*数据位为8位为0时数据位为7位*/#define LISTEN 0x08 /*自环模式(发数据同时在把发的数据接收回来)*/#define SYNC 0x04 /*同步模式为0异步模式*/#define MM 0x02 /*为1时地址位多机协议(异步) 主机模式(同步);为0时线路空闲多机协议(异步) 从机模式(同步)*/#define SWRST 0x01 /*控制位*//* UTCTL 串口发送控制寄存器*/#define CKPH 0x80 /*时钟相位控制位(只同步方式用)为1时时钟UCLK延时半个周期*/#define CKPL 0x40 /*时钟极性控制位为1时异步与UCLK相反;同步下降延有效*/#define SSEL1 0x20 /*时钟源选择位:与SSEL0组合为0,1,2,3四种方式*/#define SSEL0 0x10 /*"0"选择外部时钟,"1"选择辅助时钟,"2","3"选择系统子时钟 */#define URXSE 0x08 /*接收触发延控制位(只在异步方式下用)*/#define TXWAKE 0x04 /*多处理器通信传送控制位(只在异步方式下用)*/#define STC 0x02 /*外部引脚STE选择位为0时为4线模式为1时为3线模式*/#define TXEPT 0x01 /*发送器空标志*//* URCTL 串口接收控制寄存器同步模式下只用两位:FE和OE*/#define FE 0x80 /*帧错标志*/ #define PE 0x40 /*校验错标志位*/#define OE 0x20 /*溢出标志位*/#define BRK 0x10 /*打断检测位*/#define URXEIE 0x08 /*接收出错中断允许位*/#define URXWIE 0x04 /*接收唤醒中断允许位*/#define RXWAKE 0x02 /*接收唤醒检测位*/ #define RXERR 0x01 /*接收错误标志位*//********************************************************** *** USART 0 串口0寄存器定义*********************************************************** */#define U0CTL_ 0x0070 /* 串口0基本控制寄存器*/sfrb U0CTL = U0CTL_;#define U0TCTL_ 0x0071 /* 串口0发送控制寄存器 */sfrb U0TCTL = U0TCTL_;#define U0RCTL_ 0x0072 /* 串口0接收控制寄存器 */sfrb U0RCTL = U0RCTL_;#define U0MCTL_ 0x0073 /* 波特率调整寄存器 */sfrb U0MCTL = U0MCTL_;#define U0BR0_ 0x0074 /* 波特率选择寄存器0 */sfrb U0BR0 = U0BR0_;#define U0BR1_ 0x0075 /* 波特率选择寄存器1 */sfrb U0BR1 = U0BR1_;#define U0RXBUF_ 0x0076 /* 接收缓存寄存器 */const sfrb U0RXBUF = U0RXBUF_;#define U0TXBUF_ 0x0077 /* 发送缓存寄存器 */sfrb U0TXBUF = U0TXBUF_;/* 改变的寄存器名定义 */#define UCTL0_ 0x0070 /* UART 0 Control */sfrb UCTL0 = UCTL0_;#define UTCTL0_ 0x0071 /* UART 0 Transmit Control */sfrb UTCTL0 = UTCTL0_;#define URCTL0_ 0x0072 /* UART 0 Receive Control */sfrb URCTL0 = URCTL0_;#define UMCTL0_ 0x0073 /* UART 0 Modulation Control */sfrb UMCTL0 = UMCTL0_;#define UBR00_ 0x0074 /* UART 0 Baud Rate 0 */ sfrb UBR00 = UBR00_;#define UBR10_ 0x0075 /* UART 0 Baud Rate 1 */sfrb UBR10 = UBR10_;#define RXBUF0_ 0x0076 /* UART 0 Receive Buffer */const sfrb RXBUF0 = RXBUF0_;#define TXBUF0_ 0x0077 /* UART 0 Transmit Buffer */ sfrb TXBUF0 = TXBUF0_;#define UCTL_0_ 0x0070 /* UART 0 Control */sfrb UCTL_0 = UCTL_0_;#define UTCTL_0_ 0x0071 /* UART 0 Transmit Control */sfrb UTCTL_0 = UTCTL_0_;#define URCTL_0_ 0x0072 /* UART 0 Receive Control */sfrb URCTL_0 = URCTL_0_;#define UMCTL_0_ 0x0073 /* UART 0 Modulation Control */sfrb UMCTL_0 = UMCTL_0_;#define UBR0_0_ 0x0074 /* UART 0 Baud Rate 0 */sfrb UBR0_0 = UBR0_0_;#define UBR1_0_ 0x0075 /* UART 0 Baud Rate 1 */sfrb UBR1_0 = UBR1_0_;#define RXBUF_0_ 0x0076 /* UART 0 Receive Buffer */ const sfrb RXBUF_0 = RXBUF_0_;#define TXBUF_0_ 0x0077 /* UART 0 Transmit Buffer */sfrb TXBUF_0 = TXBUF_0_;/********************************************************** *** USART 1 串口1寄存器定义*********************************************************** */#define U1CTL_ 0x0078 /* 串口1基本控制寄存器*/sfrb U1CTL = U1CTL_;#define U1TCTL_ 0x0079 /* 串口1发送控制寄存器 */sfrb U1TCTL = U1TCTL_;#define U1RCTL_ 0x007A /* 串口1接收控制寄存器 */sfrb U1RCTL = U1RCTL_;#define U1MCTL_ 0x007B /* 波特率调整控制寄存器 */sfrb U1MCTL = U1MCTL_;#define U1BR0_ 0x007C /* 波特率选择寄存器0 */sfrb U1BR0 = U1BR0_;#define U1BR1_ 0x007D /* 波特率选择寄存器1 */sfrb U1BR1 = U1BR1_;#define U1RXBUF_ 0x007E /* 接收缓存 */const sfrb U1RXBUF = U1RXBUF_;#define U1TXBUF_ 0x007F /* 发送缓存 */ sfrb U1TXBUF = U1TXBUF_;/* 改变的寄存器名定义 */#define UCTL1_ 0x0078 /* UART 1 C。

自制51单片机常用头文件

#ifndef __COM_H__

#define __COM_H__

#define uchar unsigned char

#define uint unsigned int

#define XTAL 11059200 // CUP 晶振频率

#define baudrate 9600 // 通信波特率

void sendmsg(uint ps)

{

SBUF = ps; // 要发送的字符放入缓冲区

while(TI == 0); // 一直等等,直到发送完数据为止

TI = 0;

}

uint rcvmsg(void) //调用此函数前,要先调用RI,查看是否收到数据,确定已收到的话,再调用此函数

{

RI=0; //要先将RI=0再返回,否则,返回后,RI=0这句就不执行了。

return SBUF;

}

void initcom(void)

{

TMOD = 0x20; // 定时器1工作于8位自动重载模式, 用于产生波特率

TH1=(unsigned char)(256 - (XTAL / (32L * 12L * baudrate)));

TL1=(unsigned char)(256 - (XTAL / (32L * 12L * baudrate))); // 定时器1赋初值

SM0 = 0; //串口工作方式控制

SM1 = 1; //串口工作方式控制 //这两个共同控制了串口工作方式为 0;

REN = 1; //串口接收允许

PCON = 0x00;

TR1 = 1; //允许串口接收

ES = 0; //关闭串口中断

}

#endif。

MSP430单片机C语言的基本结构王晓宁2013/1/28随着单片机处理速度的加快和存储容量的加大以及相应的开发软件中增强的代码优化功能,用C语言编写的程序其代码效率和运行速度已堪与汇编程序相媲美,而且C语言程序因其平易性、结构化、易维护性和可移植性而日益广泛地应用于单片机的开发中。

用C语言编程时必须结合单片机的特点,不同品牌、不同系列或不同型号的单片机其内部资源、寄存器名称等都会不同,因此其软件的开发必须结合实际的硬件来进行。

但C语言的程序结构还是有许多共性的,下面结合MSP430单片机大致说一下C程序的基本结构。

C语言的程序结构还是比较规范的,一般包括头文件、宏定义、变量定义、函数定义、一个主函数main( )、以及中断处理函数等。

在多文件的管理中,还包括自定义的头文件等。

根据不同的情形,一个完整的C程序可以有不同的具体结构,但其框架基本上还是固定的。

下面通过几个简单的小例子来看一下C 程序的几种结构。

在此之前,先说一下C中的赋值方式。

很多情况下,C程序就是在那儿完成一些赋值操作。

|= 是“或”运算,&=是“与”运算,^= 是“异或”运算。

比如BIT0已经在430的头文件里定义为:BIT0=0x0001,0x0001是16进制计数,转成2进制就是(低八位),那么P1OUT|=BIT0,是一个什么结果?这是一个“或”运算(英文称or)。

首先P1OUT是一个在头文件中定义好的寄存器,是8位的,因此,我们可以把P1OUT就当成一个变量名好了,只不过这个变量是在头文件中定义的,我们直接拿来用即可。

P1OUT 的取值就是在~之间(二进制)。

因此不管P1OUT原先的值是多少,P1OUT|=BIT0就是(设P1OUT原先的值为xxxxxxxx)xxxxxxxx跟进行或运算,最低位(即BIT0)的值肯定是1的,而对其它位没有影响。

因此这样赋值后P1OUT=xxxxxxx1,达到了让BIT0位等于1(称为“置1”)的目的。

1、#define BIT0 (0×0001) //(0×0001)不是地址,而是一个16进制数值。

例1、P3DIR |= BIT3;实际上也可以写成P3DIR |= 0×0008;意思是将P3口的默认上电值0×0000和0×0008相与,设置P3口的第三位(即P3.3)管脚作输出使用。

例2、WDTCTL = WDTPW + WDTHOLD;实际上就是WDTCTL=0×5A80;你可以在头文件中查到#define WDTPW (0×5A00)和#define WDTHOLD (0×0080)。

WDTCTL是看门狗的控制寄存器,在msp430的User’Guide中有说明:当它的值为0×5A80时停止看门狗定时。

那为什么我们不直接写成WDTCTL=0×5A80;呢?这样的话程序的可读性会很差。

0×5A80只是一个数值,当你下次再看你写的程序,或者别人读你的程序时,就不明白WDTCTL=0×5A80;的意思了。

如果写成WDTCTL = WDTPW + WDTHOLD;就好理解多了:WDTPW(Watchdog timer password,看门狗的密码,WDTCTL的高8位):只有WDTCTL的高8位为0×5A时才能对WDTCTL寄存器进行写操作。

WDTHOLD(Watchdog timer hold,WDTCTL的第7位):当WDTCTL的第7位为1时,停止看门狗计时。

这样我们通过PW,HOLD就可以轻松的知道WDTCTL = WDTPW + WDTHOLD;是做什么的了。

可以看出msp430的头文件是很人性化的。

2、当然也有表示地址的,例如,头文件中有以下部分:#ifdef __IAR_SYSTEMS_ASM__#define DEFC(name, address) sfrb name = address#define DEFW(name, address) sfrw name = address;///运用了可变参数宏的宏定义格式:#define 宏符号名(参数表) 宏体;;宏体中就是写出参数表中各个//参数之间的关系。

* Standard register and bit definitions for the Texas Instruments* MSP430 microcontroller.** This file supports assembler and C development for* MSP430x14x devices.** Texas Instruments, Version 2.4** Rev. 1.2, Additional Timer B bit definitions.* Renamed XTOFF to XT2OFF.* Rev. 1.3, Removed leading 0 to aviod interpretation as octal* values under C* Included <In430.h> rather than "In430.h"* Rev. 1.4, Corrected LPMx_EXIT to reference new intrinsic _BIC_SR_IRQ* Changed TAIV and TBIV to be read-only* Rev. 1.5, Enclose all #define statements with parentheses* Rev. 1.6, Defined vectors for USART (in addition to UART)* Rev. 1.7, Added USART special function labels (UxME, UxIE, UxIFG)* Rev. 2.1, Alignment of defintions in Users Guide and of version numbers* Rev. 2.2, Fixed type in ADC12 bit definitions (replaced ADC10 with ADC12)* Rev. 2.3, Removed unused def of TASSEL2 / TBSSEL2* Rev. 2.4, added definitions for Interrupt Vectors xxIV*********************************************************************/#ifndef __msp430x14x#define __msp430x14x#ifdef __IAR_SYSTEMS_ICC__#ifndef _SYSTEM_BUILD#pragma system_include#endif#endif#if (((__TID__ >> 8) & 0x7F) != 0x2b) /* 0x2b = 43 dec */#error msp430x14x.h file for use with ICC430/A430 only#endif#ifdef __IAR_SYSTEMS_ICC__#include <in430.h>#pragma language=extended#define DEFC(name, address) __no_init volatile unsigned char name @ address;#define DEFW(name, address) __no_init volatile unsigned short name @ address; #define DEFXC volatile unsigned char#define DEFXW volatile unsigned short#endif /* __IAR_SYSTEMS_ICC__ */#ifdef __IAR_SYSTEMS_ASM__#define DEFC(name, address) sfrb name = address;#define DEFW(name, address) sfrw name = address;#endif /* __IAR_SYSTEMS_ASM__*/#ifdef __cplusplus#define READ_ONL Y#else#define READ_ONL Y const#endif/************************************************************* STANDARD BITS************************************************************/#define BIT0 (0x0001)#define BIT1 (0x0002)#define BIT2 (0x0004)#define BIT3 (0x0008)#define BIT4 (0x0010)#define BIT5 (0x0020)#define BIT6 (0x0040)#define BIT7 (0x0080)#define BIT8 (0x0100)#define BIT9 (0x0200)#define BITA (0x0400)#define BITB (0x0800)#define BITC (0x1000)#define BITD (0x2000)#define BITE (0x4000)#define BITF (0x8000)/************************************************************* STATUS REGISTER BITS************************************************************/#define C (0x0001)#define Z (0x0002)#define N (0x0004)#define V (0x0100)#define GIE (0x0008)#define CPUOFF (0x0010)#define OSCOFF (0x0020)#define SCG0 (0x0040)#define SCG1 (0x0080)/* Low Power Modes coded with Bits 4-7 in SR */#ifndef __IAR_SYSTEMS_ICC /* Begin #defines for assembler */#define LPM0 (CPUOFF)#define LPM1 (SCG0+CPUOFF)#define LPM2 (SCG1+CPUOFF)#define LPM3 (SCG1+SCG0+CPUOFF)#define LPM4 (SCG1+SCG0+OSCOFF+CPUOFF)/* End #defines for assembler */#else /* Begin #defines for C */#define LPM0_bits (CPUOFF)#define LPM1_bits (SCG0+CPUOFF)#define LPM2_bits (SCG1+CPUOFF)#define LPM3_bits (SCG1+SCG0+CPUOFF)#define LPM4_bits (SCG1+SCG0+OSCOFF+CPUOFF)#include <In430.h>#define LPM0 _BIS_SR(LPM0_bits) /* Enter Low Power Mode 0 */ #define LPM0_EXIT _BIC_SR_IRQ(LPM0_bits) /* Exit Low Power Mode 0 */ #define LPM1 _BIS_SR(LPM1_bits) /* Enter Low Power Mode 1 */ #define LPM1_EXIT _BIC_SR_IRQ(LPM1_bits) /* Exit Low Power Mode 1 */ #define LPM2 _BIS_SR(LPM2_bits) /* Enter Low Power Mode 2 */ #define LPM2_EXIT _BIC_SR_IRQ(LPM2_bits) /* Exit Low Power Mode 2 */ #define LPM3 _BIS_SR(LPM3_bits) /* Enter Low Power Mode 3 */ #define LPM3_EXIT _BIC_SR_IRQ(LPM3_bits) /* Exit Low Power Mode 3 */ #define LPM4 _BIS_SR(LPM4_bits) /* Enter Low Power Mode 4 */ #define LPM4_EXIT _BIC_SR_IRQ(LPM4_bits) /* Exit Low Power Mode 4 */ #endif /* End #defines for C *//************************************************************* PERIPHERAL FILE MAP************************************************************//************************************************************* SPECIAL FUNCTION REGISTER ADDRESSES + CONTROL BITS************************************************************/#define IE1_ (0x0000) /* Interrupt Enable 1 */DEFC( IE1 , IE1_)#define U0IE IE1 /* UART0 Interrupt Enable Register */ #define WDTIE (0x01)#define OFIE (0x02)#define NMIIE (0x10)#define ACCVIE (0x20)#define URXIE0 (0x40)#define UTXIE0 (0x80)#define IFG1_ (0x0002) /* Interrupt Flag 1 */DEFC( IFG1 , IFG1_)#define U0IFG IFG1 /* UART0 Interrupt Flag Register */ #define WDTIFG (0x01)#define OFIFG (0x02)#define NMIIFG (0x10)#define URXIFG0 (0x40)#define UTXIFG0 (0x80)#define ME1_ (0x0004) /* Module Enable 1 */DEFC( ME1 , ME1_)#define U0ME ME1 /* UART0 Module Enable Register */ #define URXE0 (0x40)#define UTXE0 (0x80)#define USPIE0 (0x40)#define IE2_ (0x0001) /* Interrupt Enable 2 */DEFC( IE2 , IE2_)#define U1IE IE2 /* UART1 Interrupt Enable Register */ #define URXIE1 (0x10)#define UTXIE1 (0x20)#define IFG2_ (0x0003) /* Interrupt Flag 2 */DEFC( IFG2 , IFG2_)#define U1IFG IFG2 /* UART1 Interrupt Flag Register */ #define URXIFG1 (0x10)#define UTXIFG1 (0x20)#define ME2_ (0x0005) /* Module Enable 2 */DEFC( ME2 , ME2_)#define U1ME ME2 /* UART1 Module Enable Register */#define URXE1 (0x10)#define UTXE1 (0x20)#define USPIE1 (0x10)/************************************************************* WATCHDOG TIMER************************************************************/#define __MSP430_HAS_WDT__ /* Definition to show that Module is available */#define WDTCTL_ (0x0120) /* Watchdog Timer Control */DEFW( WDTCTL , WDTCTL_)/* The bit names have been prefixed with "WDT" */#define WDTIS0 (0x0001)#define WDTIS1 (0x0002)#define WDTSSEL (0x0004)#define WDTCNTCL (0x0008)#define WDTTMSEL (0x0010)#define WDTNMI (0x0020)#define WDTNMIES (0x0040)#define WDTHOLD (0x0080)#define WDTPW (0x5A00)/* WDT-interval times [1ms] coded with Bits 0-2 *//* WDT is clocked by fSMCLK (assumed 1MHz) */#define WDT_MDL Y_32 (WDTPW+WDTTMSEL+WDTCNTCL) /* 32ms interval (default) */#define WDT_MDL Y_8 (WDTPW+WDTTMSEL+WDTCNTCL+WDTIS0) /* 8ms " */#define WDT_MDL Y_0_5 (WDTPW+WDTTMSEL+WDTCNTCL+WDTIS1) /* 0.5ms " */#define WDT_MDL Y_0_064 (WDTPW+WDTTMSEL+WDTCNTCL+WDTIS1+WDTIS0) /* 0.064ms " *//* WDT is clocked by fACLK (assumed 32KHz) */#define WDT_ADL Y_1000 (WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL) /* 1000ms " */#define WDT_ADL Y_250 (WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS0) /* 250ms " */#define WDT_ADL Y_16 (WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS1) /* 16ms " */#define WDT_ADL Y_1_9 (WDTPW+WDTTMSEL+WDTCNTCL+WDTSSEL+WDTIS1+WDTIS0) /* 1.9ms " *//* Watchdog mode -> reset after expired time *//* WDT is clocked by fSMCLK (assumed 1MHz) */#define WDT_MRST_32 (WDTPW+WDTCNTCL) /* 32ms interval (default) */#define WDT_MRST_8 (WDTPW+WDTCNTCL+WDTIS0) /* 8ms " */#define WDT_MRST_0_5 (WDTPW+WDTCNTCL+WDTIS1) /* 0.5ms " */#define WDT_MRST_0_064 (WDTPW+WDTCNTCL+WDTIS1+WDTIS0) /* 0.064ms " *//* WDT is clocked by fACLK (assumed 32KHz) */#define WDT_ARST_1000 (WDTPW+WDTCNTCL+WDTSSEL) /* 1000ms " */#define WDT_ARST_250 (WDTPW+WDTCNTCL+WDTSSEL+WDTIS0) /* 250ms " */#define WDT_ARST_16 (WDTPW+WDTCNTCL+WDTSSEL+WDTIS1) /* 16ms " */#define WDT_ARST_1_9 (WDTPW+WDTCNTCL+WDTSSEL+WDTIS1+WDTIS0) /* 1.9ms " *//* INTERRUPT CONTROL *//* These two bits are defined in the Special Function Registers *//* #define WDTIE 0x01 *//* #define WDTIFG 0x01 *//************************************************************* HARDWARE MULTIPLIER************************************************************/#define __MSP430_HAS_MPY__ /* Definition to show that Module is available */#define MPY_ (0x0130) /* Multiply Unsigned/Operand 1 */DEFW( MPY , MPY_)#define MPYS_ (0x0132) /* Multiply Signed/Operand 1 */DEFW( MPYS , MPYS_)#define MAC_ (0x0134) /* Multiply Unsigned and Accumulate/Operand 1 */ DEFW( MAC , MAC_)#define MACS_ (0x0136) /* Multiply Signed and Accumulate/Operand 1 */ DEFW( MACS , MACS_)#define OP2_ (0x0138) /* Operand 2 */DEFW( OP2 , OP2_)#define RESLO_ (0x013A) /* Result Low Word */DEFW( RESLO , RESLO_)#define RESHI_ (0x013C) /* Result High Word */DEFW( RESHI , RESHI_)#define SUMEXT_ (0x013E) /* Sum Extend */READ_ONL Y DEFW( SUMEXT , SUMEXT_)/************************************************************* DIGITAL I/O Port1/2************************************************************/#define __MSP430_HAS_PORT1__ /* Definition to show that Module is available */ #define __MSP430_HAS_PORT2__ /* Definition to show that Module is available */#define P1IN_ (0x0020) /* Port 1 Input */READ_ONL Y DEFC( P1IN , P1IN_)#define P1OUT_ (0x0021) /* Port 1 Output */DEFC( P1OUT , P1OUT_)#define P1DIR_ (0x0022) /* Port 1 Direction */DEFC( P1DIR , P1DIR_)#define P1IFG_ (0x0023) /* Port 1 Interrupt Flag */DEFC( P1IFG , P1IFG_)#define P1IES_ (0x0024) /* Port 1 Interrupt Edge Select */DEFC( P1IES , P1IES_)#define P1IE_ (0x0025) /* Port 1 Interrupt Enable */DEFC( P1IE , P1IE_)#define P1SEL_ (0x0026) /* Port 1 Selection */DEFC( P1SEL , P1SEL_)#define P2IN_ (0x0028) /* Port 2 Input */READ_ONL Y DEFC( P2IN , P2IN_)#define P2OUT_ (0x0029) /* Port 2 Output */DEFC( P2OUT , P2OUT_)#define P2DIR_ (0x002A) /* Port 2 Direction */DEFC( P2DIR , P2DIR_)#define P2IFG_ (0x002B) /* Port 2 Interrupt Flag */DEFC( P2IFG , P2IFG_)#define P2IES_ (0x002C) /* Port 2 Interrupt Edge Select */DEFC( P2IES , P2IES_)#define P2IE_ (0x002D) /* Port 2 Interrupt Enable */DEFC( P2IE , P2IE_)#define P2SEL_ (0x002E) /* Port 2 Selection */DEFC( P2SEL , P2SEL_)/************************************************************* DIGITAL I/O Port3/4************************************************************/#define __MSP430_HAS_PORT3__ /* Definition to show that Module is available */ #define __MSP430_HAS_PORT4__ /* Definition to show that Module is available */#define P3IN_ (0x0018) /* Port 3 Input */READ_ONL Y DEFC( P3IN , P3IN_)#define P3OUT_ (0x0019) /* Port 3 Output */DEFC( P3OUT , P3OUT_)#define P3DIR_ (0x001A) /* Port 3 Direction */DEFC( P3DIR , P3DIR_)#define P3SEL_ (0x001B) /* Port 3 Selection */DEFC( P3SEL , P3SEL_)#define P4IN_ (0x001C) /* Port 4 Input */READ_ONL Y DEFC( P4IN , P4IN_)#define P4OUT_ (0x001D) /* Port 4 Output */DEFC( P4OUT , P4OUT_)#define P4DIR_ (0x001E) /* Port 4 Direction */DEFC( P4DIR , P4DIR_)#define P4SEL_ (0x001F) /* Port 4 Selection */DEFC( P4SEL , P4SEL_)/************************************************************* DIGITAL I/O Port5/6************************************************************/#define __MSP430_HAS_PORT5__ /* Definition to show that Module is available */ #define __MSP430_HAS_PORT6__ /* Definition to show that Module is available */#define P5IN_ (0x0030) /* Port 5 Input */READ_ONL Y DEFC( P5IN , P5IN_)#define P5OUT_ (0x0031) /* Port 5 Output */DEFC( P5OUT , P5OUT_)#define P5DIR_ (0x0032) /* Port 5 Direction */DEFC( P5DIR , P5DIR_)#define P5SEL_ (0x0033) /* Port 5 Selection */DEFC( P5SEL , P5SEL_)#define P6IN_ (0x0034) /* Port 6 Input */READ_ONL Y DEFC( P6IN , P6IN_)#define P6OUT_ (0x0035) /* Port 6 Output */DEFC( P6OUT , P6OUT_)#define P6DIR_ (0x0036) /* Port 6 Direction */DEFC( P6DIR , P6DIR_)#define P6SEL_ (0x0037) /* Port 6 Selection */DEFC( P6SEL , P6SEL_)/************************************************************* USART************************************************************//* UxCTL */#define PENA (0x80) /* Parity enable */#define PEV (0x40) /* Parity 0:odd / 1:even */#define SPB (0x20) /* Stop Bits 0:one / 1: two */#define CHAR (0x10) /* Data 0:7-bits / 1:8-bits */#define LISTEN (0x08) /* Listen mode */#define SYNC (0x04) /* UART / SPI mode */#define MM (0x02) /* Master Mode off/on */#define SWRST (0x01) /* USART Software Reset *//* UxTCTL */#define CKPH (0x80) /* SPI: Clock Phase */#define CKPL (0x40) /* Clock Polarity */#define SSEL1 (0x20) /* Clock Source Select 1 */#define SSEL0 (0x10) /* Clock Source Select 0 */#define URXSE (0x08) /* Receive Start edge select */#define TXW AKE (0x04) /* TX Wake up mode */#define STC (0x02) /* SPI: STC enable 0:on / 1:off */#define TXEPT (0x01) /* TX Buffer empty *//* UxRCTL */#define FE (0x80) /* Frame Error */#define PE (0x40) /* Parity Error */#define OE (0x20) /* Overrun Error */#define BRK (0x10) /* Break detected */#define URXEIE (0x08) /* RX Error interrupt enable */#define URXWIE (0x04) /* RX Wake up interrupt enable */#define RXW AKE (0x02) /* RX Wake up detect */#define RXERR (0x01) /* RX Error Error *//************************************************************* USART 0************************************************************/#define __MSP430_HAS_UART0__ /* Definition to show that Module is available */#define U0CTL_ (0x0070) /* USART 0 Control */DEFC( U0CTL , U0CTL_)#define U0TCTL_ (0x0071) /* USART 0 Transmit Control */DEFC( U0TCTL , U0TCTL_)#define U0RCTL_ (0x0072) /* USART 0 Receive Control */DEFC( U0RCTL , U0RCTL_)#define U0MCTL_ (0x0073) /* USART 0 Modulation Control */ DEFC( U0MCTL , U0MCTL_)#define U0BR0_ (0x0074) /* USART 0 Baud Rate 0 */DEFC( U0BR0 , U0BR0_)#define U0BR1_ (0x0075) /* USART 0 Baud Rate 1 */DEFC( U0BR1 , U0BR1_)#define U0RXBUF_ (0x0076) /* USART 0 Receive Buffer */ READ_ONL Y DEFC( U0RXBUF , U0RXBUF_)#define U0TXBUF_ (0x0077) /* USART 0 Transmit Buffer */ DEFC( U0TXBUF , U0TXBUF_)/* Alternate register names */#define UCTL0 U0CTL /* USART 0 Control */#define UTCTL0 U0TCTL /* USART 0 Transmit Control */#define URCTL0 U0RCTL /* USART 0 Receive Control */#define UMCTL0 U0MCTL /* USART 0 Modulation Control */ #define UBR00 U0BR0 /* USART 0 Baud Rate 0 */#define UBR10 U0BR1 /* USART 0 Baud Rate 1 */#define RXBUF0 U0RXBUF /* USART 0 Receive Buffer */#define TXBUF0 U0TXBUF /* USART 0 Transmit Buffer */#define UCTL0_ U0CTL_ /* USART 0 Control */#define UTCTL0_ U0TCTL_ /* USART 0 Transmit Control */#define URCTL0_ U0RCTL_ /* USART 0 Receive Control */#define UMCTL0_ U0MCTL_ /* USART 0 Modulation Control */ #define UBR00_ U0BR0_ /* USART 0 Baud Rate 0 */#define UBR10_ U0BR1_ /* USART 0 Baud Rate 1 */#define RXBUF0_ U0RXBUF_ /* USART 0 Receive Buffer */#define TXBUF0_ U0TXBUF_ /* USART 0 Transmit Buffer */#define UCTL_0 U0CTL /* USART 0 Control */#define UTCTL_0 U0TCTL /* USART 0 Transmit Control */#define URCTL_0 U0RCTL /* USART 0 Receive Control */#define UMCTL_0 U0MCTL /* USART 0 Modulation Control */ #define UBR0_0 U0BR0 /* USART 0 Baud Rate 0 */#define UBR1_0 U0BR1 /* USART 0 Baud Rate 1 */#define RXBUF_0 U0RXBUF /* USART 0 Receive Buffer */#define TXBUF_0 U0TXBUF /* USART 0 Transmit Buffer */#define UCTL_0_ U0CTL_ /* USART 0 Control */#define UTCTL_0_ U0TCTL_ /* USART 0 Transmit Control */#define URCTL_0_ U0RCTL_ /* USART 0 Receive Control */#define UMCTL_0_ U0MCTL_ /* USART 0 Modulation Control */ #define UBR0_0_ U0BR0_ /* USART 0 Baud Rate 0 */#define UBR1_0_ U0BR1_ /* USART 0 Baud Rate 1 */#define RXBUF_0_ U0RXBUF_ /* USART 0 Receive Buffer */#define TXBUF_0_ U0TXBUF_ /* USART 0 Transmit Buffer *//************************************************************* USART 1************************************************************/#define __MSP430_HAS_UART1__ /* Definition to show that Module is available */#define U1CTL_ (0x0078) /* USART 1 Control */DEFC( U1CTL , U1CTL_)#define U1TCTL_ (0x0079) /* USART 1 Transmit Control */DEFC( U1TCTL , U1TCTL_)#define U1RCTL_ (0x007A) /* USART 1 Receive Control */DEFC( U1RCTL , U1RCTL_)#define U1MCTL_ (0x007B) /* USART 1 Modulation Control */DEFC( U1MCTL , U1MCTL_)#define U1BR0_ (0x007C) /* USART 1 Baud Rate 0 */DEFC( U1BR0 , U1BR0_)#define U1BR1_ (0x007D) /* USART 1 Baud Rate 1 */DEFC( U1BR1 , U1BR1_)#define U1RXBUF_ (0x007E) /* USART 1 Receive Buffer */READ_ONL Y DEFC( U1RXBUF , U1RXBUF_)#define U1TXBUF_ (0x007F) /* USART 1 Transmit Buffer */DEFC( U1TXBUF , U1TXBUF_)/* Alternate register names */#define UCTL1 U1CTL /* USART 1 Control */#define UTCTL1 U1TCTL /* USART 1 Transmit Control */#define URCTL1 U1RCTL /* USART 1 Receive Control */#define UMCTL1 U1MCTL /* USART 1 Modulation Control */#define UBR01 U1BR0 /* USART 1 Baud Rate 0 */#define UBR11 U1BR1 /* USART 1 Baud Rate 1 */#define RXBUF1 U1RXBUF /* USART 1 Receive Buffer */#define TXBUF1 U1TXBUF /* USART 1 Transmit Buffer */#define UCTL1_ U1CTL_ /* USART 1 Control */#define UTCTL1_ U1TCTL_ /* USART 1 Transmit Control */#define URCTL1_ U1RCTL_ /* USART 1 Receive Control */#define UMCTL1_ U1MCTL_ /* USART 1 Modulation Control */#define UBR01_ U1BR0_ /* USART 1 Baud Rate 0 */#define UBR11_ U1BR1_ /* USART 1 Baud Rate 1 */#define RXBUF1_ U1RXBUF_ /* USART 1 Receive Buffer */#define TXBUF1_ U1TXBUF_ /* USART 1 Transmit Buffer */#define UCTL_1 U1CTL /* USART 1 Control */#define UTCTL_1 U1TCTL /* USART 1 Transmit Control */#define URCTL_1 U1RCTL /* USART 1 Receive Control */#define UMCTL_1 U1MCTL /* USART 1 Modulation Control */#define UBR0_1 U1BR0 /* USART 1 Baud Rate 0 */#define UBR1_1 U1BR1 /* USART 1 Baud Rate 1 */#define RXBUF_1 U1RXBUF /* USART 1 Receive Buffer */#define TXBUF_1 U1TXBUF /* USART 1 Transmit Buffer */#define UCTL_1_ U1CTL_ /* USART 1 Control */#define UTCTL_1_ U1TCTL_ /* USART 1 Transmit Control */#define URCTL_1_ U1RCTL_ /* USART 1 Receive Control */#define UMCTL_1_ U1MCTL_ /* USART 1 Modulation Control */#define UBR0_1_ U1BR0_ /* USART 1 Baud Rate 0 */#define UBR1_1_ U1BR1_ /* USART 1 Baud Rate 1 */#define RXBUF_1_ U1RXBUF_ /* USART 1 Receive Buffer */#define TXBUF_1_ U1TXBUF_ /* USART 1 Transmit Buffer *//************************************************************* Timer A3************************************************************/#define __MSP430_HAS_TA3__ /* Definition to show that Module is available */#define TAIV_ (0x012E) /* Timer A Interrupt Vector Word */READ_ONL Y DEFW( TAIV , TAIV_)#define TACTL_ (0x0160) /* Timer A Control */DEFW( TACTL , TACTL_)#define TACCTL0_ (0x0162) /* Timer A Capture/Compare Control 0 */ DEFW( TACCTL0 , TACCTL0_)#define TACCTL1_ (0x0164) /* Timer A Capture/Compare Control 1 */ DEFW( TACCTL1 , TACCTL1_)#define TACCTL2_ (0x0166) /* Timer A Capture/Compare Control 2 */ DEFW( TACCTL2 , TACCTL2_)#define TAR_ (0x0170) /* Timer A */DEFW( TAR , TAR_)#define TACCR0_ (0x0172) /* Timer A Capture/Compare 0 */DEFW( TACCR0 , TACCR0_)#define TACCR1_ (0x0174) /* Timer A Capture/Compare 1 */DEFW( TACCR1 , TACCR1_)#define TACCR2_ (0x0176) /* Timer A Capture/Compare 2 */DEFW( TACCR2 , TACCR2_)/* Alternate register names */#define CCTL0 TACCTL0 /* Timer A Capture/Compare Control 0 */#define CCTL1 TACCTL1 /* Timer A Capture/Compare Control 1 */#define CCTL2 TACCTL2 /* Timer A Capture/Compare Control 2 */#define CCR0 TACCR0 /* Timer A Capture/Compare 0 */#define CCR1 TACCR1 /* Timer A Capture/Compare 1 */#define CCR2 TACCR2 /* Timer A Capture/Compare 2 */#define CCTL0_ TACCTL0_ /* Timer A Capture/Compare Control 0 */ #define CCTL1_ TACCTL1_ /* Timer A Capture/Compare Control 1 */ #define CCTL2_ TACCTL2_ /* Timer A Capture/Compare Control 2 */ #define CCR0_ TACCR0_ /* Timer A Capture/Compare 0 */#define CCR1_ TACCR1_ /* Timer A Capture/Compare 1 */#define CCR2_ TACCR2_ /* Timer A Capture/Compare 2 */#define TASSEL1 (0x0200) /* Timer A clock source select 0 */#define TASSEL0 (0x0100) /* Timer A clock source select 1 */#define ID1 (0x0080) /* Timer A clock input divider 1 */#define ID0 (0x0040) /* Timer A clock input divider 0 */#define MC1 (0x0020) /* Timer A mode control 1 */#define MC0 (0x0010) /* Timer A mode control 0 */#define TACLR (0x0004) /* Timer A counter clear */#define TAIE (0x0002) /* Timer A counter interrupt enable */#define TAIFG (0x0001) /* Timer A counter interrupt flag */#define MC_0 (0*0x10u) /* Timer A mode control: 0 - Stop */#define MC_1 (1*0x10u) /* Timer A mode control: 1 - Up to CCR0 */ #define MC_2 (2*0x10u) /* Timer A mode control: 2 - Continous up */ #define MC_3 (3*0x10u) /* Timer A mode control: 3 - Up/Down */#define ID_0 (0*0x40u) /* Timer A input divider: 0 - /1 */#define ID_1 (1*0x40u) /* Timer A input divider: 1 - /2 */#define ID_2 (2*0x40u) /* Timer A input divider: 2 - /4 */#define ID_3 (3*0x40u) /* Timer A input divider: 3 - /8 */#define TASSEL_0 (0*0x100u) /* Timer A clock source select: 0 - TACLK */ #define TASSEL_1 (1*0x100u) /* Timer A clock source select: 1 - ACLK */ #define TASSEL_2 (2*0x100u) /* Timer A clock source select: 2 - SMCLK */ #define TASSEL_3 (3*0x100u) /* Timer A clock source select: 3 - INCLK */#define CM1 (0x8000) /* Capture mode 1 */#define CM0 (0x4000) /* Capture mode 0 */#define CCIS1 (0x2000) /* Capture input select 1 */#define CCIS0 (0x1000) /* Capture input select 0 */#define SCS (0x0800) /* Capture sychronize */#define SCCI (0x0400) /* Latched capture signal (read) */#define CAP (0x0100) /* Capture mode: 1 /Compare mode : 0 */#define OUTMOD2 (0x0080) /* Output mode 2 */#define OUTMOD1 (0x0040) /* Output mode 1 */#define OUTMOD0 (0x0020) /* Output mode 0 */#define CCIE (0x0010) /* Capture/compare interrupt enable */#define CCI (0x0008) /* Capture input signal (read) */#define OUT (0x0004) /* PWM Output signal if output mode 0 */#define COV (0x0002) /* Capture/compare overflow flag */#define CCIFG (0x0001) /* Capture/compare interrupt flag */#define OUTMOD_0 (0*0x20u) /* PWM output mode: 0 - output only */#define OUTMOD_1 (1*0x20u) /* PWM output mode: 1 - set */#define OUTMOD_2 (2*0x20u) /* PWM output mode: 2 - PWM toggle/reset */ #define OUTMOD_3 (3*0x20u) /* PWM output mode: 3 - PWM set/reset */#define OUTMOD_4 (4*0x20u) /* PWM output mode: 4 - toggle */#define OUTMOD_5 (5*0x20u) /* PWM output mode: 5 - Reset */#define OUTMOD_6 (6*0x20u) /* PWM output mode: 6 - PWM toggle/set */ #define OUTMOD_7 (7*0x20u) /* PWM output mode: 7 - PWM reset/set */#define CCIS_0 (0*0x1000u) /* Capture input select: 0 - CCIxA */#define CCIS_1 (1*0x1000u) /* Capture input select: 1 - CCIxB */#define CCIS_2 (2*0x1000u) /* Capture input select: 2 - GND */#define CCIS_3 (3*0x1000u) /* Capture input select: 3 - Vcc */#define CM_0 (0*0x4000u) /* Capture mode: 0 - disabled */#define CM_1 (1*0x4000u) /* Capture mode: 1 - pos. edge */#define CM_2 (2*0x4000u) /* Capture mode: 1 - neg. edge */#define CM_3 (3*0x4000u) /* Capture mode: 1 - both edges *//* TA3IV Definitions */#define TAIV_NONE (0x0000) /* No Interrupt pending */#define TAIV_TACCR1 (0x0002) /* TACCR1_CCIFG */#define TAIV_TACCR2 (0x0004) /* TACCR2_CCIFG */#define TAIV_6 (0x0006) /* Reserved */#define TAIV_8 (0x0008) /* Reserved */#define TAIV_TAIFG (0x000A) /* TAIFG *//************************************************************* Timer B7************************************************************/#define __MSP430_HAS_TB7__ /* Definition to show that Module is available */#define TBIV_ (0x011E) /* Timer B Interrupt Vector Word */READ_ONL Y DEFW( TBIV , TBIV_)#define TBCTL_ (0x0180) /* Timer B Control */DEFW( TBCTL , TBCTL_)#define TBCCTL0_ (0x0182) /* Timer B Capture/Compare Control 0 */ DEFW( TBCCTL0 , TBCCTL0_)#define TBCCTL1_ (0x0184) /* Timer B Capture/Compare Control 1 */ DEFW( TBCCTL1 , TBCCTL1_)#define TBCCTL2_ (0x0186) /* Timer B Capture/Compare Control 2 */ DEFW( TBCCTL2 , TBCCTL2_)#define TBCCTL3_ (0x0188) /* Timer B Capture/Compare Control 3 */ DEFW( TBCCTL3 , TBCCTL3_)#define TBCCTL4_ (0x018A) /* Timer B Capture/Compare Control 4 */ DEFW( TBCCTL4 , TBCCTL4_)#define TBCCTL5_ (0x018C) /* Timer B Capture/Compare Control 5 */ DEFW( TBCCTL5 , TBCCTL5_)#define TBCCTL6_ (0x018E) /* Timer B Capture/Compare Control 6 */ DEFW( TBCCTL6 , TBCCTL6_)#define TBR_ (0x0190) /* Timer B */DEFW( TBR , TBR_)#define TBCCR0_ (0x0192) /* Timer B Capture/Compare 0 */ DEFW( TBCCR0 , TBCCR0_)#define TBCCR1_ (0x0194) /* Timer B Capture/Compare 1 */ DEFW( TBCCR1 , TBCCR1_)#define TBCCR2_ (0x0196) /* Timer B Capture/Compare 2 */ DEFW( TBCCR2 , TBCCR2_)#define TBCCR3_ (0x0198) /* Timer B Capture/Compare 3 */ DEFW( TBCCR3 , TBCCR3_)#define TBCCR4_ (0x019A) /* Timer B Capture/Compare 4 */ DEFW( TBCCR4 , TBCCR4_)#define TBCCR5_ (0x019C) /* Timer B Capture/Compare 5 */ DEFW( TBCCR5 , TBCCR5_)#define TBCCR6_ (0x019E) /* Timer B Capture/Compare 6 */ DEFW( TBCCR6 , TBCCR6_)#define TBCLGRP1 (0x4000) /* Timer B Compare latch load group 1 */ #define TBCLGRP0 (0x2000) /* Timer B Compare latch load group 0 */ #define CNTL1 (0x1000) /* Counter lenght 1 */#define CNTL0 (0x0800) /* Counter lenght 0 */#define TBSSEL1 (0x0200) /* Clock source 1 */#define TBSSEL0 (0x0100) /* Clock source 0 */#define TBCLR (0x0004) /* Timer B counter clear */#define TBIE (0x0002) /* Timer B interrupt enable */#define TBIFG (0x0001) /* Timer B interrupt flag */#define SHR1 (0x4000) /* Timer B Compare latch load group 1 */ #define SHR0 (0x2000) /* Timer B Compare latch load group 0 */#define TBSSEL_0 (0*0x0100u) /* Clock Source: TBCLK */#define TBSSEL_1 (1*0x0100u) /* Clock Source: ACLK */#define TBSSEL_2 (2*0x0100u) /* Clock Source: SMCLK */#define TBSSEL_3 (3*0x0100u) /* Clock Source: INCLK */#define CNTL_0 (0*0x0800u) /* Counter lenght: 16 bit */#define CNTL_1 (1*0x0800u) /* Counter lenght: 12 bit */#define CNTL_2 (2*0x0800u) /* Counter lenght: 10 bit */#define CNTL_3 (3*0x0800u) /* Counter lenght: 8 bit */#define SHR_0 (0*0x2000u) /* Timer B Group: 0 - individually */#define SHR_1 (1*0x2000u) /* Timer B Group: 1 - 3 groups (1-2, 3-4, 5-6) */ #define SHR_2 (2*0x2000u) /* Timer B Group: 2 - 2 groups (1-3, 4-6)*/#define SHR_3 (3*0x2000u) /* Timer B Group: 3 - 1 group (all) */#define TBCLGRP_0 (0*0x2000u) /* Timer B Group: 0 - individually */#define TBCLGRP_1 (1*0x2000u) /* Timer B Group: 1 - 3 groups (1-2, 3-4, 5-6) */#define TBCLGRP_2 (2*0x2000u) /* Timer B Group: 2 - 2 groups (1-3, 4-6)*/#define TBCLGRP_3 (3*0x2000u) /* Timer B Group: 3 - 1 group (all) *//* Additional Timer B Control Register bits are defined in Timer A */#define CLLD1 (0x0400) /* Compare latch load source 1 */#define CLLD0 (0x0200) /* Compare latch load source 0 */#define SLSHR1 (0x0400) /* Compare latch load source 1 */#define SLSHR0 (0x0200) /* Compare latch load source 0 */#define SLSHR_0 (0*0x0200u) /* Compare latch load sourec : 0 - immediate */ #define SLSHR_1 (1*0x0200u) /* Compare latch load sourec : 1 - TBR counts to 0 */#define SLSHR_2 (2*0x0200u) /* Compare latch load sourec : 2 - up/down */ #define SLSHR_3 (3*0x0200u) /* Compare latch load sourec : 3 - TBR counts to TBCTL0 */#define CLLD_0 (0*0x0200u) /* Compare latch load sourec : 0 - immediate */ #define CLLD_1 (1*0x0200u) /* Compare latch load sourec : 1 - TBR counts to 0 */#define CLLD_2 (2*0x0200u) /* Compare latch load sourec : 2 - up/down */ #define CLLD_3 (3*0x0200u) /* Compare latch load sourec : 3 - TBR counts to TBCTL0 *//* TB7IV Definitions */#define TBIV_NONE (0x0000) /* No Interrupt pending */#define TBIV_TBCCR1 (0x0002) /* TBCCR1_CCIFG */#define TBIV_TBCCR2 (0x0004) /* TBCCR2_CCIFG */#define TBIV_TBCCR3 (0x0006) /* TBCCR3_CCIFG */#define TBIV_TBCCR4 (0x0008) /* TBCCR4_CCIFG */#define TBIV_TBCCR5 (0x000A) /* TBCCR3_CCIFG */#define TBIV_TBCCR6 (0x000C) /* TBCCR4_CCIFG */#define TBIV_TBIFG (0x000E) /* TBIFG *//************************************************************。