状态机讲义

- 格式:pdf

- 大小:1.65 MB

- 文档页数:55

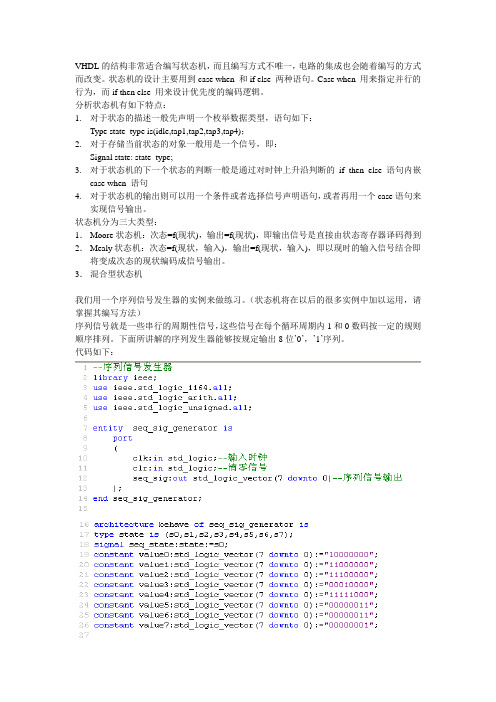

VHDL的结构非常适合编写状态机,而且编写方式不唯一,电路的集成也会随着编写的方式而改变。

状态机的设计主要用到case when 和if else 两种语句。

Case when 用来指定并行的行为,而if then else 用来设计优先度的编码逻辑。

分析状态机有如下特点:1.对于状态的描述一般先声明一个枚举数据类型,语句如下:Type state_type is(idle,tap1,tap2,tap3,tap4);2.对于存储当前状态的对象一般用是一个信号,即:Signal state: state_type;3.对于状态机的下一个状态的判断一般是通过对时钟上升沿判断的if then else 语句内嵌case when 语句4.对于状态机的输出则可以用一个条件或者选择信号声明语句,或者再用一个case语句来实现信号输出。

状态机分为三大类型:1.Moore状态机:次态=f(现状),输出=f(现状),即输出信号是直接由状态寄存器译码得到2.Mealy状态机:次态=f(现状,输入),输出=f(现状,输入),即以现时的输入信号结合即将变成次态的现状编码成信号输出。

3.混合型状态机我们用一个序列信号发生器的实例来做练习。

(状态机将在以后的很多实例中加以运用,请掌握其编写方法)序列信号就是一些串行的周期性信号,这些信号在每个循环周期内1和0数码按一定的规则顺序排列。

下面所讲解的序列发生器能够按规定输出8位’0’,’1’序列。

代码如下:逐行解释:10:清零复位信号,高电平复位清零。

12:序列信号输出。

因为是8位的端口,但序列信号是串行的,所以相当于有8路的序列信号,任取一位端口就是一个序列信号输出。

17:用type声明一种枚举类型。

共8中状态,每个状态都对应唯一的一种输出,至于在什么状态输出什么信号则由程序决定。

18:定义一个state类型信号量,其初始的状态为s0。

19-26:用constant定义一些常量,这些常量将作为在不同状态时的输出信号。

Digital System Design12011/6/21Computer Faculty of Guangdong University of Technology大部分数字系统都可以划分为控制单元和数据单元(存储单元)两个组成部分,通常,控制单元的主体是一个状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。

Digital System Design22011/6/21Computer Faculty of Guangdong University of Technology有限状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情(其实这就是状态机的本质)。

状态机的本质就是对具有逻辑顺序或时序规律事件的一种描述方法,即“逻辑顺序”和“时序规律”就是状态机所要描述的核心和强项,换言之,所有具有逻辑顺序和时序规律的事情都适合用状态机来描述。

Digital System Design32011/6/21Computer Faculty of Guangdong University of Technology1、基本概念有限状态机(Finite State Machine ,FSM )是表示实现有限个离散状态及其状态之间的转移等行为动作的数学模型。

(关注Matlab 的Stateflow )(1)状态:也叫状态变量。

在逻辑设计中,使用状态划分逻辑顺序和时序规律。

状态名称、状态编码、进入/退出操作、内部转移、子状态、延迟事件Digital System Design42011/6/21Computer Faculty of Guangdong University of Technology(2)转移:指两个状态之间的关系,表示当发生指定事件且满足指定条件时,第一个状态中的对象将执行某些操作并进入第二个状态,即“触发”了转移。

将触发转移之前的状态定义为“源”状态(初始状态),而触发转移之后的状态定义为“目标”状态(次态)。

数字起航—状态机零基础电子设计系列课程主讲人:范秋华国家级电工电子实验教学中心(青岛大学)数字启航国家级电工电子实验教学中心4.5.1 状态机(上)⏹引子⏹状态机的概念⏹状态机的要素⏹状态转换图数字启航•引子国家级电工电子实验教学中心编程序,怎么编?画流程图?顺序流程:遵循事先设定的逻辑,从头到尾地执行事件驱动:程序由外部发生的事件来驱动的,程序实际流程是根据人的操作而变化的。

运行到什么地方,不是顺序的,也不是事先设定好的,完全取决于外部的实时操作,而外部的输入比如切水果游戏中有多个位置切,无法由应用程序或程序员来控制,根本不可能画出流程图。

事件驱动的应用程序需用状态机的概念实现。

什么是状态?什么是状态机?游戏的本质也是一个状态机,它接收来自游戏者的信息,改变自身状态,通过画面或声音把新的状态告诉游戏者,游戏者又根据这些画面输入新的信息,如此往复,就成了游戏。

状态就是参数,能够实现状态不断变化的东西叫做状态机。

状态机的本质就是程序。

国家级电工电子实验教学中心数字启航•状态机的概念编程控制接口器件,如液晶显示器、串行接口、显示器等,须要用状态机的概念才能实现。

国家级电工电子实验教学中心数字启航状态机编程快速简单,易于调试,性能高,与人类思维相似从而便于梳理,灵活且容易修改。

数字启航•状态机的基本要素国家级电工电子实验教学中心状态机的基本要素状态机的编程思想:可以在任何给定时间根据输入进行操作,使得系统从一个状态转换到另一个状态,或者是使一个输出或者一种行为发生,一个有限状态机在任何瞬间只能处于一种状态。

即可以用这样的语句表示当系统处于某状态(S1)时,如果发生了什么事情(E),就执行某功能(F1),然后系统变成新状态(S2)描述;如果没发生事情(E),就执行另外功能(F2),系统保持原状态(S1)描述.现态次态当前所处的状态条件又称为“事件”。

当一个条件被满足,将会触发一个动作,或者执行一次状态的迁移。

Digital System Design大部分数字系统都可以划分为控制单元和数据单元(存储单元)两个组成部分,通常,控制单元的主体是一个状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。

12011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design有限状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情(其实这就是状态机的本质)。

状态机的本质就是对具有逻辑顺序或时序规律事件的一种描述方法,即“逻辑顺序”和“时序规律”就是状态机所要描述的核心和强项,换言之,所有具有逻辑顺序和时序规律的事情都适合用状态机来描述。

22011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design1、基本概念有限状态机(Finite State Machine,FSM)是表示实现有限个离散状态及其状态之间的转移等行为动作的数学模型。

(关注Matlab的Stateflow)(1)状态:也叫状态变量。

在逻辑设计中,使用状态划分逻辑顺序和时序规律。

状态名称、状态编码、进入/退出操作、内部转移、子状态、延迟事件32011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design(2)转移:指两个状态之间的关系,表示当发生指定事件且满足指定条件时,第一个状态中的对象将执行某些操作并进入第二个状态,即“触发”了转移。

将触发转移之前的状态定义为“源”状态(初始状态),而触发转移之后的状态定义为“目标”状态(次态)。

初始状态、转移条件、警戒条件、转移操作、目标状态42011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design52011/6/21Computer Faculty of Guangdong University of Technology概括而言,状态机由状态组成,各状态由转移连接在一起。

状态是执行某项活动或等待某个事件的条件。

转移是两个状态之间的关系,它由某个事件触发,然后执行特定的操作或评估并导致特定的结束状态。

状态的图示如下Digital System Design62011/6/21Computer Faculty of Guangdong University of Technology状态转换图如下图所示。

Digital System Design72011/6/21Computer Faculty of Guangdong University of Technology状态转换表如表5.1所示。

当前状态转移条件状态A 状态B 条件x …….条件y ….状态A 条件z ….Digital System Design(3)状态机的分类①摩尔型状态机和米勒型状态机。

摩尔型状态机:利用组合逻辑链将当前状态译码转化为输出,其状态只在全局时钟信号改变时才改变。

其最重要的特点就是将输入与输出信号隔离,所以输出稳定,能有效消除竞争冒险。

如无特殊功能设计要求,摩尔状态机是设计首选。

82011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design92011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design米勒型状态机:其输出与当前状态和输入都有关,且对输入的响应发生在当前时钟周期,比摩尔型状态机对输入信号的响应要早一个周期。

所以输入信号的噪声会直接影响输出信号,即具有竞争冒险且不能消除。

102011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design112011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design②同步状态机和异步状态机异步状态机的状态转移不由唯一的时钟边沿触发,目前多数综合工具在对异步状态机进行逻辑优化时会胡乱地简化逻辑,使综合后的异步状态机不能正常工作。

因此,应尽量不要使用综合工具来设计异步状态机。

为了能综合出有效的电路,用VerilogHDL描述的状态机应明确地由唯一时钟触发,称之为同步状态机,它是设计复杂时序逻辑电路最有效、最常用的方法之一。

异步状态机实现的功能通常都可以由同步状态机来实现。

122011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design③单进程、双进程和多进程状态机一个有限状态机总是可以被分成状态译码、状态寄存器和输出译码三个模块,可以有五种不同的方式将这些模块分配到进程语句,以实现对状态机的描述。

A.三个模块用一个进程实现,也就是说三个模块均在一个always块内,这种状态机描述称为单进程有限状态机,它既描述状态转移,又描述状态的寄存和输出。

132011/6/21Computer Faculty of Guangdong University of TechnologyDigital System DesignB.每一个模块分别用一个进程实现,也就是说三个模块对应着三个always块,这种状态机描述称为三进程有限状态机,其中一个always模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律;第三个always模块使用同步时序电路描述每个状态的输出。

142011/6/21Computer Faculty of Guangdong University of TechnologyDigital System DesignC.次态译码、输出译码分配在一个进程中,状态寄存器用另一个进程描述。

D.次态译码、状态寄存器分配在一个进程中,输出译码用另一个进程描述。

E.次态译码用一个进程描述,状态寄存器、输出译码用另一个进程描述。

在后三种状态机描述中,三个模块对应着两个always块,这种状态机描述称为152011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design162011/6/21Computer Faculty of Guangdong University of Technology2、状态机的设计流程Digital System Design3、状态机的编码方式状态机的N种状态通常需要用某种编码来表示,即状态编码,又称为状态分配。

(1)顺序二进制码:最紧密的编码,使用状态向量的位数最少,类似与前述的二进制编码器。

但从一个状态转移到相邻状态时,可能会有多个比特位发生变化,易产生毛刺。

(2)格雷码:在相邻状态的转换中,每次只有一个比特位发生变化,消除了产生毛刺的问题,但不适用于有很多状态跳转的情况。

(3)独热码:指对任意给定的状态,状态向量中仅有一位“1”,而其172011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design余为“0”,所以N状态的状态机需要N个触发器。

(4)直接输出型编码:将状态码中的某些位直接输出作为控制信号,要求状态机各状态的编码作特殊的选择,以适应控制信号的要求,该编码需要根据输出变量来定制编码。

独热码是指对任意给定的状态,状态向量中仅有一位为“1”而其余位都为“0”。

(1)独热编码的状态机具有高速的特点。

状态机的速度与其状态的数量无关,仅取决于状态跳转的数量;(2)独热编码方法无须考虑最优状态编码,当修改状态机时,添加的状态编码和原始的编码都具有同等的功能;(3)关键路径很容易被发现,有利于进行准确的静态时序分析;(4)任何状态都可以直接进行添加/删除等修改而不会影响状态机的其余部分;182011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design(5)具有设计描述简单易懂和维护便利的特点,更有利于使用FPGA器件完成综合和实现。

192011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design其缺点是:(1)当任意状态发生跳转时,与之相关的一位也必发生跳变。

由于状态机的输出是由寄存器生成的,如果变化的状态位越多,产生的毛刺就越多。

(2)可能会有很多的无效状态,应确保状态机一旦进入无效状态时,可以立即跳转到确定的已知状态以避免死锁现象的出现。

202011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design212011/6/21Computer Faculty of Guangdong University of Technology例给定状态机的状态转换图如下,实现的功能是当输入信号A 出现110序列时输出信号Y 为1,否则为0.Digital System Design编码方式表状态顺序编码独热编码直接输出型编码1直接输出型编码2S0000010000001S1010100010010S2101000100100S3。

1001100222011/6/21Computer Faculty of Guangdong University of TechnologyDigital System Design4状态机容错和设计准则(1)状态机的容错一个完备的状态机(健壮性强)应该具备初始化状态和默认状态。

当芯片加电或者复位后,状态机应能够自动将所有判断条件复位,并进入初始化状态。

另一方面,状态机也应有一个默认状态(default),当转移条件不满足或者状态发生突变时,要能保证逻辑不会陷入“死循环”,即状态机可以自恢复。