北京交通大学数字集成电路复习

- 格式:doc

- 大小:25.00 KB

- 文档页数:2

数字集成电路考试知识点一、数字逻辑基础。

1. 数制与编码。

- 二进制、十进制、十六进制的相互转换。

例如,将十进制数转换为二进制数可以使用除2取余法;将二进制数转换为十六进制数,可以每4位二进制数转换为1位十六进制数。

- 常用编码,如BCD码(8421码、余3码等)。

BCD码是用4位二进制数来表示1位十进制数,8421码是一种有权码,各位的权值分别为8、4、2、1。

2. 逻辑代数基础。

- 基本逻辑运算(与、或、非)及其符号表示、真值表和逻辑表达式。

例如,与运算只有当所有输入为1时,输出才为1;或运算只要有一个输入为1,输出就为1;非运算则是输入和输出相反。

- 复合逻辑运算(与非、或非、异或、同或)。

异或运算的特点是当两个输入不同时输出为1,相同时输出为0;同或则相反。

- 逻辑代数的基本定理和规则,如代入规则、反演规则、对偶规则。

利用这些规则可以对逻辑表达式进行化简和变换。

- 逻辑函数的化简,包括公式化简法和卡诺图化简法。

卡诺图化简法是将逻辑函数以最小项的形式表示在卡诺图上,通过合并相邻的最小项来化简逻辑函数。

二、门电路。

1. 基本门电路。

- 与门、或门、非门的电路结构(以CMOS和TTL电路为例)、电气特性(如输入输出电平、噪声容限等)。

CMOS门电路具有功耗低、集成度高的优点;TTL门电路速度较快。

- 门电路的传输延迟时间,它反映了门电路的工作速度,从输入信号变化到输出信号稳定所需要的时间。

2. 复合门电路。

- 与非门、或非门、异或门等复合门电路的逻辑功能和实现方式。

这些复合门电路可以由基本门电路组合而成,也有专门的集成电路芯片实现其功能。

三、组合逻辑电路。

1. 组合逻辑电路的分析与设计。

- 组合逻辑电路的分析方法:根据给定的逻辑电路写出逻辑表达式,化简表达式,列出真值表,分析逻辑功能。

- 组合逻辑电路的设计方法:根据逻辑功能要求列出真值表,写出逻辑表达式,化简表达式,画出逻辑电路图。

2. 常用组合逻辑电路。

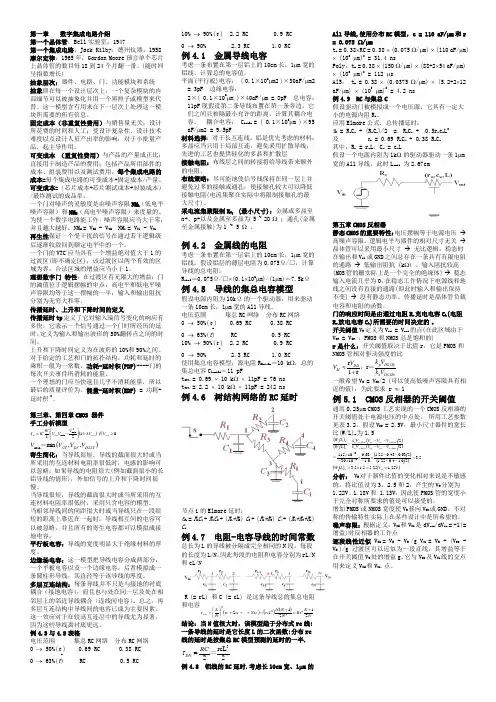

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论1、数字IC芯片制造步骤设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版制造:划片:将圆片切割成一个一个的管芯(划片槽)封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连测试:测试芯片的工作情况2、数字IC的设计方法分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用 Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的)NRE (Non-Recurrent Engineering) 成本设计时间和投入,掩膜生产,样品生产一次性成本Recurrent 成本工艺制造(silicon processing),封装(packaging),测试(test)正比于产量综合可以相互转化加了功耗信息一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数功耗:emmmm自己算4、EDA设计流程IP设计系统设计(SystemC)模块设计(verilog)版图设计(.ICC) 电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys):.db(不可读) .lib(可读).sdb .slib第二章器件基础1、保护IC的输入器件以抗静电荷(ESD保护)2、长沟道器件电压和电流的关系:3、短沟道器件电压和电流关系速度饱和:当沿着沟道的电场达到临界值ξC时,载流子的速度由于散射效应(载流子之间的碰撞)而趋于饱和。

1. 集成电路是指通过一系列特定的加工工艺,将晶体管、二极管、MOS管等有源器件和阻、电容、电感等无源器件,按一定电路互连,“集成”在一块半导体晶片(硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能的一种器件。

2.集成电路的规模大小是以它所包含的晶体管数目或等效的逻辑门数目来衡量。

等效逻辑门通常是指两输入与非门,对于CMOS集成电路来说,一个两输入与非门由四个晶体管组成,因此一个CMOS电路的晶体管数除以四,就可以得到该电路的等效逻辑门的数目,以此确定一个集成电路的集成度。

3.摩尔定律”其主要内容如下:集成电路的集成度每18个月翻一番/每三年翻两番。

摩尔分析了集成电路迅速发展的原因,他指出集成度的提高主要是三方面的贡献:(1)特征尺寸不断缩小,大约每3年缩小 1.41倍;(2)芯片面积不断增大,大约每3年增大 1.5倍;(3)器件和电路结构的改进。

4.反标注是指将版图参数提取得到的分布电阻和分布电容迭加到相对应节点的参数上去,实际上是修改了对应节点的参数值。

5.CMOS反相器的直流噪声容限:为了反映逻辑电路的抗干扰能力,引入了直流噪声容限作为电路性能参数。

直流噪声容限反映了电流能承受的实际输入电平与理想逻辑电平的偏离范围。

6. 根据实际工作确定所允许的最低输出高电平,它所对应的输入电平定义为关门电平;给定允许的最高输出低电平,它所对应的输入电平为开门电平7. 单位增益点.在增益为0和增益很大的输入电平的区域之间必然存在单位增益点,即dVout/dVin=1的点8. “闩锁”现象在正常工作状态下,PNPN四层结构之间的电压不会超过Vtg,因此它处于截止状态。

但在一定的外界因素触发下,例如由电源或输出端引入一个大的脉冲干扰,或受r射线的瞬态辐照,使PNPN四层结构之间的电压瞬间超过Vtg,这时,该寄生结构中就会出现很大的导通电流。

只要外部信号源或者Vdd和Vss能够提供大于维持电流Ih的输出,即使外界干扰信号已经消失,在PNPN四层结构之间的导通电流仍然会维持,这就是所谓的“闩锁”现象9. 延迟时间:T pdo ——晶体管本征延迟时间;UL ——最大逻辑摆幅,即最大电源电压;Cg ——扇出栅电容(负载电容);Cw ——内连线电容;Ip ——晶体管峰值电流。

北京交通大学考试试题(期中)课程名称:数字电子技术(A)学年学期:2014-2015学年第一学期课程编号:14L126Q 开课学院:电信学院出题教师:学生姓名:学号:任课教师:学生学院:班级:一、概念题(每空3分,共30分)1. 一组合逻辑电路输入信号的变化顺序有以下三种情况,当顺序为时,将可能出现竞争冒险。

(A)00→01→11→10;(B)00→11→10→01;(C)00→01→00→10。

2. TTL与非门的灌电流负载发生在输出电平情况下,负载电流越大,则输出电平越。

3.CMOS门电路与TTL门电路相比最大的优点是。

(A)传输速度快;(B)功耗低;(C)功能全;(D)价格低。

4.能实现线与功能的门电路有;能实现总线连接方式的门电路有。

(A)与非门;(B)异或门;(C)三态门;(D)OC门。

5.图1所示电路的逻辑表达F= 。

F图1图26.图2所示电路的逻辑功能是 。

7.如图所示逻辑电路的表达式F = 。

8.如图所示逻辑电路的表达式F = 。

A 0A 1二、分析题(共30分)1.分析图示集成逻辑门电路功能。

(10分)2.分析图示电路的逻辑功能。

图中74HC85是比较器,74CH283是加法器。

(10分)3213.试分析图示逻辑电路的逻辑功能。

(10分)三、设计题(共40分) 1.分别用3—8译码器和2—4数据选择器及适当的门电路,实现下面的逻辑表达式。

(10分)(10分)BC AC AB F ++=(a )S Q (b ) XCPY2.如图(a )所示电路,当其输入信号如图(b )所示,画出S 和Q 的波形。

(10分)3.电路完整的状态转换图如图所示,说明该电路的逻辑功能,判断电路能否自启动?若不能,请改正,并用D 触发器实现该功能。

(20分)。

数字集成电路--电路、系统与设计(第⼆版)课后练习题第六.Digital Integrated Circuits - 2nd Ed 11 DESIGN PROJECT Design, lay out, and simulate a CMOS four-input XOR gate in the standard 0.25 micron CMOS process. You can choose any logic circuit style, and you are free to choose how many stages of logic to use: you could use one large logic gate or a combination of smaller logic gates. The supply voltage is set at 2.5 V! Your circuit must drive an external 20 fF load in addition to whatever internal parasitics are present in your circuit. The primary design objective is to minimize the propagation delay of the worst-case transition for your circuit. The secondary objective is to minimize the area of the layout. At the very worst, your design must have a propagation delay of no more than 0.5 ns and occupy an area of no more than 500 square microns, but the faster and smaller your circuit, the better. Be aware that, when using dynamic logic, the precharge time should be made part of the delay. The design will be graded on themagnitude of A × tp2, the product of the area of your design and the square of the delay for the worst-case transition.。

数字集成电路复习要点⼀、简答题1.集成电路发展的特点:速度变快,I/O增多,⼯作电压下降……A,特征尺⼨越来越⼩,B,单个芯⽚晶体管数⽬越来越多,速度越来越快,电压越来越⼩,层数越来越多,端⼝越来越多,功耗越来越低2.P181⼤扇⼊的“设计技术”。

A,调整晶体管尺⼨B,逐级加⼤晶体管尺⼨C,重新安排输⼊D,重组逻辑结构(把光键路径上的晶体管靠近门的输出端)3.简述集成电路⼯艺中典型的光刻步骤及其相互关系。

(P28)氧化层,涂光刻胶,光刻机曝光,光刻胶的显影和烘⼲,酸刻蚀,旋转清洗和⼲燥,各种⼯艺加⼯步骤,去除光刻胶4.什么是多晶⾃对准⼯艺,有哪些优点?(P32)在掺杂之前形成图形的多晶硅栅实际确定了沟道区的确切位置,从⽽也确定了源区和漏区的位置。

它使源和漏这两个区域相对于栅具有⾮常精确的位置,有助于减⼩晶体管中的寄⽣电容。

5.CMOS逻辑门特性:(全摆幅,⽆⽐性,低输出阻抗,⾼输⼊阻抗,⽆静态功耗。

)A,电压摆幅等于电源电压,噪声容很⼤,B,逻辑电平与器件的相对尺⼨⽆关,⽆⽐逻辑,C,具有低输出阻抗,⾼输⼊阻抗,D,不消耗任何静态功率6.伪NCMOS门逻辑的特点A,减少晶体管的数⽬,由2N减到N+1,B,速度快缺点:⼩的噪声容限和⼤的静态功耗6.传输管逻辑的优点是什么?有哪些缺点,解决的办法是什么?优点:结构简单,阀值损失⼩,硬件开销⼩缺点:延时⾼,仅含NMOS的传输管将引起静态功耗并减⼩噪声容限解决办法:避免开关长串联以减⼩延时,增加电平恢复晶体管以消除静态功耗7.什么是时钟馈通,有何危害?(P215)原理:电容耦合的特殊情况,由在预充电器件的时钟输⼊和动态输出节点之间电容耦合引起的效应,当下拉⽹络不导通时,这⼀电容耦合会在时钟由低⾄⾼翻转时,引起的动态节点输出上升到VDD以上;⽽快速上升和下降时时钟边沿会耦合到信号节点上。

特点:a)可能使预充电管正常情况下反偏结⼆极管变为正向偏置,使电⼦注⼊到衬底中,被附近处于⾼电平的⾼阻节点收集,导致出错。

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

集成电路设计考点1.填空题1.NML与NMH的概念,热电势,D触发器,D锁存器,施密特触发器。

低电平噪声容限:VIL-VOL高电平噪声容限:VOH-VIH这一容限值应该大于零热电势:两种不同的金属相互接触时,其接触端与非接触端的温度若不相等,则在两种金属之间产生电位差称为热电势。

2.MOS晶体管动态响应与什么有关?(本征电容P77)MOS晶体管的动态响应值取决于它充放电这个期间的本征寄生电容与由互连线及负载引起的额外电容所需要的时间。

本征电容的来源:基本的MOS结构、沟道电荷以及漏与源反向偏置PN结的耗尽区。

3.设计技术(其他考点与这种知识点类似)P147怎样减小一个门的传播延时:减小CL:负载电容主要由以下三个主要部分组成:门本身的内部扩散电容、互连线电容与扇出电容。

增加晶体管的宽长比提高VDD4.有比逻辑与无比逻辑。

有比逻辑:有比逻辑试图减少实现有一个给定逻辑功能所需要的晶体管数目,但它经常以降低稳定性与付出额外功耗为代价。

这样的门不是采用有源的下拉与上拉网络的组合,而是由一个实现逻辑功能的NMOS下拉网络与一个简单的负载器件组成。

无比逻辑:逻辑电平与器件的相对尺寸无关的门叫做无比逻辑。

有比逻辑:逻辑电平是由组成逻辑的晶体管的相对尺寸决定的。

5.时序电路的特点:记忆功能的原理:(a)基本反馈;(b)电容存储电荷。

6.信号完整性。

(电荷分享,泄露)信号完整性问题:电荷泄露电荷分享电容耦合时钟馈通7.存储器与存储的分类按存储方式分随机存储器:任何存储单元的内容都能被随机存取,且存取时间与存储单元的物理位置无关。

顺序存储器:只能按某种顺序来存取,存取时间与存储单元的物理位置有关。

按存储器的读写功能分只读存储器(ROM):存储的内容是固定不变的,只能读出而不能写入的半导体存储器。

随机读写存储器(RAM):既能读出又能写入的半导体存储器。

按信息的可保存性分非永久记忆的存储器:断电后信息即消失的存储器。

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论1、数字IC芯片制造步骤设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版制造:划片:将圆片切割成一个一个的管芯(划片槽)封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连测试:测试芯片的工作情况2、数字IC的设计方法分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的)NRE (Non-Recurrent Engineering) 成本设计时间和投入,掩膜生产,样品生产一次性成本Recurrent 成本工艺制造(silicon processing),封装(packaging),测试(test)正比于产量一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数功耗:emmmm自己算4、EDA设计流程IP设计系统设计(SystemC)模块设计(verilog)综合版图设计(.ICC) 电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys版权):可以相互转化.db(不可读).lib(可读)加了功耗信息.sdb .slib第二章器件基础1、保护IC的输入器件以抗静电荷(ESD保护)2、长沟道器件电压和电流的关系:3、短沟道器件电压和电流关系速度饱和:当沿着沟道的电场达到临界值ξC时,载流子的速度由于散射效应(载流子之间的碰撞)而趋于饱和。

在决定考研的那一刻,我已预料到这一年将是怎样的一年,我做好了全身心地准备和精力来应对这一年枯燥、乏味、重复、单调的机械式生活。

可是虽然如此,我实在是一个有血有肉的人呐,面对诱惑和惰性,甚至几次妥协,妥协之后又陷入对自己深深的自责愧疚当中。

这种情绪反反复复,曾几度崩溃。

所以在此想要跟各位讲,心态方面要调整好,不要像我一样使自己陷入极端的情绪当中,这样无论是对自己正常生活还是考研复习都是非常不利的。

所以我想把这一年的经历写下来,用以告慰我在去年饱受折磨的心脏和躯体。

告诉它们今年我终于拿到了心仪学校的录取通知书,你们的付出和忍耐也终于可以扬眉了。

知道自己成功上岸的那一刻心情是极度开心的,所有心酸泪水,一扫而空,只剩下满心欢喜和对未来的向往。

首先非常想对大家讲的是,大家选择考研的这个决定实在是太正确了。

非常鼓励大家做这个决定,手握通知书,对未来充满着信念的现在的我尤其这样认为。

当然不是说除了考研就没有了别的出路。

只不过个人感觉考研这条路走的比较方便,流程也比较清晰。

没有太大的不稳定性,顶多是考上,考不上的问题。

而考得上考不上这个主观能动性太强了,就是说,自己决定自己的前途。

所以下面便是我这一年来积攒的所有干货,希望可以对大家有一点点小小的帮助。

由于想讲的实在比较多,所以篇幅较长,希望大家可以耐心看完。

文章结尾会附上我自己的学习资料,大家可以自取。

北京交通大学电子信息的初试科目为:(101)思想政治理论(201)英语一(301)数学一(891)通信原理或(910)电子技术(模拟、数字)参考书目为:(891)通信原理郭宇春等,《通信系统原理》,科学出版社。

ISBN 978-7-03-033528-9 (910)电子技术(模拟、数字)(1)《模拟集成电路基础》(第三版),路勇等编著,中国铁道出版社。

(2)《电子技术(模拟部分)》(第二版),刘颖编著,北京邮电大学出版社。

(3)《数字电子技术基础》(第三版),侯建军等编著,高等教育出版社先介绍一下英语现在就可以开始背单词了,识记为主(看着单词能想到其中文章即可,不需要能拼写)从前期复习到考试前每天坚持两到四篇阅读(至少也得一篇)11月到考试前一天背20篇英语范文(能默写的程度)。

北邮数电考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,以下哪个器件不是基本逻辑门?A. 与门B. 或门C. 非门D. 放大器答案:D2. 以下哪个选项是二进制数1011对应的十进制数?A. 10B. 11C. 12D. 13答案:B3. 以下哪个逻辑表达式表示的是“与非”逻辑?A. A + BB. A * BC. A' * B'D. A + B'答案:C4. 在数字电路中,一个D触发器的输出Q在时钟上升沿时的逻辑状态取决于什么?A. 当前Q的状态B. 上一个时钟周期的D输入C. 当前D输入D. 当前Q和D的异或答案:C5. 以下哪个选项是组合逻辑电路的特点?A. 有记忆功能B. 输出只依赖于当前输入C. 需要时钟信号D. 包含反馈回路答案:B6. 一个完整的二进制加法器至少需要多少个输入?A. 1B. 2C. 3D. 4答案:C7. 在数字电路中,以下哪个术语表示电路的抗干扰能力?A. 延迟B. 噪声容限C. 功耗D. 频率答案:B8. 以下哪个选项是数字电路中常用的编码方式?A. 格雷码B. 十进制码C. 十六进制码D. 二进制码答案:A9. 以下哪个选项是数字电路中常用的计数器类型?A. 同步计数器B. 异步计数器C. 串行计数器D. 并行计数器答案:A10. 在数字电路中,以下哪个选项是布尔代数的基本定理?A. 德摩根定律B. 欧拉定律C. 牛顿定律D. 皮亚诺公理答案:A二、填空题(每题2分,共20分)1. 一个4位二进制计数器的计数范围是_________到_________。

答案:0000 11112. 在数字电路中,一个逻辑门的输出为高电平时,通常表示逻辑值_________。

答案:13. 一个3-8译码器可以将3位二进制数译码为8个输出中的一个,每个输出对应一个唯一的二进制输入组合。

如果输入是101,则输出为_________。

答案:14. 在数字电路中,一个D触发器的时钟输入为低电平时,触发器的状态是_________。

《集成电路设计基础》复习大纲

重点是CMOS电路结构和设计分析。

具体范围如下:

1.模拟集成电路设计、制造过程的基本概念(包括掩膜的技术功能、掩膜在制造过程中的应用、简单版图识别)。

(参考书第1、2章)。

2.基本MOS器件的模型及其分析方法(包括MOS管基本模型、直流特性、频率特性)。

(参考书第3章)。

3.CMOS基本模拟单元电路分析(参考书第4章)

4.CMOS放大器基本结构和特性参数分析(参考书第5章)。

5. 二级运算放大器分析与设计基础(参考书第6章)

本次考试的基本形式为选择题、简答题、计算题和设计题。

本次考试不要求死记公式。

参考书:Phillip E. Allen, Douglas R. Holberg, CMOS Analog Circuit Design, Second Edition, 电子工业出版社,2007年8月。

2012.09.10。