STM32处理器内部结构

- 格式:ppt

- 大小:792.50 KB

- 文档页数:22

stm32f103zet6工作原理

STM32F103ZET6是一款基于ARM Cortex-M3处理器的微控制器。

其工

作原理主要包括内核和IO口两部分。

内核是数据处理中心,类似于人的大脑,负责处理数据。

STM32F103ZET6的内核可以理解为单片机处理器中负责处理数据的电路。

IO口是输出、输入口,是双向的,既可作输入也可作输出。

STM32F103ZET6有144个引脚,其中有112个IO口,一般IO口都能耐

5V,即外部连接的外设输入5V电压不会对IO口有损害。

并且支持调试,SWD和JTAG调试。

此外,该微控制器还有复位电路和稳压模块等功能。

复位电路使电路从某一个确定的状态开始,如果电路工作在卡死等状态,可以使用复位功能来使电路恢复最初的状态(程序未跑起来的状态)。

稳压模块将供电电压VCC转

换为单片机工作电压VDD = 。

以上信息仅供参考,如需了解更多信息,建议查阅相关书籍或咨询专业人士。

转载:/thread-51423-1-1.html作者:追风一、USB的“JoyStickMouse”例程结构分析1、例程的结构(1)底层结构包括5个文件:usb_core.c(USB总线数据处理的核心文件),usb_init.c,usb_int.c(用于端点数据输入输入中断处理),usb_mem.c(用于缓冲区操作),usb_regs.c(用于寄存器操作)。

它们都包含了头文件“usb_lib.h”。

在这个头文件中,又有以下定义:#include "usb_type.h"#include "usb_regs.h"#include "usb_def.h"#include "usb_core.h"#include "usb_init.h"#include "usb_mem.h"#include "usb_int.h"usb_lib.h中又包含了七个头文件,其中usb_type.h中主要是用typedef为stm32支持的数据类型取一些新的名称。

usb_def.h中主要是定义一些相关的数据类型。

还有一个未包含在usb_lib.h中的头文件,usb_conf.h用于USB设备的配置。

(2)上层结构上层结构总共5个文件:hw_config.c(用于USB硬件配置)、usb_pwr.c(用于USB连接、断开操作)、usb_istr.c(直接处理USB中断)、usb_prop.c(用于上层协议处理,比如HID协议,大容量存储设备协议)、usb_desc.c(具体设备的相关描述符定义和处理)。

可见,ST的USB操作库结构十分清晰明了,我先不准备直接阅读源代码。

而是先利用MDK的软件模拟器仿真执行,先了解一下设备初始化的流程。

2、设备初始化所做的工作(1)Set_System(void)这个是main函数中首先调用的函数,它位于hw_config.c文件中。

从零开始学习STM32(2)——STM32的芯片封装来自三千萝卜众STM32采用了三种封装分别是LQFP(代码为T)、BGA(代码为H)和QFN(代码为U)至于引脚数量,T代表36、C代表48、R代表64、V代表100、Z代表144比如我用的STM32F103VBT6,用的是LQFP封装,引脚数为100,这要是自己焊该怎么办啊这一刻,我愁了LQFP(好多金属脚,大型集成电路比较常见)LQFP也就是薄型QFP(Low-profile Quad Flat Package)指封装本体厚度为1.4mm的QFP,是日本电子机械工业会根据制定的新QFP外形规格所用的名称。

下面介绍下QFP封装:这种技术的中文含义叫方型扁平式封装技术(Plastic Quad Flat Package),该技术实现的CPU芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。

该技术封装CPU时操作方便,可靠性高;而且其封装外形尺寸较小,寄生参数减小,适合高频应用;该技术主要适合用SMT 表面安装技术在PCB上安装布线。

BGA(底部很多金属点,电脑cpu貌似都是这种)BGA封装(Ball Grid Array Package)的I/O端子以圆形或柱状焊点按阵列形式分布在封装下面,BGA技术的优点是I/O引脚数虽然增加了,但引脚间距并没有减小反而增加了,从而提高了组装成品率;虽然它的功耗增加,但BGA能用可控塌陷芯片法焊接,从而可以改善它的电热性能;厚度和重量都较以前的封装技术有所减少;寄生参数减小,信号传输延迟小,使用频率大大提高;组装可用共面焊接,可靠性高。

BGA封装技术可详分为五大类:1.PBGA(Plasric BGA)基板:一般为2-4层有机材料构成的多层板。

Intel系列CPU中,Pentium II、III、IV处理器均采用这种封装形式。

2.CBGA(CeramicBGA)基板:即陶瓷基板,芯片与基板间的电气连接通常采用倒装芯片(FlipChip,简称FC)的安装方式。

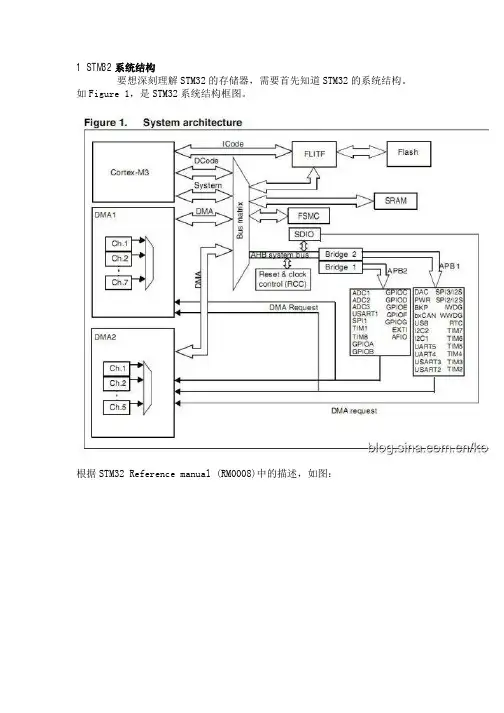

1 STM32系统结构要想深刻理解STM32的存储器,需要首先知道STM32的系统结构。

如Figure 1,是STM32系统结构框图。

根据STM32 Reference manual (RM0008)中的描述,如图:可以得知STM32系统结构的组成,每一个模块更为详细的内容,请参考相关文档。

RM0008文档中可以看出,STM32采用的是Cortex-M3内核,因此,有必要了解Cortex-M3的存储器结构。

图中还可以看出,Cortex-M3是通过各个总线和Flash、SROM相连接的。

2 STM32内核(Cortex-M3)的结构以下是Cortex-M3模块框图:该Cortex-M3内核通过I-Code、D-Code、System总线与STM32内部的Flash、SROM相连接的,该种连接情况直接关系到STM32存储器的结构组织;也就是说,Cortex-M3的存储器结构决定了STM32的存储器结构。

这里可能说的比较笼统,可以这样理解:Cortex-M3是一个内核,自身定义了一个存储器结构,ST公司按照Cortex-M3的这个存储器定义,设计出了自己的存储器结构;但是ST公司的STM32的存储器结构必须按照Cortex-M3这个定义的存储器结构来进行设计。

举个例子:我买了一个做饭的调料盒子,有三块区域(假设存储器分为3块),上面分别标有盐(Flash)、糖(SROM)、味精(Peripheral);此时,该调料盒子并没有任何意义(对应Cortex-M3内核);我按照标签放入特定品牌、特定分量的盐(Flash)、糖(SROM)、味精(Peripheral),产生一个有实际意义的调料盒(各类Cortex-M3内核的芯片,如STM32)。

期间,调料位置不能放错,但可以不放。

由上面的例子可以看出,空的调料盒子决定了有意义的调料盒子存放调料的结构。

因此,只要了解空盒子的存储结构,就可以很清楚的明白当有调料时的用法了。

STM32入门之文件结构在开始STM32的开发之前,了解其文件结构对于编写和组织代码非常重要。

文件结构是指将代码和资源组织在文件夹和文件中的方式。

一个良好的文件结构能够提高代码的可维护性、可扩展性和可读性。

下面是一个典型的STM32文件结构示例:1. Core文件夹:这个文件夹包含了一些核心的STM32的系统文件,例如启动文件、链接脚本文件等。

启动文件包含了一些处理器的初始化代码,用于设置操作模式、初始化中断向量表等。

链接脚本文件定义了代码和数据在存储器中的位置和排列方式。

2. Drivers文件夹:这个文件夹包含了所有的外设驱动文件。

每个外设都有对应的C文件和头文件,用于控制和配置外设。

这些外设包括GPIO(通用输入输出)、USART(串行通信)、SPI(串行外设接口)等。

3. Inc文件夹:这个文件夹包含了所有的头文件。

头文件是用于声明和定义变量、函数和数据结构的文件。

每个源文件都应该包含所需的头文件。

4. Src文件夹:这个文件夹包含了所有的源文件。

源文件包含了实际的代码和功能的实现。

这些文件可以包括主函数、外设初始化函数、中断处理函数等。

5. Middlewares文件夹:这个文件夹包含了一些中间件(middleware),用于简化开发过程和提供一些高级功能。

这些中间件可以包括操作系统、文件系统、图形库等。

6. Libraries文件夹:这个文件夹包含了一些标准的STM32库文件,用于提供一些常用的函数和方法。

这些库文件可以包括数学函数、字符串处理函数、操作系统函数等。

7. Tools文件夹:这个文件夹包含了一些用于开发和调试的工具。

这些工具可以包括编译器、调试器、仿真器等。

以上是一个基本的文件结构示例,实际情况中可能会有一些变化和定制。

根据项目的需求,开发者可以在文件夹中添加其他文件夹,例如Tests文件夹用于存放测试代码,Docs文件夹用于存放文档等。

通过使用一个清晰而有组织的文件结构,开发者可以更容易地理解和维护代码。

列举stm32f103c8内部硬件构成STM32F103C8是STMicroelectronics推出的一款32位高性能的微控制器,它内部拥有丰富的硬件构成,包括中央处理器、存储器、时钟、IO口、通信接口等。

下面将从这些方面展开介绍。

1. 中央处理器STM32F103C8采用ARM Cortex-M3内核,其最高主频可达72MHz。

Cortex-M3内核具有低功耗、高性能和较强的实时性,在嵌入式系统中被广泛应用。

同时,该处理器还拥有强大的指令集,可以进行高效的数据处理和算法运算。

2. 存储器STM32F103C8内部包含了64KB的闪存和20KB的静态随机存储器(SRAM),闪存被用于存储程序代码和数据,而SRAM则用于存储临时数据。

此外,STM32F103C8还支持外部存储器扩展,可以通过外部存储器接口连接更大容量的存储器。

3. 时钟STM32F103C8拥有多个时钟源和时钟模块,用于提供系统运行所需的各种时钟信号。

其中,主要时钟源包括内部高速振荡器(HSI)和外部晶体振荡器(HSE),可以根据需要选择使用。

此外,还有系统时钟、AHB总线时钟、APB1和APB2总线时钟等多个时钟信号输出。

4. IO口STM32F103C8内部集成了多个通用输入输出(IO)口,用于与外部设备进行数据交互。

每个IO口都可以配置为输入或输出模式,并且可以通过编程控制其电平状态。

此外,还可以通过引脚复用功能,将IO口配置为其他特定功能的接口,如串口、SPI、I2C等。

5. 通信接口STM32F103C8支持多种通信接口,用于实现与外部设备的数据传输和通信。

其中,包括UART(串口通信)、SPI(串行外设接口)、I2C(串行总线接口)等常见的接口协议。

这些接口能够与各类外设设备进行高效的数据交换,满足不同应用场景的需求。

6. 中断控制器STM32F103C8内部集成了一个中断控制器,用于管理和触发中断请求。

中断是一种事件响应机制,能够在特定条件满足时自动中断正在执行的程序,转而执行预先定义好的中断处理程序。

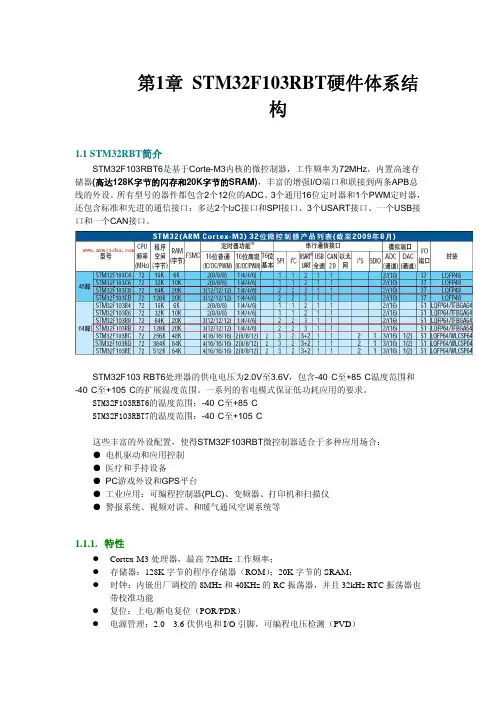

第1章 STM32F103RBT硬件体系结构1.1 STM32RBT简介STM32F103RBT6是基于Corte-M3内核的微控制器,工作频率为72MHz,内置高速存储器(高达128K字节的闪存和20K字节的SRAM),丰富的增强I/O端口和联接到两条APB总线的外设。

所有型号的器件都包含2个12位的ADC、3个通用16位定时器和1个PWM定时器,还包含标准和先进的通信接口:多达2个I2C接口和SPI接口、3个USART接口、一个USB接口和一个CAN接口。

STM32F103 RBT6处理器的供电电压为2.0V至3.6V,包含-40°C至+85°C温度范围和-40°C至+105°C的扩展温度范围。

一系列的省电模式保证低功耗应用的要求。

STM32F103RBT6的温度范围:-40°C至+85°CSTM32F103RBT7的温度范围:-40°C至+105°C这些丰富的外设配置,使得STM32F103RBT微控制器适合于多种应用场合:● 电机驱动和应用控制● 医疗和手持设备● PC游戏外设和GPS平台● 工业应用:可编程控制器(PLC)、变频器、打印机和扫描仪● 警报系统、视频对讲、和暖气通风空调系统等1.1.1.特性z Cortex-M3处理器,最高72MHz工作频率;z存储器:128K字节的程序存储器(ROM);20K字节的SRAM;z时钟:内嵌出厂调校的8MHz和40KHz的RC振荡器,并且32kHz RTC振荡器也带校准功能z复位:上电/断电复位(POR/PDR)z电源管理:2.0—3.6伏供电和I/O引脚,可编程电压检测(PVD)z低功耗:可设置睡眠、停机和待机等三种模式z AD:2个12位的模数转换器,1us转换时间(多达16个输入通道),转换范围是0至3.6V;双采样和保持功能,内部带温度传感器z DMA:7通道DMA控制器,支持的外设有定时器、ADC、SPI、I2C和USART z I/O端口:51个I/O口,所有的I/O口都可以映像到16个外部中断;几乎所有I/O 口可以容忍5V信号z定时器-----3个16位定时器(每个定时器有多达4个用于输入捕获/输出比较/PWM或脉冲计数的通道和增量编码器输入)-----1个16位带死区控制和紧急刹车,用于电机控制的PWM高级控制定时器-----2个看门狗定时器(独立的和窗口型的)-----系统时间定时器:24位自减计数器z其他外围通信接口-----多达2个I2C接口(支持SMBus/PMBus)-----多达3个USART接口(支持ISO7816接口,LIN,IrDA接口和调制解调控制)-----多达2个SPI接口(18M位/秒)-----CAN接口-----USB2.0全速接口z安全:96位的芯片唯一代码,CRC计算单元z调试模式:同时至此后单线SWD调试和JTAG接口1.1.2.器件信息STM32F103RB红框里,具体的资源列表信息一览表:1.1.3.结构STM32F103RBT模块框图总线矩阵用来将处理器和调试接口与外部总线相连。

嵌入式系统(STM32微控制器)实训指导书意法半导体公司的STM32微控制器具有32位字长的CPU,使用精简指令系统(RISC)。

精简指令系统的指令字长固定,译码方便,相对于复杂指令系统(CISC),精简指令系统的处理效率更高。

具有32位字长CPU的STM32系列微控制器的处理能力远高于8位和16位单片机,同时集成了与32位CPU相适应的强大外设(如双通道ADC、多功能定时器、7通道DMA、SPI等),能够完成过去一般单片机所无法达到控制功能。

现在,已经形成了以8位单片机为主流的低端产品和以32位微控制器为主流的高端产品两大市场。

对于自动化领域的从业人员,了解32位微控制器的结构、特点,掌握其使用方法,是很有必要的。

一、关于学习方法此前,我们已经学习过《C语言程序设计》、《微机原理》、《单片机原理及应用》等相关课程。

这些课程的学习是系统的、完整的、全面的,是有老师讲授的。

这种学习方法,适合在学校学习一些重要的基础理论课程。

在工作中,我们常常会遇到新的东西,需要以已有的知识作为基础,去解决问题、完成任务。

这就需要不同于前述的另一种学习方法。

这种方法是建立在自学基础上的,以解决实际问题为目的,允许通过局部的、模仿性的手段,来实现既定目标。

这种方法在工程实践中的应用是非常普遍的。

“白猫黑猫,能抓住老鼠就是好猫”。

能解决问题的方法就是好方法。

本次实训采取的方法是:将参考资料发给同学,同学自学其中需要的部分。

在指导教师引导下,体验各个控制项目、理解各组成部分,再以原控制软件为基础进行修改和移植,获得要达到的控制效果。

在本次实训中,我们使用的微控制器型号为STM32F103RB。

STM32F103RB是STM32微控制器系列中的一种,内部具有128KB程序存储器、20KB随机读写存储器、1个16位高级定时器、3个16位通用定时器、2个SPI、2个I2C、3个USART、1个USB、1个CAN、2个ADC。

芯片为64引脚LQFP封装,有51个I/O引脚。

STM32:内核概览前⾔ 开发⼀款芯⽚,⾸先我们需要确定制造它想要实现的⽬的,也就是想要实现的功能,以及功能与功能间沟通的接⼝;这也就是我们常说的架构; 当架构确定好后,下⼀步就是确定这些功能与接⼝的实现执⾏⽅式; 这些功能与接⼝的具体实现流程就是芯⽚的核⼼,所以我们将这些具体实现流程称之为芯⽚的内核; STM32系列芯⽚采⽤ARM架构下的cortex-M系列内核来具体执⾏和实现芯⽚的功能;1 ARM架构 ARM(Advanced RISC Machine)⾼级精简指令集处理器,简称ARM架构;也是ARM公司起名的由来;为主流芯⽚架构之⼀;CPU架构代表芯⽚指令集架构功能ARM ARM RISC指令集主要⽤于移动,嵌⼊式领域;逻辑门少,发热低,so功耗低;搭配哈佛存储结构使⽤;X86intel,AMD CISC指令集主要是⽤在电脑CPU上,性能⾼,速度快;搭配冯诺依曼存储结构使⽤;MIPS龙芯RISC指令集⽤于部分⾳频处理器和⽹络设备上,市场极⼩;后来 ARM公司作为IP核提供商,专注于ARM处理器的IP核出售业务;在推出ARM11内核之后,之后推出的内核分为三类,分别如下 1.1 cortex-A系列内核:application系列,专注于⾼端消费类电⼦,诸如⾼通,MTK等的⼿机芯⽚; 1.2 cortex-R系列内核:real-time系列,专注于要求实时性的领域,诸如航空航天之类的; 1.3 cortex-M系列内核:micro-controller系列,专注于中低端的嵌⼊式产品,也就是本⽂接下来要说的系列了;2 CPU的存储结构 cortex-m3为cortex系列推出的第⼀个内核,发布于2005年;本⽂就以cortex-m3举例把; cortex-m3为32位处理器内核,⽀持⼩端模式(常⽤)和⼤端模式(不建议);有些指令只使⽤⼩端模式且不可更改;endian模式功能data[31:0]=0x87654321, 地址:0x10,0x11,0x12,0x13⼩端模式数据的低位存放在地址低位中data[7:0]存放在0x10中⼤端模式数据的⾼位存放在地址低位中data[31:24]存放在0x10中 cortex-m3的数据总线,指令总线,寄存器都是32位的,采⽤哈佛结构总线; 那么什么是哈佛总线结构呢?既然遇到了,就在这⾥补充⼀下温馨⼩提⽰把; 2.1 CPU的存储结构 2.1.1 哈佛结构:指令寄存器和数据寄存器存放在不同的内存⾥,需要分别寻址的CPU结构; 1)代码编译之后相当于指令,这些指令通常会固定存放在单⽚机的rom的寄存器⾥,使⽤指令总线来顺序寻址指令寄存器; 相当于指令寄存器全部划分在⼀块固定的区域,指令总线和数据总线同时操作该区域的指令寄存器; 2)单⽚机执⾏过程中的数据存放在ram的寄存器⾥,使⽤地址总线对需要操作的数据寄存器进⾏寻址,然后使⽤数据总线传递数据; 相当于数据寄存器全部划分在⼀块固定的区域,地址总线和数据总线可以同时操作该区域的数据寄存器; 优势:代码安全性较⾼,效率较⾼; 2.1.2 冯诺依曼结构:指令寄存器和数据寄存器存放在相同的内存⾥,不需要分别寻址的CPU结构; 代码A编译之后存放在内存中,该代码A使⽤的数据A存放在代码A地址后;新的代码B继续放在数据A之后,然后再存放数据B... 指令寄存器的存储区域和数据寄存器的存储区域混在⼀块区域,也就是说指令总线和地址总线是相同的总线,需要分时复⽤; 冯诺依曼是早期的cpu结构,执⾏的速度受存储器速度的限制;优势的话。