(8086微处理器内部结构)

- 格式:ppt

- 大小:2.36 MB

- 文档页数:56

8086微处理器内部结构基本组成指令执行部件EU组成算术逻辑单元(ALU) 、标志寄存器、通用寄存器和EU 控制系统等部件功能执行指令总线接口部件BIU组成地址加法器、专用寄存器组、指令队列缓冲器和总线控制逻辑等部件功能形成访问存储器的物理地址,与外部(存储器或I/O 接口)进行联系内部寄存器结构通用寄存器组通用寄存器组数据寄存器地址指针和变址寄存器段寄存器组控制寄存器组指令指针寄存器IP1(16位)用来存放将要取出的下一条指令在代码段中的偏移地址。

在程序运行过程中, BIU 可修改IP 中的内容,使它始终指向将要取出的下一条指令。

标志寄存器FLAGS(双字)有9 个标志位,其中6个用来表示运算结果的状态,包括CF 、PF 、AF、ZF 、SF 和OF ,称为状态标志位,另外3 个是控制标志位,用来控制CPU 的操作,包括IF 、DF 和TF。

标志位2CFCarry Flag——进位标志位如果做加法时最高位产生进位或做减法时最高位产生借位,则CF=1 ,否则CF=0。

PFParity Flag——奇偶标志果操作结果的低八位中含有偶数个1 ,则PF= 1,否则PF=0 。

AFAuxiliary Carry Flag——辅助进位标志位如果做加法时,D3位有进位;做减法时,D3位有借位,则AF=1 ,否则AF=0。

ZFZero Flag——零标志位如果运算结果各位都为0,则ZF = 1 ,否则ZF=0SFSign Flag——符号标志位。

如果运算结果的最高位为1 ,则SF= 1 ,否则SF=0 。

OFOverllow Flag——溢出标志在加或减运算中结果超出8位或16位有符号数所能表示的数值范围时,产生溢出,OF= 1 ,否则OF=0 。

IFInterrupt Flag——中断标志位TFTrap Flag——单步标志位DFDirection Flag——方向标志位存储管理存储器的分段逻辑地址和物理地址逻辑地址由段地址和偏移地址两个部分构成。

8086结构组成8086是一款16位微处理器,它的结构组成非常复杂。

本文将从以下几个方面来详细介绍8086的结构组成。

一、总体结构8086由三个主要部分组成:执行单元(EU)、总线接口单元(BIU)和寄存器组。

1.执行单元:负责执行指令并进行算术和逻辑运算。

2.总线接口单元:负责与外部设备通信并控制数据传输。

3.寄存器组:包括通用寄存器、段寄存器和指令指针寄存器等。

二、执行单元1.指令队列指令队列是执行单元中的一个重要部分,它可以存储多条指令,以便快速地进行取指令操作。

当EU需要执行一条新的指令时,它会从队列中取出下一条指令并开始执行。

2.算术逻辑单元算术逻辑单元(ALU)是执行单元中的核心部分,它可以进行各种算术和逻辑运算,如加、减、乘、除、与、或等操作。

ALU还可以处理条件跳转和无条件跳转等控制操作。

3.状态标志寄存器状态标志寄存器(FLAGS)用于记录ALU运算的结果,以便EU进行下一步操作。

FLAGS寄存器包括零标志位、进位标志位、溢出标志位等。

三、总线接口单元1.地址加法器地址加法器(AFA)是BIU的核心部分,它可以将内部地址转换为外部地址,并控制数据传输。

2.指令缓存器指令缓存器(IC)用于存储从内存中读取的指令。

当EU需要执行一条新的指令时,BIU会从IC中取出相应的指令并传输给EU。

3.数据缓存器数据缓存器(DC)用于暂时存储从内存中读取或写入的数据。

当EU 需要访问内存时,BIU会将相应的数据传输到DC中,EU再从DC中读取或写入数据。

四、寄存器组1.通用寄存器8086有8个16位通用寄存器,分别命名为AX、BX、CX、DX、SI、DI、BP和SP。

这些寄存器可以用于保存临时数据和计算结果等。

2.段寄存器8086有4个16位段寄存器,分别命名为CS、DS、ES和SS。

这些寄存器用于保存程序和数据在内存中的位置信息。

3.指令指针寄存器指令指针寄存器(IP)用于保存下一条指令在内存中的地址。

8086CPU 的结构与功能CPU 结构与功能不管什么型号的CPU ,其内部均有这四⼤部件1. ALU :算术逻辑单元2. ⼯作寄存器:分为数据寄存器和地址寄存器⼯作寄存器的⽬的是为了提⾼运算速度,希望参与运算的数据不从外部存储器去取数据,⽽是在CPU 内部取,所以要有能暂存少量数据的寄存器。

数据寄存器是专门存放数据的,地址寄存器是专门存放地址,进⾏间接寻址⽅式,但当地址寄存器不提供地址时,也可以⽤来暂存数据。

3. 控制器:中央指挥机关4. I/O 控制逻辑电路⼀般CPU 执⾏存储器(按字节组织)⾥⾯指令过程如下:1. CPU 通过控制器部件⾥⾯的程序计数器(PC )给外部存储器的地址引脚输出地址(通过地址总线AB ),同时CPU 给存储器发送读操作命令;2. 在读操作下,就把这个地址单元的指令代码通过数据总线(DB ),取回来放在指令寄存器⾥⾯(IR ),注意此时因为指令没有执⾏完,所以PC 还不能去往下⼀条指令,IR 没有地⽅放数据。

3. 指令译码器(ID )不断检测指令寄存器有没有数据,有的话就把指令取⾛放在ID ⾥⾯,取来的指令就被ID 译码分析,就知道这个指令希望CPU 做什么,怎么做;4. ID 通知控制逻辑部件,在相应的控制引脚发出相应的有效命令(读,写等);5. 此条指令执⾏完,IR 为空,PC ⾃动增加到下⼀条指令的地址,执⾏下⼀条指令流程。

如果指令为n 字节,PC ⾃动增n 。

因为在取指令时候,不能执⾏指令,在执⾏指令时候,不能取指令,因此这种架构CPU 是取指令->执⾏指令->取指令...这样循环下去。

CPU 执⾏效率不⾼。

堆栈由先进后出原则组织的存储器区域,称为堆栈。

单⽚机应⽤中,堆栈是个特殊存储区,堆栈属于RAM 空间的⼀部分,堆栈⽤于函数调⽤、中断切换时保存和恢复现场数据(临时数据)。

对于8006 CPU ⽽⾔,堆栈操作是按字操作。

堆栈单元的地址指针由堆栈指针寄存器SP 的内容提供。

8086/8088微处理器8086是全16位微处理器,内、外数据总线都是16位。

8088是准16位微处理器,内数据总线是16位,外数据总线是8位。

二者除外数据总线位数及与此相关的部分逻辑稍有差别外,内部结构和基本性能相同,指令系统完全兼容。

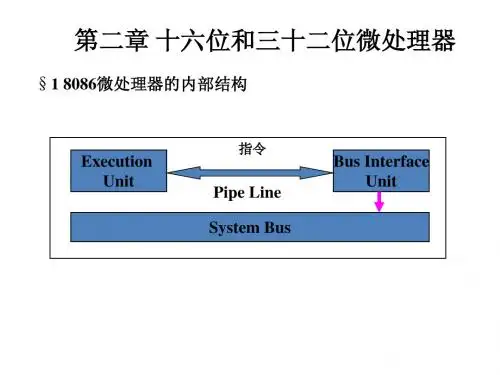

1. 内部结构8086/8088微处理器从功能上可分为两个独立的处理单元:执行单元EU(Execution Unit)和总线接口单元BIU(Bus Interface Unit)。

其内部结构如图2.1所示。

执行单元EU由8个16位的通用寄存器、1个16位的标志寄存器、1个16位的暂存寄存器、1个16位的算术逻辑单元ALU及EU控制电路组成。

8个通用寄存器中,AX、BX、CX、DX为数据寄存器,用于存放参与运算的数据或运算的结果,它们中的每一个既可以作为一个16位寄存器使用,又可以将高、低8位分别作为两个独立的8位寄存器使用。

作为8位寄存器时,它们的名称分别为AL、AH、BL、BH、CL、CH、DL、DH。

这些寄存器除了用作通用寄存器外,通常还有各自特殊的用法: AX作累加器,所有的I/O指令及一部分串操作必须使用AX或AL来执行,另外还有一些指令使用AX及由AX 分出的AL、AH作为缺省的操作数,如乘、除法指令;BX作基址寄存器,在计算内存地址时,常用于存放基址;CX作计数寄存器,可以在循环、重复的串操作及移位操作中被作为计数器来使用;DX作数据寄存器,在一些I/O指令中用来保存端口地址。

指针寄存器SP和BP分别为堆栈指针寄存器和基址指针寄存器,作为通用寄存器的一种,它们可以存放数据,但实际上,它们更经常、更重要的用途是存放内存单元的偏移地址。

而变址寄存器DI和SI则主要用于变址寻址方式的目的变址和源变址。

图2.1 8086/8088CPU内部结构示意图总线接口单元BIU由4个16位的段寄存器(CS、SS、DS、ES)、1个16位的指令指针寄存器IP、1个与EU通信的内部暂存器、1个指令队列、1个计算20位物理地址的地址加法器∑及总线控制电路组成。