15-3_Chapt_13 Editing Current Carrier Data_sc-c_1st

- 格式:pdf

- 大小:403.22 KB

- 文档页数:24

串口和并口的区别悬赏分:0 - 解决时间:2006-10-19 10:01 电脑25针和9针的口哪个是串口哪个是并口有什么区别啊提问者: gr_honey - 三级最佳答案RS-232串行接口定义计算机侧为25针公插: 设备侧为25针母插: 引脚定义 Pin Name ITU-T Dir Description 1 GND 101 Shield Ground 2 TXD 103 Transmit Data 3 RXD 104 Receive Data 4 RTS 105 Request to Send 5 CTS 106 Clear to Send 6 DSR 107 Data Set Ready 7 GND 102 System Ground 8 CD 109 Carrier Detect 9 - - RESERVED 10 - - RESERVED 11 STF 126 Select Transmit Channel 12 S.CD ? Secondary Carrier Detect 13 S.CTS ? Secondary Clear to Send 14 S.TXD ? Secondary Transmit Data 15 TCK 114 Transmission Signal Element Timing 16 S.RXD ? Secondary Receive Data 17 RCK 115 Receiver Signal Element Timing 18 LL 141 Local Loop Control 19 S.RTS ? Secondary Request to Send 20 DTR 108 Data Terminal Ready 21 RL 140 Remote Loop Control 22 RI 125 Ring Indicator 23 DSR 111 Data Signal Rate Selector 24 XCK 113 Transmit Signal Element Timing 25 TI 142 Test Indicator PC/AT 机上的串行口是 9 针公插座,引脚定义为: Pin Name Dir Description 1 CD Carrier Detect 2 RXD Receive Data 3 TXD Transmit Data 4 DTR Data Terminal Ready 5 GND System Ground 6 DSR Data Set Ready 7 RTS Request to Send 8 CTS Clear to Send 9 RI Ring Indicator PC/XT 机上的串行口是 25 针公插座,引脚定义为: Pin Name Dir Description 1 SHIELD - Shield Ground 2 TXD Transmit Data 3 RXD Receive Data 4 RTS Request to Send 5 CTS Clear to Send 6 DSR Data Set Ready 7 GND - System Ground 8 CD Carrier Detect 9 n/c - 10 n/c - 11 n/c - 12 n/c - 13 n/c - 14 n/c - 15 n/c - 16 n/c - 17 n/c - 18 n/c - 19 n/c - 20 DTR Data Terminal Ready 21 n/c - 22 RI Ring Indicator 23 n/c - 24 n/c - 25 n/c - PC 并行接口定义 PC 并行接口外观是 25 针母插座: Pin Name Dir Description 1/STROBE Strobe 2 D0 Data Bit 0 3 D1 Data Bit 1 4 D2 Data Bit 2 5 D3 Data Bit 3 6 D4 Data Bit 4 7 D5 Data Bit 5 8 D6 Data Bit 6 9 D7 Data Bit 7 10 /ACK Acknowledge 11 BUSY Busy 12 PE Paper End 13 SEL Select 14 /AUTOFD Autofeed 15 /ERROR Error 16 /INIT Initialize 17 /SELIN Select In 18 GND Signal Ground 19 GND Signal Ground 20 GND Signal Ground 21 GND Signal Ground 22 GND Signal Ground 23 GND SignalGround 24 GND Signal Ground 25 GND Signal Ground 硬盘串口和并口的区别硬盘接口是硬盘与主机系统间的连接部件,作用是在硬盘缓存和主机内存之间传输数据。

思科-网络专业人士笔记第1章故障处理方法一、网络的复杂性一般网络包括路由、拨号、交换、视频、WAN(ISDN、帧中继、ATM、…)、LAN、VLAN、…二、故障处理模型1、界定问题(Define the Problem)详细而精确地描述故障的症状和潜在的原因2、收集详细信息(Gather Facts)R>信息来源:关键用户、网络管理系统、路由器/交换机1)识别症状:2)重现故障:校验故障依然存在3)调查故障频率:4)确定故障的范围:有三种方法建立故障范围? 由外到内故障处理(Outside-In Troubleshooting):通常适用于有多个主机不能连接到一台服务器或服务器集? 由内到外故障处理(Inside-Out Troubleshooting):? 半分故障处理(Divide-by-Half Troubleshooting)3、考虑可能情形(Consider Possibilities)考虑引起故障的可能原因4、建立一份行动计划(Create the Action Plan)5、部署行动计划(Implement the Action Plan)用于纠正网络故障原因。

从最象故障源处,想出处理方法每完成一个步骤,检查故障是否解决6、观察行动计划执行结果(Observe Results)7、如有行动计划不能解决问题,重复上述过程(Iterate as Needed)三、记录所做修改在通过行动计划解决问题后,建议把记录作为故障处理的一部分,记录所有的配置修改第2章网络文档一、网络基线解决网络问题的最简单途径是把当前配置和以前的配置相比较。

基线文档由不同的网络和系统文档组成,它包括:? 网络配置表? 网络拓扑图? ES网络配置表? ES网络拓扑图创建网络的注意事项:1)确定文档覆盖的范围;2)保持一致:收集网络中所有设备的相同信息;3)明确目标:了解文档的用途;4)文档易于使用和访问;5)及时维护更新文档。

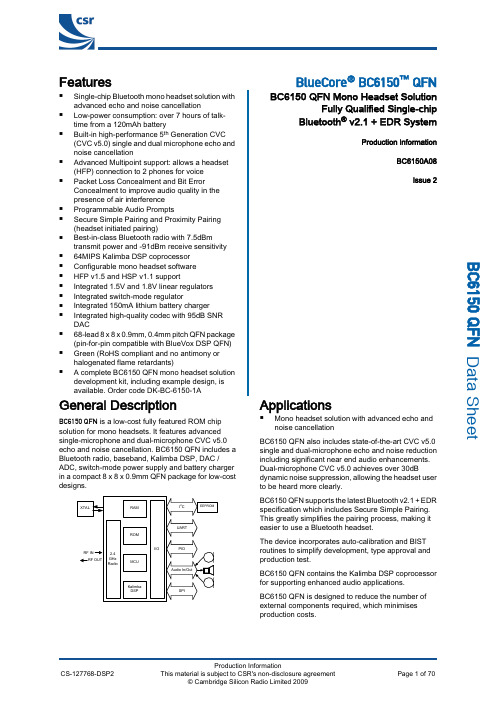

Features _äìÉ`çêÉ∆=_`SNRM »=nck■Single-chip Bluetooth mono headset solution withadvanced echo and noise cancellation ■Low-power consumption: over 7 hours of talk-time from a 120mAh battery ■Built-in high-performance 5th Generation CVC(CVC v5.0) single and dual microphone echo and noise cancellation■Advanced Multipoint support: allows a headset (HFP) connection to 2 phones for voice■Packet Loss Concealment and Bit Error Concealment to improve audio quality in thepresence of air interference■Programmable Audio Prompts■Secure Simple Pairing and Proximity Pairing(headset initiated pairing)■Best-in-class Bluetooth radio with 7.5dBmtransmit power and -91dBm receive sensitivity■64MIPS Kalimba DSP coprocessor■Configurable mono headset software■HFP v1.5 and HSP v1.1 support■Integrated 1.5V and 1.8V linear regulators■Integrated switch-mode regulator■Integrated 150mA lithium battery charger■Integrated high-quality codec with 95dB SNRDAC■68-lead 8 x 8 x 0.9mm, 0.4mm pitch QFN package(pin-for-pin compatible with BlueVox DSP QFN)■Green (RoHS compliant and no antimony orhalogenated flame retardants)■ A complete BC6150 QFN mono headset solutiondevelopment kit, including example design, isavailable. Order code DK‑BC‑6150‑1ABC6150 QFN Mono Headset SolutionFully Qualified Single-chipBluetooth ® v2.1 + EDR SystemProduction InformationBC6150A08Issue 2General Description _`SNRM=nck is a low-cost fully featured ROM chip solution for mono headsets. It features advanced single-microphone and dual-microphone CVC v5.0echo and noise cancellation. BC6150 QFN includes a Bluetooth radio, baseband, Kalimba DSP, DAC /ADC, switch-mode power supply and battery charger in a compact 8 x 8 x 0.9mm QFN package for low-cost designs.Applications■Mono headset solution with advanced echo andnoise cancellationBC6150 QFN also includes state-of-the-art CVC v5.0single and dual-microphone echo and noise reductionincluding significant near end audio enhancements.Dual-microphone CVC v5.0 achieves over 30dBdynamic noise suppression, allowing the headset userto be heard more clearly.BC6150 QFN supports the latest Bluetooth v2.1 + EDRspecification which includes Secure Simple Pairing.This greatly simplifies the pairing process, making iteasier to use a Bluetooth headset.The device incorporates auto-calibration and BISTroutines to simplify development, type approval andproduction test.BC6150 QFN contains the Kalimba DSP coprocessorfor supporting enhanced audio applications.BC6150 QFN is designed to reduce the number ofexternal components required, which minimisesproduction costs._`SNRM=nck Data SheetDocument History RevisionDate Change Reason127 AUG 09Original publication of this document.213 NOV 09Production Information added.SPI interface information updated.If you have any comments about this document, email comments@ givingthe number, title and section with your feedback.Document History_`SNRM=nck Data SheetStatus InformationThe status of this Data Sheet is Production Information .CSR Product Data Sheets progress according to the following format:Advance InformationInformation for designers concerning CSR product in development. All values specified are the target values of thedesign. Minimum and maximum values specified are only given as guidance to the final specification limits and mustnot be considered as the final values.All detailed specifications including pinouts and electrical specifications may be changed by CSR without notice.Pre-production InformationPinout and mechanical dimension specifications finalised. All values specified are the target values of the design.Minimum and maximum values specified are only given as guidance to the final specification limits and must not beconsidered as the final values.All electrical specifications may be changed by CSR without notice.Production InformationFinal Data Sheet including the guaranteed minimum and maximum limits for the electrical specifications.Production Data Sheets supersede all previous document versions.Life Support Policy and Use in Safety-critical ApplicationsCSR's products are not authorised for use in life-support or safety-critical applications. Use in such applications isdone at the sole discretion of the customer. CSR will not warrant the use of its devices in such applications.CSR Green Semiconductor Products and RoHS ComplianceBC6150 QFN devices meet the requirements of Directive 2002/95/EC of the European Parliament and of the Councilon the Restriction of Hazardous Substance (RoHS).BC6150 QFN devices are also free from halogenated or antimony trioxide-based flame retardants and otherhazardous chemicals. For more information, see CSR's Environmental Compliance Statement for CSR GreenSemiconductor Products .Trademarks, Patents and LicencesUnless otherwise stated, words and logos marked with ™ or ® are trademarks registered or owned by CSR plc or itsaffiliates. Bluetooth ® and the Bluetooth ® logos are trademarks owned by Bluetooth ® SIG, Inc. and licensed toCSR. Other products, services and names used in this document may have been trademarked by their respectiveowners.The publication of this information does not imply that any license is granted under any patent or other rights ownedby CSR plc and/or its affiliates.CSR reserves the right to make technical changes to its products as part of its development programme.While every care has been taken to ensure the accuracy of the contents of this document, CSR cannot acceptresponsibility for any errors.Refer to for compliance and conformance to standards information.Status Information_`SNRM=nck Data SheetContents1Device Details (8)2Functional Block Diagram (9)3Package Information (10)3.1Pinout Diagram (10)3.2Device Terminal Functions (11)3.3Package Dimensions (15)3.4PCB Design and Assembly Considerations (16)3.5Typical Solder Reflow Profile (16)4Bluetooth Modem (17)4.1RF Ports (17)4.1.1RF_N and RF_P (17)4.2RF Receiver (17)4.2.1Low Noise Amplifier (17)4.2.2RSSI Analogue to Digital Converter (17)4.3RF Transmitter (18)4.3.1IQ Modulator (18)4.3.2Power Amplifier (18)4.4Bluetooth Radio Synthesiser (18)4.5Baseband (18)4.5.1Burst Mode Controller (18)4.5.2Physical Layer Hardware Engine (18)4.6Basic Rate Modem (18)4.7Enhanced Data Rate Modem (18)5Clock Generation (20)5.1Clock Architecture (20)5.2Input Frequencies and PS Key Settings (20)5.3External Reference Clock (20)5.3.1Input: XTAL_IN (20)5.3.2XTAL_IN Impedance in External Mode (21)5.3.3Clock Start-up Delay (21)5.3.4Clock Timing Accuracy (21)5.4Crystal Oscillator: XTAL_IN and XTAL_OUT (22)5.4.1Load Capacitance (23)5.4.2Frequency Trim (23)5.4.3Transconductance Driver Model (24)5.4.4Negative Resistance Model (24)5.4.5Crystal PS Key Settings (25)6Bluetooth Stack Microcontroller (26)6.1Programmable I/O Ports, PIO and AIO (26)7Kalimba DSP (27)8Memory Interface and Management (28)8.1Memory Management Unit (28)8.2System RAM (28)8.3Kalimba DSP RAM (28)8.4Internal ROM (28)9Serial Interfaces (29)9.1UART Interface (29)9.1.1UART Configuration While Reset is Active (31)9.2Programming and Debug Interface (31)9.2.1Instruction Cycle ..................................................................................................................... 31_`SNRM=nck Data Sheet9.2.2Multi-slave Operation (31)9.3I 2C Interface (31)10Audio Interface (33)10.1Audio Input and Output (33)10.2Mono Audio Codec Interface (33)10.2.1Mono Audio Codec Block Diagram (34)10.2.2ADC (34)10.2.3ADC Digital Gain (34)10.2.4ADC Analogue Gain (35)10.2.5DAC (35)10.2.6DAC Digital Gain (35)10.2.7DAC Analogue Gain (36)10.2.8Microphone Input (36)10.2.9Output Stage (39)10.2.10Side Tone (40)10.2.11Integrated Digital Filter (40)11Power Control and Regulation (42)11.1Power Sequencing (42)11.2External Voltage Source (42)11.3Switch-mode Regulator (43)11.4Low-voltage Linear Regulator (43)11.5Low-voltage Audio Linear Regulator (43)11.6Voltage Regulator Enable Pins (44)11.7Battery Charger (44)11.8LED Drivers (44)11.9Reset, RST# (45)11.9.1Digital Pin States on Reset (46)11.9.2Status after Reset (46)12Example Application Schematic (47)13Electrical Characteristics (48)13.1ESD Precautions (48)13.2Absolute Maximum Ratings (48)13.3Recommended Operating Conditions (48)13.4Input/Output Terminal Characteristics (49)13.4.1Low-voltage Linear Regulator (49)13.4.2Low-voltage Linear Audio Regulator (50)13.4.3Switch-mode Regulator (51)13.4.4Battery Charger (52)13.4.5Reset (53)13.4.6Regulator Enable (53)13.4.7Digital Terminals (54)13.4.8Mono Codec: Analogue to Digital Converter (55)13.4.9Mono Codec: Digital to Analogue Converter (56)13.4.10Clocks (57)13.4.11LED Driver Pads (57)13.4.12Auxiliary ADC (58)14Power Consumption (59)15CSR Green Semiconductor Products and RoHS Compliance (61)15.1RoHS Statement (61)15.1.1List of Restricted Materials (61)16BC6150 QFN Software Stack (62)16.1BC6150 QFN Mono Headset Solution Development Kit (62)16.2BC6150 QFN Mono Headset Solution ................................................................................................. 62_`SNRM=nck Data Sheet16.3Advanced Multipoint Support (62)16.4Programmable Audio Prompts (63)16.5Proximity Pairing (63)16.5.1Proximity Pairing Configuration (63)17Ordering Information (64)17.1BC6150 QFN Mono Headset Solution Development Kit Ordering Information (64)18Tape and Reel Information (65)18.1Tape Orientation (65)18.2Tape Dimensions (65)18.3Reel Information (66)18.4Moisture Sensitivity Level (66)19Document References (67)Terms and Definitions (68)List of FiguresFigure 2.1Functional Block Diagram (9)Figure 3.1Device Pinout (10)Figure 3.2Package Dimensions (15)Figure 4.1Simplified Circuit RF_N and RF_P (17)Figure 4.2BDR and EDR Packet Structure (19)Figure 5.1Clock Architecture (20)Figure 5.2TCXO Clock Accuracy (22)Figure 5.3Crystal Driver Circuit (22)Figure 5.4Crystal Equivalent Circuit (23)Figure 7.1Kalimba DSP Interface to Internal Functions (27)Figure 9.1Universal Asynchronous Receiver (29)Figure 9.2Break Signal (30)Figure 9.3Example EEPROM Connection (32)Figure 10.1BC6150 QFN Audio Interface (33)Figure 10.2Mono Codec Audio Input and Output Stages (34)Figure 10.3ADC Analogue Amplifier Block Diagram (35)Figure 10.4Microphone Biasing (36)Figure 10.5Speaker Output (40)Figure 11.1Voltage Regulator Configuration (42)Figure 11.2LED Equivalent Circuit (45)Figure 12.1Example Application Schematic (47)Figure 16.1Programmable Audio Prompts in External I 2C EEPROM (63)Figure 18.1BC6150 QFN Tape Orientation (65)Figure 18.2Reel Dimensions (66)List of TablesTable 4.1Data Rate Schemes (19)Table 5.1External Clock Specifications (21)Table 5.2Crystal Specification (23)Table 9.1Possible UART Settings (29)Table 9.2Standard Baud Rates (30)Table 9.3Instruction Cycle for a SPI Transaction (31)Table 10.1ADC Digital Gain Rate Selection (34)Table 10.2DAC Digital Gain Rate Selection (35)Table 10.3DAC Analogue Gain Rate Selection (36)Table 10.4Voltage Output Steps ....................................................................................................................... 38_`SNRM=nck Data SheetTable 10.5Current Output Steps (39)Table 11.1BC6150 QFN Voltage Regulator Enable Pins (44)Table 11.2BC6150 QFN Digital Pin States on Reset (46)List of EquationsEquation 5.1Load Capacitance (23)Equation 5.2Trim Capacitance (23)Equation 5.3Frequency Trim (24)Equation 5.4Pullability (24)Equation 5.5Transconductance Required for Oscillation (24)Equation 5.6Equivalent Negative Resistance (25)Equation 9.1Baud Rate (30)Equation 10.1IIR Filter Transfer Function, H(z) (41)Equation 10.2IIR Filter plus DC Blocking Transfer Function, H DC(z) (41)Equation 11.1LED Current (45)Equation 11.2LED PAD Voltage (45)_`SNRM=nckData Sheet1Device DetailsRadio ■Common TX/RX terminal simplifies external matching; eliminates external antenna switch ■BIST minimises production test time ■Bluetooth v2.1 + EDR specification compliant Transmitter ■7.5dBm RF transmit power with level control from a 6-bit DAC over a typical 30dB dynamic range ■Class 2 and Class 3 support without the need for an external power amplifier or TX/RX switch Receiver ■Receiver sensitivity of -91dBm ■Integrated channel filters ■Digital demodulator for improved sensitivity and co-channel rejection ■Real-time digitised RSSI available on HCI interface ■Fast AGC for enhanced dynamic range Synthesiser ■Fully integrated synthesiser requires no external VCO, varactor diode, resonator or loop filter ■Compatible with crystals 16MHz to 26MHz or an external clock 12MHz to 52MHz Kalimba DSP ■Very low power Kalimba DSP coprocessor,64MIPS, 24-bit fixed point core ■Single-cycle MAC; 24 x 24-bit multiply and 56-bit accumulator ■32-bit instruction word, dual 24-bit data memory■6K x 32-bit program RAM, 8K x 24-bit + 8K x 24-bit data RAM ■64 x 32-bit program memory cache when executing from ROM Audio Codec ■16-bit internal codec ■ADC and DAC for stereo audio ■Integrated amplifiers for driving 16Ω speakers; no need for external components ■Support for single-ended speaker termination and line output ■Integrated low-noise microphone bias Physical Interfaces ■Synchronous serial interface for system debugging ■I²C compatible interface to external EEPROMcontaining device configuration data (PS Keys)■UART interface with data rates up to 3Mbits/s■Bidirectional serial programmable audio interfacesupporting PCM, I²S and SPDIF formats■ 2 LED drivers with fadersBaseband and Software■Internal ROM■48KB of internal RAM, allows full-speed datatransfer, mixed voice/data and full piconet support■Logic for forward error correction, header errorcontrol, access code correlation, CRC,demodulation, encryption bit stream generation,whitening and transmit pulse shaping■Transcoders for A-law, µ-law and linear voice fromhost and A-law, µ-law and CVSD voice over air■Configurable mono headset ROM software to set-up headset features and user interface■Support for HFP v1.5 (including three-way calling)and HSP v1.1■Support for Bluetooth v2.1 + EDR specificationSecure Simple Pairing■Proximity Pairing (headset initiated pairing)■Advanced Multipoint support, allowing the headsetto connect to 2 mobile phones or 1 mobile phoneand a VoIP dongle■Programmable audio prompts■Packet Loss Concealment and Bit ErrorConcealment to improve audio quality in thepresence of air interference■DSP based single-microphone CVC v5.0 echo andnoise cancellation is included in the BC6150 QFNfor effective noise cancellation under all conditions■ A high-performance dual-microphone noisecancellation is available using CVC v5.0 is availablein BC6150 QFN providing over 30dB of dynamicnoise suppressionAuxiliary Features■Crystal oscillator with built-in digital trimming■Power management includes digital shutdown andwake-up commands with an integrated low-poweroscillator for ultra-low power Park/Sniff/Hold mode■Clock request output to control external clock■On-chip regulators: 1.5V output from 1.7V to 1.95Vinput■On-chip high-efficiency switched-mode regulator:1.8V output from2.5V to 4.4V input■Power-on-reset cell detects low-supply voltage■10-bit ADC available to applications■On-chip 150mA charger for lithium ion/polymerbatteriesPackage Option■QFN 68-lead, 8 x 8 x 0.9mm, 0.4mm pitch Device Details_`SNRM=nck Data Sheet2Functional Block DiagramG-TW-0115.3.2VREGIN_AUDIO VDD_AUDIO VREGENABLE_L VREGIN_L VREGENABLE_H VSS BAT_PVDD_CHG RF_P XTAL_OUT XTAL_IN LO_REF VDD_LO LED[0]VDD_PADSVDD_MEM RST#TEST_ENVDD_SMP_CORE VDD_CORE VDD_ANA LX VDD_RADIO LED[1]AIO[0]AIO[1]PIO[5:0]VSS_PIO VDD_PIO PIO[14:11, 9]RF_N SPKR_A_PSPKR_A_NMIC_BIASMIC_A_PMIC_A_NMIC_B_NMIC_B_PAU_REF_DCPLUART_TXUART_RXUART_CTS UART_RTS VDD_UARTPIO[7]PIO[8]PIO[6]SPI_CS#SPI_MISO SPI_MOSISPI_CLKFigure 2.1: Functional Block DiagramFunctional Block Diagram_`SNRM=nck Data Sheet3Package Information 3.1Pinout DiagramG-TW-091.4.21234567891018192011121314151617212223242526272829303132333435363738394041424344454647484950515268535455565758596061626364656667Orientation from Top of DeviceFigure 3.1: Device Pinout Package Information_`SNRM=nck Data Sheet3.2Device Terminal FunctionsBluetooth Radio Lead Pad Type Supply Domain DescriptionRF_N65RFVDD_RADIO Transmitter output/switched receiverRF_P64RF Complement of RF_N Synthesiser andOscillatorLead Pad Type Supply Domain DescriptionXTAL_IN3Analogue VDD_ANA For crystal or external clock inputXTAL_OUT4Drive for crystalLO_REF5Reference voltage to decouple the synthesiserSPI Interface Lead Pad Type Supply Domain DescriptionSPI_MOSI28Input, with weak internal pull-downVDD_PADSSPI data inputSPI_CS#30Bidirectional with weakinternal pull-downChip select for SPI, active lowSPI_CLK29Bidirectional with weakinternal pull-downSPI clockSPI_MISO31Bidirectional with weakinternal pull-downSPI data outputUART Interface Lead Pad Type Supply Domain DescriptionUART_TX9Output, tri-state, with weakinternal pull-downVDD_UARTUART data output, active highUART_RX10Bidirectional with weakinternal pull-downUART data input, active highUART_RTS12Bidirectional CMOS output,tri-state, with weak internalpull-upUART request to send active lowUART_CTS11CMOS input with weakinternal pull-downUART clear to send active low_`SNRM=nckData SheetPIO Port Lead Pad Type Supply Domain Description PIO[14]20Bidirectional withprogrammable strength internal pull-up/down VDD_PADS Programmable input/output linePIO[13]19PIO[12]18PIO[11]15PIO[9]14PIO[8]21PIO[7]22PIO[6]23PIO[5]24PIO[4]25PIO[3]58Bidirectional withprogrammable strength internal pull-up/down VDD_PIO Programmable input/output linePIO[2]59PIO[1]60PIO[0]61AIO[1]6Bidirectional VDD_ANA Programmable input/output line AIO[0]7_`SNRM=nck Data SheetAudio Lead Pad Type Supply Domain DescriptionSPKR_A_N56Analogue VDD_AUDIO Speaker output, negative, channel ASPKR_A_P57Analogue VDD_AUDIO Speaker output, positive, channel AMIC_A_N52Analogue VDD_AUDIO Microphone input, negative, channel AMIC_A_P51Analogue VDD_AUDIO Microphone input, positive, channel AMIC_B_N50Analogue VDD_AUDIO Microphone input, negative, channel BMIC_B_P48Analogue VDD_AUDIO Microphone input, positive, channel BMIC_BIAS45Analogue VDD_AUDIO,BAT_PMicrophone biasAU_REF_DCPL55Analogue VDD_AUDIO Decoupling of audio reference, for high-quality audioLED Drivers Lead Pad Type Supply Domain Description LED[1]33Open drain output Open drainLED driver LED[0]32LED driver Test and Debug Lead Pad Type Supply Domain DescriptionRST#26Input with weak internal pull-upVDD_PADSReset if low. Input debounced somust be low for >5ms to cause aresetTEST_EN27Input with strong internal pull-downFor test purposes only, leaveunconnected_`SNRM=nckData SheetPower SuppliesControl Lead DescriptionVREGENABLE_L68Low-voltage linear regulator and low-voltage audiolinear regulator enable, active highVREGIN_L 1Input to internal low-voltage regulatorVREGENABLE_H 35Switch-mode regulator enable, active highVREGIN_AUDIO 46Input to internal audio low-voltage linear regulator VDD_AUDIO 47Positive supply for audioLX 37Switch-mode regulator outputVDD_ANA 2Positive supply output for analogue circuitry and1.5V regulated output, from internal low-voltageregulatorVDD_PIO 62Positive supply for digital input/output ports PIO[3:0]VDD_PADS 16Positive supply for all other digital Input/Output portsincluding PIO[14:11,9:4]VDD_CORE 17, 34Positive supply for internal digital circuitryVDD_RADIO 63, 66Positive supply for RF circuitryVDD_UART 13Positive supply for UART portsVDD_LO 67Positive supply for local oscillator circuitryBAT_P 38Lithium ion/polymer battery positive terminal. Batterycharger output and input to switch-mode regulatorVDD_CHG 39Lithium ion/polymer battery charger inputVDD_SMP_CORE 36Positive supply for switch-mode control circuitry VSS Exposed Pad Ground connectionsUnconnected Leads (N/Cs)Description8, 40, 41, 42, 43, 44, 49, 53, 54Leave unconnected_`SNRM=nck Data Sheet3.3Package DimensionsG-T W-0939.4.3Orientation from TopSeating PlaneOrientation from BottomFigure 3.2: Package Dimensions_`SNRM=nck Data Sheet3.4PCB Design and Assembly ConsiderationsThis section lists recommendations to achieve maximum board-level reliability of the 8 x 8 x 0.9mm QFN 68-leadpackage:■NSMD lands (lands smaller than the solder mask aperture) are preferred, because of the greater accuracy of the metal definition process compared to the solder mask process. With solder mask defined pads, theoverlap of the solder mask on the land creates a step in the solder at the land interface, which can causestress concentration and act as a point for crack initiation.■CSR recommends that the PCB land pattern to be in accordance with IPC standard IPC-7351.■Solder paste must be used during the assembly process.3.5Typical Solder Reflow ProfileSee Typical Solder Reflow Profile for Lead-free Devices for information._`SNRM=nckData Sheet4Bluetooth Modem4.1RF Ports4.1.1RF_N and RF_PRF_N and RF_P form a complementary balanced pair and are available for both transmit and receive. On transmit their outputs are combined using an external balun into the single-ended output required for the antenna. Similarly,on receive their input signals are combined internally.Both terminals present similar complex impedances that may require matching networks between them and the balun. Viewed from the chip, the outputs can each be modelled as an ideal current source in parallel with a lossy capacitor. An equivalent series inductance can represent the package parasitics.G-T W-03349.2.2RF_NRF_PFigure 4.1: Simplified Circuit RF_N and RF_PRF_N and RF_P require an external DC bias. The DC level must be set at VDD_RADIO.4.2RF ReceiverThe receiver features a near-zero IF architecture that allows the channel filters to be integrated onto the die. Sufficient out-of-band blocking specification at the LNA input allows the receiver to be used in close proximity to GSM and W‑CDMA cellular phone transmitters without being desensitised. The use of a digital FSK discriminator means that no discriminator tank is needed and its excellent performance in the presence of noise allows BC6150 QFN to exceed the Bluetooth requirements for co-channel and adjacent channel rejection.For EDR, the demodulator contains an ADC which digitises the IF received signal. This information is then passed to the EDR modem.4.2.1Low Noise AmplifierThe LNA operates in differential mode and takes its input from the shared RF port.4.2.2RSSI Analogue to Digital ConverterThe ADC implements fast AGC. The ADC samples the RSSI voltage on a slot-by-slot basis. The front-end LNA gain is changed according to the measured RSSI value, keeping the first mixer input signal within a limited range. This improves the dynamic range of the receiver, improving performance in interference limited environments._`SNRM=nck Data Sheet4.3RF Transmitter4.3.1IQ ModulatorThe transmitter features a direct IQ modulator to minimise frequency drift during a transmit timeslot, which results in a controlled modulation index. Digital baseband transmit circuitry provides the required spectral shaping.4.3.2Power AmplifierThe internal PA has a maximum output power that allows BC6150 QFN to be used in Class 2 and Class 3 radios without an external RF PA.4.4Bluetooth Radio SynthesiserThe Bluetooth radio synthesiser is fully integrated onto the die with no requirement for an external VCO screening can, varactor tuning diodes, LC resonators or loop filter. The synthesiser is guaranteed to lock in sufficient time across the guaranteed temperature range to meet the Bluetooth v2.1 + EDR specification.4.5Baseband4.5.1Burst Mode ControllerDuring transmission the BMC constructs a packet from header information previously loaded into memory-mapped registers by the software and payload data/voice taken from the appropriate ring buffer in the RAM. During reception, the BMC stores the packet header in memory-mapped registers and the payload data in the appropriate ring buffer in RAM. This architecture minimises the intervention required by the processor during transmission and reception.4.5.2Physical Layer Hardware EngineDedicated logic performs the following:■Forward error correction■Header error control■Cyclic redundancy check■Encryption■Data whitening■Access code correlation■Audio transcodingFirmware performs the following voice data translations and operations:■A-law/µ-law/linear voice data (from host)■A-law/µ-law/CVSD (over the air)■Voice interpolation for lost packets■Rate mismatch correctionThe hardware supports all optional and mandatory features of Bluetooth v2.1 + EDR specification including AFH and eSCO.4.6Basic Rate ModemThe basic rate modem satisfies the basic data rate requirements of the Bluetooth v2.1 + EDR specification. The basic rate was the standard data rate available on the Bluetooth v1.2 specification and below, it is based on GFSK modulation scheme.Including the basic rate modem allows BC6150 QFN compatibility with earlier Bluetooth products.The basic rate modem uses the RF ports, receiver, transmitter and synthesiser, alongside the baseband components described in Section 4.5.4.7Enhanced Data Rate ModemThe EDR modem satisfies the requirements of the Bluetooth v2.1 + EDR specification. EDR has been introduced to provide 2x and 3x data rates with minimal disruption to higher layers of the Bluetooth stack. BC6150 QFN supportsboth the basic and enhanced data rates and is compliant with the Bluetooth v2.1 + EDR specification._`SNRM=nck Data SheetAt the baseband level, EDR uses the same 1.6kHz slot rate and the 1MHz symbol rate defined for the basic data rate. EDR differs in that each symbol in the payload portion of a packet represents 2 or 3 bits. This is achieved using 2 new distinct modulation schemes. Table 4.1 and Figure 4.2 summarise these. Link Establishment and Management are unchanged and still use GFSK for both the header and payload portions of these packets.The enhanced data rate modem uses the RF ports, receiver, transmitter and synthesiser, with the baseband components described in Section 4.5.Data Rate Scheme Bits Per Symbol ModulationBasic Rate 1GFSKEDR 2π/4 DQPSKEDR 38DPSK (optional)Table 4.1: Data Rate SchemesG-TW-0244.2.3Enhanced Data Rate Figure 4.2: BDR and EDR Packet Structure_`SNRM=nck Data Sheet。

绪论:BTS的故障是按故障的起因和重要性进行分类的:▪ 1A级:MO内的故障,它会影响MO的功能特性.▪ 1B级:MO外的故障,它也会影响MO的功能特性.▪ 2A级:MO内的故障,它不会影响MO的功能特性.BSC要接收以上的BTS故障报告,应采用下列措施:▪ 1A级: MO退出操作和测试.- 如果测试结果表明MO没有故障,那么MO将返回操作状态,并且其故障以间歇性故障处理.故障计数器将对间歇性故障进行累加,当发生间歇性故障的次数太高时,MO将会永久地退出工作状态.- 如果测试结果表明MO有故障,那么MO将永久地退出工作状态,直到故障停止或人工干涉才能恢复正常状态. 在BSC/OSS上将会产生一个A2告警.▪ 1B级: MO将永久地退出工作状态,直到故障停止或人工干涉才能恢复正常状态. 在BSC/OSS上将会产生一个A2告警.▪ 2A级:在BSC/OSS上将会产生一个A2或A3告示警. 但MO仍处于工作状态.应注意的是:CF或TRXC上的2A级故障在从属MO中却被认为是1级故障.总是在CF/TRXC上读取RU的故障映象来进行故障定位.但有时应紧记要替换的被检测到的故障单元,以便更换. BTS的故障信息可以从BSC上或站上OMT接口用人机命令MML来获得。

▪从BSC上获得:- 在MO中所有激活的告警: RXASP:MO=RXO…;- 在TG中所有激活的故障(1级): RXMFP:MO=RXOTG-x,FAULTY,SUBORD;- 在MO中所有激活的故障: RXMFP:MO=RXO…;- MO的故障记录: RXELP:MO=RXO…;▪从OMT上获得:- 在TG中所有激活的故障: ”System view(系统视图) / 选择 RBS 2000 / Operations操作(或按右键) /Monitor(监视)/ Fault status(故障状态)”- 某个RU的故障记录: ”Hardware view(硬件视图) /选择RU / Operations操作(或按右键) / Save log(保存记录)” (只有 DXU, TRU和ECU才有记录区).如果在CF/TRXC上产生RU单元的故障映象,其上的红灯将会发亮. 但这不一定就指此单元一定有故障,这也可能指此单元检测到其他单元有故障。

中国移动通信有限公司分公司 发布2007-6-30发布 2007-6-30实施 移动通信维护手册爱立信交换设备维护分册-故障处理版本号:1.0.0目录1 APZ部分: (1)1.1 故障描述:告警BACKUP INFORMATION FAULT (1)1.2 故障描述:告警SIZE ALTERATION OF DATA FILES SIZE CHANGE REQUIRED (1)1.3 故障描述:告警AUDIT FUNCTION THRESHOLD SUPERVISION (2)1.4 故障描述:告警CP FAULT (2)1.5 故障描述:告警SOFTWARE ERROR (3)1.6 故障描述:告警SYSTEM RESTART (3)2 APT部分: (3)2.1 故障描述:告警ANALYSIS DATA FAULT (3)2.2 故障描述:告警BLOCKING SUPERVISION (4)2.3 故障描述:告警CCITT7 DESTINATION INACCESSIBLE (5)2.4 故障描述:告警CCITT7 SIGNALLING LINK FAILURE (5)2.5 故障描述:告警CCITT7 LINK SET SUPERVISION (6)2.6 故障描述:告警DIGITAL PATH FAULT SUPERVISION (6)2.7 故障描述:告警DISTURBANCE SUPERVISION OF TRUNK ROUTES (7)2.8 故障描述:告警GROUP SWITCH FAULT (7)2.9 故障描述:告警SEMIPERMANENT CONNECTION FAULT (8)2.10 故障描述:告警SWITCHING NETWORK TERMINAL FAULT (9)2.11 故障描述:告警NM ROUTE LOAD STATE CHANGE (10)2.12 故障描述:告警RP FAULT (10)2.13 故障描述:告警SIGNALLING FAULT SUPERVISION (11)2.14 故障描述:告警SYNCHRONOUS DIGITAL PATH FAULT SUPERVISION (11)2.15 故障描述:告警NETWORK SYNCHRONIZATION FAULT (12)2.16 故障描述:告警EVENT REPORTING THRESHOLD REACHED,门限已达到80% (12)2.17 故障描述:告警M3UA DESTINATION INACCESSIBLE (12)3 IOG部分: (13)3.1 故障描述:告警ALI FAULT MAG PCB ADDINFO ALI-0 - NO CONTACT (13)3.2 故障描述:告警PORT BLOCKED (14)3.3 故障描述:告警PVC SET-UP FAILURE (14)3.4 故障描述:告警LINE UNIT BLOCKED (15)3.5 故障描述:告警SP NODE AUTOMATICALLY BLOCKED (16)3.6、故障描述:告警SP TRANSIENT FAULT SUPERVISION (16)4 APG部分 (17)4.1 故障描述:告警AP LOG STATISTICS (17)4.2 故障描述:告警AP ANTIVIRUS FUNCTION FAULT (17)4.3 故障描述:告警AP FAULT (18)4.3.1 MIRRORED DISKS NOT REDUNDANT:磁盘镜像有问题引起。

RJ45接口通常用于数据传输,共有八芯做成,最常见的应用为网卡接口。

RJ45是各种不同接头的一种类型(例如:RJ11也是接头的一种类型,不过它是电话上用的);RJ45头跟据线的排序不同的法有两种,一种是橙白、橙、绿白、蓝、蓝白、绿、棕白、棕;另一种是绿白、绿、橙白、蓝、蓝白、橙、棕白、棕;因此使用RJ45接头的线也有两种即:直通线、交插线。

10 100base tx RJ45接口是常用的以太网接口,支持10兆和100兆自适应的网络连接速度,其实在100兆网络中实际只应用了4根线来传输数据,另4根是备份的.传输的信号为数字信号,双铰线最大传输100米距离.网卡上以及Hub 上接口的外观为8 芯母插座,如图:RJ45接口pc端的,网线为8 芯公插头10 100base tx RJ45接口引脚定义如下Pin Name Description1TX+Tranceive Data+ (发信号+)2TX-Tranceive Data- (发信号-)3RX+Receive Data+ (收信号+)4n/c Not connected (空脚)5n/c Not connected (空脚)6RX-Receive Data- (收信号-)7n/c Not connected (空脚)8n/c Not connected (空脚)RS232串行接口引脚定义图计算机侧为25针公插:设备侧为25针母插:引脚定义Pin Name ITU-T Dir Description1GND101Shield Ground2TXD103Transmit Data3RXD104Receive Data4RTS105Request to Send5CTS106Clear to Send6DSR107Data Set Ready7GND102System Ground8CD109Carrier Detect9--RESERVED10--RESERVED11STF126Select Transmit Channel12S.CD?Secondary Carrier Detect13S.CTS?Secondary Clear to Send14S.TXD?Secondary Transmit Data15TCK114Transmission Signal Element Timing 16S.RXD?Secondary Receive Data17RCK115Receiver Signal Element Timing18LL141Local Loop Control19S.RTS?Secondary Request to Send20DTR108Data Terminal Ready21RL140Remote Loop Control22RI125Ring Indicator23DSR111Data Signal Rate Selector24XCK113Transmit Signal Element Timing25TI142Test Indicatorrj45接口定义/rj45针脚定义/rj45引脚定义10 100base tx rj45接口是常用的以太网接口,支持10兆和100兆自适应的网络连接速度,网卡上以及 Hub 上接口的外观为 8 芯母插座 (RJ45):rg45接口pc端的,网线为 8 芯公插头:rg45接口外观图,,其实在100兆网络中实际只应用了4根线来传输数据,另4根是备份的.传输的信号为数字信号,双铰线最大传输100米距离,10 100base tx rj45接口引脚定义Pin Name Description1 TX+ Tranceive Data+ (发信号+)2 TX- Tranceive Data- (发信号-)3 RX+ Receive Data+ (收信号+)。

爱⽴信告警代码汇总级别告警代码级别告警代码告警名称RXOCF1A_1RXOCF1A_1重启,加电RXOCF1A_2RXOCF1A_2重启,切换RXOCF1A_3RXOCF1A_3看门狗(Watchdog)重启RXOCF1A_4RXOCF1A_4软件故障重启RXOCF1A_5RXOCF1A_5RAM故障重启RXOCF1A_6RXOCF1A_6重启,内部功能修改RXOCF1A_8RXOCF1A_8定时装置VCO故障RXOCF1A_9RXOCF1A_9时钟分配故障(仅提供软件版本R9)/定时总线故RXOCF1A_10RXOCF1A_10室内温度超出安全范围RXOCF1A_14RXOCF1A_14总线故障RXOCF1A_15RXOCF1A_15RBS数据库(软件版本R9)/IDB遭到破坏(软件版RXOCF1A_16RXOCF1A_16RU数据库遭到破坏RXOCF1A_17RXOCF1A_17硬件和IDB不相容RXOCF1A_18RXOCF1A_18内部配置失败RXOCF1A_21RXOCF1A_21硬件错误RXOCF1A_22RXOCF1A_22⽆法计算开始时间RXOCF1A_23RXOCF1A_23时间分配故障RXOCF2A_7RXOCF2A_7RX内部放⼤器错误RXOCF2A_8RXOCF2A_8超过VSWR限制RXOCF2A_9RXOCF2A_9超过电源限制RXOCF2A_12RXOCF2A_12RX最⼤/最⼩增益超标RXOCF2A_13RXOCF2A_13定时装置VCO⽼化RXOCF2A_14RXOCF2A_14⽆法进⾏监管/通信(软件版本R9);CDU⽆法进⾏RXOCF2A_15RXOCF2A_15⽆法监测VSWR/输出功率RXOCF2A_16RXOCF2A_16超出正常的室内温度范围RXOCF2A_17RXOCF2A_17内部湿度RXOCF2A_18RXOCF2A_18直流电压超出正常范围RXOCF2A_19RXOCF2A_19电源和环境系统处于独⽴模式RXOCF2A_21RXOCF2A_21内部电源容量下降RXOCF2A_22RXOCF2A_22备⽤电池的电量下降RXOCF2A_23RXOCF2A_23环境温度适应能⼒下降RXOCF2A_24RXOCF2A_24硬件故障RXOCF2A_25RXOCF2A_25DXU或ECU负载⽂件丢失RXOCF2A_26RXOCF2A_26温度传感器故障RXOCF2A_27RXOCF2A_27系统电压传感器故障RXOCF2A_28RXOCF2A_28A/D转换器故障RXOCF2A_30RXOCF2A_30总线故障RXOCF2A_31RXOCF2A_31频繁出现的软件故障RXOCF2A_32RXOCF2A_32内存损坏RXOCF2A_33RXOCF2A_33RX分级接受丢失RXOCF2A_34RXOCF2A_34输出电压故障RXOCF2A_36RXOCF2A_36RU数据库遭到破坏RXOCF2A_37RXOCF2A_37断路器或保险丝断开RXOCF2A_38RXOCF2A_38使⽤默认值RXOCF2A_39RXOCF2A_39RX电缆断路RXOCF2A_41RXOCF2A_41与TRU失去通信RXOCF2A_43RXOCF2A_43内部配置失败RXOCF2A_44RXOCF2A_44ESB分配失败RXOCF2A_45RXOCF2A_45温度过⾼RXOCF2A_46RXOCF2A_46DB参数故障RXOCF2A_47RXOCF2A_47天线跳频失败RXOCF2A_48RXOCF2A_48GPS同步故障RXOCF2A_49RXOCF2A_49电池备⽤时间⽐预定时间短RXOCF2A_50RXOCF2A_50RBS在电池上运⾏RXOCF2A_51RXOCF2A_51TMA⽆法进⾏监管/通信RXOCF2A_52RXOCF2A_52CXU⽆法进⾏监管/通信RXOCF2A_53RXOCF2A_53硬件和IDB不兼容RXOCF2A_57RXOCF2A_57接收通路不平衡具体处理搞作建议只是提⽰信息,不是故障。

13-3目前搬送数据的编辑移动到STMode的top(最初)选单。

页面选择[CARR]。

选择「搬送参数」。

搬送参数修正一部分当前的搬送数据。

在此进行有关Lead Frame搬送动作的细微设定。

13-3-1有关Frame搬送动作的功能设定(PAR1)进行下记的设定。

・・・(1) *1) *2)・・・(2) *3) *4)・・・(2) *5)・・・(2)・・・(3) *6)・・・(4) *6)・・・(5) *6)・・・(5) *7) *8)*1) NOT → ALL → TOP → F-TOP → IN-FULL*2) PRE → B’g → TOTAL*3) NOT → ALL → LAST*4) DOWN → OPEN*5) NOT → ACT*6) OFF → ON*7) PLATE → WORK → INHI-P*8) THROUG → SEPARA(1)预热的设定在「预热」执行有关预热的设定。

预热是指事先加热焊线前的Unit。

通过此设定,管理Frame搬送时的Heater Plate与Unit的接触时间,接触时间未达到设定时间的Unit作为加热不足,不提供给焊线Stage或不进行焊线动作。

设定项目有,选择对象Unit,要预热位置的选择,指定接触时间。

在第1Cell指定是否使用预热功能,使用时指定作为对象的Unit。

指定通过cyclic切换进行,可在以下5个选项中选择。

[ NOT ]:不使用预热功能。

有关预热的设定全部无效。

[ ALL ]:对于所有的Unit管理时间经过。

在第3 Cell(字段)输入时间。

[ TOP ]:对于第1 Unit管理时间经过。

在第3 Cell(字段)输入时间。

[ F-TOP ]:对于第1Frame的第1 Unit管理时间经过。

在第3 Cell(字段)输入时间。

第1Frame是指,焊线Stage中没有先行Frame状态时供应的Frame。

是「Full AutoStart」后最初被供应的Frame 。

又,由于Loader Stop,magazine reset等原因使暂时焊线Stage中没有Frame时,下一个供给的Frame就是第1Frame 。

[ IN-FULL]:对于所有的Unit管理时间经过。

与ALL的不同点是,管理时间有3种。

因此,第选择了第1 Cell单。

选择「IN-FULL」时,在专用输入选单中输入3种类的时间。

「F-TOP」是,把第1Frame的第1Unit搬送到Stage时的时间。

「TOP」是,把其他Frame的第1 Unit搬送到Stage时的时间。

「CENTER」是,把其他的Unit搬送到Stage时的时间。

时间单位都是毫秒。

在第2Cell中指定要预热的位置。

用此指定可以判断监视Heater Plate(加热板)的接触时间的范围。

通过cyclic切换进行指定,以下的3中选项中选择。

[ PRE ]: 对于前端检知Sensor(感知器)位置到焊线Stage(区域)前侧之间的Unit监视接触时间。

[ B'g ]:对于焊线stage的unit监视接触时间。

[ TOTAL ]:在「PRE」「B’g」两方监视接触时间。

[ INDVDL ]:在「PRE」「B’g」两方,并加上在个别方监视接触时间。

选择了第2call「INDVDL」专用时间的输入选单。

选择「INDVDL」时,在专用的时间输入选单中输入3种类的时间。

「PRE」是指从前端检出感知器的位置到焊线stage前侧之间的unit的接触时间。

「MAIN1ST」是指从frame的第1unit被搬送到B’gstage后到开始B’g之间的预热时间。

「MAINOTHER」指从frame的第1unit以外的unit被搬送到B’gstage后到开始B’g之间的预热时间。

时间单位都是毫秒。

第3cell中设定在第1cell选择了「IN-FULL」以外时的接触时间。

选择「INDVDL」时时「PRE」的设定时间。

输入数值。

单位是毫秒。

●与其他的功能并用时,不是必须要使用预热功能。

这是因为对于过了接触时间的unit,即使放下heater plate(加热板)直接放置unit也不会感知。

特别是与冷却功能并用时,需要考虑此情况后再进行设定。

(2)冷却的设定执行冷却相关的设定。

冷却是指将搬送动作延迟到frame冷却为止。

通过此设定,在冷却位置一直到指定时间经过为止不执行从stage的unit排出动作或UL侧magazine 的frame收纳动作。

设定项目有对象unit的选择,冷却位置的指定,冷却方法的选择,冷却时间的指定。

「Bg后冷却」中,对于把unit从stage排出时的冷却,用「排出后冷却」把frame收纳到UL侧magazine时的冷却进行设定。

又,在「第2排出后冷却」设定了「排出后冷却」时,可以重复进行指定次数内的搬送指定距离并在指定时间内待机的动作。

「Bg后冷却」的第1字段是否要进行焊线stage内的冷却时,选择进行指定对象unit。

指定通过cyclic进行切换,可以从以下3项中选择。

[ NOT ]:不进行焊线stage内的冷却。

[ ALL ]:对于所有的unit,焊线完成后从stage排出时等待指定时间。

[ LAST ]:仅对于frame的最终unit,焊线完成后从stage排出时等待指定时间。

「Bg后冷却」的第2字段,指定焊线stage的冷却时的work clamp状态。

通过cyclic(循环)切换进行指定,可以从以下2项中选择。

[ DOWN ]:工件压板在压着状态下,只下降heater plate(加热板)。

[ OPEN ]:工件压板上升,heater plate下降。

「Bg后冷却」的第3字段,设定冷却时间。

请输入数值。

单位是毫秒。

「排出后冷却」的第1字段,设定在frame收纳到UL侧magazine时是否要进行冷却。

[ NOT ]:执行将frame收纳到UL侧magazine时的冷却。

[ ACT ]:将最后的unit从焊线stage输出后,搬送到指定位置并等待指定时间。

「排出后冷却」的第2字段指定冷却位置。

输入最后的unit在焊线stage状态下的搬送量的数值。

单位为um,可以输入最小刻度5um。

「排出后冷却」的第3字段,设定在冷却位置的冷却时间。

请输入数值。

单位为毫秒。

「第2排出后冷却」的第1字段指定重复的次数。

「第2排出后冷却」的第2字段,指定冷却中搬送的距离。

输入1次的搬送量。

单位为um,可输入的最小刻度为5um。

「第2排出后冷却」的第3字段,指定每次搬送的冷却时间。

请输入数值。

单位为um,可输入的最小刻度为5um。

(3)work re-hold的设定「re-hold」中预热完成后设定是否要进行work re-hold。

work re-hold是指焊线区域执行预热后,一时解除work clamp的lead frame保持的功能。

在受热变形大的品种在焊线区域进行预热时,由于预热中的热变形把stress(应压)压着在work clamp的情况发生。

一直接进行焊线,在焊线完成后解放work clamp时可能有stress被解放,影响到wire的情况发生。

通过cyclic切换进行指定,可以从如下2项中选择。

[ OFF ]:焊线区域预热完成后不执行work re-hold。

[ ON ]:焊线区域预热完成后执行work re-hold。

(4)frame(支架)真空吸附的设定「VACUUM」中,unit搬送到焊线区域时指定是否要真空吸着。

真空吸着是指,真空吸着焊线区域内的unit固定到加热板的功能。

仅对于焊线区域存在通过支架供给动作搬送的unit时,与加热板的上下动作进行连续动作ON/OFF真空。

通过cyclic切换进行指定,可以从如下2项中选择。

[ OFF ]:一概不执行真空吸着的ON/OFF。

[ ON ]:仅限于焊线区域存在搬送的unit时,上下加热板与真空的ON/OFF连动。

(5)吸附后Ri horudo的设定吸附后指定是否进行Ri horudo[ ON ] :进行Ri horudo。

[ OFF ] :不进行Ri horudo(6)工件压板/加热板的动作设定「工件压板」中指定工件压板/加热板的动作条件。

在第1字段指定工件压板/加热板的的动作顺序。

指定是通过cyclic切换进行,可以从如下3项中选择。

[ PLATE ]:关闭work clamp时,加热板上升,工件压板下降。

打开时工件压板上升,加热板下降。

[ WORK ]:关闭work clamp时,工件压板下降, 加热板上升。

加热板下降, 打开时工件压板上升。

[ INHI-P ]:支架搬送动作时保持加热板上升。

搬送中的work clamp的开闭,仅对工件压板上下移动。

但是,手动开关的work clamp单独动作时,加热板也动作。

此时工件压板/加热板的动作顺序与PLATE相同。

在第2字段,指定动作时在cam停留点是否要一时停止。

通过cyclic切换进行指定,可以从如下2项中选择。

[ THROUG ]:work clamp动作时,在cam的停留点不能临时停止[ SEPARA ]:work clamp动作时,在cam的停留点临时停止13-3-2有关支架搬送动作的功能设定(PAR2)执行下记的设定。

・・・(1) *1) *2) *3)・・・(2)*1) CLOSE → OPEN → DOWN → OPEN+Y → DOWN+Y*2) NONE → ALL → TOP → ANY*3) L.LOC → PATTRN → L.ALGN(1)支架检出的设定「FRM检出」,「阈值」进行有关支架检出动作的设定。

支架检出是指,使用识别功能对焊线支架供应的unit输送偏移进行检出及补正排出的功能。

「FRM检出」的第1字段,指定通过识别进行输送偏移的检出时的work clamp状态。

通过cyclic切换进行指定,可以从如下3项中选择。

[ CLOSE ]:在work clamp关闭状态下进行识别。

[ OPEN ]:在work clamp开启状态下进行识别。

[ DOWN ]:仅在工件压板下降的状态下进行识别。

[ OPEN+Y]:开启work clamp,通过移动rail也可以补正Y方向的状态下进行识别。

[ DOWN+Y]:仅在工件压板下降的状态下,通过移动rail也可以补正Y方向的状态下进行识别。

「FRM检出」第2字段,指定是否要使用frame检出功能,使用时指定对象unit。

通过cyclic切换进行指定,可以从如下4项中选择。

[ NONE ]:不能使用frame检出。

[ ALL ]:所有的unit执行检出。

[ TOP ]:仅对于frame的最初unit执行检出。

[ ANY ]:从frame的所有unit中任意选择对象unit。

选择「ANY」显示对象unit选择选单画面。