5509A开发板存储空间和存储器映射

- 格式:pdf

- 大小:113.15 KB

- 文档页数:5

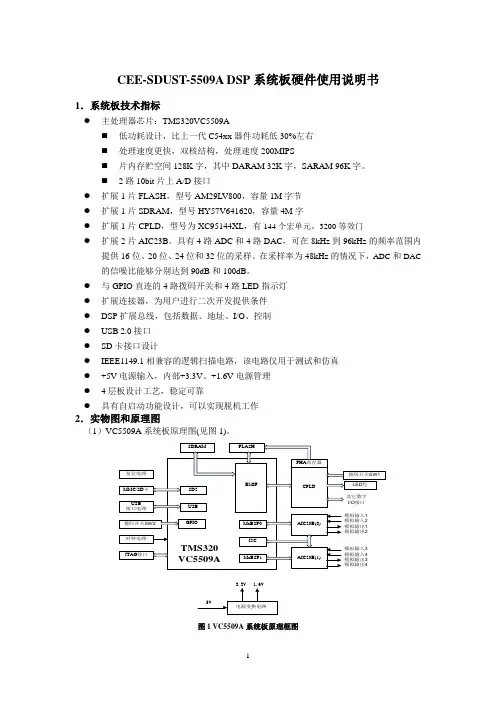

CEE-SDUST-5509A DSP系统板硬件使用说明书1.系统板技术指标●主处理器芯片:TMS320VC5509A⏹低功耗设计,比上一代C54xx器件功耗低30%左右⏹处理速度更快,双核结构,处理速度200MIPS⏹片内存贮空间128K字,其中DARAM 32K字,SARAM 96K字。

⏹2路10bit片上A/D接口●扩展1片FLASH,型号AM29LV800,容量1M字节●扩展1片SDRAM,型号HY57V641620,容量4M字●扩展1片CPLD,型号为XC95144XL,有144个宏单元,3200等效门●扩展2片AIC23B。

具有4路ADC和4路DAC,可在8kHz到96kHz的频率范围内提供16位、20位、24位和32位的采样。

在采样率为48kHz的情况下,ADC和DAC 的信噪比能够分别达到90dB和100dB。

●与GPIO直连的4路拨码开关和4路LED指示灯●扩展连接器,为用户进行二次开发提供条件●DSP扩展总线,包括数据、地址、I/O、控制●USB 2.0接口●SD卡接口设计●IEEE1149.1相兼容的逻辑扫描电路,该电路仅用于测试和仿真●+5V电源输入,内部+3.3V、+1.6V电源管理●4层板设计工艺,稳定可靠●具有自启动功能设计,可以实现脱机工作2.实物图和原理图(1)VC5509A系统板原理图(见图1)。

图1 VC5509A系统板原理框图(2)VC5509A 系统板器件布局(参见图2)图2 VC5509A 系统板器件布局图(3)VC5509A 系统板外部接口(见图3)图3 VC5509A 系统板外部接口示意图3.接插件位置和拨档开关设置4路用户拨码开关(SW1)和4路用户LED 指示灯(DS4~DS7)与CPLD 相连,用户可以通过CPLD 中的控制寄存器USER_REG 读取用户拨码开关(SW1)的状态,或控制用户LED 指示灯(DS4~DS7)的开关。

控制寄存器USER_REG 的地址为0x400601,D7~D4只读,D3~D0可读写,见表1。

TMS320C5509A DSP分页烧写FLASH存储器及自举引导的实现方法TI公司的DSP芯片TMS320C5509A(简称5509A)是性能卓越的低功耗定点DSP,在嵌入式系统中有着广泛的应用。

5509A没有自带的片上非易失性存储器,因此需要外部的非易失性存储介质,如EPROM或Flash,来存储程序和数据。

5509A片内有256K字节的RAM。

由于在片内RAM运行程序比片外运行有高速度低功耗等显著优点,通常上电后都需要从片外EPROM或Flash上加载程序到片内RAM,但是芯片自带的自举程序(简称Bootloader)只支持16K字节以内的外部程序加载,因此程序设计往往局限于16K字节空间内,限制了编程的灵活性,不能充分发挥性能,当程序空间大于16K字节时,就需要自己编写程序来实现自举。

下面首先介绍使用5509A对Am29LV800B Flash(简称Flash)存储器进行程序分页烧写的方法,然后介绍利用Bootloader来编程实现多页并行自举引导的方法。

一、分页烧写的实现1、Am29LV800B Flash的连接Flash与5509A的接口很方便,前者只需作为后者的外部数据存储器与其进行连接,而中间的逻辑电路采用CPLD实现即可。

Flash内部可以产生高电压进行编程和擦除操作;只需向其命令存储器写入标准的微处理器指令,具体编程、擦除操作由内部嵌入的算法实现。

文中采用1Mbytes Flash映射为5509A的片外数据存储空间,地址为:0x200000~0x280000,数据总线16位,用于16位方式的并行引导装载。

1MBytes的Flash被分为64页进行访问(表1)。

本文通过向0x20600地址写数据来改变A18——A13的值,从而控制Flash的换页引脚对各个分页进行访问。

地址线扇区扇区大小(KBytes) 页码A18 A17 A16A15A14A13SA0 0-3 0 0 0 0 X X 64 SA1 4-7 0 0 0 1 X X 64 SA2 8-11 0 0 1 0 X X 64 SA3 12-15 0 0 1 1 X X 64 SA4 16-19 0 1 0 0 X X 64 SA5 20-23 0 1 0 1 X X 64 SA6 24-27 0 1 1 0 X X 64 SA7 28-31 0 1 1 1 X X 64 SA8 32-35 1 0 0 0 X X 64 SA9 36-39 1 0 0 1 X X 64SA10 40-43 1 0 1 0 X X 64SA11 44-47 1 0 1 1 X X 64SA12 48-51 1 1 0 0 X X 64SA13 52-55 1 1 0 1 X X 64SA14 56-59 1 1 1 0 X X 64SA15 60-61 1 1 1 1 0 X 32SA16 62 1 1 1 1 1 0 8SA17 62 1 1 1 1 1 0 8SA18 63 1 1 1 1 1 1 16表1 页地址分配2、Am29LV800BFlash的操作命令字及其C语言程序对Flash的读取可以直接进行。

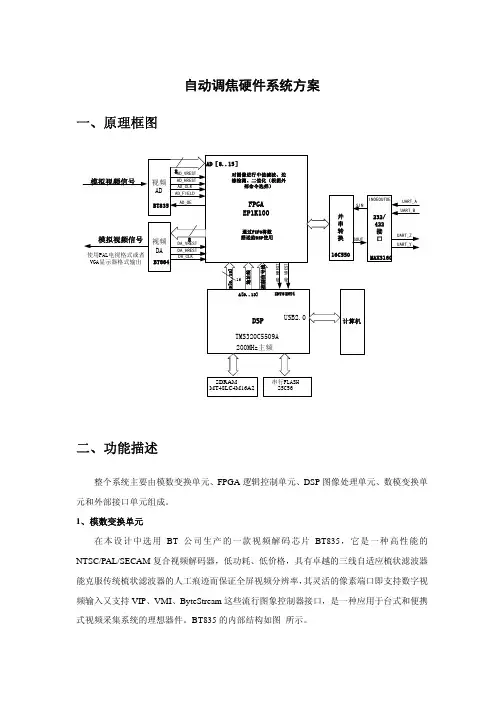

自动调焦硬件系统方案一、原理框图二、功能描述整个系统主要由模数变换单元、FPGA逻辑控制单元、DSP图像处理单元、数模变换单元和外部接口单元组成。

1、模数变换单元在本设计中选用BT公司生产的一款视频解码芯片BT835,它是一种高性能的NTSC/PAL/SECAM复合视频解码器,低功耗、低价格,具有卓越的三线自适应梳状滤波器能克服传统梳状滤波器的人工痕迹而保证全屏视频分辨率,其灵活的像素端口即支持数字视频输入又支持VIP、VMI、ByteStream这些流行图象控制器接口,是一种应用于台式和便携式视频采集系统的理想器件。

BT835的内部结构如图所示。

图 1 BT835芯片结构图BT835是基于行锁定的时钟解码原理,具有以下性能:四路模拟信号输入端(4路复合视频或3路复合视频加1路S-VIDEO),可以输入NTSC/PAL/SECAM制的视频信号。

片上的Ultralock。

平方像素和ITU-601的分辨率。

具有3-LINE的自适应梳状滤波器。

任意的水平和垂直缩放。

硬件CC解码。

垂直的消隐间隔 (VBI) 数据传输。

晶振可适合任何的视频制式。

可编程的色调,亮度 , 饱和度和对比度。

提供数字视频输入口,并且有八位可编程GPIO口。

8位或16位像素口(YcrCb 4:2:2格式输出)。

自动识别 NTSC/PAL 制式,自动增益控制(AGC)。

典型功耗500mw(3.3v),具有JTAG接口。

BT835的视频信号源可来自摄像机、VCR、照相机等的复合视频信号或Y/C信号,这里讨论的输入是复合视频信号。

首先进入BT835的复合视频信号在8*Fsc(副载频)的采样频率下通过ADC将其数字化,然后抽取、滤波到4* Fsc的采样视频流,通过自适应的3线梳状滤波器进行亮色分离,分离的亮度信号和色度信号分别进入亮度通道和色度通道,在亮度陷波及色度解调后形成Y、Cr、Cb信号以4:2:2采样格式按8位或16位从VD[15…0]输出口输出。

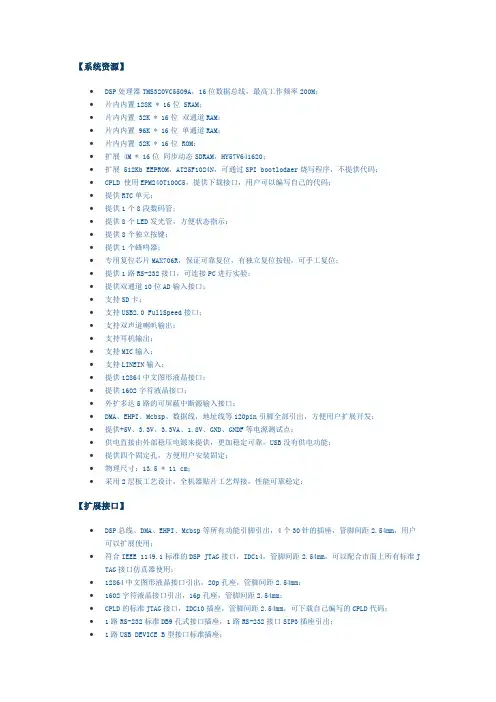

【系统资源】∙DSP处理器TMS320VC5509A,16位数据总线,最高工作频率200M;∙片内内置128K * 16位 SRAM;∙片内内置 32K * 16位双通道RAM;∙片内内置 96K * 16位单通道RAM;∙片内内置 32K * 16位 ROM;∙扩展 4M * 16位同步动态SDRAM,HY57V641620;∙扩展 512Kb EEPROM,AT25F1024N,可通过SPI bootlodaer烧写程序,不提供代码;∙CPLD 使用EPM240T100C5,提供下载接口,用户可以编写自己的代码;∙提供RTC单元;∙提供1个8段数码管;∙提供8个LED发光管,方便状态指示;∙提供8个独立按键;∙提供1个蜂鸣器;∙专用复位芯片MAX706R,保证可靠复位,有独立复位按钮,可手工复位;∙提供1路RS-232接口,可连接PC进行实验;∙提供双通道10位AD输入接口;∙支持SD卡;∙支持USB2.0 FullSpeed接口;∙支持双声道喇叭输出;∙支持耳机输出;∙支持MIC输入;∙支持LINEIN输入;∙提供12864中文图形液晶接口;∙提供1602字符液晶接口;∙外扩多达5路的可屏蔽中断源输入接口;∙DMA、EHPI、Mcbsp、数据线,地址线等120pin引脚全部引出,方便用户扩展开发;∙提供+5V、3.3V、3.3VA、1.8V、GND、GNDF等电源测试点;∙供电直接由外部稳压电源来提供,更加稳定可靠,USB没有供电功能;∙提供四个固定孔,方便用户安装固定;∙物理尺寸:13.5 * 11 cm;∙采用2层板工艺设计,全机器贴片工艺焊接,性能可靠稳定;【扩展接口】∙DSP总线、DMA、EHPI、Mcbsp等所有功能引脚引出,4个30针的插座,管脚间距2.54mm,用户可以扩展使用;∙符合IEEE 1149.1标准的DSP JTAG接口,IDC14,管脚间距2.54mm,可以配合市面上所有标准J TAG接口仿真器使用;∙12864中文图形液晶接口引出,20p孔座,管脚间距2.54mm;∙1602字符液晶接口引出,16p孔座,管脚间距2.54mm;∙CPLD的标准JTAG接口,IDC10插座,管脚间距2.54mm,可下载自己编写的CPLD代码;∙1路RS-232标准DB9孔式接口插座,1路RS-232接口SIP3插座引出;∙1路USB DEVICE B型接口标准插座;∙1路音频喇叭T输出接口;∙1路音频耳机输出接口;∙1路MIC输入接口;∙1路LINEIN输入接口;∙DC 5V外部电源输入接口;【功能图简介】【代码及实验项目】以下程序基于CCS3.3实现,CPLD代码为VHDL语言,基于QuartusII 6.0。

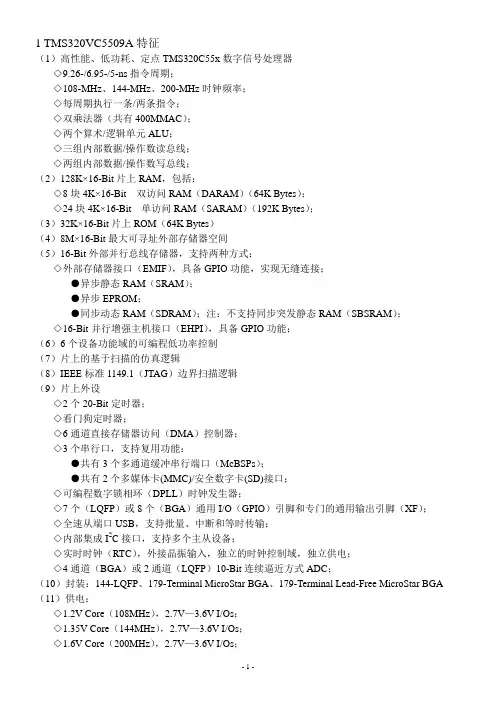

1 TMS320VC5509A特征(1)高性能、低功耗、定点TMS320C55x数字信号处理器◇9.26-/6.95-/5-ns指令周期;◇108-MHz、144-MHz、200-MHz时钟频率;◇每周期执行一条/两条指令;◇双乘法器(共有400MMAC);◇两个算术/逻辑单元ALU;◇三组内部数据/操作数读总线;◇两组内部数据/操作数写总线;(2)128K×16-Bit片上RAM,包括:◇8块4K×16-Bit 双访问RAM(DARAM)(64K Bytes);◇24块4K×16-Bit 单访问RAM(SARAM)(192K Bytes);(3)32K×16-Bit片上ROM(64K Bytes)(4)8M×16-Bit最大可寻址外部存储器空间(5)16-Bit外部并行总线存储器,支持两种方式:◇外部存储器接口(EMIF),具备GPIO功能,实现无缝连接;●异步静态RAM(SRAM);●异步EPROM;●同步动态RAM(SDRAM);注:不支持同步突发静态RAM(SBSRAM);◇16-Bit并行增强主机接口(EHPI),具备GPIO功能;(6)6个设备功能域的可编程低功率控制(7)片上的基于扫描的仿真逻辑(8)IEEE标准1149.1(JTAG)边界扫描逻辑(9)片上外设◇2个20-Bit定时器;◇看门狗定时器;◇6通道直接存储器访问(DMA)控制器;◇3个串行口,支持复用功能:●共有3个多通道缓冲串行端口(McBSPs);●共有2个多媒体卡(MMC)/安全数字卡(SD)接口;◇可编程数字锁相环(DPLL)时钟发生器;◇7个(LQFP)或8个(BGA)通用I/O(GPIO)引脚和专门的通用输出引脚(XF);◇全速从端口USB,支持批量、中断和等时传输;◇内部集成I2C接口,支持多个主从设备;◇实时时钟(RTC),外接晶振输入,独立的时钟控制域,独立供电;◇4通道(BGA)或2通道(LQFP)10-Bit连续逼近方式ADC;(10)封装:144-LQFP、179-Terminal MicroStar BGA、179-Terminal Lead-Free MicroStar BGA (11)供电:◇1.2V Core(108MHz),2.7V—3.6V I/Os;◇1.35V Core(144MHz),2.7V—3.6V I/Os;◇1.6V Core(200MHz),2.7V—3.6V I/Os;2 TMS320VC5509A存储器5509A支持一个统一的存储器映射(程序和数据存放在同一个物理空间)。

基于TMS320VC5509A的多路同步数据采集与存储系统黄霞;鲍慧;赵伟;田新成

【期刊名称】《电力系统保护与控制》

【年(卷),期】2007(035)023

【摘要】TMS320VC5509A是TI推出的新一代高性能、低功耗数字信号处理芯片,并扩充了当今流行的USB设备接口模块.系统以TMS320VC5509A为核心处理器,CPLD为系统控制译码芯片提出了一种多路A/D数据采集与存储系统的设计方案.充分利用TMS320VC5509A内置的USB接口,构成一个数字采集处理和USB 传输系统.简要介绍了系统的部分硬件和软件的设计,并分析了TMS320VC5509A USB接口模块的结构,给出了USB设备固件的设计和实现方案.

【总页数】4页(P24-27)

【作者】黄霞;鲍慧;赵伟;田新成

【作者单位】华北电力大学电子与通信工程系,河北,保定,071003;华北电力大学电子与通信工程系,河北,保定,071003;华北电力大学电子与通信工程系,河北,保定,071003;华北电力大学电子与通信工程系,河北,保定,071003

【正文语种】中文

【中图分类】TM76

【相关文献】

1.基于NiosⅡ的多路高速数据采集存储系统的实现 [J], 祝宇;王连明;艾淑平

2.基于FPGA的水下多路数据采集存储系统 [J], 喻鹏;肖大为;姬庆

3.基于FPGA及AD9223的多路数据采集、存储系统 [J], 刘鑫;任勇峰;甄国涌;张文栋

4.基于双备份多路数据采集存储系统的设计与实践 [J], 郭小兵;李圣昆;任勇峰;董小娜

5.基于ADS8365的多路数据采集存储系统设计 [J], 丁海飞;王红亮;张会新;洪应平;李健楠

因版权原因,仅展示原文概要,查看原文内容请购买。

简述tms320c5509a的结构组成TMS320C5509A是德州仪器公司(Texas Instruments)推出的一款数字信号处理器(DSP)。

它是C55x系列中的一员,具有高性能、低成本和低功耗的特点。

TMS320C5509A主要用于音频处理、语音识别、图像处理、通信等领域。

TMS320C5509A的结构组成主要包括核心、存储器、外设和系统总线。

TMS320C5509A的核心是由一个定点乘法器、一个累加器和一个数据存储器组成的。

它采用了德州仪器公司独有的定点DSP技术,能够实现高速浮点运算和高精度定点运算,从而满足复杂的信号处理需求。

TMS320C5509A配备了丰富的存储器,包括程序存储器(ROM)和数据存储器(RAM)。

ROM用于存储DSP的程序代码,RAM用于存储数据和临时变量。

通过合理地分配存储器空间,可以充分利用TMS320C5509A的计算能力和存储能力。

第三,TMS320C5509A还集成了多种外设,如通用串行总线(USB)、通用异步收发器(UART)、多通道音频接口(McASP)等。

这些外设可以与其他设备进行数据交换和通信,实现与外部世界的连接和互动。

TMS320C5509A的系统总线起到连接各个部件的作用,包括数据总线、地址总线和控制总线。

通过系统总线,各个部件可以高效地进行数据传输和控制信号的交换,从而实现协同工作。

总结起来,TMS320C5509A的结构组成主要包括核心、存储器、外设和系统总线。

核心是实现信号处理功能的关键部分,存储器提供了丰富的数据存储空间,外设实现了与外部设备的连接和通信,系统总线起到连接各个部件的桥梁作用。

TMS320C5509A在各种领域的应用中,可以快速、高效地处理信号,满足不同应用场景下的需求。

5509A开发板存储空间和存储器映射

TMS320VC5509A数字信号处理芯片具有一个比较复杂的存储空间分配体系。

因此,在使用之前,首先需要了解一下TMS320VC5509的存储空间体系。

关于TMS320VC5509的存储空间的详细说明,请参考TMS320VC5509 Datasheet 和TMS320VC5509 DSP External Memory Interface(EMIF)(编号为SPRU670)用户手册。

1. 存储空间组织

TMS320VC5509A 芯片的存储空间组织如下图所示:

明伟TMS320VC5509A开发板外扩一片16位的SDRAM,用/CE0选通,容

量为4M X 16位,寻址占用/CE0和/CE1两个存储空间。

最大可配置为8M*16

位,占用CE0—CE3全部四个片外存储空间。

片选CE0---CE3引至总线扩展器上,供用户自行连接设备。

其中,CE1和

CE2接至CPLD使用,用户使用时请详细阅读以下内容,以免造成冲突。

2. 寄存器组映射

TMS320VC5509A 开发板共有6个扩展寄存器组,用于与板上外设如按键、

网络芯片等通信,进行控制或读写信息。

这些寄存器组通过CPLD扩展,分别是:z功能选择寄存器组

z按键寄存器组

z Flash地址扩展寄存器组

z网络控制寄存器组

z LCD控制寄存器组

z LCD数据寄存器组

2.1 寄存器组定义

1)功能选择寄存器组(W,只写)

功能选择寄存器组用于选择与切换对其它寄存器组的控制功能,其各位含义

如下:

D5 D4 D3 D2 D1 D0 D15-D6

ALCDC

ALCDD ANET AFLASH AKEY X LCDDIR

X:无影响,可取任意值

LCDDIR:控制LCD的数据输入/输出方向,0为写LCD,1为读LCD

ALCDC:控制LCD控制寄存器组的使能,0为使能,1为禁用

ALCDD:控制LCD数据寄存器组的使能,0为使能,1为禁用

ANET:控制8019网络芯片控制寄存器组的使能,0为使能,1为禁用

AFLASH:控制Flash地址扩展寄存器组的使能,0为使能,1为禁用

AKEY:控制按键寄存器组的使能,0为使能,1为禁用

2)按键寄存器组(R,只读)

按键寄存器组用于读取按键K1-K4的状态,其各位含义如下:

D15-D4 D3 D2 D1 D0 X K4 K3 K2 K1 X:无影响,可取任意值

K4:读取K4的状态值,按下为0,未按下为1

K3:读取K3的状态值,按下为0,未按下为1

K2:读取K2的状态值,按下为0,未按下为1

K1:读取K1的状态值,按下为0,未按下为1

3)Flash地址扩展寄存器组(W,只写)

Flash地址扩展寄存器组用于写AM29LV800的A13-A18,其各位含义如下:

D15-D8 D7 D6 D5 D4 D3 D2 D1 D0 X FCE FRST FA18 FA17 FA16 FA15 FA14 FA13

X:无影响,可取任意值

FCE: AM29LV800片选信号,0为选中(使能),1为禁用

FRST:复位AM29LV800,0为复位

FA18-FA13:AM29LV800的18-13位地址线

4)网络控制寄存器组(W,只写)

网络控制寄存器组用于给出网络芯片RTL8019的控制信号,其各位含义如

下:

D15-D2 D1 D0

8019RST X 8019CS

X:无影响,可取任意值

8019CS: 8019片选信号,0为选中(使能),1为禁用

8019RST:8019复位信号,1位复位

5)LCD控制寄存器组(W,只写)

LCD控制寄存器组用于给出LCD的接口控制信号,其各位含义如下:

D15-D4 D3 D2 D1 D0

LCDRS

LCDRST

LCDRW

X LCDEN

X:无影响,可取任意值

LCDEN:LCD读写控制,详见《C系列中文液晶显示模块使用说明书》

LCDRW:LCD读写控制,1为读,0为写

LCDRS:LCD指令/数据接口复用控制,1为数据读写,0为指令读写

LCDRST:LCD复位信号,0为复位

6)LCD数据寄存器组(R/W,读写)

LCD控制寄存器组用于读写LCD的数据,其各位含义如下:

D15-D8 D7-D0

D[7:0]

X LCD

X:无影响,可取任意值

LCD D[7:0]:LCD的8位数据线

2.2 寄存器组访问

TMS320VC5509A 开发板通过功能选择寄存器组,利用CE2、CE3存储空

间对各寄存器组进行访问操作,操作流程如下:

1)读操作

①写功能选择寄存器组(写CE2空间任意地址),使能需要操作的目标寄存

器组,对于读LCD数据,必须将LCDDIR置为1;

②读目标寄存器组(读CE2空间任意地址);

③读操作完成后,写功能选择寄存器组,禁用所有寄存器组。

2)写操作

①写功能选择寄存器组(写CE2空间任意地址),使能需要操作的目标寄存

器组;

②写目标寄存器组(写CE3空间任意地址);

③读操作完成后,写功能选择寄存器组,禁用所有寄存器组。