第3讲_ARM 存储器结构

- 格式:ppt

- 大小:1.44 MB

- 文档页数:75

ARM存储器结构ARM存储器:片内Flash、片内静态RAM、片外存储器映射就是一一对应的意思。

重映射就是重新分配这种一一对应的关系。

我们可以把存储器看成一个具有输出和输入口的黑盒子。

输入量是地址,输出的是对应地址上存储的数据。

当然这个黑盒子是由很复杂的半导体电路实现的,具体的实现的方式我们现在不管。

存储单位一般是字节。

这样,每个字节的存储单元对应一个地址,当一个合法地址从存储器的地址总线输入后,该地址对应的存储单元上存储的数据就会出现在数据总线上面。

普通的单片机把可执行代码和数据存放到存储器中。

单片机中的CPU从储器中取指令代码和数据。

其中存储器中每个物理存储单元与其地址是一一对应而且是不可变的,UGG boots。

而ARM比较复杂,ARM芯片与普通单片机在存储器地址方面的不同在于:ARM芯片中有些物理存储单元的地址可以根据设置变换。

就是说一个物理存储单元现在对应一个地址,经过设置以后,这个存储单元就对应了另外一个地址了(这就是后面要说的重新映射)。

例如将0x00000000地址上的存储单元映射到新的地址0x00000007上。

CPU存取0x00000007就是存取0x00000000上的物理存储单元。

(随便举的例子为了说明道理,没有实际意义)存储器重新映射(Memory Re-Map)存储器重新映射是将复位后用户可见的存储器中部分区域,再次映射到其他的地址上。

存储器重新映射包括两个方面:1、Boot Block重新映射(关于Boot Block的相关内容看我博客中的另一篇文章)。

2、异常(中断)向量重新映射Boot Block重新映射:本来Boot Block在片内Flash的最高8KB,但是为了与将来期间相兼容,生产商为了产品的升级换代,在新型芯片中增加内部Flash容量时,不至于因为位于Flash高端的Boot Block的地址发生了变化而改写其代码,整个Boot Block都要被重新映射到内部存储器空间的顶部,即片内RAM的最高8KB。

嵌入式系统设计导论—基于32位微处理器与实时操作系统第三讲 ARM嵌入式微处理器体系结构北京航空航天大学机器人研究所魏洪兴本节提要1ARM编程模型ARM 异常处理嵌入式处理器概述l嵌入式微处理器是嵌入式系统的核心。

目前32位嵌入式微处理器是市场的主流。

l32位嵌入式微处理器市场,我们可以发现超过100家的芯片供应商和近30种指令体系结构。

l在1996年以前,最成功的嵌入式微处理器是Motorola公司的68000系列。

此外嵌入式微处理器市场还包括其它体系结构,如Intel公司的I960,Motorola公司的Coldfire,Sun公司的Sparc,以及嵌入式X86系列平台。

l当然,最引人注目的还是ARM公司的ARM系列、MIPS公司的MIPS系列,以及Hitachi公司的SuperH系列(其中ARM和MIPS 都知识产权公司,把他们的微处理器IP技术授权给半导体厂商,由他们生产形态各异的微处理器芯片)。

l功耗。

一般的嵌入式微处理器都有三种运行模式:运行模式(operational);待机模式(standby or power down);停机模式(and clock-off)。

功耗的评测指标是MIPS/W;l代码存储密度。

传统的CISC指令集计算机具有较好的代码存储密度。

而RICS指令集计算机由于要求指令编码长度固定,虽然可以简化和加速指令译码过程,但为了实现与CISC指令集计算机相同的作业,往往需要更多的指令来完成,从而增加了代码长度。

如Hitachi的SuperH体系结构采用了定长的16位指令,对每条指令按16位的格式存储。

ARM则采用16位扩展的Thumb指令集,片内的逻辑译码器将其等价为32位的ARM指令而实时解码。

而MIPS则采用MIPS16方法来解决这个问题。

(影响代码密度的另外一个主要因素是所采用的C编译器。

ANSI C是当前嵌入式领域的标准编程语言,随着嵌入式微处理器性能的提高,面向对象的语言也将被采用并会逐渐成为主流,一些编译器供应商已经开始着手解决代码密度问题。

ARM嵌入式系统第2章ARM体系结构ARM微处理器的编程模型♦ARM徴处理器的工作状态♦ARM体系结构的存储器格式♦ARM体系结构的指令长度及数据宽度♦ARM微处理器的处理器模式♦ARM体系结构的寄存器组织♦ARM微处理器的异常状态字、半字、字节字(Word)在ARM体系结构中,字的长度为32位半字(Half-Word)在ARM体系结构中,半字的长度为16位字节(Byg)在ARM体系结构中,字节的长度为8位。

ARM微处理器的工作状态(1)字对齐:四字节对齐半字对齐:两字节对齐两种状态:♦ARM状态:处理器执行32位的字对齐的令♦Thumb状态:处理器执行16位的、半字对齐的Thumb指令处理器工作状态的转变并不影响处理器的工作模式和相应寄存器中的内容。

I ARM微处理器的工作状态(2 )状态切换:BX {<cond>} <Rm><cond>指令的条件码。

忽略时无条件执行。

<Rm>子存器中为跳转的目标地址,当<Rm><存器的bit[O]为0时, 目标地址处的指令为ARM指令;当<Rm>^存器的bit[O]为1时,目标地址处的指令为Thumb 指令。

伪代码:if ConditionPassed(cond) thenT Flag=Rm[O]PC=Rm AND OxFFFFFFFEARM微处理器在复位或上电时处于ARM状态,发生异常时处于ARM状态。

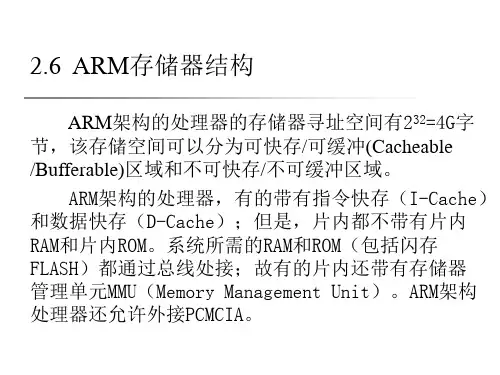

右ARM体系结构的存储器格式(1)ARM体系结构所支持的最大寻址空间为4GB (2^字节)♦大端格式(Big Endian)字数据的高字节存储在低地址中,而字数据的低字节则存放在高地址中。

♦小端格式(Little Endian)低地址中存放的是字数据的低字节,高地址存放的是字数据的高字节。

字地址字地址右ARM 体系结构的存储器格式(2)(0H)=0123H (4H)=4567H (8H)=89ABHBig Endian(0H)=3210H (4H)=7654H (8H)=BA98HLittle Endian右ARM 体系结构的存储器格式(3)8 9 AB4 5 6 7 0123一 “A ・■ • rO= 0x11223344 I 11 I 22 33 : 44 ILittle endian Big endianR2 =异FI*右 ARM 体系结构的指令长度及数据宽度♦指令长度:32位(在ARM 状态下) 16位(在Thumb 状态下)♦数据宽度: 字节(8位) 半字(16位) 字(32位)三种数据宽度对存储器及外部设备的访问。

一、ARM7的体系结构(一)每种单片机的区别在于内核前段时间学习的以51为核的单片机,现在正在学习ARM9,实际上是以ARM处理器为核的单片机,51为核的单片机就是把中央处理器,存储器,输入输出设备集成在一个芯片内的芯片,ARM处理器为核的单片机就是把ARM处理器,存储器,输入输出设备集成在一个芯片内的芯片。

对于ARM处理器来说,对外围的操作都是对外围设备的寄存器的操作,也就是对地址的操作。

(外围设备如串口,定时器等等,他们也有相应的寄存器)。

但是ARM处理器里面有37个32位寄存器,31个通用寄存器,6个状态寄存器,这些寄存器都是不能同时被访问的,具体那些寄存器是可编程访问的,取决于微处理器的工作状态和运行模式。

但在任何时候,通用寄存器R0--R14、程序计数器PC、一个或两个状态寄存器都是可以访问的。

ARM处理器都是一样的,只是生产厂家不同而有了像S3C2440这样的单片机等等,实际上这些都是在以ARM处理器外增加了许多外围而形成了单片机,然后在加些外围成了开发板。

(二)ARM处理器的存储结构1.有两种存储方式,大端和小端2.在使用一个单片机之前一定要搞清楚此单片机的存储格式3.每个存储单元为一个字节,且都有一个地址,对于32位机来说,数据或代码有32位的,那么一个数据就需要四个单元来存,就涉及到顺序问题,也就是大端方式存和小端方式。

4.对字,半字,字节操作(如图)5.与51核单片机不同,ARM处理器的指令代码字节数是相同的,在Tumb指令集中,所有的指令代码都是16位2字节代码,在ARM指令集中,所有的指令代码都是32位4字节代码。

6.ARM处理器有多种模式,而51只有一种模式,可以访问全部资源。

(三)ARM处理器内部寄存器1.为了使用方便,常常赋予寄存器专用的助记符,也就是寄存器的名称,如下图:2.关于寄存器R13、R14、R15R13作为堆栈指针,和51系列单片机中的SP一样。

如果程序发生异常中断时,中断服务程序要把保护的寄存器值堆栈到R13指向的堆栈入口,在退出中断服务时,再把堆栈中的数据弹出来。

简述arm微处理器的存储器组织方式-回复ARM微处理器的存储器组织方式【引言】随着计算机技术的迅猛发展,微处理器成为现代计算机的核心部件之一。

而ARM(Advanced RISC Machine)微处理器则是一种广泛应用于各种移动设备和嵌入式系统的微处理器架构。

存储器是微处理器中至关重要的组成部分,它承担着存储和取回程序和数据的任务。

在本文中,我们将简要介绍ARM微处理器的存储器组织方式。

【1. 存储器类型】ARM微处理器采用的存储器组织方式分为多个级别,每个级别都有其特定的功能和特点。

ARM微处理器主要包括下列几种存储器类型:- 寄存器:寄存器是位于CPU内部的高速存储器,用于存储和操作数据。

ARM微处理器通常拥有多个通用寄存器,特定目的寄存器和状态寄存器,用于不同的数据操作和系统控制。

- 高速缓存:高速缓存是位于CPU核心和主存之间的中间存储器,用于加速主存的数据读取和写入。

ARM微处理器通常包括多级高速缓存,如一级指令缓存和数据缓存、二级缓存等,其容量和速度逐级递减。

- 主存储器:主存储器是微处理器中最大容量的存储器,用于存储程序和数据。

ARM微处理器支持多种主存类型,如静态RAM(SRAM)、动态RAM(DRAM)等,其容量可以从几兆字节到几个千兆字节不等。

【2. 存储器层次结构】ARM微处理器的存储器组织方式采用存储器层次结构,以便提高存储器的访问效率和性能。

存储器层次结构由多级存储器组成,每级存储器的容量和速度都不同,分别用于存储不同级别的数据。

ARM微处理器的存储器层次结构通常包括以下几个层次:- 第一级缓存(L1 Cache):一级缓存是位于CPU核心和主存之间的最接近CPU的高速缓存。

它通常分为一级指令缓存(L1 I-Cache)和一级数据缓存(L1 D-Cache),分别用于存储指令和数据。

一级缓存的容量较小,但速度非常快,可以迅速地响应CPU的读写请求。

- 第二级缓存(L2 Cache):二级缓存是位于一级缓存和主存之间的中间缓存,其容量比一级缓存大,速度相对较慢。