计组实验二

- 格式:doc

- 大小:93.07 KB

- 文档页数:8

编码16位模式32位模式操作)000AX EAX AL001CX ECX CL010DX EDX DL011BX EBX BL100SP ESP AH101BP EBP CH110SI ESI DH111DI EDI BHR/M字段受MOD字段控制。

若MOD=11,为寄存器方式,R/M字段将指出第二操作数所在寄存器编号。

MOD=00,01,10为存储器方式,R/M则指出如何计算存储器中操作数地址。

MOD与R/M字段组合的寻址方式见表3。

表3 各种MOD与R/M字段组合编码及有关地址的计算(16位地址模式下)MOD=11寄存器寻址MOD≠11存储寻址、有效地址的计算公式R/M W=1W=0R/M不带位移l量MOD=00带8位位移量MOD=01带16位位移量MOD=10 000AX AL000[BX+SI][BX+SI+D8][BX+SI+D16]001CX CL001[BX+DI][BX+DI+D8][BX+SI+D16]010DX DL010[BP+SI][BP+SI+D8][BP+SI+D16]011BX BL011[BP+DI][BP+DI+D8][BP+DI+D16]100SP AH100[SI][SI+D8][SI+D16]101BP CH101[DI][DI+D8][DI+D16]110SI DH110(直接寻址)[BP+D8][BP+D16]111DI BH111[BX][BX+D8][BX+D16]例如:指令MOV AH,[BX+DI+50H]。

代码格式如下。

OPCODE D W MOD REG R/M DISP—8100010 1 0 01 100 001 01010000指令码:8A6150H。

指令ADD DISP [BX] [DI],DX;DISP=4523H代码格式:OPCODE D W MOD REG R/M DISP—Lo DISP—Hi000000 0 1 10 010 001 00100011 01000101指令码为:01 91 23 45H。

实验2 运算器的编程实现一、实验目的1、加深对计算机中运算器的基本概念、运算方法和基本原理的理解。

2、提高学生对计算机编程语言掌握的熟练程度。

二、实验内容运用一种编程语言实现计算器的基本功能。

思考:1、计算机中数据是如何表示的?2、计算机中二进制数的加、减、乘、除四则运算如何实现?3、运算器的基本结构和功能有哪些?三、实验结果分析1、计算机中数据是如何表示的?计算机的数据表示方法是二进制。

2、计算机中二进制的加减乘除四则运算是如何实现的?各种数据在计算机中表示的形式称为机器数。

机器数有无符号和带符号之分,为了便于运算,带符号的机器数可以采用源码、反码和补码的等不同的编码方法,这叫码制最高位最示符号位:0表示正号,1表示负号,正数的补码和反码是相同的。

反码=原码取反补码=反码+1二进制的运算法则1)二进制加法的进位法则是“逢二进一”。

0+0=0 1+0=1 0+1=1 1+1=0(进位)2)二进制减法的进位法则是“借一为二”。

0–0=0 1–0=1 1–1=0 0–1=1(借位)3)二进制乘法规则。

0*0=0 1*0=0 0*1=0 1*1=14)二进制除法即是乘法的逆运算,类似十进制除法。

加法 0+0=0,0+1=1+0=1,1+1=10减法 0-0=0,1-0=1,1-1=0,0-1=-1,10100-1010=1010 乘法0×0=0,0×1=1×0=0,1×1=1除法0÷1=0,1÷1=1只有0和1两个数码,基数为二。

加法运算步骤:(1)首先是最右数码位相加。

这里加数和被加数的最后一位分别为“0”和“1”,根据加法原则可以知道,相加后为“1”。

(2)再进行倒数第二位相加。

这里加数和被加数的倒数第二位都为“1”,根据加法原则可以知道,相加后为“(10)2”,此时把后面的“0”留下,而把第一位的“1”向高一位进“1”。

(3)再进行倒数第三位相加。

计算机组成原理实验报告实验一寄存器组成实验一、实验目的(1)熟悉D触发器的功能及使用方法。

(2)掌握寄存器文件的逻辑组成及使用方法。

二、实验内容(1)掌握Quartus II的使用方法,能够进行数字电路的设计及仿真。

(2)验证Quartus II所提供D触发器的功能及使用方法。

(3)设计具有1个读端口、1个写端口的寄存器文件,并进行存取操作仿真/验证。

三、实验原理及方案Quartus II提供了多种类型的触发器模块,如D触发器、T触发器等。

固定特性的触发器模块有不同的型号,参数化的触发器模块有lpm_ff、lpm_dff、lpm_tff等。

D触发器常来构建寄存器。

本次实验我们用Quartus II中提供的8为D触发器模块,实现了一个8×8bits 的寄存器组,因此,操作地址均为3位,数据均为8位。

由于要求读写端口分离,因此,读操作的相关引脚有地址raddr[2..0]、数据输出q[7..0],写操作的相关引脚有地址waddr[2..0]、数据输入data[7..0]、写使能wen。

其中,省略读使能信号可以简化控制,即数据输出不受限制。

寄存器文件通过写地址waddr[2..0]、写使能wen信号来实现触发器的写入控制,通过读地址raddr[2..0]信号来控制触发器的数据输出选择。

其连接电路原理如图所示。

寄存器文件的组成则由此,可在Quartus II中连接原理图:四、实验结果仿真波形如下:五、小结通过此次实验,我们学会了Quartus II的原理图的构造方法,以及仿真方法,并且使用lpm_dff作为三态门,控制数据的输入,并且在输出时,用lpm_mux选择每个寄存器的数据输出。

最后,在本次实验中,我们重新巩固了课堂学习的内容,也对寄存器加深了了解,相信我们会通过实验在计组的学习道路上越走越远。

实验二运算器组成实验一、实验目的(1)熟悉加/减法器的功能及使用方法。

(2)掌握算术逻辑部件(ALU)的功能及其逻辑组成。

软112,网112-运算器112485冯朝阳-112479李芸-SHL-80H-SUB-80H-04H运算器实验报告一、实验目的:1、熟悉74LS181函数功能发生器,提高应用器件在系统中应用的能力。

2、熟悉运算器的数据传送通路。

3、完成几种算术逻辑运算操作,加深对运算器工作原理的理解。

二、实验内容:(一)实验设计和连线步骤;运算器是计算机对数据进行运算的重要部件,它的核心是AlU函数功能发生器,其次还要有存放操作数和运算中间结果的寄存器、移位门、传送数据的总线等部件,在不同的控制信号下,运算器完成不同的运算功能。

SA、SB为存放两个现行操作数的缓冲寄存器。

其中SA兼作存放中间结果的累加器,并给予显示。

它们仅接收来自总线的数据信息,送入ALU进行算逻运算。

ALU输出经移位门,将运算结果送入母线。

移位门挂母线是发送源,需用三态门作隔离器。

可采用74LS244兼作移位门和隔离器。

在计算机运算过程中,经常要根据运算结果和进位输出来决定程序的流程,可从ALU 的A=B和C n+4端输出判断信息,分别打入进位位C和结果Z触发器。

当n位数运算结果超出n位所能表示的数的范围时,即发生了溢出。

在八位补码形式运算中,数的表示在-128~127范围内,溢出V同操作数的符号位及运算结果的符号位输出有如下关系:(1)加操作时,两操作数符号位(第七位)相同,才会产生溢出,即:(2)减操作时,两操作数符号位相异,才会产生溢出,即:所以V=V㈩ + V㈠。

实验中,为减少拟开关占用量,可在总线上挂一个指令寄存器,存放ALU的控制信息S3~S0,M、Cn。

ALU数据通路实验1、按图2.2运算器数据通路图设计一个能完成表2-1所列出的八种补码运算指令的运算器。

表2-1 运算器的8种指令功能表2、完成元件选择,依据详细实验电路逻辑图,进行连线组装成电路。

3、在电路上进行表2-1八种指令的操作(操作数、指令码由数据开关输入),观察运算器数据通路上显示灯的运行结果。

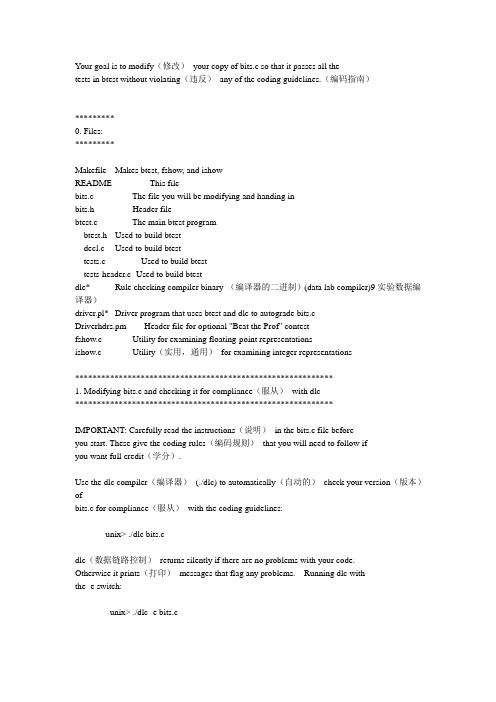

Your goal is to modify(修改)your copy of bits.c so that it passes all thetests in btest without violating(违反)any of the coding guidelines.(编码指南)*********0. Files:*********Makefile - Makes btest, fshow, and ishowREADME - This filebits.c - The file you will be modifying and handing inbits.h - Header filebtest.c - The main btest programbtest.h - Used to build btestdecl.c - Used to build btesttests.c - Used to build btesttests-header.c- Used to build btestdlc* - Rule checking compiler binary (编译器的二进制)(data lab compiler)9实验数据编译器)driver.pl* - Driver program that uses btest and dlc to autograde bits.cDriverhdrs.pm - Header file for optional "Beat the Prof" contestfshow.c - Utility for examining floating-point representationsishow.c - Utility(实用,通用)for examining integer representations***********************************************************1. Modifying bits.c and checking it for compliance(服从)with dlc***********************************************************IMPORTANT: Carefully read the instructions(说明)in the bits.c file beforeyou start. These give the coding rules(编码规则)that you will need to follow ifyou want full credit(学分).Use the dlc compiler(编译器)(./dlc) to automatically(自动的)check your version(版本)ofbits.c for compliance(服从)with the coding guidelines:unix> ./dlc bits.cdlc(数据链路控制)returns silently if there are no problems with your code.Otherwise it prints(打印)messages that flag any problems. Running dlc withthe -e switch:unix> ./dlc -e bits.ccauses dlc to print counts of the number of operators(运算符)used by each function.Once you have a legal solution, you can test it for correctness usingthe ./btest program.*********************2. Testing with btest*********************The Makefile in this directory compiles your version of bits.c withadditional code(辅助码,补码)to create a program (or test harness) named btest.To compile and run the btest program, type:unix> make btestunix> ./btest [optional cmd line args]You will need to recompile(重新编译)btest each time you change your bits.cprogram. When moving from one platform(平台)to another, you will want toget rid of the old version of btest and generate a new one. Use thecommands:unix> make cleanunix> make btestBtest tests your code for correctness by running millions of testcases on each function. It tests wide swaths around well known cornercases such as Tmin and zero for integer puzzles, and zero, inf(无穷大), andthe boundary(边界)between denormalized(非规划的)and normalized numbers for floating point puzzles. When btest detects(发现)an error in one of your functions,it prints out the test that failed, the incorrect result, and theexpected result, and then terminates the testing for that function.Here are the command line options for btest:unix> ./btest -hUsage: ./btest [-hg] [-r <n>] [-f <name> [-1|-2|-3 <val>]*] [-T <time limit>]-1 <val> Specify first function argument-2 <val> Specify second function argument-3 <val> Specify third function argument-f <name> Test only the named function-g Format output for autograding with no error messages-h Print this message-r <n> Give uniform weight of n for all problems-T <lim> Set timeout limit to limExamples:Test all functions for correctness and print out error messages:unix> ./btestTest all functions in a compact form with no error messages:unix> ./btest -gTest function foo for correctness:unix> ./btest -f fooTest function foo for correctness with specific arguments:unix> ./btest -f foo -1 27 -2 0xfBtest does not check your code for compliance with the codingguidelines. Use dlc to do that.*******************3. Helper Programs*******************We have included the ishow and fshow programs to help you decipherinteger and floating point representations respectively. Each takes asingle decimal or hex number as an argument. To build them type:unix> makeExample usages:unix> ./ishow 0x27Hex = 0x00000027, S igned = 39, Unsigned = 39unix> ./ishow 27Hex = 0x0000001b, S igned = 27, Unsigned = 27unix> ./fshow 0x15213243Floating point value 3.255334057e-26Bit Representation 0x15213243, sign = 0, exponent = 0x2a, fraction = 0x213243 Normalized. +1.2593463659 X 2^(-85)linux> ./fshow 15213243Floating point value 2.131829405e-38Bit Representation 0x00e822bb, sign = 0, exponent = 0x01, fraction = 0x6822bb Normalized. +1.8135598898 X 2^(-126)。

杭州电子科技大学计算机学院

实验报告

实验项目:实验2-超前进位加法器设计实验

课程名称:计算机组成原理与系统结构课程设计

姓名:学号:同组姓名:学号:

实验位置(机号):

实验日期:指导教师:

二、结果

思考题:

(1)综合得到的电路图,它和想要设计的电路在引脚的输入输出方面是完全相同的,但是相比较内部的RTL图,实验实现的结果是相同的,但是我编写的实验代码并没有调用实验一的全加器设计。

(2)尝试编写8位超前进位加法器设计实验

module add_8 ( input [7:0]a, input [7:0]b, input cin, output [7:0] s, output co );

wire [7:0]c_tmp;

wire [7:0]g;

wire [7:0]p;。

广州大学学生实验报告开课学院及实验室:室 2013年 5月11日学院计算机科学与教育软件学院年级、专业、班姓名学号实验课程名称计算机组成与系统结构实验成绩实验项目名称存储器和总线传输实验指导老师2.3.3准双向I/O口实验一、实验目的熟悉与了解准双向I/O口的构成原理。

二、实验原理Dais-CMX16+向用户提供的是按准双向原理设计的十六位输入/输出I/O口,当该位为“1”时才能用作输入源,上电或复位(手动态按【返回】键),该十六位I/O口被置位(即为“0FFFFh”)。

通常情况下,在用作输入的时候就不能再有输出定义。

电路结构如图2-3-4所示。

该口外接十六位二进制数据开关,适用于外部数据的输入,该口跨接十六个发光二极管,经缓冲驱动四个七段显示,能以二进制和十六进制两种方式显示I/O口的输入输出状态。

发光管在高电平“1”时发光点亮。

图2-3-4 准双向I/O电路实验中所用的I/O口数据通路如图2-3-5所示。

I/O的输入经2片74LS245缓冲与数据总线相连,I/O口的输出由2片74LS574锁存后输出,锁存器的输入端与数据总线相连。

图2-3-5 I/O口数据通路三、使用仪器、器材Dais-CMX16+实验箱、导线若干四、实验步骤及数据记录1.实验连线连线信号孔接入孔作用有效电平1 IOCK CLOCK 单元手动实验状态的时钟来源下降沿打入2 W K6(M6) 总线字长:0=16位字操作,1=8位字节操作3 X2 K10(M10) 源部件定义译码端X2 三八译码八中选一低电平有效4 X1 K9(M9) 源部件定义译码端X15 X0 K8(M8) 源部件定义译码端X06 XP K7(M7) 源奇偶位:0=偶寻址,1=奇寻址7 IOW K17(M17) I/O写使能,本例定义到M17位低电平有效8 OP K16(M16) 目的奇偶位:0=偶寻址,1=奇寻址9 RXW K19(M19) 寄存器写使能,本例定义到M19位低电平有效10 DI K18(K18) 目标寄存器编址:0=CX,1=DX,定义到M182.搭接方式I/O的寻址定义I/O口源编址I/O口目的编址源编码I/O编址注释目的I/O编址注释X2 X1 X0 W XP IOW W OP IOCK1 0 00 0 IO字读0 0 ↓IO字写10IOL偶字节读 1 0 ↓IOL偶字节写X1IOH奇字节读X 1 ↓IOH奇字节写3.I/O口写操作(输出)执行OUT I/O,AX 指令,把AX内容送I/O口。

计算机组成原理实验报告记录————————————————————————————————作者:————————————————————————————————日期:郑州航空工业管理学院计算机科学与应用系实验报告课程名:计算机组成原理学号:141096138姓名:阚丰蕊指导教师:范喆成绩;计算机科学与应用系实验一运算器实验(一)1、实验目的①深入了解AM2901运算器的功能及具体用法。

②深化运算器部件的组成、设计、控制与使用知识。

③能够熟练掌握对运算器所需控制信号的设置,并使之完成运算。

④能够独立地成功完成所给指令在运算器中的运算实验。

2、实验要求①实验前,认真了解AM2901运算器的基本结构,预习所需实验的内容,并在课前填写实验步骤表格,对于实验数据和实验结果进行预期性的分析,以提高实验效率。

②实验过程中,要按照正确的流程操作,防止损坏设备,分析可能遇到的各种现象,判断结果是否正确,并记录运算结果。

③实验之后,要认真填写实验报告,包括对对到的各种现象的分析,实验步骤和实验结果。

3、实验原理(1)运算器数据通路TEC-XP教学机的运算器主要采用4片AM2901芯片级联组成;每片AM2901芯片实现4位运算,4片芯片级联成16位的运算器。

AM2901芯片组成包括:1个4位的算术逻辑运算单元ALU、16个4位的通用寄存器、一个4位的乘商寄存器Q和若干个多路选择开关。

AM2901的数据通路如图所示:①算术逻辑运算单元ALUALU有两个数据输入端R和S。

在RS的各种组合中除去没有意思的和重复的,只有8种有效组合。

ALU可完成连个操作数的加、减、与、或、异或等多种操作。

ALU的输出结果可保存到通用寄存器、乘商寄存器Q,并且可将其值乘除2之后在保存。

ALU根据其运算的结果会产生4个标志位——符号标志位F3、零标志位F=0、溢出标志位OVR和进位标志位Cn+4。

②通用寄存器组AM2901中的通用寄存器组是由16个寄存器构成,具有双端口读写电路。

计算机组成原理实验课程实验报告实验名称运算器实验

实验二运算器

一.实验目的

了解简单运算器的数据传输通路。

验证运算功能发生器的组合功能。

掌握算术逻辑运算加、减、与的工作原理。

二.实验环境

Quartus 2 9.1

三.实验基本原理及步骤

算术逻辑单元运算器ALU181根据74LS181的功能,用VHDL硬件描述语言编辑而成,构成8位字长的ALU。

参加运算的两个8位数据分别为A[7..0]和B[7..0],运算模式由S[3..0]的16种组合决定,S[3..0]的值由4位2进制计数器LPM_COUNTER产生,计数时钟是Sclk(图2-1);此外,设M=0,选择算术运算,M=1为逻辑运算,C N为低位的进位位;

F[7..0]为输出结果,C O为运算后的输出进位位。

两个8位数据由总线IN[7..0]分别通过两个电平锁存器74373锁入,ALU功能如表所示。

四.仿真及软件设计

Vhd编程(非自己写,粘贴了群里文件):

将编程存为器件以及定制74373b,如图

bdf电路图:

五.实验结果分析及回答问题(或测试环境及测试结果)实验问题:

发现是

后来将IN[7…0]改为IN[7..0]

运行成功

仿真结果:

经检验结果正确:。

计算机科学与技术系

实验报告

专业名称计算机科学与技术

课程名称计算机组成原理

项目名称静态随机存储器实验

班级

学号

姓名

同组人员无

实验日期 2016.5.10

一、实验目的与要求

(一)实验目的:

掌握静态随机存储RAM工作特性及数据的读写方法

实验要求:

1.实验之前,应认真准备,写出实验步骤和具体设计内容,否则实验效率会很低,一次实验时间根本无法完成实验任务;

2.应在实验前掌握所以控制信号的作用,写出实验预习报告并带入实验室;

3.实验过程中,应认真进行实验操作,既不要因为粗心造成短路等事故而损坏设备,又要自习思考实验有关内容;

4.实验之后,应认真思考总结,写出实验报告,包括实验步骤和具体实验结果,遇到的问题和分析与解决思路。

还应写出自己的心得体会,也可以对教学实验提出新的建议等。

实验报告要上交老师。

二、实验逻辑原理图与分析

2.1 画实验逻辑原理图

D7 - - - - - - - - - - - - - -D0

O E C S D7- - - - - - - - - - - - - - D0

R D

A10—A8 A7- - - - - - - - - - - - -A0 WE

读写译码

74LS273 74LS245 IN单元AD7 | AD0

2.2 逻辑原理图分析

1、存储器数据线接至数据总线,数据总线上接有8个LED 灯显示D7—D0 的内容。

地址线接至地址总线,地址总线上接有8 个LED 灯显示A7—A0 的内容,地址由地址锁存器(74LS273,位于PC&AR单元)给出。

2、数据开关(位于IN单元)经一个三态门(74LS245)连至数据总线,分时给出地址和数据。

地址寄存器为8位,接入6116的地址A7—A0,6116 的高三位地址A10—A8 接地,所以其实际容量为256 字节。

3、实验箱中所有单元的时序都连接至时序控制台操作,CRL都连接至CON 按钮。

实验时T3由时序单元给出,其余信号由CON单元的二进制开关模拟给出,其中,IOM应为低,RD、WR高有效,MR、MW低有效,LDAR高有效。

三、数据通路图及分析(画出数据通路图并作出分析)

数据总线

××××××××

OE# CE# ××××××××WR#

MEM单元

A1 A8 ××××××××RD#

××××××××

AR单元

≥1

××××××××

IN单元

将地址输入寄存器:先关掉存储器的读写数据开关输入地址,然后打开地址寄存器门控信号,按动ST产生T3脉冲,将地址打入AR中。

数据总线

××××××××

OE# CE# ××××××××WR#

MEM单元

A1 A8 ××××××××RD#

××××××××

AR单元

≥1

××××××××

IN单元

将数据输入寄存器:先关掉存储器的读写,和地址寄存器门控信号,数据开关输出要写入数据,打开输入三态门,然后使存储器处于写状态,按动ST产生T3脉冲,将数据打入到存储器。

数据总线

××××××××

OE# CE# ××××××××WR#

MEM单元

A1 A8 ××××××××RD#

××××××××

AR单元

≥1

××××××××

IN单元

从存储器中读出数据:首先先关掉存储器的读写数据开关输入地址,然后打开地址寄存器门控信号,按动ST产生T3脉冲,将地址打入AR中。

告知寄存器我所要输出的数据去地址是什么。

数据总线

××××××××

OE# CE# ××××××××WR#

MEM单元

A1 A8 ××××××××RD#

××××××××

AR单元

≥1

××××××××

IN单元

从寄存器中输出数据。

四、实验数据和结果分析

4.1 实验结果数据

单元地址写入数据读出数据

00H 11H 11H

01H 12H 12H

02H 13H 13H

03H 14H 14H

04H 15H 15H

4.2 结果数据分析

首先由存储器的输入给出地址经过总线打入到地址寄存器,然后在此地址中输入数据,将其保存住,因为数据和地址由同一个开关给出,所以数据和地址需要分开填写。

将数据存入以后,想要读取内容时,需要先给出操作数的地址,再有pc的值改变找到其操作数,再控制微命令将其输出即可完成实验。

不过在读取的时候要将存储器处于读的状态,当前输入的才是地址。

五、实验问题分析、思考题与小结

(实验过程中的问题分析、产生的原因以及解决方法;思考题;总结)

问题分析:

1.在实验中出现了输入的跟输出的内容不一致。

分析:写入的时候,操作步骤出现错误。

重新输入就正确了。

思考题

1、实现IN单元的数据开关-BUS-AR的数据通路需要哪些控制信号?

答:IN单元的输出制信号(IN_B=1)、地址寄存器门控制信号(LDAR=1)。

2、实现IN单元的数据开关-BUS-RAM的数据通路需要哪些控制信号?

答:IN单元的输出制信号(IN_B=1)、地址寄存器门控制信号(LDAR=1)、存储器写入控制信号(WR=1)。

3、实现存储器读的数据通路需要哪些控制信号?

答:存储器读控制信号(RD=1)。

4、存储器写与存储器读的控制信号有何不同?

答:存储器写控制信号是将WR置为1、RD置为0,存储器读控制信号是将RD置为1,WR置为0

5、IN单元的数据开关=00000010B、IN_B=0、CE=1、LDAR=1、T3=1实现什么数据通路?

答:将IN单元的00000010打入到地址寄存器AR中

实验总结:

此外,我们可以分析得到:FC、 FZ 表示当前运算会影响到该标志,FC 为向高位的进位标志, FZ 为运算器零标志。

注:本次实验过程中,我开始没有考虑到Fc的进位,全部置为Fc=0,(因为我实现的八种功能的进位都为0;后来发现这样做是不完整的,于是我将输出的寄存器设为9位,当存在最高位有进位时,令Fc=F(8)即可解决这个问题。

实验报告分析评价

课程名称班级实验名称时间实验报告情况分析:

经验总结及进一步改进措施:。