西工大数字集成电路实验报告_实验2反相器代码

- 格式:doc

- 大小:62.00 KB

- 文档页数:6

数字集成电路实验报告西北工业大学2014年5月7日星期三实验二、反相器(上)一、分析电路,解答下面的问题。

1. 这个电路是不是反相器,为什么?该门属于有比逻辑,还是无比逻辑,为什么?答:该电路是反相器电路,因为当输入为0时,MOS 管截止,vout 连接到高电位Vdd ,当输入为Vdd 时,输出取决于MOS 管电阻与上面电阻的分压,是一个较低的电位。

该门是一个有比逻辑,因为输出与MOS 管的尺寸有关。

2. 计算出这个电路的VOH VOL 及VIH VIL 。

(计算可先排除速度饱和的可能)答:V V v V O H in 5.20=⇒=v V in 5.2=时,无法判断器件工作状态。

假设NMOS 工作在临界饱和区有:AI V R I vV V V AI V V L W K I D out L D T in out D T in D 61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据D D I I <1说明器件饱和时,同一通路上下电流大小不一致。

那么Vout 必须相应减小使同一通路的电流一致,所以器件必定进入线性区。

进一步求Vol⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L WK I in OL L D OL OL T in D 5.25.2]2)[(2` 6`10115-⨯=K 将,5.0/5.1=LW,43.0=T V 代入kohm R L 75=VVol A I 0.04638 10272.35=⨯=-(注:经过Hspice 仿真结果为0.0356V )当out in V V =时NMOS 工作在饱和区⎪⎩⎪⎨⎧+=-⨯=outL D T in D V R I V V L W K I 5.2)(2/2`可解得反相器阈值电压===out in M V V V 0.7932V此时 -9.3978V)43.0(875.25,)43.0(9375.125.22=--==--=in VinVoutin out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.6116V ||0.8776V ||g V V V V g V V V M OH MIL M M IH分析电路噪声容限。

数字电子技术基础实验报告题目:实验二组合电路实验设计小构成员:小构成员:实验二组合电路实验设计一、实验目的1.经过实验的方法学习数据选择器的电路结构和特色2.掌握数据选择器的逻辑功能及其基本应用3.经过实验的方法学习 74LS138的电路结构和特色4.掌握 74LS138的逻辑功能及其基本应用二、实验要求要求一:参照参照内容,调用MAXPLUSII 库中的组合逻辑器件74153 双四数据选择器和 7400 与非门,用原理图输入方法实现一位全加器。

(MULTISIM仿真和FPGA实现)要求二:参照参照内容,调用MAXPLUSII 库中的组合逻辑器件74138 三线八线译码器和 7420 与非门,用原理图输入方法实现一位全减器。

(MULTISIM仿真和FPGA实现)要求三:参照参照内容,调用MAXPLUSII 库中的组合逻辑器件74138 三线八线译码器和门电路,用原理图输入方法实现一个两位二进制数值比较器。

(MULTISIM 仿真和 FPGA 实现)三、实验设施(1)电脑一台;(2)数字电路实验箱;(3)数据线一根。

四、实验原理Multisim的模拟电路编程原理Quartus II的模拟电路编译、波形仿真及目标器件写入的基本应用数字电路逻辑表达式变换的基本知识数据选择器和译码器的电路结构及其特色实验开发板的基本使用知识五、实验内容1、调用 MAXPLUSII 库中的组合逻辑器件 74153双四数据选择器和 7400与非门,用原理图输入方法实现一位全加器。

( MULTISIM仿真和 FPGA 实现)(1)建立真值表、卡诺图及降维卡诺图真值表:真值表:S1卡诺图:C0卡诺图:降维卡诺图:(2)逻辑表达式变换过程(3)原理图( Multisim 和QuartusII 中绘制的原理图):Quartus II中原理图Multisim中原理图(4)波形仿真:(5)记录电路输出结果A B C S C000000001100101001101100101010111001111112、调用MAXPLUSII库中的组合逻辑器件74138三线八线译码器和7420与非门,用原理图输入方法实现一位全减器。

哈尔滨理工大学数字集成电路设计实验报告学院:应用科学学院专业班级:电科12 - 1班学号:1207010132姓名:周龙指导教师:刘倩2015年5月20日实验一、反相器版图设计1.实验目的1)、熟悉mos晶体管版图结构及绘制步骤;2)、熟悉反相器版图结构及版图仿真;2. 实验内容1)绘制PMOS布局图;2)绘制NMOS布局图;3)绘制反相器布局图并仿真;3. 实验步骤1、绘制PMOS布局图:(1) 绘制N Well图层;(2) 绘制Active图层;(3) 绘制P Select图层;(4) 绘制Poly图层;(5) 绘制Active Contact图层;(6) 绘制Metal1图层;(7) 设计规则检查;(8) 检查错误;(9) 修改错误;(10)截面观察;2、绘制NMOS布局图:(1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览;3、绘制反相器布局图:(1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos 组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点;(11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice模拟;4. 实验结果4.1 nmos版图4.2 pmos版图4.3反相器的版图4.4反相器的spice文件4.5反相器的仿真曲线5.实验结论通过对仿真曲线的分析,当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。

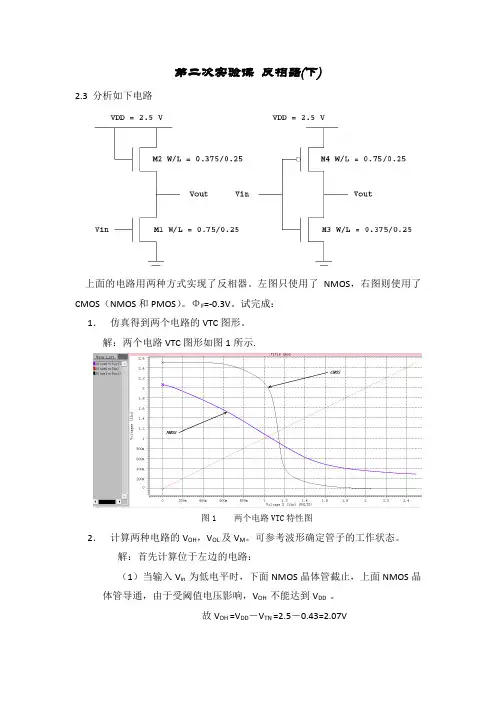

第二次实验课反相器(下)2.3 分析如下电路上面的电路用两种方式实现了反相器。

左图只使用了NMOS,右图则使用了CMOS(NMOS和PMOS)。

ΦF=-0.3V。

试完成:1.仿真得到两个电路的VTC图形。

解:两个电路VTC图形如图1所示.图1 两个电路VTC特性图2.计算两种电路的V OH,V OL及V M。

可参考波形确定管子的工作状态。

解:首先计算位于左边的电路:(1)当输入V in 为低电平时,下面NMOS晶体管截止,上面NMOS晶体管导通,由于受阈值电压影响,V OH 不能达到V DD 。

故V OH =V DD-V TN =2.5-0.43=2.07V(2)当输入V in 为高电平时,下面NMOS 晶体管导通,上面NMOS 晶体管也导通,参考(1)的VTC 曲线可知,此时M1是线性工作区,假设M2是速度饱和,则M2电流'22[()](1+V )2n DS GS T DS DS k W V i V V V L λ=-- M1电流'21[()]2n DS GS T DS k W V i V V V L =-- 令12i i =得V out =0.26V ,所以V Ol =V out =0.26V (参照(1)中VTC 曲线,可知V Ol 也在0.25V 左右)。

(3) 计算V M 时,我们假设两个晶体管都处于速度饱和,且V M = V in = V out ,'2222'2111[()](1+(-V ))2[()](1+V )2n DS DD M T DS DD M n DS GS T DS M k W V I V V V V V L k W V I V V V L λλ⎧=---⎪⎪⎨⎪=--⎪⎩, 令12i i =可得:V M =1.26V 。

随后计算右边的电路由于右边是标准CMOS电路,可以直接按公式求得,于是 V OH =V DD =2.5V, V Ol =0V,n (221DSATp DSATn T DD Tp M V V r V V r=+(V +)++V + 其中p DSATpn DSATn k V r k V =于是M V =1.038V (由(1)的传输特性曲线得到M V =1.12V.)3. 哪一种结构的反相器的功能性更好,为什么?(噪声容限,再生性,过渡区增益)解:(1)首先求左边的电路在阈值电压M V 附近:k g ()voutL in T in d R W V V d L==--=-1.43 M V =1.26V,故 2.14M I H M V V V g=-=V, DD M IL M V V V V g-=+=0.39V , 于是 0.36H D D I HN M V V =-= 0.39L IL NM V ==(2) 然后求右边的电路很容易求得, 1.04M V V =, 6.67g =-故: 1.20M I H M V V VVg =-=0.82DD M IL M V V V V V g -=+=,1.46H DD IH NM V V V =-=0.82L IL NM V V ==。

数电实验1一.实验目的1.了解掌握QuartusⅡ中原理图的设计方法2.了解掌握ED0实验开发板的使用方法二.实验设备1.Quartus开发环境2.ED0开发板三.实验内容要求 1:根据参考内容,用原理图输入方法实现一位全加器。

1)用 QuartusII波形仿真验证;2)下载到 DE0 开发板验证。

要求 2:参照参考内容,用 74138 3-8 译码器和 7400 与非门,用原理图输入方法实现一位全减器。

1)用 QuartusII 波形仿真验证;2)下载到 DE0 开发板验证。

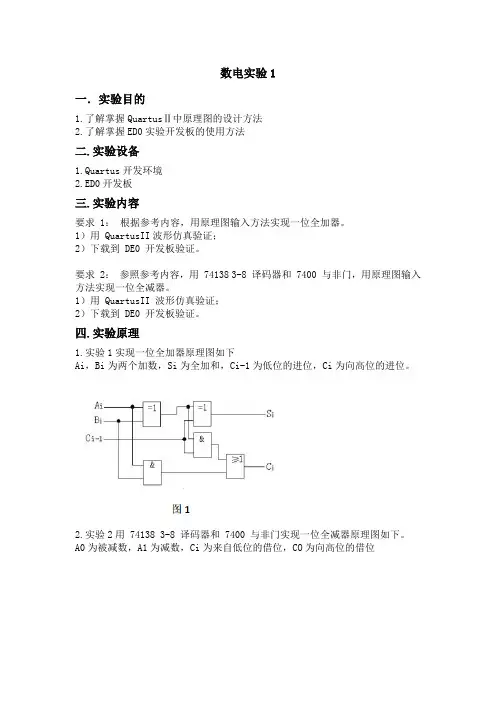

四.实验原理1.实验1实现一位全加器原理图如下Ai,Bi为两个加数,Si为全加和,Ci-1为低位的进位,Ci为向高位的进位。

2.实验2用 74138 3-8 译码器和 7400 与非门实现一位全减器原理图如下。

A0为被减数,A1为减数,Ci为来自低位的借位,CO为向高位的借位五.实验结果实验1:原理图输入波形仿真配置针脚在计算机上完成模拟实验之后,重新进行编译,然后将程序下载到DE0开发板上并对全加器进行验证。

验证结果无误。

实验2:原理图输入波形仿真六.故障排除&实验心得实验中,我们最大的问题就在于如何构建整个系统。

整个实验都是比较基本的一些语句和一些简单门电路的综合使用。

我们进一步的了解了整个系统的构建和编译过程,使我们对VHDL语句和Quartus的使用有了进一步的认识。

个人认为,VHDL语言不够简洁,有些表示比较麻烦。

这次实验首次让我们将数电理论运用到实践,增强了我们对于全加器和全减器的理解和运用,为我们将来的学习和工作提供了良好的基础。

数字集成电路设计课程实验报告姓名:班级:学号:指导老师:实验时间:实验地点:实验一:设计一个反相器一、实验目的1、学习及掌握cadence 图形输入及仿真方法;2、掌握基本反相器的原理与设计方法;3、掌握反相器电压传输特性曲线VTC 的测试方法;4、分析电压传输特性曲线,确定五个关键电压OH V 、OL V 、IH V 、IL V 、TH V 。

二、实验内容本次实验主要是利用cadence 软件来设计一基本反相器(inverter),并利用仿真工具Analog Artist(Spectre)来测试反相器的电压传输特性曲线(VTC, Voltage transfer characteristic curves),并分析其五个关键电压:输出高电平OHV 、输出低电平OLV 、输入高电平IHV 、输入低电平ILV 、阈值电压THV 。

1、在cadence 环境中绘制的反相器原理图如图一所示。

值得注意的是应将NMOS 的衬底接地(GND ),而相应的应将PMOS 的衬底接电源(VDD ),这样不仅能消除体效应,而且还能够减弱闩锁效应(在NMOS 实现中并不存在)。

2、在Analog Environment 中,对反相器进行瞬态分析(tran),仿真时间设置为4ns 。

其输入输出波形如图二所示。

三、实验环境 软件:Cadence硬件:计算机四、实验结果由图可以看出:输出高电平5OH V V =、输出低电平0OL V V =、输入高电平 3.15IH V V =、输入低电平 2.24IL V V =、阈值电压 2.66TH V V =。

所以,噪声容限为:2.240 2.24L IL OL NM V V V =-=-= 53.15 1.85H OH IH NM V V V =-=-=实验二:设计一个水位控制器一、设计要求1、给出满足题目要求的电路图;2、根据设计目标,计算各MOS 管的尺寸;3、对电路进行仿真,仿真内容包括:直流输入范围、直流输出范围;4、对结果进行分析。

数字集成电路实验报告西北工业大学2014年5月12日星期一实验二、反相器(下)三、分析如下电路,解答下面的问题。

上面的电路用两种方式实现了反相器。

左图只使用了NMOS,右图则使用了CMOS(NMOS 和PMOS)。

试完成:ΦF=‐0.3V1.仿真得到两个电路的VTC 图形黄色的线条表示的是第一个反相器的电压传输特性曲线,红色的线条表示的是第二个电压传输特性曲线。

2.计算两种电路的VOH,VOL及VM。

可参考波形确定管子的工作状态。

答:对于第一个电路构成的反相器而言当vin = 0的时候,M1截止,M2导通,输出电压vout = 2.5-0.43 = 2.07V 即 V V OH 07.2=当vin = 2.5V 的时候,M1、M2均导通,且M1处于线性区,M2处于饱和区(速度饱和),通过两个 管子的电流相等,所以有]2/)[()(]2/)[()(2111'222'DS DS TH GS M DSTA DSTA TH DD M DSAT V V V V L W K I V V V V L W K I -⨯-⨯⨯=-⨯-⨯⨯=由于存在体效应M2的阈值电压变为)22(0F SB F T T V V V φφγ-+-+= 其中out SB V V =解得=OL V 0.287V接着计算开关阈值M V ,此时,输入等于输出,判定M1与M2都处于饱和区。

]2/)[()(]2/)[()(2111'12222'2DSSAT DSAT TH GS M n D DSAT DSAT TH GS M n DSATM V V V V LW K I V V V V LW K I -⨯-⨯⨯=-⨯-⨯⨯= 而且OUT IN SB M V V V V ===求得V 995.0=M V而对于CMOS 反相器来说当vin = 0的时候,V V OH 5.2=当vin = 2.5V 的时候,0=OL V接着计算开关阈值M V ,此时,输入等于输出,判定M3与M4都处于饱和区。

集成电路集中上机实验报告——反相器、与非门设计学院:专业:姓名:学号:一、实验目的(一)全面了解Schematic设计环境,并学会运用(二)掌握与非门、或非门、反相器等电路原理图输入方法(三)掌握逻辑符号创建方法二、实验原理启动Schematic Editor后,在命令解释窗口CIW中,打开任意库与单元中的Schematic视图,浏览Schematic Editing窗口,具体介绍如下:图2.1 Schematic Editing窗口菜单栏中可选菜单有Tool、Design、Window、Edit、Add、Check、Sheet、Options等项。

图标栏内的所有命令都可以在菜单栏实现,图标栏提供使用频率较高的一些菜单为快捷方式,旨在提高设计效率。

在设计过程中,除了可以使用图标快捷方式外,还有盲键(Bindkey)快捷方式。

Cadence系统安装过程中已经设置了通用的盲键,但用户可以根据自己的需要自行设置,在CIW窗口中,选择Options→Bindkeys,可以对所有设置的盲键自定义。

Cadence系统支持3D鼠标,左、中、右分别定义为LMB、MMB、RMB。

LMB用于点击和选择之用,MMB用于辅助编辑,RMB与LMB配合使用,在调查元件属性,局域放大,元件旋转等方面都有应用,在具体实验过程中有详细说明。

在所有元件的添加中,必须定义元件的属性。

最后,为了后续设计中执行仿真,每个元件必须具有物理模型(Model),在lab3中将有实例说明。

三、电路原理图设计的一般流程(一)创建库与视图(二)添加元件:在Schematic Editing窗口中,选择Add→Instance。

(三)添加Pins :在左侧Tool bar图标栏中选择pin icon图标,出现Add form,在Pin names栏中输入。

(四)添加Sources和Ground:选择Add→Instance,在Library column中选择analogLib,再选择vdd并添加到schematic中。

1. 2. 计算出这个电路的V OH V OL 及V IH V IL 。

(计算可先排除速度饱和的可能)V in =0时,V OH =2.5VV in=2.5时,假设NMOS 工作在临界饱和区:AI V R I vV V V A I V V L W K I D out L D T in out D T in D61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据D D I I <1,器件实际工作在线性区⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L W KI in OL L D OL OL T in D 5.25.2]2)[(2`6`10115-⨯=K 将, 5.0/5.1=L W,43.0=T V 代入kohm R L 75=解得:=OL V 0.04633V由图得:V OH =2.5V, V OL =0.0356V. 当out in V V =时,NMOS 工作在饱和区⎪⎩⎪⎨⎧+=-⨯=outL D T in D V R I V V L W K I 5.2)(2/2`反相器阈值电压===out in M V V V 0.7932 此时 -6.8978)43.0(875.255.2,)43.0(9375.125.22=--==--=in VinVoutin out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.5458||0.9082||g V V V V g V V V M OH M IL M M IH由图得:V IH=0.881V, V IL=0.0378V.SP文件:.TITLE 1.2UM CMOS INVERTER.options probe.options tnom=25.options ingold=2 limpts=30000 method=gear.options lvltim=2 imax=20 gmindc=1.0e-12.protect.lib'C:\synopsys\cmos25_level49.lib' TT.unprotect.global vddMn out in 0 0 NMOS W=1.5u L=0.5u *(工艺中要求尺寸最大0.5u)RL OUT VDD 75kVDD VDD 0 2.5VVIN IN 0 0.DC VIN 0 2.5V 0.1V.op.probe dc v(out).end2.3.分析电路噪声容限。

数字集成电路设计实验报告Prepared on 24 November 2020哈尔滨理工大学数字集成电路设计实验报告学院:应用科学学院专业班级:电科12 - 1班学号: 32姓名:周龙指导教师:刘倩2015年5月20日实验一、反相器版图设计1.实验目的1)、熟悉mos晶体管版图结构及绘制步骤;2)、熟悉反相器版图结构及版图仿真;2. 实验内容1)绘制PMOS布局图;2)绘制NMOS布局图;3)绘制反相器布局图并仿真;3. 实验步骤1、绘制PMOS布局图:(1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察;2、绘制NMOS布局图:(1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览;3、绘制反相器布局图:(1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice模拟;4. 实验结果nmos版图pmos版图反相器的版图反相器的spice文件反相器的仿真曲线5.实验结论通过对仿真曲线的分析,当输入为高电平时,输出为低电平;当输入为低电平时,输出为高电平。

TTL集成门电路逻辑变换班级:03051001班学号:姓名:同组成员:一、实验目的1.加深了解TTL逻辑门电路的参数意义。

2.掌握TTL逻辑门电路的主要参数及测量方法。

3.认识各种门电路及掌握空闲端处理方法。

4.掌握各种TTL门电路的逻辑功能。

5.掌握验证逻辑门电路的方法。

6.掌握空闲输入端的处理方法。

二、实验设备数字电路试验箱、数字双踪示波器、函数信号发生器、数字万用表、74LS00、电位器、电阻三、实验原理门电路是数字逻辑电路的基本组成单元,它最早是由分立元件构成,体积大,性能差,随着现代半导体工艺的快速发展和电路设计概念的不断改进,使所有分立元件连同分布线都集成在一小块硅芯片上,形成集成逻辑门。

集成逻辑门是最基本的数字集成元件,在数字电路中被大量使用,因此它的特性参数选择得适当与否在很大程度上影响整个电路工作的可靠性,所以理解和掌握集成逻辑门的参数特性对数字电路设计至关重要。

目前使用最普遍的双极型数字集成电路是TTL逻辑门电路,它们通常都采用双列直插式封装在集成芯片内。

双列直插式集成电路的右下方引脚通常是地线GND,左上方引脚一般是电源线VCC,其它引脚的用途如图中门电路的符号所示,每个集成电路都有自己的代号,与代号对应的名称形象地说明了集成电路的用途。

本实验中选用TTL74LS00二输入端四与非门实现与逻辑、或逻辑、异或逻辑,以掌握电路的主要参数的意义和测试方法。

74LS00引脚图门电路是数字逻辑电路的基本组成单元,门电路按逻辑功能可分为:与门、或门、非门及与非门、或非门、异或门等。

按电路结构组成的不同,可分为分立元件电路、CMOS集成门电路、TTL集成门电路等。

集成门电路通常封装在集成芯片内,一般有双列直插和表面贴装两种封装形式。

试验中常用的封装形式为双列直插式。

每个集成电路都有自己的代号,与代号对应的名称形象地说明了集成电路的用途。

如:74LS00是二输入端四与非门,她说明这个集成电路中包含了四个二输入端的与非门。

实验二:Quartus II入门班级:姓名:学号:同组人员:一、实验目的(1)掌握Quartus Ⅱ集成开发软件的原理。

(2)熟练运用Quartus Ⅱ集成开发软件实现基本逻辑电路的实现。

(3)熟悉DEO硬件开发板的连接使用。

二、实验要求要求1:根据参考内容,用原理图输入方法实现一位全加器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求2:参照参考内容,用74138 3-8 译码器和7400与非门,用原理图输入方法实现一位全减器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

三、实验内容(一)全加器的设计与实现a.根据逻辑真值表写出逻辑函数表达式Ai和Bi分别表示加数与被加数,Ci表示低位向本位的进位,Si表示本位和,Ci1表示本位向高位的进位。

b.根据逻辑函数表达式画出电路逻辑图c.在QuartusII上绘制全加器原理图并仿真出波形,结果如下:d.下载到DEO板子上验证,实现全加器功能。

(二)全减器的设计与实现a.根据逻辑真值表写出逻辑函数表达式An和Bn分别表示被减数和减数,Cn表示低位向本位的借位,Dn 表示本位差,Cn1表示本位向高位的借位。

逻辑真值表An Bn Cn Cn1 Dn0 0 0 0 00 1 1 10 1 0 1 10 1 1 1 01 0 0 0 11 0 1 0 01 1 0 0 01 1 1 1 1b.根据逻辑函数表达式画出电路逻辑图c.在QuartusII上绘制全减器原理图并仿真出波形,结果如下:d.下载到DEO板子上验证,实现全减器功能。

四、实验心得通过这个实验,我对与非门的用法有了更深刻的理解,对设计电路也从之前的“纸上谈兵”变成了具体实践,设计以及实验完成之后很有成就感。

最重要的是我了解并掌握了Quartyrs的一些基本用法,相信在以后的学习中可以取得更深入的了解。

《数字集成电路》上机实验姓名:***班级:***学号:***第一次实验一、实验目的:掌握HSPICES软件的使用方法,用于分析二极管及CMOS反相器的直流特性,通过改变电源电压及MOS管的宽长比得到一组CMOS反相器的电压传输特性曲线,从而理解CMOS反相器电压传输特性曲线的影响因素和调整方法。

二、实验内容:1. 由上图所示,令(1)I S=10-14A,T=300K;(2) I S=10-16A,T=300K;(3) I S=10-14A,T=350K,利用SPICE求解V D1、V D2和I D。

【仿真代码】.TITLE amplifierSHU.LIB 'D:\Digital\lib\csmc06.LIB' TT.TEMP temvalueR1 1 2 2kR2 3 4 2kD1 2 3 DMODD2 4 0 DMOD.MODEL DMOD D Is=isvalue.PARAM temvalue=27 isvalue=1E-14 V1 1 0 DC 2.5.OP.ALTER.PARAM temvalue=27 isvalue=1E-16 .ALTER.PARAM temvalue=77 isvalue=1E-14 .OPIONS LIST NODE POST=2.END【结果】【分析】V D1=525.4463mv、V D2=525.4463mv和I D=362.2768uA2. (1)由下图所示,令Vin从0V变化到2.5V,步长为0.5V,利用SPICE求M1管电流变化的曲线,判断管子的工作状态;当M1的尺寸变化为W/L=4u/1u时,求I M1,并解释两条曲线存在误差的原因。

【仿真代码】.TITLE amplifierSHU.LIB 'D:\Digital\lib\mix025_1.lib' TT.PARAM dd=2.5Vdd 1 0 DC ddVin 2 0 DCM_M1 0 2 1 1 pch L=1U W=4U.DC Vin 0 2.5 0.5.PRINT I(2).OP.OPTION NODE LIST POST.END.TITLE amplifierSHU.LIB 'D:\Digital\lib\mix025_1.lib' TT.PARAM dd=2.5Vdd 1 0 DC ddVin 2 0 DCM_M1 0 2 1 1 pch L=0.25U W=1U .DC Vin 0 2.5 0.5.PRINT I(2).OP.OPTION NODE LIST POST.END【结果】【分析】在1.5V之前是工作在线性区,1.5-2V之间是可变电阻区,2V以后工作在饱和区。

数电实验2一.实验目的1.学习并掌握硬件描述语言(VHDL 或Verilog HDL);熟悉门电路的逻辑功能,并用硬件描述语言实现门电路的设计。

2.熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。

3.熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。

4.熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。

二.实验设备1.Quartus开发环境2.ED0开发板三.实验内容要求1:编写一个异或门逻辑电路,编译程序如下。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求2:编写一个将二进制码转换成0-F 的七段码译码器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板,利用开发板上的数码管验证。

要求3:编写一个计数器。

1)用QuartusII 波形仿真验证;2)下载到DE0 开发板验证。

要求4:编写一个能实现占空比50%的5M 和50M 分频器即两个输出,输出信号频率分别为10Hz 和1Hz。

1)下载到DE0 开发板验证。

(提示:利用DE0 板上已有的50M 晶振作为输入信号,通过开发板上两个的LED 灯观察输出信号)。

2)电路框图如下:扩展内容:利用已经实现的VHDL 模块文件,采用原理图方法,实现0-F 计数自动循环显示,频率10Hz。

(提示:如何将VHDL 模块文件在逻辑原理图中应用,参考参考内容5)四.实验原理1.实验1实现异或门逻辑电路,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EXORGATE ISPORT(A,B:IN STD_LOGIC;C:OUT STD_LOGIC);END EXORGATE;ARCHITECTURE fwm OF EXORGATE ISBEGINC<=A XOR B;END;2.实验2实现一个将二进制码转换成0-F的七段译码器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sevendecoder ISPORT (data_in:IN STD_LOGIC_VECTOR(3 DOWNTO 0);dis_out:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END sevendecoder;ARCHITECTURE fwm OF sevendecoder ISBEGINPROCESS(data_in)BEGINCASE data_in ISWHEN"0000"=>dis_out<="1000000";--显示0 WHEN"0001"=>dis_out<="1111001";--显示1 WHEN"0010"=>dis_out<="0100100";--显示2 WHEN"0011"=>dis_out<="0110000";--显示3 WHEN"0100"=>dis_out<="0011001";--显示4 WHEN"0101"=>dis_out<="0010010";--显示5 WHEN"0110"=>dis_out<="0000010";--显示6WHEN"0111"=>dis_out<="1111000";--显示7 WHEN"1000"=>dis_out<="0000000";--显示8 WHEN"1001"=>dis_out<="0010000";--显示9 WHEN"1010"=>dis_out<="0001000";--显示A WHEN"1011"=>dis_out<="0000011";--显示b WHEN"1100"=>dis_out<="1000110";--显示C WHEN"1101"=>dis_out<="0100001";--显示d WHEN"1110"=>dis_out<="0000110";--显示E WHEN"1111"=>dis_out<="0001110";--显示FWHEN OTHERS=> dis_out<="1111111";--灭灯,不显示END CASE;END PROCESS;END fwm;3.实验3完成一个计数器,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter ISPORT ( clk,RST : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0); --四位计数COUT : OUT STD_LOGIC); --进位位END counter;ARCHITECTURE fwm OF counter ISSIGNAL Q1 : STD_LOGIC_VECTOR (3 DOWNTO 0);BEGINPROCESS(clk,RST)BEGINIF RST = '0' THEN Q1<=(OTHERS => '0'); COUT<= '0';ELSIF clk'EVENT AND clk='1' THENQ1<=Q1+1;COUT<= '0';IF Q1 >= "1001" THEN Q1<=(OTHERS => '0'); COUT<= '1';END IF;END IF;END PROCESS;DOUT<=Q1 ;END fwm;4.实验4编写一个能实现占空比50%的5M 和50M 分频器即两个输出,输出信号频率分别为10Hz 和1Hz,VHDL源代码如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY fpq ISPORT(clk:IN STD_LOGIC;clk_out,clk_out1:OUT STD_LOGIC);END fpq;ARCHITECTURE fwm OF fpq ISCONSTANT m : INTEGER:= 25000000; --50M 分频到1Hz 时=25000000。

实验一、反相器链实验要求:下图反相器中的MOS 管L=0.5u ,W=1.2u 。

试建立反相器子电路,并考察子电路的VTC 特性。

建立完整电路后,分析该反相器链的直流传输特性、时序特性及带负载能力(负载为电容0.5P 1P 2P )。

一、设计反相器单元VoutVdd二、写出输入文件,执行DC 分析获得反相器的VTC 特性图 Sp 文件:.TITLE 1.2UM CMOS INVERTER.options probe.options tnom=25.options ingold=2 limpts=30000 method=gear.options lvltim=2 imax=20 gmindc=1.0e-12.protect.lib'C:\synopsys\cmos25_level49.lib' TT.unprotect.global vddMn out in 0 0 NMOS W=1.2u L=0.5u *(工艺中要求尺寸最大0.5u)Mp out in vdd vdd PMOS W=2.4u L=0.5u * 此处W需做更改)CL OUT 0 0.5PFVDD VDD 0 5VVIN IN 0 PULSE(0 5V 10NS 1N 1N 50N 100N).DC VIN 0 5V 0.1V.op.probe dc v(out).end仿真结果:三、写出SUBCKT并实例化三个,来实现反相器链对反相器链执行DC扫描。

Sp文件:.TITLE 1.2UM CMOS INVERTER CHAIN.options probe.options tnom=25.options ingold=2 limpts=30000 method=gear.options lvltim=2 imax=20 gmindc=1.0e-12.protect.lib'C:\synopsys\cmos25_level49.lib' TT.unprotect.global vdd.SUBCKT INV IN OUTMn out in 0 0 NMOS W=1.2u L=0.5uMp out in vdd vdd PMOS W=2.4u L=0.5u.ENDSX1 IN 1 INVX2 1 2 INVX3 2 OUT INVCL OUT 0 1PFVDD VDD 0 5VVIN IN 0 0.DC VIN 0 5V 0.1V.measure DC V1 when v(out)=2.5v.PROBE dc v(out).END仿真结果:V(out)=2.5时,V1的值:四、执行measure 命令测量延迟时间。

实验二半加器、全加器及其应用

一、实验目的:

1.掌握全加器和半加器的逻辑功能。

2.熟悉集成加法器的使用方法。

3.了解算术运算电路的结构。

二、实验设备:

数字电路实验箱,74LS00,74LS86。

三、实验原理:

两个二进制数相加,叫做半加,实现半加操作的电路,称为半加器。

A表示被加数,B 表示加数,S表示半加和,以表示向高位的进位。

全加器能进行加数,被加数和低位来的信号相加,并根据求和的结果给出该位的进位信号。

四、实验内容:

1.半加器,M=0时实现半加功能,当M=1时实现半减功能。

实验电路图:

2.全加器,M=0时实现全加功能,当M=1时实现全减功能。

实验电路图:

五、

实验结果:

1、 半加器:S=A ○+B ,CO=()B A M ⊕

2、 全加器:S= A ○+B ○+C ,CO= ()()BCI M A B C ∙⊕⊕

六、

故障排除:

先排除74LS00和74LS86的故障因素,确保元器件功能完好,然后就是确定线路、引脚和实验电路箱的插口紧密相连。

七、 心得体会:

掌握全加器和半加器的逻辑功能; 熟悉集成加法器的使用方法; 了解算术运算电路的结构。

不仅使我们更好的掌握了基础理论知识,而且能够灵活运用所学知识。

1. 2. 计算出这个电路的V OH V OL 及V IH V IL 。

(计算可先排除速度饱和的

可能)

V in =0时,V OH =

V in=时,假设NMOS 工作在临界饱和区:

A

I V R I v

V V V A I V V L W K I D out L D T in out D T in D 61142`1073.55.207.243.05.21039.7)(2/--⨯=⇒+=⎪⎩⎪⎨⎧=-=-=⨯=⇒-⨯=这样的话根据 D D I I <1,器件实际工作在线性区

⎪⎪⎪⎩⎪⎪⎪⎨⎧=+=--=v V V R I V V V V L W K I in

OL L D OL OL T in D 5.25.2]2)[(2`

6`10115-⨯=K 将, 5.0/5.1=L W ,43.0=T V 代入kohm R L 75=

解得:

=OL V

由图得:V OH =, V OL =.

当out in V V =时,NMOS 工作在饱和区

⎪⎩⎪⎨⎧+=-⨯=out

L D T in D V R I V V L W K I 5.2)(2/2`

反相器阈值电压===out in M V V V

此时 -6.8978)43.0(875.255.2,)43.0(9375.125.22=--==

--=in Vin

Vout in out V d d g V V ⎪⎪⎩⎪⎪⎨⎧=--==+=0.5458||0.9082||g V V V V g V V V M OH M IL M M IH

由图得:V IH =, V IL =.

SP 文件:

.TITLE CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=

.protect

.lib'C:\synopsys\' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W= L= *(工艺中要求尺寸最大) RL OUT VDD 75k

VDD VDD 0

VIN IN 0 0

.DC VIN 0

.op

.probe dc v(out)

.end

2.3.分析电路噪声容限。

计算NM H(高电平噪声容限)和NM L(低电平噪

声容限), 并使用HSPICE画出反相器的VTC曲线。

NM H=V OH - V IH=

NM L= V IL- V OL=

SP文件:

.TITLE CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=

.protect

.lib'C:\synopsys\' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W= L= *(工艺中要求尺寸最大)

RL OUT VDD 75k

VDD VDD 0

.DC VIN 0

.op

.probe dc v(out)

.end

3.4.使用HSPICE画出RL=35k,75K,150k三种情况下的VTC。

(从左到右依次为RL=150k,75k, 35k)

SP文件:

.TITLE CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=

.protect

.lib'C:\synopsys\' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W= L=

RL VDD OUT 75k

VDD VDD 0

.DC VIN 0

.probe V(out)

.probe V(in)

.alter

.TITLE Exercise RL = 150k

RL Vdd out 150k

.alter

.TITLE Exercise RL = 35k

RL Vdd out 35k

.end

1.5.对2的结果进行仿真验证。

(tran 仿真;输入加脉冲,上升和

下降时间都为5ns)

由图得:t PHL=; t PLH=s

SP文件:

.TITLE CMOS INVERTER

.options probe

.options tnom=25

.options ingold=2 limpts=30000 method=gear

.options lvltim=2 imax=20 gmindc=

.protect

.lib'C:\synopsys\' TT

.unprotect

.global vdd

Mn out in 0 0 NMOS W= L= *(工艺中要求尺寸最大)

RL OUT VDD 75k

CL OUT 0 3p

VDD VDD 0

Vin in 0 PULSE(0 100n 5n 5n 5u 10u)

.TRAN 1n 30u

.measure tran TPHL trig v(in) val= td=1n rise=2 targ v(out) +val= td=1n fall=2

.measure tran TPLH trig v(in) val= td=1n fall=2 targ v(out) +val= td=1n rise=2

.probe V(out)

.probe V(in)

.end。