MPC860在七号信令网关中的应用

- 格式:doc

- 大小:7.05 KB

- 文档页数:3

七号信令的数据配置及相关问题一、概述七号信令是专门用来传送电信网节点处理机之间各种类型信令和信息的一种数据通信形式。

七号信令系统划分为一个公共的消息传递部分(MTP)和若干个用户部分(TUP),包括四个功能级:信令数据链路功能、信令链路功能、信令网络功能及用户部分。

以消息传递部份(MTP)和用户部分(TUP)组成的四级信令结构,能够有效地传送各种呼叫控制和接续控制信息,是电话通信网特别是数字电话网理想的信令系统。

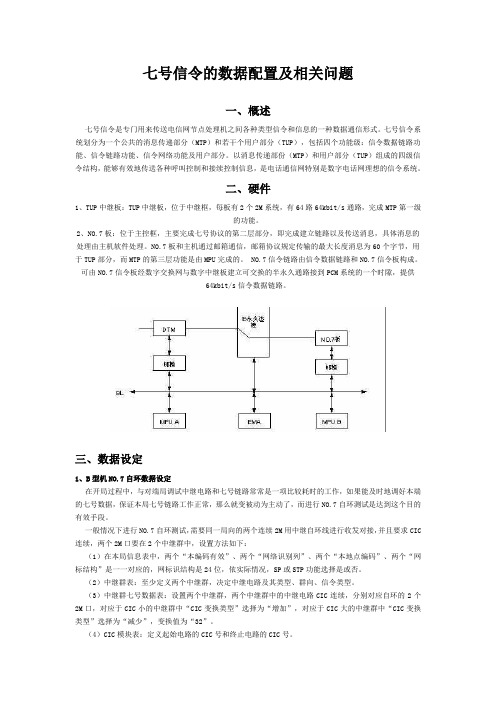

二、硬件1、TUP中继板:TUP中继板,位于中继框,每板有2个2M系统,有64路64kbit/s通路,完成MTP第一级的功能。

2、NO.7板:位于主控框,主要完成七号协议的第二层部分,即完成建立链路以及传送消息,具体消息的处理由主机软件处理。

NO.7板和主机通过邮箱通信,邮箱协议规定传输的最大长度消息为60个字节,用于TUP部分,而MTP的第三层功能是由MPU完成的。

NO.7信令链路由信令数据链路和NO.7信令板构成。

可由NO.7信令板经数字交换网与数字中继板建立可交换的半永久通路接到PCM系统的一个时隙,提供64kbit/s信令数据链路。

三、数据设定1、B型机NO.7自环数据设定在开局过程中,与对端局调试中继电路和七号链路常常是一项比较耗时的工作,如果能及时地调好本端的七号数据,保证本局七号链路工作正常,那么就变被动为主动了,而进行NO.7自环测试是达到这个目的有效手段。

一般情况下进行NO.7自环测试,需要同一局向的两个连续2M用中继自环线进行收发对接,并且要求CIC 连续,两个2M口要在2个中继群中,设置方法如下:(1)在本局信息表中,两个“本编码有效”、两个“网络识别列”、两个“本地点编码”、两个“网标结构”是一一对应的,网标识结构是24位,依实际情况,SP或STP功能选择是或否。

(2)中继群表:至少定义两个中继群,决定中继电路及其类型、群向、信令类型。

(3)中继群七号数据表:设置两个中继群,两个中继群中的中继电路CIC连续,分别对应自环的2个2M口,对应于CIC小的中继群中“CIC变换类型”选择为“增加”,对应于CIC大的中继群中“CIC变换类型”选择为“减少”,变换值为“32”。

M PC860T 处理器在卫星通信数据业务处理中的应用杨巧丽,倪 炜(总参第63研究所,江苏省南京市210007)摘 要:提出了一种新的基于MPC860T 的卫星通信数据业务处理模块。

介绍了MPC860T 的内部结构和基本特性,描述了卫星通信数据业务处理模块的主要功能及其基于AT 命令的工作流程,给出了MPC860T 硬件平台的接口电路、存储器电路、复位和时钟电路的设计方案,分析了基于实时操作系统Vx Works 软件平台的C /C++程序的实现、调试和下载过程。

显示了MPC860T 在通信处理方面的优越性。

关键词:卫星通信;数据业务处理;Vx Works;MPC860T;AT 命令中图分类号:T N927.2收稿日期:2005208216;修回日期:2006201213。

0 引 言随着各种新技术的不断应用,卫星通信业务也从单一话音向数据、图像等多媒体方向发展,新一代卫星通信设备将能够同时支持两路话音或数据业务,根据其信息处理量大、通信接口种类繁多以及实时处理速度快等需求特点,其数据业务处理模块将采用Mot or o 2la 公司提供的PowerPC 系列处理器MPC860T 来构建其硬件平台,软件平台将采用W indR iver 公司提供的Vx Works 实时操作系统和C /C++语言,以提高该卫星通信设备的实时性、可靠性和稳定性。

1 M PC860T 简介MPC860T 是Mot or ola 公司基于嵌入式PowerPC 体系结构设计的32位多用途通信处理器,内部集成了嵌入式PowerPC 内核、CP M (通信处理模块)和FEC (快速网络控制器)。

由于CP M 和FEC 分担了嵌入式Po werPC 内核的外围处理任务,因此为实现低功耗、低成本和高性价比的通信产品提供了保证。

CP M 支持8个串行通道:2个S MC (串行管理控制器)、4个SCC (串行通信控制器)、1个SP I (串行外围接口)电路和1个I 2C 接口。

基于MPC860的综合复分接设备设计及实现作者:陈清亮来源:《中国新通信》2014年第04期【摘要】本文根据用户实际应用需要提出了一种基以MPC860的综合复分接设备设计与实现方案。

方案中利用以具有代表性的广泛应用的MPC860作为核心芯片,配以其他功能芯片设计和实现了基于嵌入式技术的综合复分接设备,该设备可实现二/四线音频、PTT音频、异步数据、电话、以太网等业务的接入和交换并可将接入的业务信息通过数字中继接口(E1)进行远程传输。

【关键词】综合业务接入嵌入式系统 MPC860一、引言某用户根据形势发展需要,需要对目前的短波机动通信车系统进行技术改造,增加部分设备,将分散的机动通信车辆组合成机动通信系统,以形成具有多种通信手段、多种接入方式的综合化、网络化、自动化的通信系统。

本文所讨论的综合复分接设备是某短波机动通信车技术改造中的核心设备,可实现二/四线音频、PTT音频、异步数据、电话、以太网等业务的接入和交换并可将接入的业务信息通过数字中继接口(E1)进行远程传输。

二、MPC860处理器简介MPC860是Mororla公司嵌入式芯片MPC8XX系列微处理器中的一种,它内部集成了微处理器和一些控制领域的常用的外围组件,特别适用于通信产品,器件具有良好的适应性、扩展能力强和集成度高。

本设计采用了MPC860T芯片,该芯片CPU总线为32位,总线速度最高可达80M,处理器内部集成了通用CPU、专用通信控制RISC和定时、DMA、缓冲区管理等资源,可提供10/100M以太网控制器、HDLC同步通信控制器和异步通信控制器等多种网络通信控制器和通信接口,大大增强了嵌入式系统的功能,简化了系统设计,提高了可靠性。

三、综合复分接设备硬件设计与实现(一)综合复分接设备硬件体系架构综合复分接设备硬件设计采用模块化设计,交换控制部分设计为系统板,是整个系统的控制核心,主要实现系统控制、业务处理和电话处理等功能;各类业务分别作为功能模块集成在母板上,实现各业务接入和基本接口功能。

MPC860 IDMA接口在嵌入式IP-CATV数据广播网关中的

应用

戴玮;张朝阳

【期刊名称】《计算机工程与应用》

【年(卷),期】2004(040)009

【摘要】介绍了MPC860IDMA接口的特点,并结合CATV网络IP数据广播网关项目阐述其在VxWorks嵌入式实时操作系统下的实现,最后对实现的IDMA性能作了简要分析.

【总页数】4页(P126-128,187)

【作者】戴玮;张朝阳

【作者单位】浙江大学信电系通信网络实验室,杭州,310027;浙江大学信电系通信网络实验室,杭州,310027

【正文语种】中文

【中图分类】TP316.2

【相关文献】

1.IP-CATV网关中的BSP开发 [J], 李芸;傅一恭;王匡;张明

2.IP-CATV/CATV-IP网关中NIOS嵌入式系统的实现 [J], 傅一恭;李芸;王匡

3.MPC860在七号信令网关中的应用 [J], 朱建军;杨镇西;丁有志;高志强

4.SPORT及IDMA接口在电力系统监控产品中的应用 [J], 孙瑞正

5.基于MPC860的数据采集接口的设计与实现 [J], 陈麒;张晓斌;董延军

因版权原因,仅展示原文概要,查看原文内容请购买。

MPC860 UPM口的应用一、MPC860的UPM口的结构UPM(User Programmable Machines)是MPC860提供给用户的可编程存贮器接口。

MPC860有8个片选机构即/CS0~/CS7,任意一个片选机构都可以配置成GPCM或UPM,但总的UPM的个数不能超过两个,即:UPMA和UPMB。

UPM提供了非常灵活的可编程性,可以和需要复杂时序的外设相连,比如DRAM或SDRAM等存贮器。

UPM有64个RAM WORDS(32位),用于产生时序。

这64个RAM WORDS被分割成6个区域它们分别是:1.single read request 8个WORDS,当CPU进行single read操作时将按这些RAM WORDS的控制产生相应的时序。

2.burst read request 16个WORDS,当CPU进行burst read操作时将按这些RAM WORDS的控制产生相应的时序。

3.single write request 8个WORDS,当CPU进行single write操作时将按这些RAM WORDS的控制产生相应的时序。

4.burst write request 16个WORDS,当CPU进行burst write操作时按这些RAM WORDS的控制产生相应的时序。

5.periodic timer request,每个UPM都有一个定时器,定时器定时时间到,就按这些RAM WORDS的控制产生相应的时序。

注意这个时序和数据线没有关系,通常用于存贮器刷新。

6.exception condition request,当/TEA,/SRESET或/HRESET被外部设备拉低的话,UPM就按这些RAM WORDS的控制产生相应的时序。

这样可以在发生异常时控制时序以免数据丢失。

二、UPM的寄存器和它的RAM WORDS。

三、MPC860和SDRAM(以KM432S2030B为例)的接口。

MPC860寄存器配置1999.10 Rev 1.01 概述MPC860的系统接口单元(SIU )控制系统启动、初始化、运行、保护和外部系统总线。

这些功能是靠许多寄存器实现的。

这篇文档将详细说明各个寄存器的配置情况。

2 寄存器的配置按功能分类,可以将寄存器分为系统配置和保护寄存器、复位寄存器、时钟和电源寄存器、存储器控制器寄存器和PCMCIA 寄存器等。

下面分别说明配置情况。

2.1 系统配置和保护寄存器配置系统配置和保护寄存器包括IMMR 、SIUMCR 、SYPCR 、TESR 、SIPEND 、SIMASK 、SIEL 、SIVEC 、SWT 、SWSR 、DEC 、TBU 、TBL 、TBREFA 、TBREFB 、TBSCR 、RTCSC 、RTC 、RTCAL 、RTSEC 、PIT 、PISCR 、PITC 、PTTR 等,其中除了IMMR 、 SIUMCR 、SYPCR ,其它的暂不用进行配置。

2.1.1 Internal Memory Map Register (IMMR)IMMR 指示特殊设备和内部存储器映像的基地址,这是一个32位的寄存器,其中0~15bit 为基地址的值(ISB ),根据系统复位时配置字的值来定。

在本次设计中,ISB 的值置为0xFF00,表示内部存储器映像的基地址为0xFF000000。

2.1.2 SIU Module Configuration Register (SIUMCR)通过SIUMCR ,可以配置SIU 的以下功能: 外部总线仲裁 外部主机支持 调试口配置系统接口管脚配置 校验支持表2-1为SIUMCR 的配置说明。

表2-1 SIUMCR 配置说明 位名 称描 述配 置0 EARB 外部仲裁,根据复位配置字设置0 实行内部仲裁1 实行外部仲裁 0 没有外部仲裁1-3 EARP 外部仲裁请求优先级000 最低优先级111 最高优先级0004-7 保留00008 DSHWData show cycles 0 不显示 1 显示所有的内部数据周期0 但调试时可设为“1”9-10 DBGC 调试管脚配置,根据复位配置字设置 11 11-12 DBPC 调试口管脚配置,根据复位配置字设置 0013保留14 FRC 配置管脚FRZ/IRQ6的功能0 FRZ/IRQ6配置为FRZ1 FRZ/IRQ6配置为IRQ6 015 DLK锁住调试寄存器 0 复位时的状态1 8-15位被锁住,不再执行对这些位的写操作,当内部FRZ 信号有效时才可以写这些位 1 这些位由复位配置字决定,不需要改写16 OPAR 奇校验0 读内存时进行奇校验1 写内存时进行奇校验任意17 PNCS非存储器控制器区域的校验使能,可为不受存储器控制器控制的内存区域产生和检查校验位 0 没有不受存储器控制器控制的内存区域18 DPC 数据校验管脚配置0 DP[0-3]/IRQ[3-6]配置为IRQ[3-6]1 DP[0-3]/IRQ[3-6]配置为DP[0-3] 0 不需要数据校验19 MPRE 多处理器保留使能0 RSV/IRQ2配置为IRQ21 RSV/IRQ2配置为RSV 020-21 MLRC 多级保留控制00 KR/RETRY/IRQ4/SPKROUT 配置为 IRQ401 KR/RETRY/IRQ4/SPKROUT 配置为三态10 KR/RETRY/IRQ4/SPKROUT 配置为KR/RETRY 11 KR/RETRY/IRQ4/SPKROUT 配置为SPKROUT 0022 AEME外部异步主控制器使能0 存储器控制器忽略AS 信号的状态1 存储器控制器将AS 信号的有效解释为外部异步主控制器正在初始化一次transaction 023 SEME外部同步主控制器使能(同AEME )0 24 BSC 配置存储器控制器和PCMCIA 接口的字节选择信号0 25 GB5E GPL_B5使能0 BDIP 功能1 GPL_B5功能26 B2DD Bank 2 double drive ,如果置位,GPL_x2可配置为CS20 27 B3DD Bank 3 double drive ,如果置位,GPL_x3可配置为CS30 28-31 保留0000SIUMCR 的值配置为0x006100002.1.3 System Protection Control Register (SYPCR)SYPCR 控制系统监视器和总线监视器的时序。

七号信令的四级功能结构七号信令(SS7 signaling system number 7)是一种全球通用的电话信令协议,被广泛用于公共交换电话网络(PSTN)和移动通信网络中的信令传输和控制。

七号信令的四级功能结构是指其在系统中的四个主要功能层级,包括物理层、传输层、网络层和应用层。

在下面的文章中,我们将逐步解析七号信令的四级功能结构,探讨每个层级的作用和功能。

物理层(P h y s i c a l l a y e r)是七号信令的最底层,它负责传输二进制数据。

在物理层中,数据以电信号的形式通过传输介质(如光纤、铜线或无线电波)进行传输。

物理层负责将数据按照特定的传输规则进行编码和解码,以确保数据的正确传输和接收。

在七号信令中,物理层的主要任务是提供可靠的信道,确保信令数据能够在不同设备之间进行传输。

传输层(T r a n s p o r t l a y e r)负责在物理层之上提供端到端的可靠数据传输。

传输层通过使用适当的传输协议(如T C P或U D P)将数据分割成小的数据包,并确保这些数据包按照正确的顺序传输和重新组装。

传输层还负责错误检测和纠正,以保证数据的完整性和准确性。

在七号信令中,传输层的主要任务是提供可靠的数据传输服务,确保信令数据在网络中的可靠传输。

网络层(N e t w o r k l a y e r)负责在传输层之上进行路由和转发数据。

网络层使用路由表来确定数据包的最佳路径,并根据实际网络的拓扑结构将数据包发送到目标设备。

网络层还负责数据包的分段和重新组装,以确保数据能够按照正确的顺序送达目标设备。

在七号信令中,网络层的主要任务是提供逐跳(h o p-b y-h o p)的数据传输服务,确保信令数据按照正确的路径在网络中转发。

应用层(A p p l i c a t i o n l a y e r)是七号信令的最高层,负责提供信令传输和控制的实际功能。

应用层定义了一系列的协议和接口,用于执行各种不同的信令任务,如呼叫建立、呼叫保持、呼叫释放等。

14---1 在本章中你可以学到:1、定义SMC2、列出SMC管脚3、描述SMC怎样工作4、描述在UART中SMC怎样接收和发送。

5、初始化SMC为UART14---2 什么是SMC?SMC为2个全双工通道,编程可以配置它们独立支持UART,透明方式和GCI。

SMC比SCC的能力少一些,它支持少一些协议,而且CPM RISC提供的服务也少一些。

这个图说明SMC的工作。

注意,与SCC一样,SMC使用缓存描述字符,缓存在存储器中,与SCC一样,SMC向CPM RISC 提供请求,使SDMA传送数据。

SCC与SMC一个显著的不同为没有FIFO做接收和发送工作,相反接收和发送为双缓存。

让我们看一下SMC接收工作。

首先,数据接收到接收移位器,当第一个数据到达时,SMC决定第一个缓存描述符是否空。

然后,SMC 向CPM RISC请求服务。

第3步,CPM RISC通过写SDMA从接收寄存器中转移命令入当前接收缓存。

现在,让我们看一下SMC发送工作。

首先,在发送寄存器中必须有空间,SMC查询第一个发送缓存描述字符,当有数据发送时,SMC向CPM RISC请求服务。

然后,CPM RISC写SDMA从当前发送缓存中移动命令到发送寄存器。

SMC重要的特性有:1、以UART或透明方式传输数据。

2、工作在非复用串行接口(NMSI)方式或时分复用总线。

3、支持TDM的GCI为ISDN应用。

4、工作在全双工。

5、经环回和回波方式支持测试和调试。

14---3 什么是SMC管脚?下图总结SMC管脚。

有3个SMC管脚,一个发送管脚,一个接收管脚步和同步管脚,同步管脚在发送和接收开始后,只用于透明方式。

这个图说明了在端口B中这些管脚的位置。

一些可以共用,用户必须根据需要配置这个端口,它可以通过端口配置寄存器实现。

14---4 SMC举例。

这张图说明了SMC工作的例子。

SMC通常用于RS232,可以将发送和接收管脚连接到RS232接口,这个接口接到一个DB 9插座或支持连接到一个终端。

MPC860在七号信令网关中的应用摘要:介绍了PowerPC MPC860的内部结构、主要功能和性能特性,描述了它在七号信令网关中的应用,突出了其良好的性能及在七号信令网关中的重要地位。

关键词:PowerPC MPC860 通信处理模块七号信令1 MPC860介绍PMC860是Motorola PowerPC系列CPU芯片主导产品,是互联网络和数据通信及控制领域使用较多、性能相当优越的嵌入式微处理器,内部集成了微处理器和一些通信领域的常用外围设备控制组件。

MPC860相对先前的68K系列,性能和功能都有了大幅提高,CPU处理速度更快,通信处理能力强大。

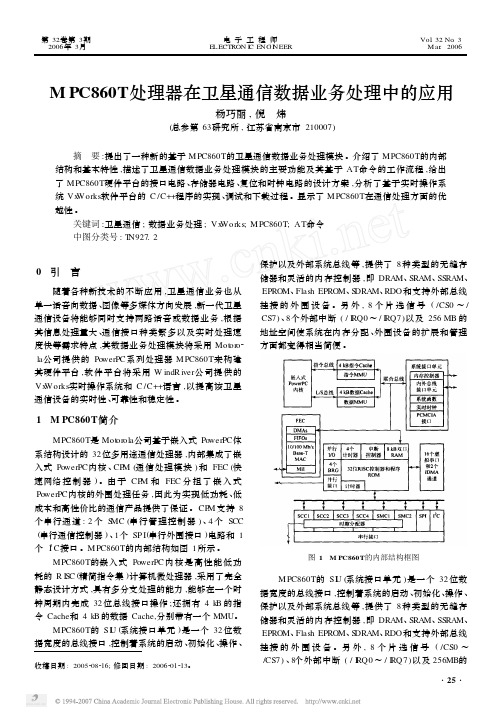

MPC860结构框图如图1所示。

由图1可以看出,MPC860主要可分为三部分:PowerPC处理器核、系统接口单元(SIU)和通信处理模块(CPM)。

嵌入式PowerPC内核是主要的核心处理机单元,采用USIA(User Instruction Set Architecture)结构和全静态设计,拥有整形单元IU(Integer Unit)和加载/存储单元LSU(Load/Store Unit),支持32位内/外部总线接口。

它包括4KB数据和指令高速缓存;集成有存储管理单元MMU;在50MHz时钟输入时拥有66MIPS的指令处理速度。

系统接口单元主要包括存储控制、总线监视、中断控制、软件看门狗、实时时钟、复位控制、总线仲裁和JTAC调试等功能模块。

在32位系统总线下存储控制器支持动态数据总线宽度,可以分别支持8、16和32位外设或存储设备。

通信处理机模块主要包括RISC处理器、四个串行通信控制器(SCC)、两个串行管理控制器(SMC)、一个串行外围接口电路(SPI)、一个I2C(Inter-Integrated Circuit)接口、5KB双端口RAM、三个并行I/O端口、四个独立的波特率发生器以及16位支持SCC、SMC、SPI和I2C的串行DMA通道。

SCC可支持以太网、HDLC/SDLC、HDLC总线、AppleTalk、7号信令系统、UART、BISYNC、透明传输、支持PPP的异步HDLC等标准协议;SMC则可支持UART和透明传输等模式。

CPM 在几个不同的通信组件如SCC和SMC上可以同时收发数据,所有的通信组件可以独立地工作。

SCC和SMC的物理接口由串行接口SI(Serial Interface)实现,SI允许SCC和SMC有两种外部连接方式:时分复用(TDM)接口引脚和非时分复用串行接口(NMSI)时的专用引脚。

时分复用接口由MPC860的TDM引脚和时隙分配器(TSA)实现。

MPC860提供两个TDM接口(TDMa、TDMb),用户可以通过编程TSA来实现TDM和SCC、SMC之间的数据路由。

每个通信设备都有独立的DMA控制器,32位RISC控制这16个串行DMA在通信设备与双端口RAM或外部SDRAM 之间传送数据。

接收数据时,串行DMA从通信设备接收数据并将数据存入双端口RAM或外部SDRAM中;发送时顺序相反,串行DMA从双端口RAM或外部SDRAM中读取数据,由通信设备完成数据的发送。

MPC860采用双处理器结构,内部集成PowerPC Processor和CPM RISC Processor。

PowerPC执行高层代码,完成对外设的配置;RISC用来处理通信控制中的底层通信任务。

两个处理器通过内部的5KB双端口RAM相互配合工作。

在该存储区,每个处理器都可以根据运行情况独立设置控制位、读取状态位。

由于CPM分担了嵌入式PowerPC的外围工作任务,减少了PowerPC对底层通信任务的干预,因而提高了PowerPC的工作效率。

[!--empirenews.page--] 由于通信处理模块中各通信控制器支持多种网络协议再加上PowerPC较快的处理速度,MPC860在许多领域得到了大量的应用,尤其适用于宽带接入设备如路由器、接入集线器、LAN/WAN交换机、PBX系统和STM网关等设计。

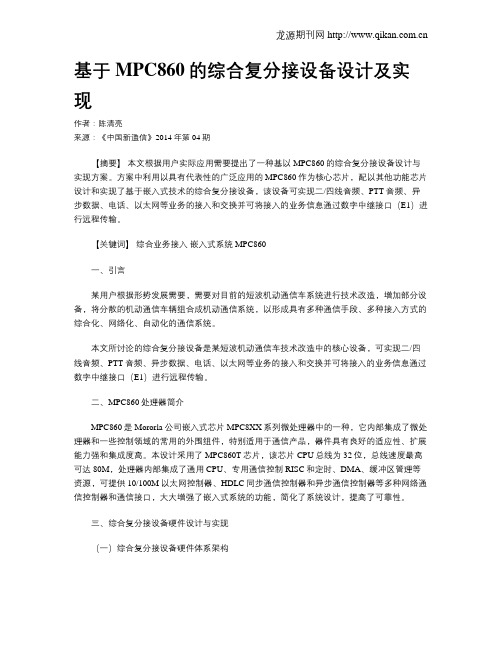

2 七层信令系统七号信令系统是数字通信网中采用最多的公共信道信号技术,它由消息传递部分(MTP)和用户部分(UP)组成。

消息传递部分又可分为信令数据链路、信令链咱和信令网三部分,即通常所称的MTP1、MTP2和MTP3;用户部分则可分为电话用户部分(TUP)、数据用户部分(DUP)和ISDN 用户部分(ISDN-UP)。

其结构图如图2所示。

信令数据链路(MTP1)是指信令传递的物理介质,主要定义了信令数据链路的物理、电气和功能特性,规定与数据链路的连接方式,为信令链路提供信息载体。

信令链路(MTP2)规定信令消息在信令数据链路上传递的功能和程序,与信令数据链路一起为两点间信令传递提供可靠的功能和程序,主要用来实现消息路由、消息识别、消息分配以及信令业务量管理、信令链路管理和信令路由管理等功能。

随着七号信令的普及,七号信令的业务量不断增加,特别是在移动信令网上,原有64kbps信令链路已经不能完全适应业务量增长的需求,对2Mbps高速信令链路的需求日益迫切。

在下面的设计中,同时提供了64kbps和2Mbps两种迫令链路,以满足不同业务的需求。

3 七号信令处理子系统的实现七号信令处理子系统是七号信令网关的一部分,主要用来实现MTP中一、二级功能,同时为二、三级提供可靠的数据通路。

3.1 硬件组成七号信令处理子系统的硬件主要由核心处理器MPC860、数据交换网络(DSN)、E1接口模块、内存SDRAM、引导FLASH和HDLC控制器组成,结构如图3所示。

E1接口模块选用集成有E1成帧器(FRAMER)和线路接口单元(LIU)的专用E1收发器。

E1收发器直接挂接到MPC860 PPC总线上,由MPC860配置。

在接收方向,每4路E1复用为128通道的8.192Mbps H-MVIP(大容量多路复选综合协议)接口数据(与H-100兼容);发送方向相反,8.192Mbps H-MVIP分用出4路E1。

线路接口单元完成数据的A/D和D/A转换,有B8ZS、HDB3和AMI三种数据编解码方法可供选择。

数据交换网络可以采用专用的多速率交换芯片实现。

将多条E1链路的任意32或64时隙交换到MPC860的串行通道SCCn(n可以为1,2,3,4中的一个或多个)上。

交换芯片的配置也是由MPC860完成,根据交换配置的不同,可以实现64Kbps和2Mbps两种不同的信令链路。

与数据交换网络相连的串行通道SCCn和MPC860的QMC控制。

QMC(QUICC Multichannel Controller)是QUICC多通道控制器的简称。

每个SCC都可以工作在QMC模式下,独立支持64条信道,并且允许将64条信道任意映射到TDM中的64个时隙。

QMC同时使用TSA的两个TDM(TDMa和TDMb),每条信道可以独立地配置成HDLC或透明传输(transparent)模式。

[!--empirenews.page--]HDLC 控制器为MTP2与MTP3通信提供可靠的物理链路,每个HDLC控制器可以提供多条HDLC链路。

HDLC控制器由MPC860通过PCI桥配置,PCI桥则由专门的桥接芯片来实现。

桥接芯片和MPC860通过PPC总线相连(称作Qbus),与HDLC控制器都挂接在PCI总线上。

桥接芯片完成Qbus 和PCI总线之间电路特性的[1][2]下一页转换、数据传递以及地址和存储空间的映射。

内存(SDRAM)用来存放用户数据和代码,为程序运行和保存临时文件提供空间。

由于系统中有不同的总线主设备要用SDRAM存储数据和代码,各设备并不都能提供内部地址复用功能,所以SDRAM采用外部地址复用。

可以根据实际需要采取不同大小的内存。

上电引导Flash用来固化上电引导程序、操作系统内核以及用户应用程序。

为便于调试,系统提供RS232串口和10Mbps/100Mbps网口与计算机通信。

串口使用MPC860的SMC1或SCM2,通过RS232收发器完成RS232电平转换。

10Mbps和100Mbps网口可分别采用串行通信控制器SCC和快速以太网控制器FEC。

通过这些调试口可以完成操作系统内核和应用程序的加载,对系统性能和运行状况进行实时监控。

另外系统还采用MPC860的BDM(Background Debug Mode)作为系统的调试端口,应用VisionCLICK或XRAY等调试软件对系统进行调试,完成操作系统内核的加载和固化等。

可编程逻辑模块CPLD主要用来实现:(1)各模块间时序关系的调整;(2)译码逻辑;(3)系统运行状态的监测; >(4)为调试而设计的其他相关逻辑控制。

(5) CPLD的具体实现可以有多种选择,如Xilinx的Foundation、Maxplus等。

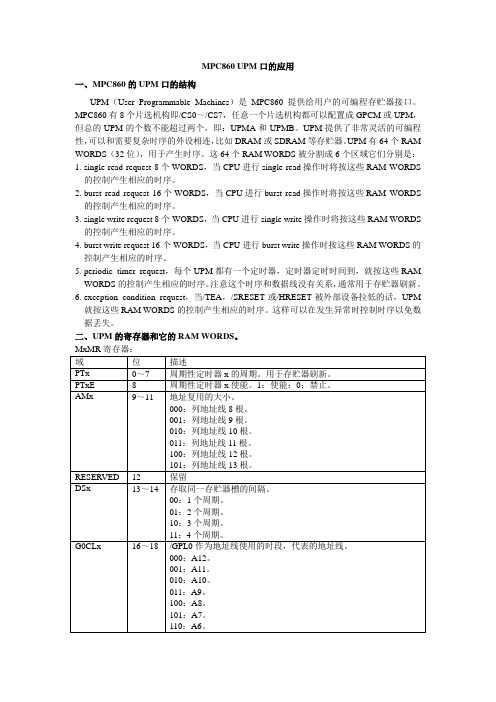

3.2 软件实现针对系统硬件设计,系统软件分成相应的几个模块,主要包括BSP、数据链路初始化和MTP2,如图4所示。

(1)BSP(Board Support Packet)为Vxworks操作系统内核提供基本硬件接口,完成上电后的硬件初始化,支持Vxworks与硬件驱动的通信。

根据系统硬件的实际应用情况,制作生成BootROM映像和Vxworks映像。

其中BootROM映像完成最小的系统初始化,同时为装载Vxworks映像提供环境。

(2)初始化模块包括了对E1接口、数据交换网络、HDLC控制模块和桥接芯片的初始化,使得各模块处于激活或工作状态;(3)MTP2一方面根据MTP3的编程功能,把要发送的信令消息发到信令数据链路上去,同时把接收的信令消息传送到MTP3;另一方面,还要在信令点终端内或两个终端之间传递信令链路状态信息及处理机状态信道,并根据这些信息采取一定的控制处理措施。

MTP2可分为链路状态控制、起始定位控制、处理机故障控制、基本发送控制、基本接收控制、定位误差率监视、信号单元误差监视和拥塞控制等模块。

[!--empirenews.page--]七号信令处理子系统为用户提供了64kbps和2Mbps两种信令链路,可以满足不同的业务需求。

MPC860作为主控器件,很好地完成了对各子模块的配置和监控,其快捷的处理速度和强大的通信处理能力为系统提供了很好的实时性。