一种基于FPGA的真随机数发生器设计与实现

- 格式:pdf

- 大小:324.14 KB

- 文档页数:5

基于 FPGA 一种真随机数生成器的设计和实现吴飞;李艳萍【摘要】Aiming at the application of random number in secure communication , we design and implement a new FPGA-based true random number generator ( TRNG) in this paper .It takes the metastability of RS flip-flop as the random source to reduce the phase shift of clock signal and minimises the process differences of internal components so as to guarantee the randomness of output sequence .The outputs of multi-triggers are conducted the XOR operations and are added the post-processing module for enhancing the quality of random sequences and increasing the entropy per bit .This design has been implemented on Xilinx Spartan 3 XC3S400 platform, the random sequence generated can pass the NIST test , and all the indexes meet the design requirements .The true random number generator consists of common logic unites only, it can be quickly transplanted into ASIC design and shorten the development cycle .%针对随机数在保密通信中的应用,设计并实现一种基于FPGA的真随机数生成器,将RS触发器的亚稳态作为随机源,减小时钟信号的相位偏移,最小化内部元件的工艺差异,从而保证输出序列的随机性,对多个触发器的输出进行异或操作并且加入后处理模块来提高随机序列的质量和增加每比特的熵。

基于FPGA的伪随机序列发生器设计方案1基本概念与应用1)1FSR:线性反馈移位寄存器(1inear feedbackshiftregister,1FSR)是指给定前一状态的输出,将该输出的线性的薮再用作输入的移位寄存器。

异或运算是最常见的单比特线性函数:对寄存器的某些位进行异或操作后作为输入,再对寄存器中的各比特进行整体移位。

1FSR产生的两种形式为伽罗瓦(Ga1ois)和斐波那契(FibonaCCi)两种形式。

也有成为外部(Ex隹rna1)执行方式和内部(Interna1)执行方式。

(1)伽罗瓦方式(Interna1)X0X4X17! ! TepCount ,-Θ□□EF-Γ>4300000000Θ{3B0-*~*DaiaFtowW>)∙ι.x4.χ“(Ga1oisImp1ementation)Ga1ois方式特征数据的方向从左至右,反馈线路是从右至左。

其中XCo项(本原多项式里面的T'这一项)作为起始项。

按照本原多项式的指示确定异或门(XOR)在移位寄存器电路上的位置。

如上图所示XM。

因此Ga1ois方式也有人称作线内或模类型(M-型)1FSRo(2)斐波那契方式(Externa1)TapCountB*0;E3t3-⅛QEHIH30GHZHHDGIFSHpcivncrTMrig(M)-X14.X,>♦X n»1(Fibonacciimp1ementation)从图中我们可以看到Fibonacci方式的数学流向和反馈形式是恰好跟Ga1ois方式相反的,按照本原多项式,其中XCO这一项作为最后一项,这里需要一个XOR∏,将本原多项式中所给的taps来设定它的异或方式。

因此Fibonacci方式也被叫做线外或者简型(S-型)1FSR。

2)本原多项式本原多项式是近世代数中的一个概念,是唯一分解整环上满足所有系数的最大公因数为1的多项式。

本原多项式不等于零,与本原多项式相伴的多项式仍为本原多项式。

利用FPGA产生真随机噪声技术分析【摘要】在工程应用中,经常需要产生随机数,从而对实际的工程算法进行仿真验证,并且最好是在项目调试现场进行仿真输入从而对系统的整体性能进行测试,规避了常见的在上验证正常,在实际系统中工作不正常的问题,并且由于在Matlab中常见的伪随机数的算法均较为复杂,不利于实现.本文采用了一种基于FPGA中非门逻辑单元来实现真随机数的方式,利于嵌入到实际运行的工程中,从而进行现场验证.【关键词】真随机数;FPGA;非门环0 引言真随机数在密码学以及其它的学科中有着重要并广泛的应用,工程应用中的随机数常常用来产生实际环境中的本底噪声附加到理想信号上用于仿真实际情况下的输入信号.随机数分为伪随机数以及真随机数,通常在计算机系统中产生的随机数都是伪随机数,所谓的伪随机数通常是利用特定的函数来生成的,虽然在不同程度上逼近真随机数,但是它的致命的弱点是可追溯的.真随机数,顾名思义,即是真正的随机数,一般都是由物理过程产生的随机数,不能预先演算得到的,具有天然的不可破解的特性.产生真随机数的方式有很多,其中利用FPGA内部时钟抖动产生真随机数的方式已经广泛被使用[1-2],利用FPGA产生真随机数利用的是时钟的抖动,时钟抖动越大,真随机性能越好.本文中给出了一种经过实际验证的真随机数的产生方式,利用该种方式产生的随机数能够通过NIST推出的专用软件进行性能测试,之后才能够投入到实际的生产使用中.1 FPGA中真随机数产生产生真随机数的基础是利用真实存在的熵源,FPGA中的真实熵源是时钟JITTER,例如在D触发器时钟到达的时候,数据线处在跳变的过程中,导致不能满足其常规工作时所需要的建立保持时间的要求,输出的数据处于不稳定的随机状态,这是利用FPGA产生随机数的基本原理.在FPGA中产生真随机数的方式是利用三个非门组成的非门环,在将多个非门环进行异或操作,最终再进行时钟采样的方式,如图1所示.非门环本身运转起来之后,线上的数字在高速的进行跳变,在高电平以及低电平之间高速的切换,然后将其中一个非门的输出接到D触发器上,这样D触发器根据其工作时钟定期到非门环上取一个数据进行锁存,这样有一定概率出现取数时D触发器的数据线正好在进行跳变的过程中,这样其输出的数值就是真正意义上的随机数.但是,单个非门环的数据中真随机数的概率有限,还不能做到真正意义上的真随机数,必须要利用多个非门环进行联合工作,然后再进行全局的异或操作,只要有一个状态为真随机数,则最终输出为真随机数.如图1所示,该种方式产生的随机数为真随机数,非门环本身运转的速度很高,高低跳变的周期小于1ns,并且各个非门环之间的状态是完全独立的,故在进行异或操作时,如果非门环输出为1的个数为偶数时,则输出为0,个数为奇数时,输出为1;在进入D触发器时,由于采样时钟为低速时钟,在D 触发器采样时钟到来时,数据线上的输入如果发生跳变,则会产生真随机数,我们通过增加非门环的个数来增加该真随机数出现的概率.在工程应用中,可以控制不同的M,N,L值,从而获得不同效果的真随机数,N值主要控制单路的非门环之后的非门的个数,M值主要控制非门环的个数,M个非门环最终通过1个异或门从而得到1路真随机数输出,该路输出再经过L个非门之后再送入到一路D触发器中进行时钟采样,从而得到最终的输出.异或门是整个系统中的关键部位之一,它的作用是将所有的单路中的真随机数的因素汇总起来,在这里合成到一路中,其基本原理是真随机数和任何数据进行异或的结果都是真随机数,这种结构下要想得不是真随机数的情况只有所有路的输出都是非随机数,即每一路都能满足建立保持时间的要求,这个要求随着路数的增加,变得越来越难满足,概率越来越小.通过增加非门环的数量从而减少输出端非真随机数的出现概率,最终得到真随机数.2 真随机数测试3 结论利用FPGA产生真随机数能够达到较高的速度,且利于系统集成,并且能够进行位扩展,能够同时生成多个真随机数源,再通过并串转换再产生更高速率的真随机数,并且集成度高,能够在系统现场进行仿真输入,测试系统工作的稳定性,可以应用于工程实践中.【】[1]张聪,于忠臣.一种基于FPGA的真随机数发生器设计与实现[J].电子设计工程,2011,19(10):176-179.[2]霍文捷,刘政林,陈毅成,等.一种基于FPGA的真随机数生成器的设计[J].华中科技大学学报:自然科学版,2009,37(1):73-76.。

随机数发⽣器设计原理及实现随机数发⽣器设计原理及实现作者:不赖猴内核编程和密码学群:20264887随机数是密码学算法的基础,是现代加密体系中最重要的部分之⼀。

⼏乎所有的密码学算法都需要使⽤随机数。

那么是否真的存在真正的随机数呢?这个问题已经讨论了很多年,我们这⾥就不论述了,我们只需要知道量⼦⼒学已经证明在现实世界中随机数是真实存在的。

什么是随机数发⽣器?定义:⼀个随机数发⽣器就是⼀个产⽣数据流的设备,数据流中的每⼀位都是不可预测,偶然的。

但是从⼀定长度的数据流来看,它⼜符合某种分布。

从定义上看,随机数发⽣器具备以下三个属性:i.看起来具备随机性。

ii.不可预测性。

iii.不能被可靠的重复产⽣。

⼤多数编译器都已嵌⼊了随机数⽣成器,但是这些随机数发⽣器对密码来说⼏乎肯定是不安全的,甚⾄他们中的⼤部分产⽣的是⾮常差的随机数。

通常应⽤中对随机数有两个不同的并且不⼀定相容的要求:随机程度和不可预测程度。

随机程度:通常在产⽣的⼀系列声称是随机的数值时,我们关⼼的是这些数值在某种统计意义上是随机的。

即均匀分布和独⽴性。

不可预测程度:对于“真正的”随机序列,每个数与序列中的其他数都是统计独⽴的,因此不可预测。

然⽽,实际上我们很少能使⽤到真正的随机数;相反我们⽤到的都是由某种算法⽣成的。

这个时候,我们得防⽌攻击者从序列前边的元素预测出将来的元素。

随机数发⽣器的分类。

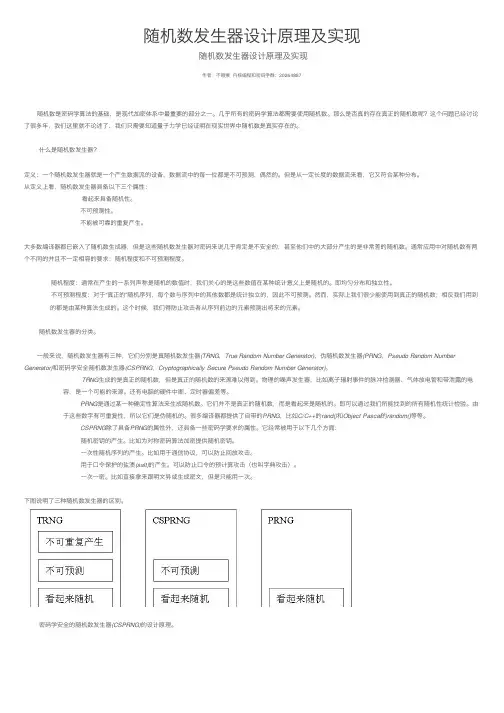

⼀般来说,随机数发⽣器有三种,它们分别是真随机数发⽣器(TRNG,True Random Number Generator)、伪随机数发⽣器(PRNG,Pseudo Random Number Generator)和密码学安全随机数发⽣器(CSPRNG,Cryptographically Secure Pseudo Random Number Generator)。

i.TRNG⽣成的是真正的随机数,但是真正的随机数的来源难以得到。

物理的噪声发⽣器,⽐如离⼦辐射事件的脉冲检测器、⽓体放电管和带泄露的电容,是⼀个可能的来源。

基于FPGA的高速高斯随机数发生器基于FPGA的高速高斯随机数发生器陆兴平,许拔(国防科学技术大学电子科学与工程学院湖南长沙410073)摘要:设计了一个基于FPGA的高速、高性能的高斯随机数发生器。

首先简要介绍了以前的一些算法并指出其不足之处。

然后阐明了本文的算法:对均匀随机数进行高效的变换以生成非常接近高斯分布的随机数,再依据中心极限定理把两个上述随机数相加得到高斯随机数。

算法所需的运算只有RAM的读操作与乘法、加法运算。

分析了算法的性能并与其他算法做了对比,证明了本文算法的高效性。

最后给出了FPGA实现的系统结构,并分析了所需的硬件资源。

关键词:正态分布;随机数发生器;FPGA;RAMHighspeed Gaussian Random Number Generator Impl emented with FPGALU Xingping,XU Ba(College of Electronic Science and Engineering, National University of DefenseTechnology, Changsha, 410073, China)Abstract:A highspeed gaussian random number generator implemented with FPGA is pr esented in this paper Several algorithms are briefly introduced and their sh ortcomings are pointed out Then algorithm is presented: firstly,uniformly distributed random numbers are effectively transformed to "GaussianLike" numbers,secondly,based on central limit theorem,each two of such "Gau ssianLike"numbers are added together to generate a gaussian sample A ll the operations needed are addition,multiplication and RAM reading The perfo rmance of the generator is excellent compared with others Finally the system s tructure in FPGA is givenKeywords:norm distribution;random number generator;FPGA;RAM高速地产生高斯随机数在仿真领域具有重要意义。

一种基于FPGA的真随机数发生芯片设计

余菲;赵杰

【期刊名称】《深圳职业技术学院学报》

【年(卷),期】2013(12)5

【摘要】为了解决电子系统对随机数越来越高的要求,利用FPGA芯片,结合PLL 技术和组合逻辑竞争冒险的原理,设计并实现了一款真随机发生芯片.由于避免使用震荡采样的方法,实验研究证明随机数发生器具有良好的随机特性及均匀性,芯片的功耗和寿命都得到了大幅提高.芯片利用门控时钟技术和可变频率的方法,降低了功耗,经过理论分析和仿真,该芯片达到了理想的随机性效果,有良好的应用价值.【总页数】4页(P3-6)

【作者】余菲;赵杰

【作者单位】深圳职业技术学院电子与通信工程学院,广东深圳518055;深圳职业技术学院电子与通信工程学院,广东深圳518055

【正文语种】中文

【中图分类】TN791

【相关文献】

1.一种基于FPGA的真随机数发生器设计与实现 [J], 张聪;于忠臣

2.一种基于FPGA实现的真随机数发生器 [J], 张润捷

3.基于 FPGA 一种真随机数生成器的设计和实现 [J], 吴飞;李艳萍

4.基于混沌系统的真随机数发生器芯片设计和实现 [J], 张亮;戎蒙恬;诸悦;吕永其

5.一种基于比较器共模模式的真随机数发生器设计方案 [J], 李桢;汪鹏君;程旭;李刚;张会红

因版权原因,仅展示原文概要,查看原文内容请购买。