CMOS宽带低噪放大器的研究与设计

- 格式:pdf

- 大小:1.26 MB

- 文档页数:71

CMOS低噪声放大器的设计与优化的开题报告一、选题背景CMOS低噪声放大器作为一种重要的电路结构,在各种电子系统中广泛应用。

在无线通信、雷达测量、成像等领域,CMOS低噪声放大器的性能对整个系统的性能影响至关重要。

因此,设计和优化高性能的CMOS低噪声放大器对于提高电子系统性能具有重要的意义。

二、选题意义本课题的研究涉及到多个学科领域,包括电路设计、模拟仿真、集成电路工艺等。

另外,开展该课题有以下几个方面的意义:1. CMOS低噪声放大器是现代电子技术中不可缺少的一个部分。

在很多应用领域中,CMOS低噪声放大器的性能影响到整个系统的性能。

因此,设计和优化CMOS低噪声放大器对于提高电子系统的性能至关重要。

2. 现有的CMOS低噪声放大器设计方法存在一定的缺陷,比如性能复杂或者难以实现等。

因此,本课题的研究可为该领域提供新的设计方法,从而提高CMOS低噪声放大器的性能。

3. CMOS低噪声放大器的研究还直接关系到一些领域的发展,比如通信领域、医学成像领域等。

因此,本课题的研究可以推动这些领域的发展。

三、研究内容本课题的研究内容包括以下几个方面:1. CMOS低噪声放大器的设计和优化。

包括设计各个环节的电路部分(如共源放大器,差动放大器,电流源等),在完成设计后进行仿真和优化。

并通过实际测量对设计的放大器进行验证。

2. CMOS低噪声放大器的模拟仿真。

通过仿真软件(如Cadence等)对放大器的性能进行模拟,包括增益、带宽、噪声等指标。

3. CMOS低噪声放大器的工艺实现。

在进行电路设计后,需要实际在实验室中通过CMOS工艺进行实现以进行实际测试。

四、研究方法本课题研究采用的方法主要包括仿真模拟和实验测试两个部分。

具体来讲,仿真模拟主要采用SPICE仿真软件,进行各个部分电路的仿真以及系统仿真。

实验测试主要通过实际电路设计,并在实验室中进行工艺实现和测试。

五、预期结果本课题的研究旨在设计并优化高性能的CMOS低噪声放大器,主要预期结果如下:1. 在各个环节的电路设计上,实现高性能的CMOS低噪声放大器。

CMOS低噪声放大器的分析与设计的开题报告一、选题背景随着现代电子技术的迅速发展,各种高性能、低功耗的电子设备被广泛应用到各个领域中。

而这些电子设备中,低噪声放大器(Low Noise Amplifier,LNA)则是至关重要的一个组成部分。

在通信领域中,LNA扮演着接收信号的第一道防线,因此其性能决定了整个系统的灵敏度、抗干扰能力和信噪比等重要指标。

而随着通信系统的发展,对LNA的性能要求也越来越高,要求其具备高增益、宽带、低噪声等优秀特性。

CMOS 技术因其具有低成本、低功耗、集成度高等优势,逐渐成为LNA研究领域的热点。

因此,LNA的分析与设计成为了当前重要的研究方向之一。

二、研究目的本课题旨在对CMOS低噪声放大器的原理和性能进行深入分析,设计出符合高性能LNA的设计需求的电路,并对其进行仿真与验证,最终得到性能优秀的LNA电路。

三、研究内容1. CMOS低噪声放大器的原理与基本结构2. LNA设计中常用的两种匹配方式——L型匹配和电感-电容匹配3. CMOS LNA的关键参数——增益、带宽、噪声系数等的计算与分析4. 所设计LNA电路的仿真与验证四、研究方法本课题首先进行对CMOS LNA的低噪声放大器原理、结构和匹配等分析,在此基础上,采用ADS软件设计出LNA电路,并通过仿真与验证对电路的性能进行评估和分析。

仿真时采用S 参数仿真,验证时则采用实验测试数据进行对比。

五、预期成果通过本次研究,预计可以得到以下成果:1. 对CMOS LNA的低噪声放大器原理、结构和匹配等方面有进一步的深入了解。

2. 成功设计出符合高性能LNA的需求的电路。

3. 对电路的实际性能进行评价,得出优秀的性能指标,并在仿真和实验中进行验证。

4. 通过实验的验证,为CMOS LNA的未来研究提供一定的参考。

六、论文结构1. 绪论:介绍论文的研究背景、意义和目的2. CMOS低噪声放大器的原理与设计3. LNA的匹配方式4. CMOS LNA的关键参数分析与计算5. LNA电路的仿真与验证6. 结束语:总结论文的研究内容和取得的成果,并对未来研究提出展望和建议。

摘要摘要随着信息化时代的到来,人们对通信的需求越来越高,为了提高通信效率、降低通信成本、加强通信安全性,超宽带技术(Ultra WideBand,UWB)应运而生。

而超宽带低噪声放大器作为无线接收机前端的重要模块,其性能直接影响着超宽带接受机的整体性能。

本文的研究对象为超宽带低噪声放大器。

在系统分析了近年来全球的超宽带低噪声放大器研究状况后,对超宽带低噪声放大器的实现原理进行了分析,并将目前主流的几种超宽带低噪声放大器拓扑结构进行了详细的分析以及对比,总结其优点以及缺点。

然后,在现有结构的基础上,提出一种新型的全对称自偏置低功耗的超宽带低噪声放大器电路,并进行设计仿真得到结果以及版图。

最后,在前文设计的基础上,又提出了一种结合人工神经网络工作特点,对超宽带低噪声放大器进行进一步优化的设计。

本次设计,主要结合了近年来超宽带低噪声放大器的主流设计架构,通过将可以实现带宽展宽的自偏置电阻负反馈匹配电路和用以实现良好阻抗匹配电感源极负反馈电路结合得到了电路的第一级结构即输入匹配级电路,在获得足够增益带宽的同时也满足了输入阻抗的匹配条件;而为了使低噪声放大器得到足够的增益尤其是高频增益,又进一步设计了第二级高频增益放大电路来使得总体电路的增益满足条件,并利用电感串联峰化技术将两级电路级联在一起以保证获得足够的工作带宽。

论文的第三章最后给出了本次超宽带低噪声放大器的仿真结果,其工作带宽为1GHz-10.6GHz,在此工作带宽内,电路增益为15.6-18dB,噪声系数NF为2.4dB-3.9dB,并实现了不错的输入阻抗匹配(S11<-10dB),而整个电路的功耗也较低,电路的总功耗仅仅为9.75mW。

同目前的同类研究对比,该电路的带宽、增益、噪声都有着一定的优势。

为了进一步提高超宽带低噪声放大器的性能,本文第四章提出了一种利用人工神经网络的记忆能力以及学习能力来对超宽带低噪声放大器性能进行优化的方法,并给出了实际案例。

CMOS宽带低噪声放大器的研究与设计的开题报告一、选题的背景和意义随着电子技术的快速发展和应用的广泛开展,宽带低噪声放大器成为了许多领域的核心技术之一,如通信、无线电、雷达、电视等。

特别是在5G通信时代,宽带低噪声放大器的性能和效率对整个通信系统的性能影响越来越大。

同时,随着射频电路的日渐复杂和小型化,CMOS技术作为一种高度集成的技术,更能满足这些需求。

二、研究内容本文的主要研究内容如下:1. 综述宽带低噪声放大器的基本原理和发展历程;2. 研究CMOS技术的特点和优势,并介绍CMOS宽带低噪声放大器的设计方法;3. 对CMOS宽带低噪声放大器的关键技术进行深入探讨,如抗干扰能力、线性度等;4. 实现设计并对其进行性能测试。

三、预期研究结果通过本文的研究,预期获得以下成果:1. 深入了解宽带低噪声放大器的基本原理和发展历程;2. 掌握CMOS宽带低噪声放大器的设计方法和关键技术;3. 利用EDA软件设计CMOS宽带低噪声放大器,并进行性能测试;4. 获得一种优化的CMOS宽带低噪声放大器,具有更高的抗干扰能力和更好的线性度。

四、研究方法本文采用文献综述和实验研究相结合的方法,首先通过文献综述和分析,深入了解宽带低噪声放大器的原理、设计方法以及关键技术。

然后,利用EDA软件设计并实现CMOS宽带低噪声放大器,并进行性能测试,评估设计的有效性和可行性。

五、进度安排第一学期:1. 阅读相关文献,了解宽带低噪声放大器的基本原理和发展历程;2. 学习CMOS技术的特点和优势,掌握CMOS宽带低噪声放大器的设计方法;3. 研究CMOS宽带低噪声放大器的关键技术。

第二学期:1. 利用EDA软件设计CMOS宽带低噪声放大器;2. 进行性能测试;3. 对测试结果进行分析和总结,撰写论文。

0.18μm CMOS无线传感器网络低噪声放大器设计及优化的开题报告【摘要】无线传感网络具有广泛的应用前景,其中低功耗,低噪声放大器是非常重要的组件。

本文提出了一种0.18μm CMOS无线传感器网络低噪声放大器设计及优化的方案。

首先,引入井垒侧壁电容的布局技术,减小了井垒面积,提高了单位面积的输入电容。

接着,通过优化源极偏压与集电极电阻的比例,实现了最佳的功率噪声平衡。

然后,设计了一个基于电压控制电阻的增益控制电路,实现了动态增益控制。

最后,利用TSMC 0.18μm工艺实现了该低噪声放大器,并测试了其性能。

实验结果表明,该低噪声放大器具有68dB的增益,1.2nV/√Hz的输入等效噪声,2.2μA 的静态功耗,以及20nA/mV的动态功耗。

该低噪声放大器的优化方案可以为无线传感器网络中的低功耗前置放大器设计提供参考。

【关键词】无线传感器网络;低噪声放大器;0.18μm CMOS工艺;动态增益控制。

【Abstract】Wireless sensor networks have broad application prospects, and low-power, low-noise amplifiers are critical components. This paper proposes a design and optimization scheme for a low-noise amplifier for 0.18μm CMOS wireless sensor networks. First, the layout technology of the sidewall capacitance of the well is introduced, which reduces the well area and increases the unit area input capacitance. Next, the optimal power noise balance is achieved by optimizing the ratio of the source-drain bias voltage and the collector resistor. Then, a gain control circuit based on voltage-controlled resistors is designed to achieve dynamic gain control. Finally, the low-noise amplifier was implemented using TSMC 0.18μm technology, and its performance was tested. The experimental results show that the low-noise amplifier has a gain of 68dB, an input equivalent noise of 1.2nV/√Hz, a static power consumption of 2.2μA, and a dynamic power consumption of 20nA/mV. The optimization scheme for the low-noise amplifier can provide a reference for the design of low-power preamplifiers in wireless sensor networks.【Keywords】Wireless sensor networks; Low-noise amplifier; 0.18μm CMOS technology; Dynamic gain control.。

基于CMOS工艺的超宽带低噪声放大器设计的开题报告一、研究背景和意义超宽带(Ultra-WideBand, UWB)是近年来新兴的无线通信技术,其传输带宽一般大于20 MHz,一般以极短脉冲时间间隔传输数据。

UWB技术具有以下优越性:(1)高速传输:UWB技术的传输速度可达到数Gbps,比传统的通信技术(如WLAN、Bluetooth)快上几个数量级。

(2)高保真度:UWB技术具有极好的时域特性,可提供准确可靠的位置和距离信息,适用于高精度定位和跟踪应用。

(3)抗干扰:UWB信号是低功率、短脉冲的宽带信号,干扰产生的能量很小,因此UWB信号不容易被其他无线设备干扰。

低噪声放大器(Low-Noise Amplifier,LNA)作为UWB系统中一项重要且难以实现的关键电路,承担着接收器前端的信号放大和噪声降低的任务。

在UWB系统中,LNA的主要目标是最大限度地提高接收器的灵敏度,并提高传输速率和特征值的信噪比。

此外,LNA还需要尽可能降低功耗、占用面积和成本,以提高整个系统的性能。

基于CMOS工艺的LNA已经成为了UWB通信领域的核心研究方向。

CMOS工艺具有功耗低、占用面积小、成本低等优点,可以满足UWB通信系统对电路设计的要求。

因此,设计一种基于CMOS工艺的超宽带LNA,具有促进新一代UWB无线通信技术发展的重要意义。

二、研究内容和方法本文旨在设计一种基于CMOS工艺的超宽带LNA,并分析其性能表现。

具体研究内容和方法如下:(1)分析UWB系统的要求和LNA的设计指标,建立设计模型。

(2)根据设计模型,利用Cadence软件设计出LNA电路,并进行仿真验证。

该电路包括放大器的结构、调制方式、传输媒介和双平衡混频器(Double Balanced Mixer,DBM)的设计。

(3)根据仿真结果优化LNA电路,进一步提高其性能表现,并进行特性分析。

(4)在TSMC 65nm工艺下进行电路实现,对电路进行测试评估,比较仿真结果和实验结果,验证设计结果的准确性和性能表现。

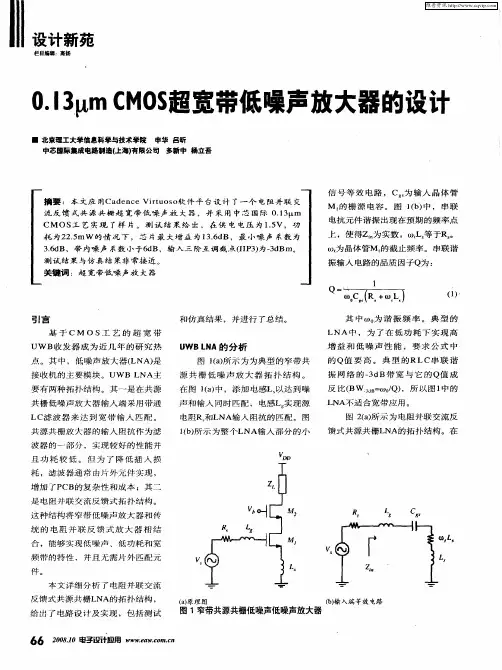

第1期王春华等:3.1~10.6GHzCMOS超宽带低噪声放大器设计75软件完成。

最终的各项仿真结果见图5~图9。

图5是通过原理图仿真得到的S参数¥21、Sll和S22曲线,图6在完成版图验证和寄生参数提取之后通过后仿真(Post—layoutSimulation)得到的相应的S参数结果。

对比图5和图6不难发现,在3.1~10.6GHz频带内,后仿真得到的放大器正向增益S2l较之前仿真结果减小了大约6dB,降到了14士0.4dB,增益曲线仍然具有比较好的平坦度。

后仿真得到的放大器增益有所下降,特别是高频端的增益下降得比较快,是因为后仿真考虑了电路版图中存在的寄生电容等影响,并且考虑到工艺中电感Q值不高这一实际情况,能比较真实的反映出电路的实际性能。

电路在3.1~10.6GHz频带内的输入反射系数S1l、输出反射系数¥22均小于.10dB。

电路的反向隔离性也比较好,整个频带内S12保持在.75dB以下。

由图7,后仿真的噪声系数最小值为3.2dB,3.1.10.6GHz范围内的平均值约为5.8dB。

在高频端的噪声性能有所恶化,这与电路结构有关,凶为共栅极结构本身噪声系数比较大11310本文之所以采用共栅极结构而没有采用LC无源滤波器结构【8】,是在实现超宽带的阻抗匹配和低噪声系数的折衷权衡。

后仿真结果显示电路P1dB压缩点为一37dBm。

图9是电路版图结果,芯片面积约为0.95mm2(1.3mmx0.73mm)。

本设计的工作电压为0.85V,电路的直流功耗为10mW。

表1给出了本设计与近年来部分采用0.18LLmRFCMOS工艺的超宽带低噪声放大器设计的比较。

由表1可知,文献8和文献15中电路的直流功耗虽然低于lOmW,但是同时它们的增益也较低,均为10dB左右。

文献[14】的设计功耗与本设计频率(GHz)图7噪声系数NF图8反向隔离S12图9放大器电路版图相当,但是增益也不高(峰值为12dB),且带内增益曲线平坦度也不理想。

CMOS宽带低噪声放大器的设计林丽芬;凌朝东;杨骁【期刊名称】《华侨大学学报(自然科学版)》【年(卷),期】2012(033)006【摘要】提出一种利用噪声抵消技术减小热噪声因子的互补金属氧化物半导体(CMOS)宽带低噪声放大器电路.它具有不平衡变换器可转换单端信号为差分信号,无需外接平衡-不平衡变换器,也未采用电感匹配技术,进一步减小了芯片的面积.该低噪声放大器基于TSMC0.18μm RF CMOS 1.8 V的工艺设计,仿真和验证采用Cadence公司的Spectre工具.结果表明:在150~600 MHz频带内的噪声系数为3.9dB,输入匹配参数S11小于-11.7 dB,输入3.阶截点IIP3为1.03 dBm.%In this paper, a wide-band complementary metal oxide semiconductor (CMOS) with low noise amplifier is presented, in which the noise-canceling technique is exploited to reduce the thermal noise of input transistor. The LNA combining with active balun can convert the single-ended signal into differential signals, so off-chip balun is not needed. Furthermore, the LNA is inductor-less, which can reduce chip area. The LNA is designed in TSMC 0.18μm RF CMOS process with 1. 8 V supply voltage, simulated and verified by using the Spectre tools of Candence. The simulation results show that the noise figure is less than 3. 9 dB, the input match is less than —11. 7 dB rang from 150 MHz to 600 MHz and IIP3 is 1. 03 dBm.【总页数】4页(P640-643)【作者】林丽芬;凌朝东;杨骁【作者单位】华侨大学信息科学与工程学院,福建361021;厦门市专用集成电路系统重点实验室,福建厦门361008;华侨大学信息科学与工程学院,福建361021;厦门市专用集成电路系统重点实验室,福建厦门361008;华侨大学信息科学与工程学院,福建361021;厦门市专用集成电路系统重点实验室,福建厦门361008【正文语种】中文【中图分类】TN492【相关文献】1.3~5GHz超宽带可变增益CMOS低噪声放大器的设计 [J], 陈昌明;彭烨;王建波2.3 GHz~5 GHz CMOS超宽带低噪声放大器分析与设计 [J], 唐江波3.3GHz~5 GHz CMOS超宽带低噪声放大器分析与设计 [J], 唐江波;4.CMOS超宽带低噪声放大器设计难点和要点分析 [J], 石磊;华梦琪;张惠国5.基于3.1~10.6 GHz CMOS超宽带低噪声放大器设计 [J], 赵小荣;范洪辉;朱明放;傅中君;黄海军;陈鉴富因版权原因,仅展示原文概要,查看原文内容请购买。

摘 要近年来,无线通信领域的进步以及高速数据通信的需求促使了通信技术的快速发展。

超宽带系统由于具有高吞吐率的优点,目前已成为非常受欢迎的通信技术。

超宽带低噪声放大器作为超宽带接收机的第一级系统,它性能的好坏直接对其后各个系统有较大的影响,因此对于超宽带低噪声放大器的研究很有必要。

在文中首先讲述了超宽带低噪声放大器的研究背景和近几年国内外的研究现状,其次简要阐述了低噪声放大器的主要性能参数,如噪声性能、输入阻抗匹配性能、线性度以及电路的增益性能,并且分析了三种无源器件的特性。

在第三章中主要总结了各类常见的低噪声放大器电路结构及其优缺点,另外,片上电感作为超宽带低噪声放大器设计中最常见的无源器件,对其模型的研究是很有意义的,因此,在本章中也提出了一种改进型单π模型。

通过对各种电路成果进行改进,设计了分别工作在4-18GHz和3-5GHz的高增益、低功耗的超宽带低噪声放大器电路。

主要的研究工作和成果为:(1) 针对片上螺旋电感提出了一种改进型单π集总参数等效电路模型。

提出的模型可以很好地模拟高频下的衬底耦合效应、趋肤效应以及邻近效应;利用R-L-C并联结构实现衬底的寄生耦合效应;使用二端口分析方法和拟线性函数方法可以很容易地得到参数值。

提出的片上电感的模型与HFSS软件仿真的结果相比,模型在0-20GHz时拟合度很高。

(2) 设计并研究了一种工作频带为4-18GHz的超宽带低噪声放大器,该放大器基于TSMC 0.18μm RF CMOS工艺,通过在放大级采用三谐振匹配网络技术不仅提高了电路的增益,而且拓宽了电路的频带。

此外,通过引入衬底偏置技术使电路的功耗下降。

利用ADS软件对电路进行优化仿真,并分析了温度以及工艺角对电路的影响。

最终的仿真结果表明,该放大器在室温25℃的状态下,工作带宽为4-18GHz,增益为15.95-18.73dB,增益的平坦度为2.78dB,噪声系数小于4.9dB,其中最小的噪声系数为3.22dB,电路的工作电压为0.9V,功耗仅为5.715mW,该放大器可广泛应用于低功耗、宽频带的射频集成电路中。

CMOS低噪声高增益放大器的设计及仿真分析本科学生毕业论文论文题目: CMOS低噪声高增益放大器的设计及仿真分析学院: 电子工程学院年级:专业: 集成电路设计与集成系统姓名:学号:指导教师:摘要运算放大器已经成为模拟电路设计中用途最广、最重要的部分。

运算放大器简称运放被广泛应用于无线电接收机的高频或中频前置放大级和一些高灵敏度电子设备中。

运放在电路中会产生噪声,在一些需要放大微弱信号的情况下,运放自身的噪声对有用信号的干扰可能会很严重,所以设计了一款低噪声系数、高功率增益、工作稳定性强、有足够带宽和较大动态范围的运算放大器电路。

MOS场效应晶体管会在电路中产生噪声,而且随着MOSFET尺寸的减小与信号幅度的降低,电路中低频噪声特性变得越来越重要。

论文首先分析运放电路中主要产生噪声的原因,然后结合基本噪声理论对电路中相应的元器件参数进行分析设计,然后针对电路的各项指标要求再对电路的元器件的参数进行调整。

运放输入级采用PMOS差分输入的结构,可以提高增益,也起到了抑制噪声的目的,输出级也采用共源共栅形式,可进一步抑制噪声。

通过对电路整体的噪声性能分析,优化了电路的噪声特性。

最后电路达到了设计的目标:增益带宽积大于60MHz、输入噪声功率谱密度在10MHz时小于35nV/rtHz、DC增益大于60dB、相位裕度大于45º。

关键词CMOS;运算放大器;低噪声;高增益;带宽IAbstractOperational amplifier (Op amp) is the most important and comprehensive element in CMOS analog integrated circuits. Operational amplifier is widely used in various types of high-frequency or intermediate frequency as a radio receiver pre-amplifier stage or the high sensitivity of electronic devices. MOS field effect transistor (MOSFET) circuit would bring noise under weak signal amplification. Noise interference may be very serious for useful signal in an op amp. Thus, it is very necessary that designing an op amp circuit with low noise, high gain, good stability, sufficient bandwidth and large dynamic range.MOS field effect transistor circuit would bring noise. With the MOSFET sizes decreasing and the signal amplitude decreasing, the low-frequency noise characteristics of the circuit are becoming increasingly important. This paper analyzes mainly noise sources of thee op ampcircuit firstly, then designs the corresponding component parameters of the circuit considering of the basic noise theory, and adjusts the parameters of certain components. The input stage of Op amp used PMOS differential input gain enhances direct telescopic structure to improve gain and suppress noise. The output stage is horizontal+output+stage to further suppress noise. Seen from the whole circuit noise performance,the noise characteristics are optimized. At last the simulated result also indicated that it reached the requirement of design: gain bandwidth product should be larger than 60dB, input noise power spectral density should be lower than 35nV/rtHz, DC gain shoud be higher than 60dB, phase margin should be larger than 45º.Key wordsCMOS; Operational amplifier; Low noise; High gain; BandwidthII目录摘要 ..................................................................... .. (I)Abstract ........................................................... .. (II)第一章绪论 ..................................................................... ................................................... 1 1.1 论文课题的价值及其意义 ..................................................................... ............... 1 1.2 运算放大器的发展过程及现状 ..................................................................... ........ 1 1.3 论文的章节安排 ..................................................................... . (2)第二章运算放大器的性能分析 ..................................................................... .................... 3 2.1 噪声 ..................................................................... .. (3)2.1.1 噪声类型 ..................................................................... .. (3)2.1.1.1 热噪声 ..................................................................... .. (3)2.1.1.2 散弹噪声 ..................................................................... . (4)2.1.1.3 闪烁噪声 ..................................................................... . (5)2.1.1.4 爆裂噪声 ..................................................................... . (5)2.1.2 MOS管中影响较大的噪声源 ....................................................................52.1.2.1 散弹噪声 ..................................................................... . (6)2.1.2.2 闪烁噪声 ..................................................................... . (6)2.1.2.3 沟道热噪声 ..................................................................... (6)2.1.3 噪声系数与计算噪声的基本方法 (7)2.1.3.1噪声系数 ..................................................................... .. (7)2.1.3.2噪声计算方法 ..................................................................... ..................... 7 2.2 开环增益 ..................................................................... .......................................... 8 2.3 开环带宽和增益带宽积 ..................................................................... ................... 8 2.4 输出摆幅 ..................................................................... .......................................... 9 2.5 相位裕度 ............................................................................................................... 9 2.6 DC功耗 ..................................................................... ............................................ 9 2.7 共模输入范围...................................................................... . (9)2.8 运放中各性能指标之间的关系 ..................................................................... ........ 9 2.9 两种常用结构CMOS放大器 ..................................................................... ........ 10 2.9.1 差分结构放大器 ..................................................................... ......................... 10 2.9.2 共源共栅结构放大器 ..................................................................... .. (13)第三章低噪声高增益运算放大器的设计 ..................................................................... ... 15 3.1 电路设计的指标 ..................................................................... ............................. 15 3.2 电路结构的设计 ..................................................................... .. (15)3.2.1 电路结构的确定 ..................................................................... (15)3.2.2 电路的噪声分析 ..................................................................... (17)3.2.3 电路的增益分析 ..................................................................... .................. 18 3.3 电路参数的确定 ..................................................................... ............................. 19 3.4 电路参数的验证 ..................................................................... .. (21)3.4.1 增益指标的验证 ..................................................................... (21)3.4.2 噪声指标的验证 ..................................................................... (22)第四章电路的仿真分析 ..................................................................... .............................. 23 4.1 理论值仿真分析 ..................................................................... .. (23)4.1.1 直流参数仿真 ..................................................................... . (23)4.1.2 交流小信号仿真 ..................................................................... .................. 24 4.2 电路的改进及仿真分析 ..................................................................... .. (25)4.2.1 M1管与M2管宽长比为20/1的仿真结果 (25)4.2.2 M1管与M2管宽长比为30/1的仿真结果 (26)4.2.3 增益提高的总结 ..................................................................... .................. 26 4.3 考虑噪声的仿真分析 ..................................................................... (27)4.3.1 噪声仿真 ..................................................................... (27)4.3.2 直流仿真 ..................................................................... (28)4.3.3 交流分析 ..................................................................... (28)4.3.4 与设计目标的比较 ..................................................................... .. (29)第五章版图的设计 ..................................................................... . (30)结论 ..................................................................... .. (33)参考文献 ..................................................................... . (34)致谢 ..................................................................... .. (36)CMOS低噪声高增益放大器的设计及仿真分析第一章绪论本章内容主要介绍运算放大器的发展过程,现阶段运算放大器的发展状况论文研究的意义与背景及论文的章节安排。

适用于无线局域网的CMOS低噪声放大器设计的开题报告I. 研究背景随着无线通信技术的普及和发展,对于无线局域网的需求也在不断增加。

其中,低噪声放大器在无线局域网中扮演着重要角色,能够实现信号的放大和强化,并保证信号质量和稳定性。

CMOS低噪声放大器在无线局域网中应用广泛,CMOS工艺具有成本低、功耗小、易于集成等优点,更加适合无线局域网应用。

因此,对于该领域的低噪声放大器的设计和优化具有重要意义。

II. 研究内容本课题旨在设计一种适用于无线局域网的CMOS低噪声放大器,主要研究内容如下:1. 低噪声放大器电路结构的设计和优化。

2. 低噪声放大器中的噪声源分析和优化,实现对噪声的最小化。

3. 低噪声放大器的参数优化,包括增益、线性度、带宽等等。

4. 基于所设计的低噪声放大器,进行实验和测试,验证其在无线局域网中的性能和可行性。

III. 研究意义与应用价值本研究可以为无线局域网领域提供一种更加优秀的低噪声放大器设计方法。

具体的意义和应用价值如下:1. 提高无线局域网系统的接收性能和稳定性。

2. 降低无线局域网系统成本,提高系统可靠性和可扩展性。

3. 推动无线通信技术的进一步发展和应用。

IV. 研究方法本研究采用以下方法进行实现:1. 基于CMOS工艺,设计和优化低噪声放大器电路结构。

2. 分析低噪声放大器中的噪声源,采用合适的方法和技术,实现对噪声的最小化。

3. 采用模拟电路仿真工具,模拟和优化低噪声放大器的参数,包括增益、线性度、带宽等。

4. 基于实验平台,进行实际的测试和验证。

V. 研究进度安排1. 前期调研:2022年7月 - 2022年8月2. 低噪声放大器电路结构的设计与优化:2022年9月 - 2022年11月3. 噪声源分析和优化:2022年12月 - 2023年1月4. 参数优化和仿真:2023年2月 - 2023年4月5. 实验和测试:2023年5月 - 2023年6月6. 论文撰写:2023年7月 - 2023年8月VI. 参考文献1. Molnar, T.G., et al. A 4-GHz low-noise amplifier in 130-nm CMOS using composite right/left-handed transmission line. IEEE J. Solid-State Circuits 41, 3087–3094 (2006).2. Gao, X., et al. A High-performance ultra-low-voltage and low-power RF front-end using 90-nm CMOS technology, IEEE Journal of Solid-State Circuits, 2017, 52(1): 30-45.3. Wang, K., et al. Design of a low noise amplifier with ultra-wideband filtering and strong blocking capability. Journal of Semiconductors, 2016, 37(8): 085004.4. Liu, Y., et al.5.8GHz CMOS low noise amplifier using shorted shunt feedback inductors. Electronics Letters, 2010, 46(12): 854-855.。

CMOS图像传感器设计中的低噪声放大器技术研究第一章引言CMOS图像传感器(CMOS image sensor,CIS)是当前数字图像采集和处理领域不可或缺的部件之一。

其通过集成一个或多个像素单元在芯片上制造出可控电荷转换器、电荷放大器、电荷储存器、选择电路和读出电路等硅微电子器件,实现了图像的采集和预处理功能。

低噪声放大器(Low Noise Amplifier,LNA)技术是CMOS图像传感器中提高信噪比和增强图像质量的关键之一。

第二章 CMOS图像传感器基础CMOS图像传感器是一种集成电路,其基础的材料是硅(Si)。

CMOS图像传感器由感光元件、信号读出电路和图像处理电路三部分组成,其中感光元件即图像传感器的核心。

硅的光敏特性是CMOS图像传感器感光元件的核心。

通常硅光电二极管(Si-PD)作为CMOS图像传感器的像素单元,因其响应速度快、能量转换效率高、噪声小等特点,在集成电路制造中被广泛应用。

第三章 CMOS图像传感器的噪声源CMOS图像传感器的噪声源主要包括热噪声、暗噪声和放大器噪声。

在光线较弱的情况下,暗噪声占据了主要噪声。

由于暗电流的引入,信号晕染现象时常发生,从而导致图像质量不佳。

传感器的放大器噪声主要由输入场效应晶体管的1/f噪声引起,且与传感器像素单元的数量成线性关系。

如何有效控制放大器噪声对CMOS图像传感器的影响,成为了CMOS图像传感器设计中关键的一环。

第四章 LNA的设计原理低噪声放大器(LNA)的主要设计原理包括最大增益、高传递效率、低输入噪声和高线性度等特点。

在CMOS图像传感器设计中,根据噪声建模理论,LNA的噪声系数(NF)成为LNA性能的主要衡量指标,同时为应对暗场噪声的影响,LNA的品质因数(Q-factor)也成为关键参数之一。

第五章 LNA设计实例本文结合设计实例,给出了一种CMOS图像传感器中采用CMOS差分放大器电路实现低噪声放大器的设计方案。

该方案采用电荷平衡的方案虽然可以控制在寄生电容下降的情况下极其低的输入噪声,但是残留的CMOS工艺变量如来自工艺偏差的器件转移特性偏差、背景电荷的脱附等,均会给LNA的设计带来影响,进而影响图像的质量。

学校代码: 10246学号: 042052031硕士学位论文CMOS宽带低噪声放大器的研究与设计院系:信息科学与工程学院专业:微电子学与固体电子学姓名:廖友春指导教师:唐长文闵昊完成日期:2007年7月4日目录目录 (I)摘要 (III)Abstract (IV)第一章概述 (1)1.1 数字电视调谐器系统 (1)1.2 低噪声放大器 (3)1.3 论文研究内容及贡献 (4)1.4论文组织结构 (5)参考文献 (5)第二章 MOS管噪声模型 (8)2.1 沟道电流热噪声 (8)2.2 栅噪声(准静态模型) (8)2.3 栅噪声与沟道噪声的相关性 (10)2.4 MOS器件非线性模型 (11)参考文献 (12)第三章窄带LNA电路设计与优化 (13)3.1 四种基本窄带LNA结构及噪声分析 (13)3.1.1 栅极匹配电阻型共源结构 (13)3.1.2 电阻反馈型共源结构 (14)3.1.3 共栅放大结构 (14)3.1.4 带源极电感反馈的共源结构 (15)3.2 源极电感反馈型LNA噪声分析 (16)3.2.1 简约模型(忽略感应栅噪声) (16)3.2.2 完整模型(包括感应栅噪声) (19)3.3 噪声优化 (23)3.3.1 固定增益求最小噪声系数 (25)3.3.2 固定功耗求最小噪声系数 (26)参考文献 (26)第四章噪声抵消LNA的设计方法 (28)4.1 噪声抵消原理 (28)4.2 噪声系数计算 (31)4.3 线性度分析 (32)4.4 各参数间的权衡关系 (32)参考文献 (33)第五章差分可变增益LNA设计 (34)5.1 电容交叉耦合LNA 基本结构 (34)5.2 输入端设计 (36)5.3 理想Balun特性 (36)5.4 负载设计 (39)5.5 电路参数计算 (40)5.5.1 增益 (40)5.5.2 噪声系数 (41)5.5.3 线性度 (42)5.6 可变增益LNA设计 (43)参考文献 (44)第六章芯片设计与测试实例 (46)6.1 噪声抵消宽带LNA设计 (46)6.1.1电路实现 (46)6.1.2 版图设计 (47)6.1.3 芯片实现及测试结果 (48)6.1.4 设计小结 (51)6.2 差分电容交叉耦合LNA (51)6.2.1 完整电路实现 (51)6.2.2 版图设计 (53)6.2.3 芯片实现及测试结果 (53)6.2.4 测试结果小结 (57)6.3 差分可变增益LNA (58)6.3.1 版图设计 (58)6.3.2 仿真(测试)结果 (59)参考文献 (60)第七章总结与展望 (62)7.1 成果总结 (62)7.2 展望与进一步研究 (62)参考文献 (63)致谢 (65)摘要无线通信技术和CMOS工艺的迅速发展使得越来越多的射频系统的单片集成成为可能。

应用于数字高清电视的射频电视调谐器就是其中之一。

随着全世界数字电视产业的飞速发展,电视调谐器系统的单片集成技术也得到了广泛的关注和深入的研究。

宽带低噪声放大器是电视调谐器的重要模块,其功能在于对接收到的射频信号进行预处理以得到适当幅度、高信噪比的输出信号,再由后级模块进行处理。

本文主要针对电视调谐器系统应用,研究宽带低噪声放大器的电路理论与实现方法,并详细分析了电路设计过程中的各种关键技术问题。

首先,从电视调谐器系统架构得出低噪声放大器的性能指标要求,初步分析了电路设计的难点是低噪声与高线性度等要求。

接着,对基本的MOS器件噪声模型进行分析,研究了CMOS器件中噪声的机理与模型,以及器件非线性的计算方法。

在此基础上,介绍了几种基本的窄带低噪声放大器电路结构,对各自的输入阻抗、噪声系数等参数进行了推导,为宽带低噪声放大器的分析和设计提供了初步的理论基础。

在此基础上,开始研究宽带低噪声放大器的设计与优化。

文中详细的介绍了一个采用噪声抵消技术的单端宽带低噪声放大器的设计方法,包括电路结构的选取,电路参数的分析与计算,器件参数的选取,电路性能的优化等。

总结了该电路的优缺点和设计极限。

更进一步的,介绍本文工作的重点,即全差分可变增益低噪声放大器的设计。

该电路基于电容交叉耦合共栅放大结构,提出了采用平衡-非平衡变压器(Balun)做直流通路对噪声的降低作用,以及采用NMOS管做负载对降低噪声系数、稳定直流工作点和提高线性度的好处。

理论分析和仿真显示电路设计指标优良。

最后,通过两次流片验证了电路的基本理论和设计方法和正确性。

详细介绍了芯片版图设计,封装,测试等环节需要考虑的细节。

测试结果显示芯片各项指标已经基本满足了电视调谐器的系统要求。

关键词:CMOS集成电路设计,电视调谐器,宽带低噪声放大器,噪声系数,线性度中图分类号:TN4.AbstractThe rapidly progress on wireless-communication and CMOS technology makes more and more radio frequency (RF) systems integrated in a System-On-a-Chip (SOC) to be possible. One of them is the RF TV tuner for digital High-Definition Television (HDTV). With the development of digital TV industry, the TV tuner system has gained widely attention and deeply research.Low-Noise Amplifier (LNA) is one of the most important modules in TV tuner system. The main function of a LNA is to pre-process the weak RF signal received by the antenna and increase the signal-to-noise ratio of the TV signal. This work focuses on the wide-band CMOS LNA design for TV tuner application, including circuit theory analysis, parameters calculation, chip implement and measurement.Firstly, a double-conversion low-IF TV tuner system architecture is presented, from which the LNA specification is derived. And the MOS transistor noise is researched, including the noise source and noise model, the non-linear device model and IIP3 calculation. Based on these theory analysis, several kinds of narrow-band LNA circuits are presented, the circuit topology, impedance, noise are deeply studied. The design, noise analysis and optimize of a source-degeneration narrow-band LNA are presented in detailed.Secondly, the wide-band LNA design and optimize methodology is presented. A wide-band single-ended LNA exploiting a noise-canceling technique is introduced. Including the circuit design, parameters calculate and devices choose.The fully-differential variable-gain LNA design is the principal part of this paper. The circuit bases on a capacitor-cross-coupled common-gate amplifier, a balun for DC path and noise-canceling is proposed. And two NMOS transistors are used as load to reduce noise figure, stabilize the DC output voltage and improve the linearity.Finally, the chip design and measurement results are presented. The chip achieves good performance in the required frequency band, and can be satisfy the TV tuner application.Key Words: CMOS IC Design, TV Tuner, Wide-Band Low-Noise Amplifier, Noise Figure, Linearity第一章概述1.1 数字电视调谐器系统随着信息通信和集成电路技术的不断进步,各种基于CMOS集成电路工艺的有线/无线收发系统都得到了迅猛的发展。

技术的不断革新使得一些传统的射频收发系统逐渐被淘汰,如电报、传呼机等;另外一些在不断的改进和完善,如手机,无线局域网等;而更多的新兴技术和领域正蓄势待发,将对各种传统模式和人们的日常生活带来巨大的变革。

这些新兴领域包括射频识别(RFID),超宽带网络(UWB),数字高清电视等。

数字高清电视是最近十年才出现的新兴产业。

相对于传统的模拟电视,数字电视具有画面清晰度高,抗干扰能力强,频谱利用率高等优点,得到了世界各国的广泛关注。

从1996年法国在全世界首先试播数字电视以来,各国均积极的制定了自己的发展战略,到2006年美国已经全部实现了电视信号的数字化传送,淘汰了传统的模拟电视。