根据逻辑函数求真值表

- 格式:docx

- 大小:36.74 KB

- 文档页数:2

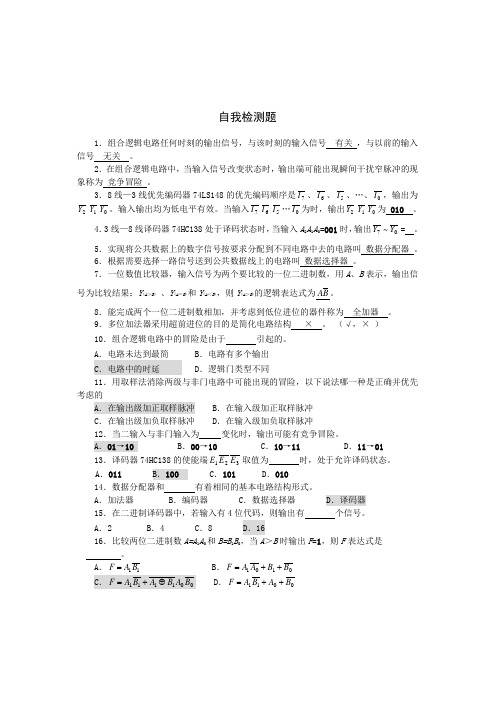

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

(√,× ) 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未达到最简 B .电路有多个输出C .电路中的时延D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→0113.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .01014.数据分配器和 有着相同的基本电路结构形式。

数字逻辑考试题答案及评分标准数字逻辑考试题答案及评分标准(一)一、填空(共20分,每空1分)1. 11.75 B.C2. 000101103. 高电平 低电平 高阻状态 6. AB+AC 7. 2n 10. 0100 11. JK12. S=2N13. 原函数 反函数二、选择题(共10分,每题1分) 1. B 3. C 4. A 5. A 6. B 9. D 10. C三、简答题(共15分)1. n 位无符号二进制数的取值最小可以是全为0,最大是全为1,对应的十进制数的范围是0~2n-1。

最大的2位十进制数为99,由于27>99>26,所以表示一个最大2位十进制数至少需要7位二进制数。

3.(1)0110010100100001 (2)010*********.00000011 四、计算(共20分)1. (1)AB AB ABC A BC AB =+=+)( (3分) (2)B A B A B A =+))(( (3分)2.(3分)∑=++++++++=++++=+++++)14,12,11,9,6,5,4,1()()()(5414614129111__________m m m m m m m m m m C B A D BC D AB D C B CD B A C B A D B C A D C B D CD B A (1分)D B A D C A D B Y ++= (1分)3. (5分)CA D C D ABC B B C A B AD C D A C B B A B A C B D B C A ABBC BD AC AB BC BD AC +++=+++++++=+++++=⋅+⋅=⋅⋅⋅))(())((__________________________________________________________________________________________4. 模为6(4分) 五、1.当没有车辆行驶时,道路的状态设为0,有车辆行驶时,道路的状态为1;通道允许行驶时的状态设为1,不允许行驶时的状态设为0。

三输入变量判奇电路的真值表及表达式摘要:以三输入判奇为例,通过对其输出函数表达式的形式变换,分别采用多种门电路及译码器、数据选择器等74 系列器件进行电路设计,给出了7 种电路实现形式,并分析了各种电路实现的优缺点。

此例说明了组合逻辑电路设计的灵活性及电路实现的多样性,所采用的设计方法对其他组合逻辑电路设计具有一定的启发与指导意义。

目前数字基础课程的实验内容包括验证性实验、综合性实验、设计性实验三部分,每一部分实验内容安排的侧重点不同。

比如设计性实验的关键是设计,要求学生依据设计要求,设计合理的实验电路,并选择器件、安装调试完成实验内容。

从教学实践来看,多数学生能够顺利完成实验要求,但解决问题的思路单一,设计过程灵活性差,不注意创新思维能力的锻炼。

这就要求教师在合理安排实验内容的同时,不断通过各种途径,引导学生拓宽知识面,创新思维方式,对待同一问题,积极探索多种解决问题的路径。

组合逻辑电路的设计多种多样,笔者选择一种奇偶校验电路实现进行详细阐述。

奇偶校验电路在组合逻辑电路的分析与设计中具有一定的典型性和实用性,熟悉判奇电路的逻辑功能及电路实现,有助于加深对组合逻辑电路的理解与掌握。

以判奇电路实现为例,分别讨论了用门电路、译码器、数据选择器的多种实现方案,用实例说明了组合逻辑电路设计的灵活性与多样性。

1 三输入变量判奇电路的真值表及表达式对于三输入变量的判奇问题,设其输入变量分别用A、B、C 表示,输出函数用F 表示。

当输入变量的取值组合中有奇数个1 时,输出函数值为1;当输入变量的取值组合中1 的个数为偶数时,输出函数值为0,依据这种逻辑关系可列写出三输入变量判奇电路的真值表如表1 所示。

表1 三输入判奇电路的真值表由真值表1 可见,有4 组输入变量取值组合使输出函数值为1,即分别为。

所以,三输入变量判奇逻辑问题的输出函数表达式为:2 采用门电路实现三输入变量判奇电路门电路实现三输入变量判奇电路的方法有很多,文中列举如下。

逻辑函数的五种描述方法

逻辑函数的五种描述方法包括:

1.真值表:逻辑函数的真值表是一种描述逻辑函数的方法,它列出逻辑函数的输入和

输出变量的所有可能组合,以及对应的函数值。

2.表达式:逻辑函数可以用布尔代数表达式来描述,例如和、差、积、商、最大项、

最小项等。

这些表达式可以用来表示逻辑函数,并且可以方便地用于逻辑函数的计算和化简。

3.逻辑图:逻辑图是一种描述逻辑函数的方法,它用电路元件和连线来表示逻辑函数。

在逻辑图中,每个电路元件代表一个逻辑运算,每个连线代表一个逻辑变量。

4.卡诺图:卡诺图是一种描述逻辑函数的方法,它用方格来表示逻辑函数。

在卡诺图

中,每个方格代表一个逻辑函数,每个方格中的涂色表示逻辑函数的取值。

5.表格:逻辑函数也可以用表格来描述,表格列出逻辑函数的输入和输出变量的所有

可能组合,以及对应的函数值。

这些描述方法可以互相转换,并且在实际应用中根据需要选择合适的方法。

第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是一个三变量的奇偶检测电路,当输入变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())真值表:由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对十进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG 1、TG 3、TG 5导通,TG 2、TG 4、TG 6关断。

3232211 , ,A A Y A Y A Y ⊕===, 4324A A A Y ++=(2)COMP=0、Z=0时,Y 1=A 1, Y 2=A 2, Y 3=A 3, Y 4=A 4。

、COMP=1、Z=0时的真值表COMP=0、Z=0的真值表从略。

[题]用与非门设1,输入为其他状态时输出为0。

填空题1.将十进制数10转换成二进制数为____。

2.D 触发器的特性方程是____。

3.静态RAM 是靠____存储信息,动态RAM 是靠 存储信息。

4.描述时序逻辑电路逻辑功能的方程有____方程、_____方程和____方程。

5.逻辑函数的表达形式主要有_____、______、 、______四种。

6.逻辑函数F=B A B A 的对偶函数F ′=______。

7.存储4位二进制信息,要_____个触发器。

8.对于T 触发器,若初态为0,欲使次态为0,则输入T=____。

9.对9个输入信号进行编码,至少需要_____位二进制编码。

1.十进制数15转换为二进制是____。

2.只读存储器ROM 在掉电后所存数据将____。

3.对于JK 触发器,若J=K=1,则可完成的逻辑功能是_____。

4.描述时序逻辑电路逻辑功能的方程有____方程、_____方程和____方程。

5.组合逻辑电路的输出在任何时刻都只取决于同一时刻的_____,而与电路_____的状态无关。

6.RAM 根据所采用的存储单元工作原理不同,可以分为_____存储器和_____存储器。

7.集成单稳态触发器按工作特性可分为____和____两种类型。

8..对于T 触发器,若初态为1,欲使次态为0,则输入T=____。

9.JK 触发器特征方程为_____。

10.对4个输入信号进行编码,至少需要_____位二进制数码。

判断题1.数字电路中的1比0大。

2.当决定某个事件的全部条件都具备时,这件事才会发生。

这种关系称为与关系。

3.十进制数10和十六进制数10一样大。

4.优先编码器的输入信号是相互排斥的,不允多个输入信号同时有效。

5.时序电路由组合电路和存储电路两部分组成。

1.逻辑变量的取值,1比0大。

2.八进制数17比十进制17小。

3.若两个函数具有不同的真值表,则两个逻辑函数必然不相等。

4.时序电路无记忆功能,组合逻辑电路有记忆功能。

第2章习题解答题2-1 用真值表证明下列恒等式。

(1) ()A B C AB AC ⊕=⊕(2) ()()()()()A B A C B C A B A C ''+++=++ (3) ()0A B A B A B '⊕==⊕⊕解:将输入变量所有的取值逐一代入公式两边计算,然后将计算结果列成真值表。

如果两边的真值表相同,则等式成立。

(1)证明()A B C AB AC ⊕=⊕表JT2-1(2) 证明 ()()()()()A B A C B C A B A C ''+++=++表JT2-2(3) 证明()0A B A B A B '⊕==⊕⊕表JT2-3题2-2 证明下列逻辑等式(证明方法不限)。

(1)()()BC D D B C AD B B D '''++++=+(2) A C A B BC A C D A BC ''''''''+++=+(3) ()ABCD A B C D AB BC CD A D '''''''''+=+++ (4) ()()()A C B D B D AB BC '''+++=+解:在实际应用中,除非逻辑式很简单、而且逻辑变量数很少的情况下,一般不宜用列真值表的方法。

对多变量、复杂的逻辑等式、通常采用公式推演或公式推演与画卡诺图相结合的方法去证明。

如果有条件使用Multisim 等EDA 软件进行证明,则更简单、便捷。

(1)()()()()BC D D B C AD B BC D B C AD B BC D AB D AC D BB BC B D'''''++++=++++''''=+++++=+(2)()A C A B BC A C D A C A B BC A BC BC A BC ''''''''''''''+++=++=+=+(3)()()()()()()()()()()()AB BC CD A D AB BC CD A D A B B C C D A D A B A C BC AC AD C D ABCD A B C D '''''''''''''+++=''''''''''=++++=++++''''=+ (4)()()()()()()A C B D B D A C B BD BD A C B AB BC ''''''+++=+++=+=+题2-3已知逻辑函数Y 1和Y 2的真值表如表JT2-4(a )、(b )所示,试写出Y 1和Y 2的逻辑函数式。

列出逻辑函数y=ab+bc的真值表逻辑函数 y=ab+bc 的真值表如下:a |b |c |y---- |---- |---- |----0 |0 |0 |00 |0 |1 |00 |1 |0 |00 |1 |1 |11 |0 |0 |01 |0 |1 |11 |1 |0 |11 |1 |1 |1根据逻辑函数y=ab+bc的真值表,当条件a,b,c的值同时为0时,y的值也为0,也就是a、b、c三个条件中有一个条件不满足时,整体的真值就为假,即y=0;当a、b、c三个条件都满足时,y的值为1,也就是a、b、c三个条件同时满足时,整体真值为真,即y=1。

可见,逻辑函数 y=ab+bc 的真值表是以 “与” 和 “或” 的逻辑关系来判断整体结果的真假,是一个用来判断某一事物是否满足数学逻辑条件的判断表达式。

在日常生活和工作中,逻辑函数 y=ab+bc 的真值表用来解决事物是否真实存在的问题,如对于某些事物是否存在时,就可以判断某个条件是否满足,如果这个条件满足,就表明事物是真实存在的,如果条件不满足,就表明事物是不存在的。

例如,在判断某个句子是否满足这三个条件,如果句子满足这三个条件就表示它是正确的,而如果不满足,就表示它是错误的;又比如在判断某一事物是否特定条件,如果满足就表明它满足这个特定的条件,而如果不满足,则表明它是不满足这个特定的条件。

另外,逻辑函数 y=ab+bc 的真值表还可以用来判断设计的思路是否正确,当某个事物满足a,b,c三个条件的时候,我们就可以根据逻辑函数 y=ab+bc 的真值表来判断这个设计思路是否正确。

在自然和社会科学中,逻辑函数 y=ab+bc 的真值表也可以用来用来判断某一类事物是否存在、是否存在等,因此,逻辑函数 y=ab+bc 的真值表在现实生活中具有非常重要的作用。

在函数f=ab+bc的真值表

函数f(a,b,c) = ab + bc 的真值表如下:

真值表是一种常用的方法来检验一个逻辑函数的正确性,通过真值表可以清楚地看出函数的输入和输出之间的关系。

需要注意的是,这个真值表只是这个具体函数的一种情况,如果参数类型不同或者有其它不同,那么真值表也会有所不同。

在这个真值表中,每一行都对应了一组参数的输入和函数的输出。

每一列都对应了一个参数的不同值,在这个例子中,a,b,c都是布尔类型,只有0和1两种取值,所以真值表中有8组数据。

从真值表中可以看出,当a=1,b=1,c=1时,函数f(a,b,c)的值为2,这是因为a和b都为1,b和c都为1,所以ab+bc=11+11=2。

而当a=0,b=0,c=0时,函数f(a,b,c)的值为0,这是因为a和b都为0,b和c都为0,所以ab+bc=00+00=0。

真值表可以帮助我们确定函数的输入输出

对于函数f(a,b,c) = ab + bc, 我们可以通过真值表来检验它是否正确。

当我们有了一个真值表之后,可以通过手工代入参数来验证函数的输出是否正确。

如果函数是由多个子函数组成的复合函数,我们可以通过构建每个子函数的真值表,然后组合起来构建复合函数的真值表来检验函数的正确性。

此外,真值表还可以用来比较两个不同函数的行为。

如果两个函数的真值表相同,。

根据逻辑函数求真值表

**真值表**

| A | B | C | Z |

|--:|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

在逻辑中,一个真值表是用来表示一组逻辑变量(A,B,C)之间的联系并阐明了它们之间各种不同可能输入和输出值的情况下即关系的表示法。

上述真值表指出,在三个输入变量(A,B,C)条件下,有八种可能输入值组合,其输出Z的真值情

况如上表格所示。

从上表可以看出,在不同的输入变量处理下,Z的输出值基本

为两种情况:Z=1和Z=0,这对建立起相应的逻辑函数很有帮助。

我们还可以从表格中比较其他输入变量之间的联系,通常情况下,当A为1,B为0,C为1时,Z=1,而当A为0,B为

1,C为1时,Z=0。

真值表可以帮助我们现实生活中的决策过程,使决策变得更加客观和精确。

例如,当一个商家有以下三个因素可供选择:时间,质量和价格,以最优的方式决定哪些因素更重要,而哪些是可以忽略的可以使用真值表帮助我们实现。

总的来说,真值表是一种有效的分析工具,可以用来全面分析和识别问题。

它可以帮助我们准确判断问题,消除它们之间的不确定性,并有助于实现最优决策。