三输入多数表决器版图设计

- 格式:docx

- 大小:1.28 MB

- 文档页数:9

实验十九三人多数表决电路的设计欧阳家百(2021.03.07)一、设计目的1、掌握用门电路设计组合逻辑电路的方法。

2、掌握用中规模集成组合逻辑芯片设计组合逻辑电路的方法。

3、要求同学们能够根据给定的题目,用几种方法设计电路。

二、设计要求1、用三种方法设计三人多数表决电路。

2、分析各种方法的优点和缺点。

3、思考四人多数表决电路的设计方法。

要求用三种方法设计一个三人多数表决电路。

要求自拟实验步骤,用所给芯片实现电路。

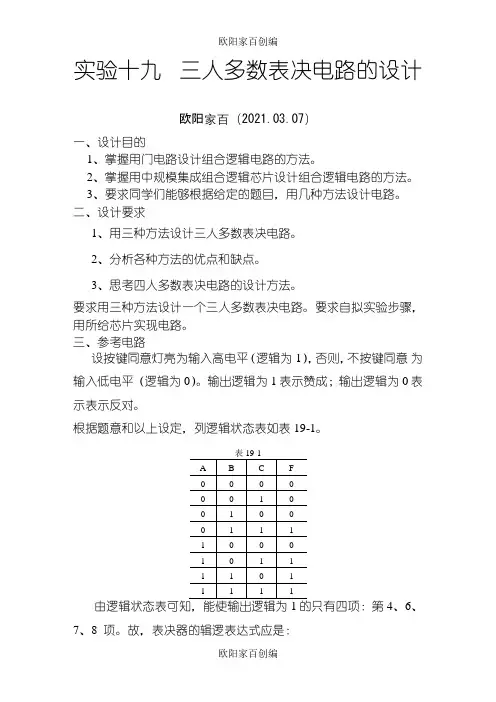

三、参考电路设按键同意灯亮为输入高电平(逻辑为1),否则,不按键同意为输入低电平(逻辑为0)。

输出逻辑为1表示赞成;输出逻辑为0表示表示反对。

根据题意和以上设定,列逻辑状态表如表19-1。

4、6、7、8 项。

故,表决器的辑逻表达式应是:从化简后的逻辑表达式可知,前一项括号中表达的是一个异或门关系。

因此,作逻辑图如下。

经常用来设计组合逻辑电路的MSI芯片主要是:译码器和数据选择器。

设计步骤前几步同上,写出的逻辑函数表达式可以不化简,直接用最小项之和的形式,然后根据题目要求选择合适的器件,并图19—1 三人表决电路且画出原理图实现。

四、实验设备与器件本实验的设备和器件如下:实验设备:数字逻辑实验箱,逻辑笔,万用表及工具;实验器件:74LS00、74LS20、74LS138、74LS153等。

五、实验报告要求1、写出具体设计步骤,画出实验线路。

2、根据实验结果分析各种设计方法的优点及使用场合。

实验二十序列脉冲检测器的设计一、设计目的1、学习时序逻辑电路的设计与调试方法。

2、了解序列脉冲发生器和序列脉冲检测器的功能区别及设计方法。

二、设计要求及技术指标1、设计一个序列脉冲检测器,当连续输入信号110时,该电路输出为1,否则输出为0。

2、确定合理的总体方案。

对各种方案进行比较,以电路的先进性、结构的繁简、成本的高低及制作的难易等方面作综合比较。

自拟设计步骤,写出设计过程,选择合适的芯片,完成画出电路图。

三输入或门版图设计.1 绪论1.1 设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S:电路图网表* SPICE netlist written by S-Edit Win32 7.03* Written on Jul 5, 2013 at 10:20:01.include "C:\Users\Administrator\Desktop\tanner\TSpice70\models\ml2_125.md" Vdd Vdd Gnd 5V A A Gnd PULSE (0 5 0 10n 10n 50n 100n)VB B Gnd PULSE (0 5 0 10n 10n 50n 100n)VC C Gnd PULSE (0 5 0 10n 10n 50n 100n).tran/op 10n 200n method=bdf.print tran v(A) v(B) v(C) v(Y)* Waveform probing commands*.probe.options probefilename="D:\xuexi\LJB\dianlu\Module0.dat"+probesdbfile="C:\Users\Administrator\Desktop\LJB\dianlu\1003040101l u.sdb"+ probetopmodule="Module0".include C:\Users\Administrator\Desktop\tanner\TSpice70\models\ml2_125.md* Main circuit: Module0M1 N11 B Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M2 N11 A Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M3 N11 C Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M4 Y N11 Gnd GndNMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M5 N18 A Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM6 N17 B N18 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM7 N11 C N17 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM8 Y N11 Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u* End of main circuit: Module0word教育资料达到当天最大量API KEY 超过次数限制。

制作与测试(二)单击此处添加标题完整电路图完成电路图后还有哪些步骤呢?起点1111功能要求逻辑电路完整电路电路布局元器件检查与成型(2)(3)手工焊接(5)元器件插装(4)电路检查(6)3.安装实际电路集成电路选择(1)由电路图可知,本电路需要3个二输入与非门,74LS00为四2输入与非门,内含4个独立的二输入与非门,因此,选择一块74LS00集成电路。

(1)集成电路选择一块74LS10集成电路。

1012459368211312(2)电路布局走线、跳线、元件卧式安装的方向统一(水平或垂直);走线、元件和跳线不能相交;整体布局成矩形,元件疏密一致,尽量紧凑;大致按照原理图放置元器件;电源线和信号线引出合理(一般电源在左侧,输出在右侧)。

14253(3)元器件检查与成型(4)元器件插装(5)手工焊接(6)电路检查(1)集成电路选择(5)手工焊接(3)元器件检查与成型(6)电路检查(2)电路布局(4)元器件插装起点1111功能要求逻辑电路完整电路实际电路4.测试逻辑功能(1)接通+5V电源(集成电路7引脚接电源负极,14引脚接电源正极);(2)按真值表设置按键状态,测出相应的输出逻辑电平,并记录在表格中(输入按键SB1、SB2、SB3按下为1状态,未按下为0状态;输出发光二极管亮为1状态,灭为0状态)。

三人表决器功能测试结果记录表功能:输入A 、B 、C 中,若两个或三个输入端加高电平,输出为高电平;否则输出为0。

输入输出AB C Y 00010111000001010011100101110111起点1111功能要求逻辑电路完整电路实际电路逻辑功能谢谢!。

集成电路版图设计课程设计报告课题名称:三输入多数表决器姓名:XXXX学号: 21111111 班级:电子科学与技术班1.概述集成电路是一种微型电子器件或部件。

它是采用一定的工艺,把一个电路中所需的晶体管等有源器件和电阻、电容等无源器件及布线互连在一起,制作在一小块半导体晶片上,封装在一个管壳内,执行特定电路或系统功能的微型结构;这样,整个电路的体积大大缩小,且引出线和接点的数目也可控制、大为减少,从而使电子元件向着微小型化、低功耗和高可靠性方面迈进一大步。

目前,集成电路经历了小规模集成、中规模集成、大规模集成和超大规模集成。

单个芯片上已经可以制作包含臣大数量晶体管的、完整的数字系统。

在整个集成电路设计过程中,版图设计是其中重要的一环。

它是把每个原件的电路表示转换成集合表示,同时,元件间连接的线也被转换成几何连线图形。

对于复杂的版图设计,一般把版图设计划分成若干个子版图进行设计,对每个子版图进行合理的规划和布图,子版图之间进行优化连线、合理布局,使其大小和功能都符合要求。

版图设计有特定的规则,这些规则是集成电路制造厂家根据自己的工艺特点而制定的。

不同的工艺,有不同的设计规则。

设计者只有得到了厂家提供的规则以后,才能开始设计。

在版图设计过程中,要进行定期的检查,避免错误的积累而导致难以修改。

2.设计要求1) .设计一个三输入的多数表决器的版图。

2).分析三输入多数表决器的功能及逻辑关系。

3).用与非门的形式构建该表决器的电路图。

4).利用EDA工具PDT画出其相应版图。

5).利用几何设计规则文件进行在线DRC验证并修改版图。

3.电路分析根据三输入多数表决器的功能要求设计如果同意则输入1不同意输入0三输入表决器功能为有两个或者两个以上人同意则,则输出1,否者输出0,其真值表如下:化简真值表得逻辑表达式表示并化简为:Out=A BC + A B C + AB C +ABC=AB+BC+AC= AB BC AC这样可以用到三个两输入与非门和一个四输入与非门,达到逻辑功能和晶体管数量最小化的效果,节约了版图资源,减小了复杂程度。

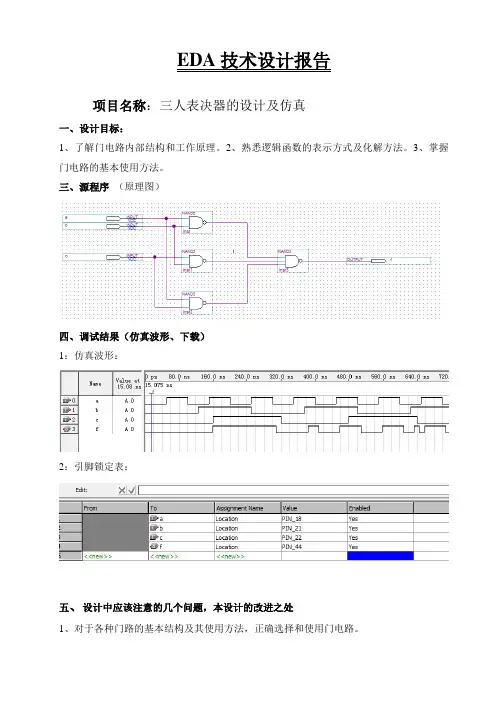

EDA技术设计报告

项目名称:三人表决器的设计及仿真

一、设计目标:

1、了解门电路内部结构和工作原理。

2、熟悉逻辑函数的表示方式及化解方法。

3、掌握门电路的基本使用方法。

三、源程序(原理图)

四、调试结果(仿真波形、下载)

1:仿真波形:

2:引脚锁定表:

五、设计中应该注意的几个问题,本设计的改进之处

1、对于各种门路的基本结构及其使用方法,正确选择和使用门电路。

2、设计时注意怎样才能实现三人表决,源程序的设计一定要有理有据。

3、引脚分配时注意分清设计的源程序中哪些是输入端,哪些是输出端,根据引脚对照表确定引脚分配。

参考文献:。

Quartus2原理图输入法(上机实训)原理图输入法设计三人表决器实验一:Quartus II 7.2 启动___________•方法一、直接双击桌聞上的图标Lawd,可以打开Quartus IT 7.2 :•方法二、执行:【开始【程序】一(Alteral - [Quartus II 7. 2] - (Quartus II 7. 2 TalkBack Install]菜单命令,可N打开软件°•启动软件后,甘你的电脑没有Internet互联网,会岀现提示,提示你没有连接到Altera的官方网站*将无法获得更新的资潞f点击瞪确定d继续,因为这不影响软件的正常使用・二Quartus II 7.2 软件界面"Lx -gggp isfcirn 4詰4仝:- • ”ZL」J 土Quartus II 7.2软件的狀认启动界面如下图所示,由标题栏、菜单栏、常用工具栏、整源管理窗口* 程序编译或仿真运行状态的显示窗口、程序編译或仿頁的结果显示窗口和工程編辑T作区组成・三:Quartus II 7.2软件使用:_. ^I C E SC:"' S■--仕n_1.新建项目工程使用Quartusl门.2设计一个数字逻辑电路,并用时序波形图对电路的功能进行仿真,同时还可以将设计正确的电路下载到可编程的逻辑器件(CTLD、FPGA)中.因软件在完成密个设计、编译.仿真和下载等这些丁.作过程中,会有很多相芸的文件产生,刃了便于管理这些设计文件・我们在设计电踣Zllih先骡建立一个项口工程(NewProject)・幷设瓷好这个工稗能正常工作的相关条件和坏境・建立工程的方法和步骤如下:(1)先建一个文件夹。

就在电脑本地硬盘找个地方建一个用于保存下一步工作中要产生的工程项目的文件夹.注意,文件夹的命名及其保存的路径中不能育中文字符.(2)再开始建立新项目工程・方法如右图点击:[File]菜单,选择下拉列衰中的[New Project Wizard...J 令・打开建立新项目工程的向导对话框。

集成电路版图设计

课程设计报告

课题名称:三输入多数表决器

姓名: XXXX 学号: 21111111 班级:电子科学与技术班

1.概述

集成电路是一种微型电子器件或部件。

它是采用一定的工艺,把一个电路中所需的晶体管等有源器件和电阻、电容等无源器件及布线互连在一起,制作在一小块半导体晶片上,封装在一个管壳内,执行特定电路或系统功能的微型结构;这样,整个电路的体积大大缩小,且引出线和接点的数目也可控制、大为减少,从而使电子元件向着微小型化、低功耗和高可靠性方面迈进一大步。

目前,集成电路经历了小规模集成、中规模集成、大规模集成和超大规模集成。

单个芯片上已经可以制作包含臣大数量晶体管的、完整的数字系统。

在整个集成电路设计过程中,版图设计是其中重要的一环。

它是把每个原件的电路表示转换成集合表示,同时,元件间连接的线也被转换成几何连线图形。

对于复杂的版图设计,一般把版图设计划分成若干个子版图进行设计,对每个子版图进行合理的规划和布图,子版图之间进行优化连线、合理布局,使其大小和功能都符合要求。

版图设计有特定的规则,这些规则是集成电路制造厂家根据自己的工艺特点而制定的。

不同的工艺,有不同的设计规则。

设计者只有得到了厂家提供的规则以后,才能开始设计。

在版图设计过程中,要进行定期的检查,避免错误的积累而导致难以修改。

2.设计要求

1) .设计一个三输入的多数表决器的版图。

2).分析三输入多数表决器的功能及逻辑关系。

3).用与非门的形式构建该表决器的电路图。

4).利用EDA工具PDT画出其相应版图。

5).利用几何设计规则文件进行在线DRC验证并修改版图。

3.电路分析

根据三输入多数表决器的功能要求设计如果同意则输入1不同意输入0三输入表决器功能为有两个或者两个以上人同意则,则输出1,否者输出0,其真值表如下:

化简真值表得逻辑表达式表示并化简为:

Out=A BC + A B C + AB C +ABC

=AB+BC+AC

= AB BC AC

这样可以用到三个两输入与非门和一个四输入与非门,达到逻辑功能和晶体管数量最小化的效果,节约了版图资源,减小了复杂程度。

其逻辑电路图很容易得出如下:

4.版图设计

版图设计在一个重要环节,画棒状图。

其作用相当于打草稿,可以减少不必要的错误,同时提高工作效率。

由电路图可以画出三输入表决器的版图棒状图

如下:

5.画版图

1)LINUX系统下右击鼠标点击“新建终端”;

2)输入“mkdir 20074456”,新建一个名为20074456的文件夹;3)cp –r file.tar 20074456,将根目录下file.tar文件拷贝到新建的文件夹里面;

4)输入“cd 20074456”进入工作目录,让知己的工作文件都在这个文件夹里生成

输入“tar xvf file.tar”解压文件夹file.tar到20074456;5)输入“pdt”打开新建版图路径界面,新建的版图libriry name 是liling,cell name 是liling1;

6)按照棒形图画出版图,注意同层间各区域的距离及其工艺参数,并标注;

7)画好之后,进行DRC验证;版图设计规则检查,是对IC版图做几何尺寸检查,以确保电路能够被特定加工工艺实现。

结果如下图:

输入“zse”,打开新建电路图路径界面,电路图 libriry name 是liling2, cell name 是liling3;

8)用Mos管画出三输入表决器电路图:

9)画好之后,进行ERC验证;电气规则检查,检查电源、地的短路,悬空器件和节点特性。

检查无误之后,生成lvs网表文件如下;

10)输入“ldc -i inv.lvs”,进行lvs验证,再打开界面中修改其中五个地方,①在PRIMARY之后,将原来的内容改为版图的cell name,②在LIBRARY之后,将原来的内容改为版图的library name,③在第一个SCH—NETLIST之后,将原来的内容改为电路图的library name,④在第二个SCH—NETLIST之后,将原来的内容改为电路图的cell name,⑤将最后三行字符删除。

保存更改结果。

开始跑运行,版图与电路图一致性检查,将版图与电路图对比,经检查电路的加连接,与MOS的宽长比是否匹配。

11)验证完之后,可查看验证结果,如果有错误,可根据错误原因和错误出处进行修改,直至验证结果正确。

6.心得体会

画版图,选择比例比较重要。

开始我们仅用了半天时间就画出了版图,但是由于画的距离太近,没有把握好各模块减的距离导致了重

画。

刚开始时候要

每画一步验证一下是否有错,当各个区域都出来了以后就可以用复制粘贴的方法去画。

比如我已经画好了电源的n注入区,在下面画n管时就可以直接复制n注入区,应为前面区域大小已经订好,复制可以避免各层间的距离问题。

而且当管子要重复用时也可以复制以减少工作量和避免不必要的错误。

根据版图再画电路图,版图和电路图之间要相对应,如哪个PMOS或哪个NMOS有接电源或接地,输入、输出及电源符号等等。

课程设计,提前画棒状图是其中的关键一环,版图大多是根据棒状图画的;另外,合理的布局布线也比较重要,可以使版图和电路图更加美观,并且不容易出错。

几天试验下来,发现版图设计操作并不难。

不断练习,积累经验才是其核心所在。

因为我们一星期有四天在擦错改错,这些错误也只有不断的做,不断的积累才可以避免不在出现。

唯有不断积累,才能熟能生巧。

.。