网上下载的一个三分频电路说明

- 格式:docx

- 大小:74.87 KB

- 文档页数:7

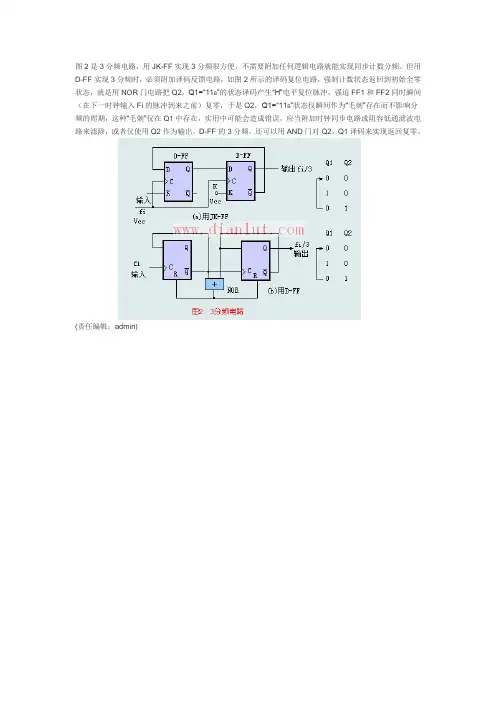

图2是3分频电路,用JK-FF实现3分频很方便,不需要附加任何逻辑电路就能实现同步计数分频。

但用D-FF实现3分频时,必须附加译码反馈电路,如图2所示的译码复位电路,强制计数状态返回到初始全零状态,就是用NOR门电路把Q2,Q1=“11B”的状态译码产生“H”电平复位脉冲,强迫FF1和FF2同时瞬间(在下一时钟输入Fi的脉冲到来之前)复零,于是Q2,Q1=“11B”状态仅瞬间作为“毛刺”存在而不影响分频的周期,这种“毛刺”仅在Q1中存在,实用中可能会造成错误,应当附加时钟同步电路或阻容低通滤波电路来滤除,或者仅使用Q2作为输出。

D-FF的3分频,还可以用AND门对Q2,Q1译码来实现返回复零。

(责任编辑:admin)。

自制前级三分频功放笔者介绍的是三分频功放,电路见图1,其缩小印板图见图2。

印刷电路的设计思路电子元件的定位以最短信号线布局,舍去为使阻容件列队好看而走曲径的做法。

为避免功放电源做在功放板上距分频电路过近造成干扰,电源单独制作,在距电源远点供电处增加滤波组件。

分频电路四周以地线与功放电路隔离,左右声道接地分开。

各功放元件接地后各行其道,汇一处后,各声道地及喇叭接地汇总于电源地。

因而,本电路噪声背景十分干净。

分频点的计算可用公式f=1/2πRC计算分频网络元件值,笔者用该公式在一些电路中得到了验证。

本电路取fL=800Hz,fH=5kHz,如R2取5.6k时,则C3=C4=1/(2πR2fL)=0.036uF。

IC1b、C6、C7、R6、R7和IC3a、R8、R9、C8、C9组成800Hz~5kHz的带通滤波器。

元器件的选取分频核心件IC选用OP275。

W为音量控制,w1、W2、W3分别为L、Z、H声道增益控制,用以调整整体音响的平衡度,一次调好不必再动。

首选音质细腻通透的TDA7294做L通道功放。

音色温暖亮丽的双功放LM4766做Z、H通道功放最为合适,实践证明,完全消除了用LM3886担当此任音质沉闷的感觉。

每块功放用8cmx8cm的肋式散热器,使用中没有明显的温升现象,全电路见图1。

试机及随想笔者曾按《电子报》刊出电路多次制作电路板,感受之深莫过于此。

本电路的制作是以《电子报》上刊登的《三声道功率放大器》(以下简称“三电路”)文中电路为据制板,当焊接完毕后通电试机,却立烧AC保险。

查知该板正负电源电路之间正反向电阻均为32Ω!切开TDA7294供电电路后分别测试又都正常,并接后再测依旧,再切开,仔细测量发现,TDA72942正负供电电路的正向电阻远大于反向电阻,怀疑正负脚反接。

查阅其他资料,是《三电路》的⑧、15脚及⑦、13脚分别错接到电源的正负极上,造成正反电阻异常,不得已切断铜箔,改接。

Verilog实现三分频的多种方法(附有代码)用Verilog语言实现奇数倍分频电路 3分频 5分频 7分频分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去,这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,占空比不限定时,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

三分频扬声器系统分频器电感的精确设计三分频扬声器系统分频器电感的精确设计1 引言扬声器系统的分频器分为前级分频和功率分频2类。

前级分频是前级电路中由电子元件产生的分频,再由各自的功放分别驱动高﹑中﹑低音扬声器系统,如图(1a)所示,属于小信号有源分频。

而功率分频则是由电感、电容、电阻元件构成的位于功放与扬声器之间的无源分频电路,如图(1b)所示。

采用功率分频的扬声器系统结构简单、成本低,而且又能获得很高的放音质量,因而在现代高保真放音系统中应用最为普遍。

其性能的好坏与扬声器的各项指标以及分频电路、电感元件的性能、精度有密不可分的关系,精确计算电感参数便是成功的关键。

2 对分频器电路、元件的要求(1)电路中电感元件直流电阻、电感值误差越小越好。

而且为使频响曲线平坦最好使用空心电感。

(2)电路中电容元件损耗尽可能小。

最好使用音频专用金属化聚丙烯电容。

(3)使各扬声器单元分配到较平坦的信号功率,且起到保护高频扬声器的作用。

(4)各频道分频组合传输功率特性应满足图2所示特性曲线的要求(P0为最大值,P1为对应分频点f1、f2的值)。

分频点处的功率与功率最大值之间幅度应满足P1(=0.3~0.5)P0的范围。

(5)整个频段内损耗平坦,基本不出现“高峰”和“深谷”。

3 分频电感电容参数值的计算下面以三分频分频器为例说明其参数的计算,如图3所示。

1)计算分频电感L1,L2,L3,L4和分频电容C1,C2,C3,C4。

为了得到理想的频谱特性曲线,理论计算时可取:C1=C4,C3=C2,L1=L3,L4=L2,分频点频率为f1,(f2见图2),则分频点ω1=2πf0,ω2=2πf2。

并设想高、中、低扬声器阻抗均相同为RL。

每倍频程衰减12 dB。

2)实验修正C1,C2,C3,C4,L1,L2,L3,L4的值为精确起见,可用实验方法稍微调整C1,C2,C3,C4,L1,L2,L3,L4的值,以满足设计曲线﹙见图2﹚的要求。

三段音调电路的分频点1.引言1.1 概述概述部分的内容:音调电路是一种常见的电子设备,广泛应用于音乐器材、配音设备和音频处理等领域。

在音乐制作和音频处理过程中,分频点是一个重要的参数,它决定了音频信号在频域上的划分和处理方式。

三段音调电路是一种常见的分频电路,它能够将输入的音频信号按照频率划分成三个不同的频段,并对每个频段进行独立的调节。

本文将在引言部分对三段音调电路的概念和作用进行介绍。

随后的正文部分将详细阐述三段音调电路的原理和分频点的定义与作用。

最后的结论部分将对三段音调电路的特点进行总结,并探讨不同分频点对音调产生的影响。

通过本文的阅读,读者将能够深入了解三段音调电路的工作原理和分频点的重要性。

同时,读者还将了解到不同分频点对音调的影响,并能够根据实际需求进行合理的选择和调节。

希望本文能够为读者提供有关三段音调电路的全面理解和应用指导。

1.2 文章结构文章结构指的是文章的组织框架和内容安排,它对于读者理解文章的逻辑结构和脉络十分重要。

本文的结构分为三个主要部分:引言、正文和结论。

在引言部分,首先对三段音调电路的概述进行了介绍,说明了该电路的主要特点和应用背景。

接着,明确了本文的结构和内容安排,即引言、正文和结论。

最后,阐明了本文的目的,即探讨分频点对三段音调电路的影响。

在正文部分,首先对三段音调电路的原理进行了阐述,介绍了音调电路的工作原理和基本组成部分。

其次,详细说明了分频点的定义和作用,解释了分频点在音调电路中的重要性和作用。

在结论部分,对三段音调电路的特点进行了总结,简要概括了该电路的特点和优势。

同时,探讨了不同分频点对音调产生的影响,说明了分频点选择对音调效果的重要性。

通过以上的文章结构,读者能够清晰地了解到本文的思路和组织,有助于更好地理解和把握文章的内容和要点。

1.3 目的本文旨在探讨三段音调电路的分频点对音调产生的影响,并分析不同分频点选取的理由。

通过对三段音调电路原理和分频点的定义与作用的介绍,我们可以更深入地理解和认识这一电路设计中的关键要素。

通用型音箱三分频器的制作音箱是音频设备中的关键组成部分,负责将信号转换为声音输出。

在音箱中,三分频器是一种重要的电路组件,用于将输入的音频信号分成低频、中频和高频三个频段进行处理,从而使音质更加清晰和平衡。

本文将介绍如何制作一个通用型音箱三分频器。

材料准备:1.电容器:选择合适的电容器用于分频电路的设计,常见的有陶瓷电容、薄膜电容和电解电容等。

2.电感器:选择适合的电感器用于分频电路的设计,常见的有蜡线电感和铁氧体电感等。

3.电阻器:选择合适的电阻器用于分频电路的设计,常见的有金属膜电阻和炭膜电阻等。

4.音箱和喇叭单元:选择合适的音箱和喇叭单元,以满足所需的音频输出要求。

5.音频线:用于连接音源和音箱的音频线。

步骤:1.确定频率范围:根据所需的音频输出要求,确定低频、中频和高频的分界频率。

通常情况下,低频分界频率为20Hz-200Hz,中频为200Hz-2kHz,高频为2kHz-20kHz。

2.计算电容器和电阻器数值:根据所选定的分界频率,使用以下公式计算所需的电容器和电阻器数值:-低频段:C=1/(2πfL)-中频段:C=1/(2πfL)-高频段:C=1/(2πfL)其中C为电容器的值,f为分界频率,L为电感器的值。

3.搭建分频电路:根据计算得到的数值,使用电容器、电感器和电阻器在电路板上搭建三个分频电路。

分频电路的原理是通过电容器、电感器和电阻器的组合,将不同频率的信号分到不同的通道中。

4.连接音箱和喇叭单元:将制作好的分频电路连接到音箱和相应的喇叭单元上。

低频信号通过低频分频电路传递到低音单元,中频信号通过中频分频电路传递到中音单元,高频信号通过高频分频电路传递到高音单元。

5.连接音源:将音源通过音频线连接到音箱的输入端口上,确保音箱与音源正常连接。

注意事项:1.在制作分频电路时,应选用合适的组件,以确保电容器和电感器的功能和性能符合所需的要求。

2.在连接分频电路和音箱时,应确保连接的稳固可靠,以确保音频信号的正常传输。

三分频器电路三分频器是一种常用的电路,用于将输入信号分成三个相等的输出信号。

它在很多电子设备中都有广泛的应用,比如音频放大器、通信系统和信号处理器等。

三分频器电路的基本原理是利用滤波器和分频器的组合。

滤波器用于分离不同频率的信号,而分频器则将输入信号分成多个频率相等的信号。

三分频器电路一般由低通滤波器、带通滤波器和高通滤波器组成。

低通滤波器用于传递低频信号,带通滤波器用于传递中频信号,高通滤波器用于传递高频信号。

在三分频器电路中,输入信号首先经过一个低通滤波器。

低通滤波器的作用是将高频信号滤除,只保留低频信号。

然后,低通滤波器的输出信号经过一个带通滤波器。

带通滤波器的作用是将中频信号滤除,只保留高频信号和低频信号。

最后,带通滤波器的输出信号再经过一个高通滤波器。

高通滤波器的作用是将低频信号滤除,只保留高频信号。

三分频器电路的设计需要考虑滤波器的特性和频率范围。

滤波器的特性可以通过选择合适的电容和电感来实现。

频率范围则是根据应用需求来确定的,可以根据需要选择不同的滤波器参数。

三分频器电路的应用非常广泛。

在音频放大器中,三分频器可以将音频信号分成低频、中频和高频三个部分,分别经过不同的放大电路进行放大,然后再合并成一个完整的音频信号。

在通信系统中,三分频器可以将信号分成不同的频率段,分别进行处理和传输。

在信号处理器中,三分频器可以将输入信号分成不同频率的信号,然后进行不同的处理操作。

三分频器是一种重要的电路,它可以将输入信号分成三个相等的输出信号。

它在音频放大器、通信系统和信号处理器等电子设备中都有广泛的应用。

通过合理设计滤波器和分频器,可以实现不同频率信号的分离和处理。

三分频器的应用范围非常广泛,可以满足各种不同的需求。

音箱三分频器电路图(四款模拟电路设计原理图详解)展开全文什么是音箱分频器?音箱分频器是一种组合式滤波器,可以将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放,对音质的好坏至关重要。

换句话说,使用分频器可以将高频信号送到高音扬声器中,低频信号送到低音扬声器中,高、低频信号各行其道,尽可能大地利用了各自扬声器的工作频带优势,以保证不同工作频段的扬声器充分发挥作用,使各频率的放音特性更加均衡一致。

音箱分频器电路图音箱三分频器电路图(一)音箱分频器电路图如下两图所示,从电路结构来看,分频器本质上是由电容器和电感线圈构成的LC滤波网络,高音通道是高通滤波器,它只让高频信号通过而阻此低频信号;低音通道正好想反,它只让低音通过而阻此高频信号;中音通道则是一个带通滤波器,除了一低一高两个分频点之间的频率可以通过,高频成份和低频成份都将被阻止。

音箱分频器电路图连接高音喇叭的电路:让电流先流过电容器,阻止低频,让高频通过,并且喇叭与一个线圈并联,让线圈产生负电压,那么这个电压对于高音喇叭来说正好是一个电压补偿,于是可以近似地逼真还原声音电流。

音箱分频器电路图连接低音喇叭电路:电流先流过线圈,这样高频部分被阻止,而低频段由于线圈基本没有阻碍作用而顺利通过,同样,低音喇叭并联了一个电容器,就是利用电容器在高频的时候产生一个电压来补偿损失的电压,道理和高音喇叭端是一样的。

在实际的分频器中,有时为了平衡高、低音单元之间的灵敏度差异,还要加入衰减电阻;另外,有些分频器中还加入了由电阻、电容构成的阻抗补偿网络,其目的是使音箱的阻抗曲线心理平坦一些,以便于功放驱动。

音箱三分频器电路图(二)分频器是音箱中的“大脑”,对音质的好坏至关重要。

功放输出的音乐讯号必须经过分频器中的过滤波元件处理,让各单元特定频率的讯号通过。

要科学、合理、严谨地设计好音箱之分频器,才能有效地修饰喇叭单元的不同特性,优化组合,使得各单元扬长避短,淋漓尽致地发挥出各自应有的潜能,使各频段的频响变得平滑、声像相位准确,才能使高、中、低音播放出来的音乐层次分明、合拍、明朗、舒适、宽广、自然的音质效果。

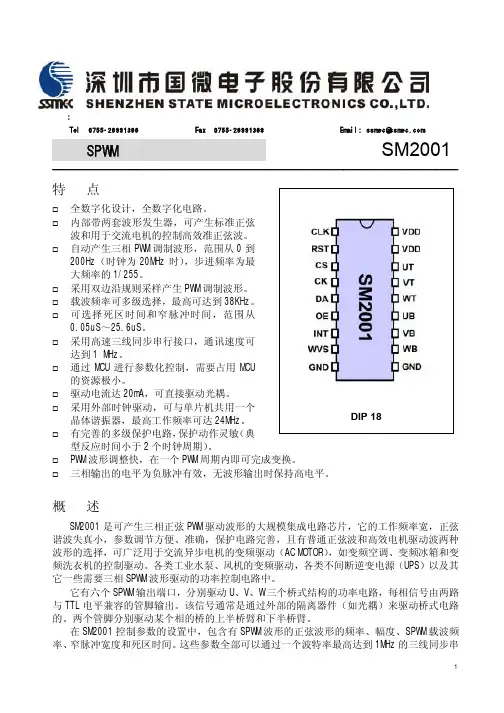

地址: 深圳市高新技术产业园南区高新南一道国微大厦电话Tel:*************传真Fax:*************电子邮件Email:***************三相SPWM波形发生器专用电路SM2001━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━━特点全数字化设计,全数字化电路。

内部带两套波形发生器,可产生标准正弦波和用于交流电机的控制高效准正弦波。

自动产生三相PWM调制波形,范围从0到200Hz(时钟为20MHz时),步进频率为最大频率的1/255。

采用双边沿规则采样产生PWM调制波形。

载波频率可多级选择,最高可达到38KHz。

可选择死区时间和窄脉冲时间,范围从0.05uS~25.6uS。

采用高速三线同步串行接口,通讯速度可达到1 MHz。

通过MCU进行参数化控制,需要占用MCU的资源极小。

驱动电流达20mA,可直接驱动光耦。

采用外部时钟驱动,可与单片机共用一个晶体谐振器,最高工作频率可达24MHz。

有完善的多级保护电路,保护动作灵敏(典型反应时间小于2个时钟周期)。

PWM波形调整快,在一个PWM周期内即可完成变换。

三相输出的电平为负脉冲有效,无波形输出时保持高电平。

概述SM2001是可产生三相正弦PWM驱动波形的大规模集成电路芯片,它的工作频率宽,正弦谐波失真小,参数调节方便、准确,保护电路完善,且有普通正弦波和高效电机驱动波两种波形的选择,可广泛用于交流异步电机的变频驱动(AC MOTOR),如变频空调、变频冰箱和变频洗衣机的控制驱动。

各类工业水泵、风机的变频驱动,各类不间断逆变电源(UPS)以及其它一些需要三相SPWM波形驱动的功率控制电路中。

它有六个SPWM输出端口,分别驱动U、V、W三个桥式结构的功率电路,每相信号由两路与TTL电平兼容的管脚输出。

该信号通常是通过外部的隔离器件(如光耦)来驱动桥式电路的。

两个管脚分别驱动某个相的桥的上半桥臂和下半桥臂。

![[转载]分频电路,二分频、三分频和四分频](https://uimg.taocdn.com/f1aace0c640e52ea551810a6f524ccbff121caac.webp)

[转载]分频电路,⼆分频、三分频和四分频原⽂地址:分频电路,⼆分频、三分频和四分频作者:davis⾳箱的⾼中低频主要靠分频器来区分。

分频器按分频频段可分⼆分频、三分频和四分频。

⼆分频是将⾳频信号的整个频带划分为⾼频和低频两个频段;三分频是将整个频带划分成⾼频、中频和低频三个频段;四分频将三分频多划分出⼀个超低频段。

分频点与分频斜率是直接影响分频品质分频频率(交*频率)。

分频点是指两个相邻扬声器(如⼆分频中的⾼⾳与低⾳,三分频中的⾼⾳与中⾳,中⾳与低⾳)的频响曲线在某⼀频率上的相交点,通常为两个扬声器中功率输出的⼀半处(即-3dB点)的频率,要根据⾳箱和每个扬声器的频率特性和失真度等参数决定。

通常⼆分选购上,建议您在购买的时候⼀定要多加⼩⼼,不要盲⽬地听店主的推荐和介绍,买这种东西绝对不可以⼼急。

最好之前楼主多去⼀些⾳响论坛先去具体了解些⾳响知识。

个⼈建议楼主去⾼级别的钻⽯卖家购买,与卖家多聊聊,还可以通过聊天软件向曾经购买者在⼀个扬声器系统⾥,⼈们把箱体、分频电路、扬声器单元称为扬声器系统的三⼤件,⽽分频电路对扬声器系统能否⾼质量地还原电声信号起着极其重要的作⽤。

尤其在中、⾼频部分,分频电路所起到的作⽤就更为明显。

编辑摘要⽬录[隐藏 ]1 作⽤2 分频点3 分频⽅式4 优点5 挑选分频电路 - 作⽤分频电路作⽤如下:1、合理地分割各单元的⼯作频段;2、合理地进⾏各单元功率分配;3、使各单元之间具有恰当的相位关系以减少各单元在⼯作中出现的声⼲涉失真;4、利⽤分频电路的特性以弥补单元在某频段⾥的声缺陷;5、将各频段圆滑平顺地对接起来。

显然,分频电路的这些作⽤已被⼈们所认识和接受。

分频电路 - 分频点脉冲分频电路1·分频点指分频器⾼通、带通和低通滤波器之间的分界点,常⽤频率来表⽰,单位为赫兹。

分频点应根据各频段扬声器单元或⾳箱的频率特性和功率分配来具体确定。

2·分频点的选择:1)、考虑中低单元指向性实⽤边界频率f=345/d(d=单元振膜有效直径)。

用Verilog语言实现奇数倍分频电路 3分频 5分频 7分频分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相环资源,如altera 的PLL,Xilinx的DLL.来进行时钟的分频,倍频以及相移。

但是对于时钟要求不高的基本设计,通过语言进行时钟的分频相移仍然非常流行,首先这种方法可以节省芯片内部的锁相环资源,再者,消耗不多的逻辑单元就可以达到对时钟操作的目的。

另一方面,通过语言设计进行时钟分频,可以看出设计者对设计语言的理解程度。

下面讲讲对各种分频系数进行分频的方法:第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去,这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频常常在论坛上有人问起,实际上,奇数倍分频有两种实现方法:首先,占空比不限定时,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

如果要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

教你制作音箱分频器

最简单就是用一个2、2μF电容与高音喇叭串联,低音喇叭直接接在功放上。

高音喇叭千万不要直接接在功放上,要烧了。

1.今天,为大家送上一个自制的低音分频器,虽然材料不多,也简单,但低音效果极强.

2.下面上图

3.因为电路要用2个无极电容,我没有无极电容,所以用4个50v10uf电容串联代替无极电容.

4.洞洞板.

5.绕线圈的模子.

6.因我是东西做好后才拍照,所以绕线圈的照片没有,线圈的绕法是从内向外20圈一层,绕5层,中间用502加固.绕好后将胶水瓶子上的一层膜连线圈取下,撕去膜,线圈就脱胎了.线圈的接线是外接MP3的一个脚,内接电容和扬声器.

低音喇叭本来就是一个电感,对高频信号影响很小,低音其实可以不要分频。

实在要的话,串联一个电感,可以自己绕1mm的漆包线在中性笔上绕20至30圈,也可以用电表里面的粗线圈直接用。

音箱三路分频器电路图

分频器是音箱中的“大脑”,对音质的好坏至关重要。

功放输出的音乐讯号必须经过分频器中的过滤波元件处理,让各单元特定频率的讯号通过。

要科学、合理、严谨地设计好音箱之分频器,才能有效地修饰喇叭单元的不同特性,优化组合,使得各单元扬长避短,淋漓尽致地发挥出各自应有的潜能,使各频段的频响变得平滑、声像相位准确,才能使高、中、低音播放出来的音乐层次分明、合拍、明朗、舒适、宽广、自然的音质效果。

音箱分频器是一种组合式滤波器,可以将声音信号分成若干个频段。

音响的二路分频器就是由一个高通滤波器和一个低通滤波器组成,而三路分频则又增加了一个带通滤波器。

本文所介绍的是一款简单的音箱三路分频器电路图,输入端可接同一输出端。

如图所示。

三分频电路设计你们有没有见过那种能把一种东西分成好几部分的小发明呀?就像把一个大蛋糕切成三块一样,三分频电路呢,就是把电信号分成三个不同部分的神奇电路。

我给你们讲个故事吧。

有一次我在听音乐,发现音响里发出来的声音有高音、中音和低音,特别好听。

后来我才知道,这里面就可能用到了类似三分频电路的东西。

就好比有三个小伙伴在唱歌,一个小伙伴负责高音部分,声音清脆响亮,像小鸟在枝头欢快地叫;一个小伙伴负责中音部分,声音圆润动听,就像我们平常说话那样舒服;还有一个小伙伴负责低音部分,声音低沉有力,就像是大笨钟敲响时的那种嗡嗡声。

而三分频电路就像是一个聪明的指挥家,把电信号按照不同的高低音要求,准确地分配给不同的“小歌手”,这样我们听到的音乐才会这么美妙。

那这个三分频电路是怎么做到的呢?咱们可以想象一下电路就像一条条小马路,电信号就是在路上跑的小汽车。

在三分频电路里,有一些特殊的“交通标志”和“岔路口”。

这些“交通标志”和“岔路口”就像一个个小关卡,它们可以让一部分电信号走这条“路”,另一部分走另一条“路”。

比如说,有一个“关卡”专门拦住那些高音的电信号,让它们从一条特定的“小路”通过,这就成了高音部分的电路;还有一个“关卡”拦住低音的电信号,让它们从另外的“小路”走,就形成了低音部分的电路;剩下的那些电信号就成了中音部分的电路啦。

咱们再举个例子吧。

假如我们有一个装满彩色珠子的盒子,我们想把珠子按照颜色分成三堆,红色一堆、蓝色一堆、绿色一堆。

我们可以用一些有小缝隙的板子,缝隙的大小刚好能让一种颜色的珠子通过,这样就能把珠子分开啦。

三分频电路里的那些小元件就像是这些有缝隙的板子,把不同的电信号分开。

虽然三分频电路听起来有点复杂,但是只要我们发挥想象,把它想象成生活里熟悉的东西,就会觉得很有趣。

而且它在我们生活中的很多地方都能用到呢,就像我们的音响、收音机这些能发出不同声音的东西里面,可能都藏着这个神奇的三分频电路。

1,使用原理图文件设计三分频电路:仿真需要设置function功能,然后生成网表(processing)仿真结果:2,使用Verilog 程序设计三分频,四分频,五分频设计三分频:module sanfp(clkin,clkout);input clkin;output clkout;reg[1:0] step1,step;always @(posedge clkin)begincase (step)2'b00:step<=2'b01;2'b01:step<=2'b10;2'b10:step<=2'b00;default:step<=2'b00;endcaseendalways @(negedge clkin)begincase(step1)2'b00:step1<=2'b01;2'b01:step1<=2'b10;2'b10:step1<=2'b00;default:step1<=2'b00;endcaseendassign clkout=~(step1[1]|step[1]);endmodule四分频:module sifenp(clkin, clkout); input clkin;output clkout;reg[1:0] count1;always @(posedge clkin) begincase (count1)2'b00: count1<=2'b01;2'b01: count1<=2'b10;2'b10: count1<=2'b11;2'b11: count1<=2'b00; default count1<=2'b00; endcaseendassign clkout=count1[1]; endmodule五分频:module fivefp(clkin, clkout,clkout1,clkout2);input clkin;output clkout,clkout1,clkout2;reg[2:0] cnt1, cnt2;always @(posedge clkin)begincase (cnt1)3'b000:cnt1<=3'b001;3'b001:cnt1<=3'b010;3'b010:cnt1<=3'b100;3'b100:cnt1<=3'b101;3'b101:cnt1<=3'b000;default cnt1<=3'b000;endcaseendalways @(negedge clkin)begincase (cnt2)3'b000:cnt2<=3'b001;3'b001:cnt2<=3'b010;3'b010:cnt2<=3'b100;3'b100:cnt2<=3'b101;3'b101:cnt2<=3'b000;default cnt2<=3'b000;endcaseendassign clkout=cnt1[2]|cnt2[2];assign clkout1=cnt1[2];assign clkout2=cnt2[2];endmodule采用2个计数器cnt1和cnt2Cnt1需要在第3个clk上升沿时翻转,而且计数最高位要为1,即100.而后面计数需要保持2个周期的高,这样总共五个周期,只是占空比不为50%。

Hi-Fi三路有源分频器明日一日路有源分频器此立体声三路有源分频器与三路扬声器系统配用,可避免无源分频网络的缺点,使扬声器获得最佳的功率电平.什么是有源分频器?为什么需要有源分频器绝大多数H1~F1高保真音响爱好者都知道分频.即在2路和3 路扬声器系统中均含有一种无源网络.用其将音频频谱分为二个频段(对于2路扬声器系统)或三个频段(对于3路扬声器系统).无源分频器用电感,电容和电阻将音频分成各个频段,并将相应的音频信号电平馈送到各个扬声器驱动级.例如,低音扬声器通常比中音和高声扬声器的灵敏度低,所以,输入中音和高音扬声器的信号需作相应衰减,这样,三个扬声器的整体输出才相同.在较高档的扬声器系统中,分频器通常很复杂,要求也很高.因常要衰减中音器的功率.此口陈伟鑫间的一个复杂网络,这就意味着有一定的插入损耗.而这对于大家都需要的低音影响会很大,对中音和高音能清晰地播放,其影响也较为明显.凡此种种,都是因为采用了无源的方案.在.有源系统中,省掉了无源分频器,并用电子学的方法将左,右声道各自分为三个频段:低音,中音和高音.这就是.有源分频器要完成的任务.有源分频器的输出信号馈入六个独立的放大器.以驱动每个音箱中的低音,中音和高音扬声器单元.整个系统的构成如图l所示.总之,这里要比常见的系统多用几个放大器.但也给你带来更大的灵活性.更为有利的是.你可以得到一个性能更佳,功率更大的音响系统.有源分频法也意味,日B1^H-汉L1个u/b1OIlIJ上=i?/.1毋高通和高音信号.实际上就意味着要浪费放大厂卜功放卜_.外,无源分频器是插在扬声器和放大器之带通厂-l\功放卜_.口=低通LL——,I功放卜CD机或其他_—前置放大器,I立体声信号源及控制单元高通R.R,-一II功放卜II带通几卜功放卜低通__,卜_功放卜口=2006年第7期3路分频器左声道高音左声道中音左声道低音右声道高音右声道中音低音三图2三路有源分频器信号处理电路(左声道)着你可以在同一系统中混用4Q和8Q扬声器,电平匹配很容易.没有功率浪费.一,有源分频器这里介绍的有源分频器可装入一个单独的机箱内,其面板上只有电源开关.此分频器未设用户控制,既没有用来改变分频频率的开关.也没有输出信号的外部电平控制.要改变对扬声器的激励,就必须调整驱动放大器的音量控制.在后面板上,有四对RCA插口,一对用于立体声信号输入.另外三对则分别用于立体声的低音,中音和高音信号的输出.后面板上还有一个NEC电源插座和一个接在电源变压器初级电路的保险丝盒.在机箱内.全部电路均装在一块尺寸为219mmX99mm的印刷电路板上.一组RCA输入和输出插座亦装在其上.唯一的外部接线是环形电源变压器的次级与电路板的连接线.二,电路介绍分频器电路如图2.由于左,右两声道电路相同.这里仅考虑左声道.电源电路也装在印刷电路板上.如图3N示.总的看来,左声道用了12个运算放大器,即三个左声道左声道中音输出左声道低音输出TL074(四FET输入运放集成块).IC1a,IC1b,IC5a和IC5b用作输入或输出缓冲器,而其余8个运放则用作L1nkwr1te—Ri1ey有源滤波器,此滤波器的斜率为l2dB/倍频程.在每~种情况下.都由两个12dB/倍频程滤波器串联.以给出总的滤波器斜率24dB/倍频程.这比无源分频器通常所用的斜率要陡得多.所有这些滤波器的通带内电压增益为1.三,低通,高通在作进一步探讨之前.这里将对几个初学者常会发生混淆的术语加以说明.即所谓低通,高通和带通.一个低通滤波器允许低频信号通过.而阻止较高频率的信号.因此,一个驱动低音扬声器的电路通常称为低通滤波器.因为这类电路的驱动信号频率约低于2OOHZ.类似地.一个高通滤波器只允许高频信号通过,而阻止低频信号通过.因此,馈送信号至高音扬声器的这部分分频网络则称为高通滤波器,即使其组成仅仅是一个电容器.如果将一个高通滤波器和一个低通滤波器串联,则其组合将只允许一个频带内的信号通过,因此,我们称其为带通滤波器.在这里的有源分频网络中,带通滤波2oo6年第7期器用于中频输出.我们还应当了解滤波器术语中的截止频率和滤波器斜率.本电路所用的滤波器具有12dB/倍频程的衰减:这就是滤波器的斜率.截止频率是信号输出较额定电平小3dB处的频率.例如,在一个低通滤波器中,可以有一个1kHZ的截止频率(一3dB点),而从此处起,滤波器的斜率为12dB/倍频程.在理论上,这就意味着在2kHz处(即是1kHz的一个倍频)频率响应为一15dB在实际中可能没有这么精确.此电路中,所用的滤波器为L1nkwr1te-Ri1ey结构,且用了八个这类的滤波器,四个是高通,四个是低通,这仅仅是一个声道.每个滤波器由一个接成电压跟随器的运放和前置的两个RC网络共同构成.前已指出,对于每个高通和低通滤波器.均用2个l2dB/倍频程的滤波器串联而成,使其总的衰减为24dB/倍频程(4阶).基本滤波器的结构如图4所示.图中还给出了分频点的计算公式.在此处特定情况下.分隔频率在-6dB点,其原因是本设计中每级滤波电路由两个滤波器级联而成(2x3dB=6dB).注意,在低通滤波器中图示的电容值为C和2C.而在高通滤波器中,所用的电阻的阻值为R和2R(参见图4).在图2所示主电路中.可以注意到2C元件实际上是两个等值电容的并联,这是因为很难找到一个电容器,其值正好是另一个电容的两倍.而在另一方面.找电阻要容易得多,所以R用的是10kQ电阻,2R用的是20kQ 电阻.现在让我们再回来讨论图2的电路.到左声道的输入信号是经由一RC滤波器馈入的.该滤波器的滚降频率为100kHZ,然后,信号进入运放IC1a,这里IC1a被接成单位增益缓冲器(又称电压跟随器).IC1a的输出推动两个由IC1d和IC1C级联而成的低通滤波器.以及由IC3a和IC3d级联而成的两个低通滤波器.这里的低通和高通滤波器的截止频率均设定在5.1kHZ.第二个高通滤波器的输出(IC1C)馈至电平控制器VR1,然后再送至IC1b,而IC1b被接成增益为2的同相放大器.IC1b提供左声道的高音输出.因此,高音扬声器仅得到高于5kHz的频率.四,带通低通滤波器IC3d的输出馈至由IC3c和IC3b构成的高通滤波器,这两个高通滤波器的截止频率均为239HZ.高通滤波器IC3b的输出则馈至音量控制微调电位器VR2,然后进入增益为2的运放IC5a.这样就获得了左声道的中频段输出激励.其频带范围为239HZ至5.1kHZ.由图2可知,运放IC3d不但驱动高通滤波器IC3c和IC3b,同时还驱动由IC5d和IC5c构成的串联低通滤波器,而这两个低通的截止频率也是239HZ.IC5C的输出加至微调电位器VR3,然后又馈入增益为2的运放IC5b. 这样就得到了频率低于239Hz的低音左声道输出信号. 各级的所有输出在分频点上是同相的.在交叉频率处的电压增益各级均为一6dB(即为基准电平的一半). 因此,当高,中,低三频段的频响曲线加在一起时,即可获得总增益为1的极其平坦的频率响应.由图5N示的频响曲线可以看出此有源分频器的性能是多么良好.图中画出了三种滤波器(低通,高通和带通)的频响曲线,顶端便是总频响曲线.图8给出了相应的加法电路,仅供有兴趣的读者参考.图3所示为电源电路,这里用了一个20V A的环形电源变压器,二个次级的输出均为15V.双15V输出用来驱动桥式整流器(D1~D4),再经两个1000F的电容滤波,就获得了未经稳压的直流双电源,其值约为±22V.接着又馈入稳压集成块REG1和REG2.以产生稳定的双二r一.一一l叶.,叶VV叶一lIkInlJTl一一一lLI—TIII1I'I…CND…l'固:中:}15V:1O00pF1OOpF一100nFx7+15V.25,x225VWx2一..GNDlNI:}15V'-上'L上一I100nFx7II—一0rl...…1.一1二二__J1一l'',uu0l一一一一20o6年第7期图电源电路—————————————1■————————————一R..卜……辞滤波器Od8m10.Oo00.0—10.0o一-20.0o馏霉-30.0o—4J0.0o-50.0o通滤波器图4低通和高通痣波器基本结构月I)总-牲,,一一,,{::-●--)l'|..I\\|l.|'I\|I1/~I\『J/1『/r1Il高互\确匝/酗互l●J1010o1k]Ok10ok频率(1{z】图5三个滤波器的频响曲线总特性十分平坦电源±15V.每路电源均有一个1OOp.F电容器和7个100nF多层陶瓷电容器构成的旁路电容.这些电容器均安装在印刷电路板上.五,制作如前所述.此有源分频器的全部电路均安装在一块尺寸为219mmx99mm的单面印刷电路板上,因此,电路结构简单直观.但若你希望自行调整交叉频率,电路会稍复杂.如需这样做,可从表1中选取相应的元件值. 例如.如果你决定将高音交叉频率选在3kHz左右,则查表1,从表的右边一列可得310O的交叉频率,再从第1,第2列得R和C的值.实际上要改动的就是电容和电阻.即在高通和低通滤波器中与IC1和IC3并联的2.2I'IF电容器,现在必须改为3.3I'IF,而相关的10kQ电阻则需增加到11kQ.20kQ增加到22kQ.注意.与高音扬声器配用的高通滤波器(IC3a和IC3d)和与中频扬声器配用的低通滤波器(IC3a和IC3d)必须有绝对相同的截止频率,否则就不能获得完全平坦的频率响应.类似地.如果需要将低音截止频率改到约35OHz,则可由表1右边第3列查得最接近的347Hz,然后由第1列和第3列相应查得R的数值为12kQ,2R为24kQ,由第2列得C的值为27i'iF.当然.你也可以参考有关资料或教科书自行设计计算.当交叉频率已经决定后,即可开始装配,首先检查印刷电路板,仔细查看板上电路有无短路,开路等.检查时应对照图6给出的印刷电路板装配图.然后安装全部电阻,接着安装电容器和多圈微调电位器.应保证电解电容按正确的定位进行安装.双极电解电容无极性,可按任一方向安装.在理想条件下.全部滤波器电路都用精度为1%的电容.如有困难,可以取出100个所需值的电容.然后用一电容表.或万用表的电容挡,选取20个最接近标称值的电容.二个直流稳压器可平放在印刷电路板上.但需注意不能互换,否则,可能使其损坏.最后,安装运放和RCA插座.至此,电路板安装完工.现在,即可接线至电源变压器,并装箱,具体可参阅图7.要特别注意电源接线,全部接线要加热缩套管,并用电缆夹固定引线,具体如图所示.另外,保险丝盒必须用市电保安型的.六,电压检查接下来可将印刷电路板暂时装入机箱,加电,用数字万用表检查已稳压的双电源.其值应为±15VDC.再检查每个TL074的引脚4,其上应有±15V,而每个集成块的儿脚应有一15V.现在可轻触每个集成块,看其是否发热——应当全是冷的.2006年第7期图6元件配置图下一步是用各个微调电位器来调整整个电路.调整过程很简单.只需将每个输出级在其通带内的增益调至1(即单位增益).这可以在三个频率处进行,例如,低音在100Hz,中音在1kHz.而高音则在12kHz.这时.需要有一个音频振荡器,还要一个交流频响达20kHz或更高的数字万用表.将音频振荡器接至一个声道的RCA输入连接器.其频率设定为100Hz,1kHz或12kHz,具体取决于要调试的频段.振荡器的输出电平设定为1Vs.现在测量所调试级输出端上的电平.对于高音输出,用10kHz,并调节微调电位器VR1(左声道)或VR4(右声道),使在输出端子上获得1V的信号电平.类似地,对于中音(中频段),用1kHz信号,调VR2(左声道)或VR5(右声道),使其输出端子上获得1Vs的信号电平.最后,对于低音,用100Hz,并调VR3(左声道)或VR6(右声道).调试输出电压完毕后,现在要做的就是整理机箱内部接线.准备将本装置接至放大器.七,功率放大器我们的H1一F1三路有源分频器现在已经制作完成了(见题图),要真正体验其实际效果必须与功率放大器配用,这里需要六个放大器,高音,中音,低音各一个,因为是立体声,为双声道,所以还得乘2.那么,究竟需要用什么样的功率放大器呢典型的情况是,低音放大器所需的功率为中音和高音放大2006年第7期带指示的电源开关图7接线图高音输人中音输入低音输入图8加法器电路输出器输出功率的二倍.为什么呢原因很简单,因为低音扬声器的灵敏度比较低.所以,如果需要为你的三路扬声器系统每个声道配置IOOW~,则还需为低音扬声器配置两个1OOW放大器(一个声道一个),当然,你也可以将两个为中音和高音配置的功率放大器改为5OW.这样,撤下的放大器可以用于维修,随时可以替换功率不足"的现场放大器.八,接入系统本装置可以方便地接入音响系统.其步序很简单,首先将3路有源分频器的立体声输出接至相应的低音,中音和高音立体声放大器的输入端,然后将各放大器的输出直接接至音箱内相应的各个扬声器.当然,在音箱内原有的无源分频网络必须拆开,同时,在音箱背面另外再装两组接线端子. 所有放大器的音调控制十分平整(虽然对高,中,低音调的嗜好不尽相同, 但高音控制决不会过多影响低音放大器,低音控制也决不会影响高音放大器).最后.音量控制可以分别调节,以获得低,中,高扬声器之间的最佳平衡.附:技术特性电压增益:1(单位增益)频率响应:10Hz至20kHz频段内为±1%(见图5)滤波器衰减斜率:24db/倍频程总谐波失真:在1V输出时为0.003%(典型值)信噪比:对于1V输出在22Hz至22kHz频段内,未加权时为-94dB声道隔离:在10Hz至20kHz频段内,通常好-t--lOOdB输入阻抗:47kQ输出阻抗:小-t-200~囫表1:R,C值RC2R交叉频率(kQ)(nF)(kQ)(Hz)15473O16O15393O1921247242OO11472221815333O2271O472O23912392424O15273O278 1233242841O392O289 11332231O 7.54715319 15223O341 1O332O341 122724347 112722379 7.53915385 1O272O417 122224426 7.53315455 1122224651O222O512 7.52715556 7.52215682 154.73O1596 153.93O1924 124.7241995 114.7222177 153.33O2274 1O4.72O2394 123.9242405 113.9222623 152.73O2779 123.3242842 1O3.92O2886 113.32231OO152.23O3410 1O3.32O3410 122.7243473 112.7223789 7.53.9153848 1O2.72O4168 122.2244263 7.53.3154547 112.222465O 1O2.22O5115 7.52.7155558 7.52.2156821 2o嘶年第7期\_●L。

目录一.设计题目 (2)二.题目功能与要求 (2)1功能 (2)2.要求 (2)三.整体方案设计 (3)方框图子框图作用四.单元电路设计 (4)1.低通滤波器2.高通滤波器3.带通滤波器五.整体电路分析 (6)1.二阶有源低通电路图………………………………………………………(6 )2.二阶有源高通带你路途 (6)3.二阶有源带通电路图 (7)六.元器件明细 (8)七.设计结果验证 (9)八.电路说明书 (11)九.心得体会 (12)十.参考文献 (13)一.设计题目:三分频选频电路二.设计功能与要求功能:由RC元件与运算放大器组成的滤波器称为RC有源滤波器,其功能是让必然频率范围内的信号通过,抑制或急剧衰减此频率范围之外的信号,因受运算放大器带宽限制,这种滤波器仅适用于低频范围,依照频率范围可将其分为低通、高通、带通与带阻四种滤波器要求:(1)别离设计二阶RC低通、高通、带通滤波器电路,计算电路元件参数,拟定测试方案和步骤;(2)在面包板或全能板上安装好电路,测量并调整静态工作点;(3)测量技术指标参数。

三.总体方案设计1.方案框图RC有源滤波总框图2.子框图的作用1.RC网络的作用在电路中RC网络起着滤波的作用,滤掉不需要的信号,如此在对波形的选取上起着相当重要的作用,通常要紧由电阻和电容组成。

2 . 放大器的作用电路中运用了同相输入运放,其闭环增益 RVF=1+R4/R3同相放大器具有输入阻抗超级高,输出阻抗很低的特点,普遍用于前置放大级。

3.反馈网络的作用将输出信号的一部份或全数通过牧电路印象输入端,称为反馈,其中的电路称为反馈网络,反馈网络分为正、负反馈。

四.单元电路设计1. 低通滤波器低通滤波器电路图 传输函数依照202200/)()()(ωωω++==Q s s A s U s U s H i () f0=有 R1=Rf Rc= 取 R1=1K C=因此RF=1K,R=.2 . 高通滤波器高通滤波器电路图 传输函数二阶高通滤波器参数的确信:依照202200/)()()(ωωω++==Q s s A s U s U s H i f0=得 RF=4R1 RC= 取 R1= C=1UF 因此 RF= R=3. 带通滤波器带通滤波器电路图 传输函数二阶带通滤波器参数的确信:依照202000//)()()(ωωω++==Q s s Qs A s U s U s H i f0=得 RC= R0=取 R1=R2=R3=R C=1UF R0= 因此 R1=R2=R3= RF= C1=C2=C=1UF.五.整体电路分析依照上面的参数,用EWB 设计出如下的电路图1).二阶低通滤波器电路图图其中R1=1 k Ω R=300Ω RF= k Ω C=μ 电源电压为100Mv/60 Hz 其上限截止频率为12H f RCπ==1690 Hz 仿真波形仿真后取得幅频特性曲线为2).二阶高通滤波器电路图其中R1=200Ω R2=R3=570Ω RF=800Ω C=1μF电源电压为100Mv/60Hz 其上限中心频率为12H f RCπ==77 Hz 仿真波形:仿真后取得幅频特性曲线为3).二阶带通滤波器电路图其R1=R2=R3=200ΩR0=300ΩRf=500ΩC=1μF 电源电压为100Mv/60Hz仿真波形:仿真后取得幅频特性曲线为六.元器件明细名称数量名称数量1 kΩ电阻 3 2kΩ电阻 2 1UF 4 kΩ电阻 1 741芯片 3 kΩ电阻 4 万能板 1kΩ电阻 1 电烙铁 1kΩ电阻 2 电脑 1 七.设计结果验证实践说明,一个电子装置,即便依照设计的电路参数进行安装往往也难于达到预期成效。

always@( negedge resetn or posedge clk or negedge clk) begin

if (resetn==1'b0)

begin

counter[2:0]<=3'd0;

out_clk<=1'b0;

end

else

begin

if (counter[2:0]==3'd5)

begin

counter[2:0]<=3'd0;

end

else

beign

counter[2:0]<= counter[2:0]+1;

end

////////////////////////////////////////////////////

if (counter[2:0]==3'd5 || counter[2:0]==3'd2)

begin

out_clk<=~out_clk;

end

end

end

其仿真结果是正确的

这个逻辑无法综合。

存在半导体工艺问题。

2.下面给出一个逻辑图。

逻辑是用器件画出来的,保证不存在物理上的实现问题。

仿真图如下:

也许有人要问,既然仿真都是对的,那么为什么要说实际中是80%工作呢?

看到波形图上的clk1(黄色)上的那些毛刺了么,毛刺并不可怕,但是这个电路工作的基础却是那些毛刺,准确地说,那些毛刺是必须有的,是工作过程的比不可少的部份。

这样的电路是否能正常工作就很让人匪夷所思了。

我们能不能让电路的正常功能不依赖于毛刺呢?

小结一下:

以上的思路都是试图在输入的clk上做改造,试图在恰当的地

方取正沿,恰当的地方取反沿。

但是要知道,这一定会导致竞争和冒险。

虽然逻辑上是可性的,但是实践中却没有那么简单。

这个时候,我们需要调整一下思路了:

能不能营造一个安全的时机来切换时钟沿的选择?显然,这需要在切换时钟沿时,强制时钟输出固定电平,当切换完成后,在取消这个强制条件。

对么?我们来试试看。

3. 看看以下的代码,也是一段有趣的东西。

always@(negedge resetn or posedge clk)

begin

if (resetn==1'b0)

begin

cnt1[1:0]<=2'd0;

end

else

begin

if(cnt1[1:0]==2'd2)

begin

cnt1[1:0]<=2'd0;

end

else

begin

cnt1[1:0]<=cnt1[1:0]+1;

end

end

end

always@(negedge resetn or negedge clk)

begin

if (resetn==1'b0)

begin

cnt2[1:0]<=2'd0;

end

else

begin

if(cnt2[1:0]==2'd2)

begin

cnt2[1:0]<=2'd0;

end

else

begin

cnt2[1:0]<=cnt2[1:0]+1;

end

end

end

always@*

begin

if (cnt1[1:0]==2'd2 || cnt2[1:0]==2'd0)

begin

clk1 = 1'b0;

end

else if (cnt1[1:0]==1'b1)

begin

clk1 = ~clk;

end

else

begin

clk1 = clk;

end

end

always@(negedge resetn or posedge clk1)

begin

if (resetn==1'b0)

begin

clk_out<=1'b0;

end

else

begin

clk_out<=~clk_out;

end

end

最后用的时钟clk1是clk和clk的反,但是在切换之间加上的强制为0的逻辑。

这段代码肯定是可综合的,而且简单的约束一下时序就可以生产。

但重要的是看了这段逻辑后我们突然明白了一件事情:要想长生质量好的3分频时钟,我们似乎必须要用到clk的下降沿来做点控制逻辑,这是被反复求证后逼出来的(不知道其它人是否有同感)。

那么我们为什么不愿意用下降沿触发的的寄存器呢?因为有些库里可能没有这样的器件,而必须在时钟树上上加反向。

如果有下降沿的寄存器,那么今后的扫瞄链又要多一些麻烦,虽然这些麻烦都可以客服,但是作为一个成熟的工程师要明白:尽量不要给自己找麻烦。

在工程上,最平常的东西最可靠。

4. 到这里我们的命题似乎解决了,但是我们的思考还不应该停止。

既然我们要用clk的下降沿,呢就完全可以打破以前的思路,来看看这个新的手段能给我们带来什么。

always@(negedge resetn or posedge clk)

begin

if (resetn==1'b0)

begin

cnt1[1:0]<=2'd0;

clk1<=1'b0;

end

else

begin

if(cnt1[1:0]==2'd2)

begin

cnt1[1:0]<=2'd0;

clk1<=1'b1;

end

else

begin

cnt1[1:0]<=cnt1[1:0]+1;

clk1<=1'b0;

end

end

end

always@(negedge resetn or negedge clk)

begin

if (resetn==1'b0)

begin

clk2<=2'd0;

end

else

begin

clk2<=clk1;

end

end

assign clk_out = clk1 | clk2;

代码似乎更简单了,思路也完全变了。

这回的思路是:先做一个简单的3分频电路,然后再调整占空比。

以这个思路,所有的1/N分频都可以解决。