AT89C51并行加载DDS芯片AD9850的方法

- 格式:pdf

- 大小:418.53 KB

- 文档页数:3

基于89C51和AD9854的DDS高精度频率信号实现摘要:针对美国AD(Analog Devices) 公司生产的DDS 技术产品———AD9854 芯片的功能特点进行了介绍,在信号源设计中采用了ATMEL89C51单片机作为控制单片机实现高精度信号发生器。

并针对信号源的功能进行了C 语言程序设计,完成了软件设计实现.关键词:DDS 技术;AD9854 ;信号源;ATMEL89C51 ;程序控制目录摘要 (1)1.1 DDS基础3 (3)1.1.1DDS(直接数字式频率合成器)基本原理与结构 (3)1.1.2常用的可编程DDS结构 (4)1.1.3 频率合成器的技术指标 (4)1.1.4 DDS的调制特性 (5)2.1 AD9854和89C51的介绍和电路连接 (6)2.1.1 AD9854的介绍 (6)2.1.2.AT89C51的介绍 (7)2.1.3.AD9854与AT89C51的电路连接 (8)3.1 软件设计 (9)附录 (16)1.1DDS基础1.1.1 DDS(直接数字式频率合成器)基本原理与结构一.两种基本合成方式1)根据正弦函数关系式,按照一定的时间间隔利用计算机进行数字递推关系计算,求解瞬时正弦函数幅值并实时地送入数/模转换器,从而合成出所要求频率的正弦波信号。

优点:电路简单、成本低、合成信号频率的分辨率可做得很高等优点,缺点:受计算机速度的限制,合成信号频率较低,一般在几千赫兹左右;2)用硬件电路取代计算机的软件运算过程,即利用高速存储器将正弦波的M 个样品存在其中,然后以查表的方式按均匀的速率把这些样品输入到高速数/模转换器,变换成所设定频率的正弦波信号。

优点:采用高速存储器产生正弦波幅值数据,合成频率已可以做得很高,目前已达到数百兆赫。

使用最广泛。

图一.DDS基本结构框图DDS的输出频率f o和基准时钟f c、相位累加器长度N及频率控制字FSW 的关系为:f o= f c·FSW/2N。

AD9850/9851DDS电路使用说明书江苏省无线电运动协会2007年4月9850/9851DDS电路简介AD9850/9851DDS电路是专为业余无线电电台设计的,它提供本机振荡信号和波段控制信号,特别适合做自制电台的本振源及老电台改造。

本电路使用有背光1602型通用液晶显示器,显示接收频率及工作模式。

电路大部分元器件为贴片封装,体积小,便于安装(PCB尺寸:36*93mm)。

在满足基本应用的条件下尽量简化设计,以提高性价比。

本电路可以使用AD9850(时钟100MHz)或AD9851(时钟20MHz)芯片,由用户设置。

中频频率可以由用户任意设置。

波段控制输出可以选择4波段或9波段,由用户设置。

所有设置均由软件实现并保存在芯片内。

关机前的工作频率将被保存,下次开机将工作在这个频率。

为简化电路,10MHz以下设计为高本振、10MHz以上为低本振,这样只要一个插入载频即可以完成对10MHz以下的LSB解调和10MHz以上的USB解调。

也可以选择本振减中频的模式(本振总是减中频、DDS输出减中频=接收频率)。

主要功能如下:1.频率范围:0.1-40MHz2.频率分辨率:10Hz3.频率步进:10Hz、100Hz、1KHz、10KHz、100KHz、1MHz4.存储频点:20个存储频点可由用户任意设置。

5.显示模式:USB、LSB、CW、AM、FM6.接收频率微调:具有加减80KHz的接收频率微调功能。

7.收发转换:两种发信方式:普通方式和CW方式。

8.电源:电压8-12V DC,电流约180mA(背光打开),110mA(背光关闭)。

其他功能:1.频率校正:对DDS芯片的基准频率误差可通过软件设置校正。

2.边带切换:当选择了+-IF的模式时上下边带自动切换,10MHz以下为LSB、10MHz以上为USB,。

CW发信方式是利用了DDS的特点而特别设计的,如果选择这种方式,则发信时DDS将直接输出所需的频率而不需要任何频率变换,简化了发信电路。

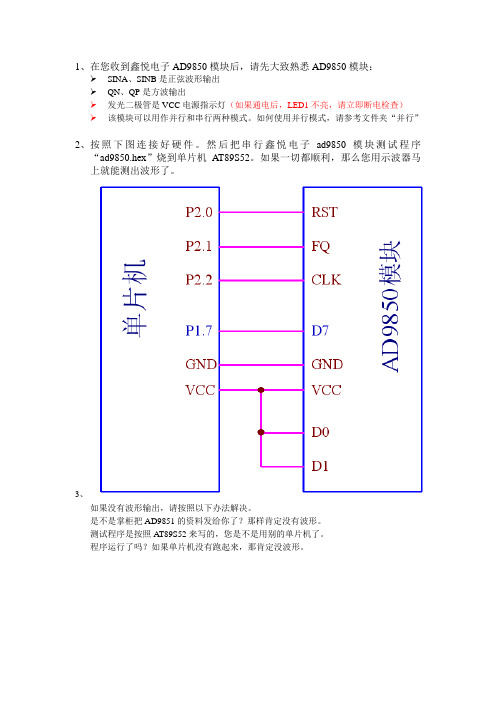

1、在您收到鑫悦电子AD9850模块后,请先大致熟悉AD9850模块:

SINA、SINB是正弦波形输出

QN、QP是方波输出

发光二极管是VCC电源指示灯(如果通电后,LED1不亮,请立即断电检查) 该模块可以用作并行和串行两种模式。

如何使用并行模式,请参考文件夹“并行”

2、按照下图连接好硬件。

然后把串行鑫悦电子ad9850模块测试程序

“ad9850.hex”烧到单片机AT89S52。

如果一切都顺利,那么您用示波器马上就能测出波形了。

3、

如果没有波形输出,请按照以下办法解决。

是不是掌柜把AD9851的资料发给你了?那样肯定没有波形。

测试程序是按照A T89S52来写的,您是不是用别的单片机了。

程序运行了吗?如果单片机没有跑起来,那肯定没波形。

一种基于DDS芯片AD9850的信号源摘要:直接数字合成(DDS)是一种重要的频率合成技术,具有分辨率高、频率变换快等优点,在雷达及通信等领域有着广泛的应用前景。

文中介绍了一种高性能DDS芯片AD9850的基本原理和工作特点,阐述了如何利用此芯片设计一种频率在0~50 kHz内变化、相位正交的信号源,给出了AD9850芯片和MCS51单片机的硬件接口和软件流程。

关键词:直接数字频率合成;信号源;AD9850芯片;设计一、引言随着数字技术的飞速发展,高精度大动态范围数字/模拟(D/A)转换器的出现和广泛应用,用数字控制方法从一个标准参考频率源产生多个频率信号的技术,即直接数字合成(DDS)技术异军突起。

其主要优点有:(1)频率转换快:DDS频率转换时间短,一般在纳秒级;(2)分辨率高:大多数DDS可提供的频率分辨率在1 Hz数量级,许多可达0.001 Hz;(3)频率合成范围宽;(4)相位噪声低,信号纯度高;(5)可控制相位:DDS可方便地控制输出信号的相位,在频率变换时也能保持相位联系;(6)生成的正弦/余弦信号正交特性好等。

因此,利用DDS技术特别容易产生频率快速转换、分辨率高、相位可控的信号,这在电子测量、雷达系统、调频通信、电子对抗等领域具有十分广泛的应用前景。

美国AD公司推出的高集成度频率合成芯片AD9850就是采用DDS技术的典型产品之一。

针对DDS的上述特点,本文基于AD9850器件设计了一种信号源,用来产生两路相位正交、频率可在0~50 kHz范围变化、分辨率为1 Hz 的正弦波信号,并给出了AD9850芯片的工作原理和信号源设计的硬件接口电路及软件设计流程。

二、AD9850芯片介绍AD9850是AD公司生产的最高时钟为125 MHz、采用先进的CMOS技术的直接频率合成器,主要由可编程DDS系统、高性能模数变换器(DAC)和高速比较器3部分构成,能实现全数字编程控制的频率合成,并具有时钟产生功能,其原理框图如图1所示。

DDS芯片AD9850的工作原理及其与单片机的接口作者:武汉空军雷达学院石雄杨加功彭世蕤来源:《国外电子元器件》摘要:介绍了美国AD公司采用先进的直接数字频率合成(DDS)技术推出的高集成度频率合成器AD9850的工作原理、主要特点及其与MCS51单片机的接口,并给出了接口电路图和部分源程序。

关键词:直接数字频率合成(DDS)控制字控制时序接口 AD98501 AD9850简介随着数字技术的飞速发展,用数字控制方法从一个参考频率源产生多种频率的技术,即直接数字频率合成(DDS)技术异军突起。

美国AD公司推出的高集成度频率合成器AD9850便是采用DDS技术的典型产品之一。

AD9850采用先地蝗CMOS工艺,其功耗在3.3V供电时仅为155mW,扩展工业级温度范围为-40~80℃,采用28脚SSOP表面封装形式。

AD9850的引脚排列如图1所示,图2为其组成框图。

图2中层虚线内是一个完整的可编程DDS系统,外层虚线内包含了AD9850的主要组成部分。

AD9850内含可编程DDS系统和高速比较器,能实现全数字编程控制的频率合成。

可编程DDS系统的核心是相位累加器,它由一个加法器和一个N位相位寄存器组成,N一般为24~32。

每来一个外部参考时钟,相位寄存器便以步长M递加。

相位寄存器的输出与相位控制字相加后可输入到正弦查询表地址上。

正弦查询表包含一个正弦波周期的数字幅度信息,每一个地址对应正弦波中0°~360°范围的一个相位点。

查询表把输入地址的相位信息映射成正弦波幅度信号,然后驱动DAC以输出模式量。

相位寄存器每过2N/M个外部参考时钟后返回到初始状态一次,相位地正弦查询表每消费品一个循环也回到初始位置,从而使整个DDS系统输出一个正弦波。

输出的正弦波周期To=Tc2N/M,频率fout=Mfc/2N,Tc、fc分别为外部参考时钟的周期和频率。

AD9850采用32位的相位累加器将信号截断成14位输入到正弦查询表,查询表的输出再被截断成10位后输入到DAC,DAC再输出两个互补的电流。

应用笔记AN-587One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106 • 电话:781/329-4700 • 传真:781/326-8703 • 同步多个基于DDS 的频率合成器AD9850/AD9851作者:David Brandon ,ADI最佳布局简介许多应用要求产生两个或更多具有已知相位关系(如正交)的正弦波信号。

ADI 公司的AD9850和AD9851 DDS IC 能够提供这种信号。

本应用笔记详细说明了如何使两个或更多该器件同步,同时考虑了可能的相位误差源。

参考时钟(REF CLOCK)成功同步多个AD9850/AD9851的首要要求是所有DDS 的R EF CLK 输入之间的相位误差必须达到最小。

R EF CLK 边沿之间的任何相位差异都会导致DDS 输出处出现成比例的相位差异。

用户必须审慎考虑时钟分配在电路板PCB 上的布局,以确保REF CLK 边沿同步(见图1)。

AD9850/AD9851 R EF CLK 输入电路采用单端设计,因此,R EF CLK 必须具有最小的输入抖动和较短的上升/下降时间(建议5 ns 以下)。

R EF CLK 边沿上升时间较长会导致误差,因为输入电路的电压跳变点因器件不同而异。

这些属性同样适用于W_CLK 和FQ_UD 输入。

AD9850/AD9851 I/O 访问详情拥有边沿快速且路径适当的R EF CLK 信号之后,下一个时序要求是数据必须同步传输至DDS 程序寄存器。

FQ_UD 信号将数据传输至DDS 内核。

同步多个DDS 要求FQ_UD 的上升沿同时发生在所有DDS 上,如同EF CLK 一样。

另外,FQ_UD 必须发生在相对REF CLK 而言的适当时间。

图1. REF CLK 的分配AN-587图2. AD9850/AD9851功能框图图2为AD9850/AD9851的功能框图,两种器件之间仅存在较小差异。