复旦大学模拟电路二级运放实例

- 格式:pdf

- 大小:1.65 MB

- 文档页数:89

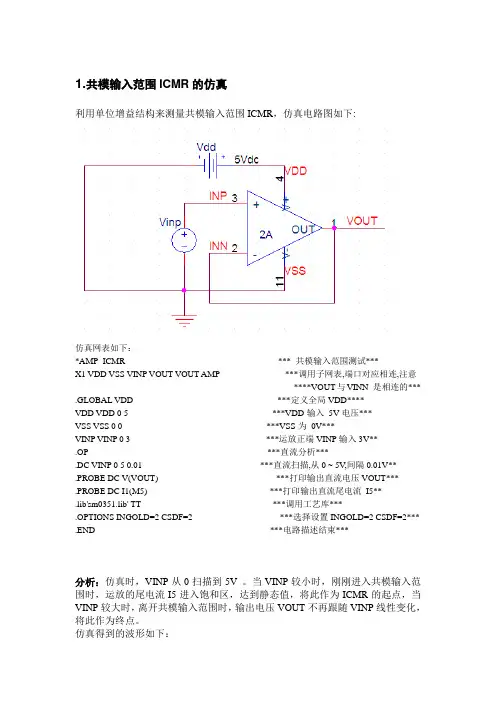

1.共模输入范围ICMR的仿真利用单位增益结构来测量共模输入范围ICMR,仿真电路图如下:仿真网表如下:*AMP_ICMR *** 共模输入范围测试***X1 VDD VSS VINP VOUT VOUT AMP ***调用子网表,端口对应相连,注意****VOUT与VINN 是相连的*** .GLOBAL VDD ***定义全局VDD****VDD VDD 0 5 ***VDD输入5V电压***VSS VSS 0 0 ***VSS为0V***VINP VINP 0 3 ***运放正端VINP输入3V**.OP ***直流分析***.DC VINP 0 5 0.01 ***直流扫描,从0 ~ 5V,间隔0.01V**.PROBE DC V(VOUT) ***打印输出直流电压VOUT***.PROBE DC I1(M5) ***打印输出直流尾电流I5**.lib'sm0351.lib' TT ***调用工艺库***.OPTIONS INGOLD=2 CSDF=2 ***选择设置INGOLD=2 CSDF=2*** .END ***电路描述结束***分析:仿真时,VINP从0扫描到5V 。

当VINP较小时,刚刚进入共模输入范围时,运放的尾电流I5进入饱和区,达到静态值,将此作为ICMR的起点,当VINP较大时,离开共模输入范围时,输出电压VOUT不再跟随VINP线性变化,将此作为终点。

仿真得到的波形如下:(输出VOUT)(运放尾电流I5)结果分析:从波形可以看出,当尾电流I5进入饱和区时,输出电压为1.5V,当输出电压不再跟随输入VINP线性变化时,输出电压值为4.6V。

满足设计要求。

2.输出电压范围的仿真在单位增益中,传输曲线的线性受到ICMR的限制,在高增益下结构下,输出曲线的线性部分与放大器的输出电压范围一致,下面采用增益为10的结构电路图仿真:仿真网表如下:*AMP_AMP_OUTPUT **输出摆幅测试**X1 VDD VSS VINP VINN VOUT AMP ***调用子网表,端口与子网对应相连*** R1 VINN 0 10K ***在运放负输入端和地之间接10K电阻** R2 VOUT VINN 90K ***运放输出端和负输入端接90K电阻** .GLOBAL VDD ***定义全局VDD****VDD VDD 0 5 ***VDD输入5V电压***VSS VSS 0 0 ***VSS为0V***VINP VINP 0 2 ***运放正端VINP输入2V**.OP ***直流分析***.DC VINP 0 5 0.01 ***直流扫描,从0 ~ 5V,间隔0.01V**.PROBE V(VOUT) ***打印输出电压VOUT***.lib'sm0351.lib' TT ***调用工艺库***.OPTIONS INGOLD=2 CSDF=2 ***选择设置INGOLD=2 CSDF=2***.END ***电路描述结束***分析:当直流电压VINP从0扫面到5V时,得到输出电压的波形如下:结果分析:个从仿真结果大致可以看出,输出电压范围与曲线中增益为10的线性范围一致的条件下得到输出电压范围在500mVd到4.8V之间,基本满足设计要求。

《IC设计实践》报告姓名:潘阿成学号:200881229院系:电子科学与技术学院专业:集成电路设计与集成系统2012年2月25日目录一、设计目标 (1)二、设计平台 (1)三、原理图设计 (1)1、电路结构与工作原理 (1)2、手工计算电路参数 (2)3、仿真、分析与参数调整 (6)4、电路参数仿真结果汇总 (14)四、版图设计 (15)1、版图层次及常用设计规则 (15)2、DRC验证与版图修改 (16)3、LVS验证与版图修改 (17)五、寄生参数提取与后仿真 (117)六、小结 (19)一、设计目标通过使用mentor软件设计一个两级运算放大器,并且使其满足以下指标,如表1所示。

电源电压VDD 5V 共模抑制比CMRR >60dB直流增益Av >60dB 电源抑制比PSRR >60dB 单位增益带宽GB >5MHz 负载电容CL 8pF输入共模范围ICMR 2~4.5V 沟道长L >0.5um输出摆率V out 2~4.8V 功耗P <2mW压摆率SR >10V/us表1 运算放大器设计指标二、设计平台mentor软件及华润上华工艺库0.5um P衬底N阱双多晶硅三层金属混合信号工艺。

三、原理图设计1、电路结构与工作原理电路结构如图1所示。

图1 二级运放电路结构该电路的组成与工作原理:图1中有多个电流镜结构,M5的电流在M1与M2组成的差分对中被平分,流过M1的电流与流过M2电流1,23,45/2d d d I I I ==,同时M3,M4组成电流镜结构,如果M3和M4管对称,那么相同的结构使得在x ,y 两点的电压在Vin 的共模输入范围内不随着Vin 的变化而变化,为第二极放大器提供了恒定的电压和电流。

图1所示,Cc 为引入的米勒补偿电容。

2、手工计算电路参数本次实践使用的工艺是华润上华工艺库0.5um P 衬底N 阱双多晶硅三层金属混合信号工艺。

实验一、两级运算放大器的仿真验证一、实验目的1、学习集成运算电路单元的设计参数的仿真、测试、验证。

2、学习采用Cadence工具实现IC电路设计的基本操作和方法,包括电路图的编辑以及仿真调试过程。

二、实验内容本实验通过设计一个两级运算放大器电路学习Cadence工具下电路的设计和仿真方法。

实验内容包括:1.熟悉Cadence界面及基本的建立新的cell文件等基本过程;2.完成两级运算放大器电路的设计;3.利用Cadence的仿真环境得到波形,分析仿真结果。

该电路设计采用上华CSMC0.5umCMOS工艺设计,工作电压5V。

三、实验原理运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路。

1.共模抑制比:差分放大电路抑制共模信号及放大差模信号的能力,常用共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电压放大倍数Aud与对共模信号的电压放大倍数Auc之比,称为共模抑制比,英文全称是Common Mode Rejection Ratio,因此一般用简写CMRR来表示,符号为Kcmr,单位是分贝db。

2.共模输入范围:是指在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。

3.电源抑制比:是输入电源变化量(以伏为单位)与转换器输出变化量(以伏为单位)的比值(PSRR),常用分贝表示。

通常把满量程电压变化的百分数与电源电压变化的百分数之比称为电源抑制比。

1前言12二级运算放大器电路 12.1电路结构 12.2设计指标 23 Cadence仿真软件 33.1 schematic原理图绘制 33.2 生成测试电路 33.3 电路的仿真与分析 43.1.1直流仿真 43.1.2交流仿真 43.4 版图绘制 53.4.1差分对版图设计 63.4.2电流源版图设计 73.4.3负载MOS管版图设计 73.5 DRC & LVS版图验证 83.5.1 DRC验证 83.5.2 LVS验证 8 4结论 95参考文献 9本文利用cadence软件简述了二级运算放大器的电路仿真和版图设计。

以传统的二级运算放大器为例,在ADE电路仿真中实现0.16umCMOS工艺,输入直流电源为5v,直流电流源范围27~50uA,根据电路知识,设置各个MOS管合适的宽长比,调节弥勒电容的大小,进入stectre仿真使运放增益达到40db,截止带宽达到80MHz和相位裕度至少为60。

版图设计要求DRC验证0错误,LVS验证使电路图与提取的版图相匹配,观看输出报告,要求验证比对结果一一对应。

关键词:cadence仿真,设计指标,版图验证。

AbstractIn this paper, the circuit simulation and layout design of two stage operational amplifier are briefly described by using cadence software. In the traditional two stage operational amplifier as an example, the realization of 0.16umCMOS technology in ADE circuit simulation, the input DC power supply 5V DC current source 27~50uA, according to the circuit knowledge, set up each MOS tube suitable ratio of width and length, the size of the capacitor into the regulation of Maitreya, the simulation of stectre amplifier gain reaches 40dB, the cut-off bandwidth reaches 80MHz and the phase margin of at least 60.. The layout design requires DRC to verify 0 errors, and LVS validation makes the circuit map matching the extracted layout, viewing the output report, and requiring verification to verify the comparison results one by one.Key words: cadence simulation, design index, layout verification.1前言近几年来,人们已投入很大力量研究版图设计自动化,计算机辅助设计方法学在给定所需功能行为描述的数字系统设计自动化方面已经非常成功。

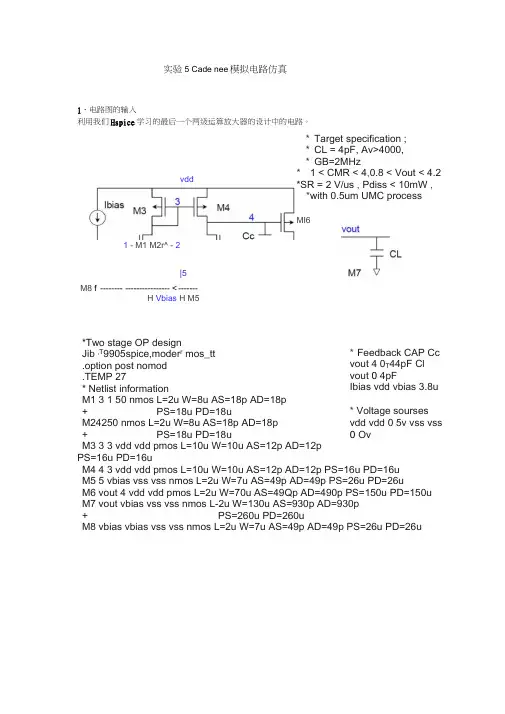

实验5 Cade nee 模拟电路仿真1、电路图的输入利用我们Hspice 学习的最后一个两级运算放大器的设计中的电路。

* Target specification ; * CL = 4pF, Av>4000, * GB=2MHz* 1 < CMR < 4,0.8 < Vout < 4.2 *SR = 2 V/us , Pdiss < 10mW , * w ith 0.5um UMC processMI6*Two stage OP designJib ,T 9905spice,moder r mos_tt.option post nomod.TEMP 27* Netlist informationM1 3 1 50 nmos L=2u W=8u AS=18p AD=18p+ PS=18u PD=18uM24250 nmos L=2u W=8u AS=18p AD=18p+ PS=18u PD=18u M3 3 3 vdd vdd pmos L=10u W=10u AS=12p AD=12p PS=16u PD=16uM4 4 3 vdd vdd pmos L=10u W=10u AS=12p AD=12p PS=16u PD=16u M5 5 vbias vss vss nmos L=2u W=7u AS=49p AD=49p PS=26u PD=26uM6 vout 4 vdd vdd pmos L=2u W=70u AS=49Qp AD=490p PS=150u PD=150u M7 vout vbias vss vss nmos L-2u W=130u AS=930p AD=930p + PS=260u PD=260uM8 vbias vbias vss vss nmos L=2u W=7u AS=49p AD=49p PS=26u PD=26u* Feedback CAP Cc vout 4 0T 44pF Cl vout 0 4pF Ibias vdd vbias 3.8u * Voltage sourses vdd vdd 0 5v vss vss 0 Ov vdd1 - M1 M2r^ - 2|5M8 f -------- ---------------- < -------H Vbias H M5vin2 2 0 2.5v vin1 1 ODC 2+5v AC 1 *.OP* AC Analysis function .ac dec 10 10 100MEG .probe ac vdb(vout)+ vp(vout) vdb(4)vp(4) .meas ac Uriit_gain + when vdb(vout)=0 .meas ac phase_mar + FIND vp(vout) when vdb(vout)=0* Transient analysis sectionM1 3 vout 5 0 nmos L=2u W=8u AS=18p AD=18p PS=18u PD=18u vin2 2 0 pulse(0v 5v 1n 1p 1p 600n 1200n) .tran 5n 2u对该运放的电路进行输入,仿真模型利用 Oban 中提供的模型文件。

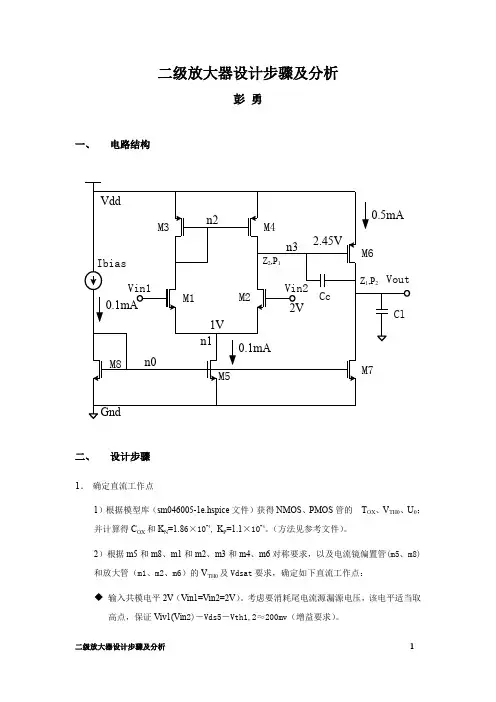

基本两级运放设计一、实验要求电源电压2.7V,CMR在0.2—1.5v之间,增益大于80db,转换速率大于10v/us,单位增益带宽大于10M,输出电压范围0.3v—2.4v之间。

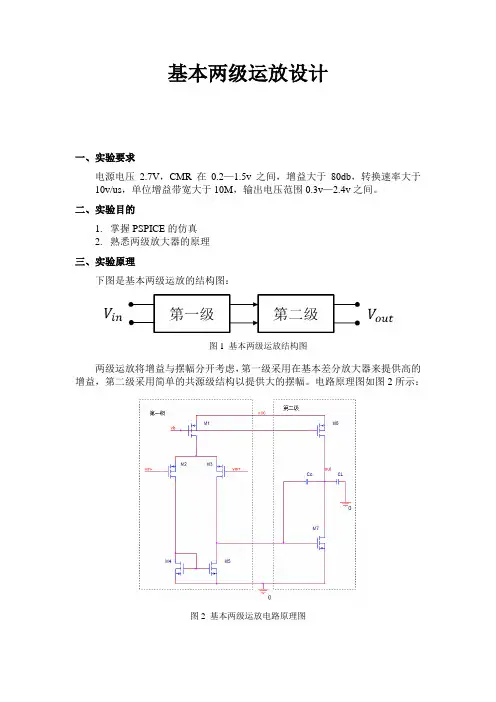

二、实验目的1.掌握PSPICE的仿真2.熟悉两级放大器的原理三、实验原理下图是基本两级运放的结构图:图1 基本两级运放结构图两级运放将增益与摆幅分开考虑,第一级采用在基本差分放大器来提供高的增益,第二级采用简单的共源级结构以提供大的摆幅。

电路原理图如图2所示:图2 基本两级运放电路原理图● 输入共模电压范围:由M1管饱和条件SD on V V ≥,得到:2112(||)||CC incm TP on on incm CC TP on on V V V V V V V V V V -++⇒---≥≤ 由M2管饱和条件SD on V V ≥,得到:66||||GS incm TP incm GS TP V V V V V V +⇒-≤≥ 取150.2V on on V V = ,,||0.67V TP V =,0.45V TN V =输入共模电压范围为:0V 1.63V incm V ≤≤ ● 输出摆幅:由M6管和M7管的饱和条件DS on V V ≥,得到76on out CC on V V V V -≤≤取670.2V on on V V ==,得到输出摆幅为:0.2V 2.5V out V ≤≤ 四、实验步骤 1、 增益带宽仿真电路图如图3所示:图3 增益带宽仿真电路图通过给定的偏置电流值设置好各个MOS 管和晶体管的参数,然后对整个电路进行交流仿真(AC Sweep ),得到仿真曲线图如图4所示:Frequency1.0Hz 3.0Hz 10Hz30Hz 100Hz 300Hz 1.0KHz 3.0KHz 10KHz 30KHz 100KHz 300KHz 1.0MHz 3.0MHz 10MHz 30MHz 100MHz 300MHz 1.0GHzVDB(OUTDM)VP(OUTDM)-500-400-300-200-100-0100(11.587M,-118.037)(11.587M,-17.185m)(1.0410K,78.264)(2.8411,81.320)图4 交流仿真波特图从上图中,可以看出,该电路的增益81.3d A dB =,带宽为1.04K ,单位增益带宽11.6GB MHz =,相位余度为62°。