计算机组成原理第8章

- 格式:ppt

- 大小:1.18 MB

- 文档页数:144

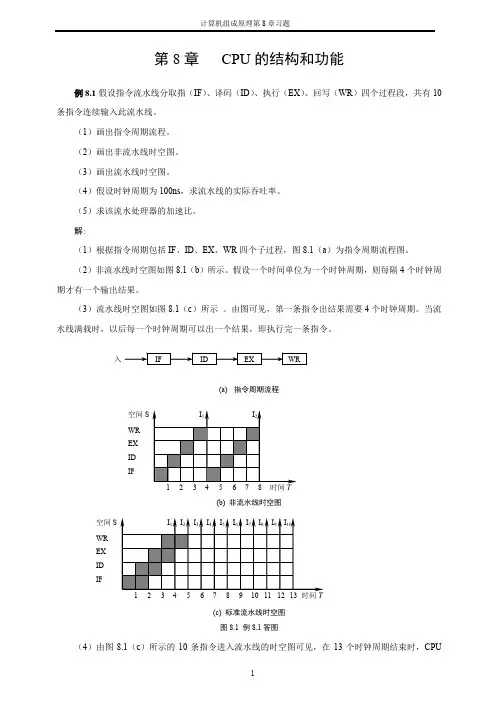

第8章CPU的结构和功能例8.1假设指令流水线分取指(IF)、译码(ID)、执行(EX)、回写(WR)四个过程段,共有10条指令连续输入此流水线。

(1)画出指令周期流程。

(2)画出非流水线时空图。

(3)画出流水线时空图。

(4)假设时钟周期为100ns,求流水线的实际吞吐率。

(5)求该流水处理器的加速比。

解:(1)根据指令周期包括IF、ID、EX、WR四个子过程,图8.1(a)为指令周期流程图。

(2)非流水线时空图如图8.1(b)所示。

假设一个时间单位为一个时钟周期,则每隔4个时钟周期才有一个输出结果。

(3)流水线时空图如图8.1(c)所示。

由图可见,第一条指令出结果需要4个时钟周期。

当流水线满载时,以后每一个时钟周期可以出一个结果,即执行完一条指令。

(a)指令周期流程(b) 非流水线时空图(c) 标准流水线时空图图8.1 例8.1答图(4)由图8.1(c)所示的10条指令进入流水线的时空图可见,在13个时钟周期结束时,CPU执行完10条指令,故实际吞吐率为:10/(100ns×13) ≈ 0.77×107条指令/秒(5)在流水处理器中,当任务饱满时,指令不断输入流水线,不论是几级流水线,每隔一个时钟周期都输出一个结果。

对于本题四级流水线而言,处理10条指令所需的时钟周期数为T4 = 4 +(10 −1)= 13。

而非流水线处理10条指令需4×10 = 40个时钟周期。

故该流水处理器的加速比为40 ÷13 ≈ 3.08 例8.2设某机有四个中断源1、2、3、4,其硬件排队优先次序按1→2→3→4降序排列,各中断源的服务程序中所对应的屏蔽字如表8.1所示。

表8.1 例8.2各中断源对应的屏蔽字中断源 屏蔽字1 2 3 41 1 1 0 12 0 1 0 03 1 1 1 14 0 1 0 1(1)给出上述四个中断源的中断处理次序。

(2)若四个中断源同时有中断请求,画出CPU执行程序的轨迹。

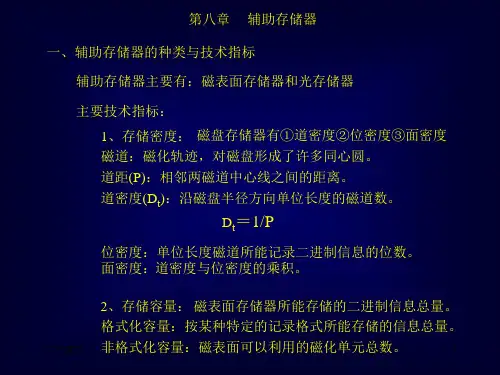

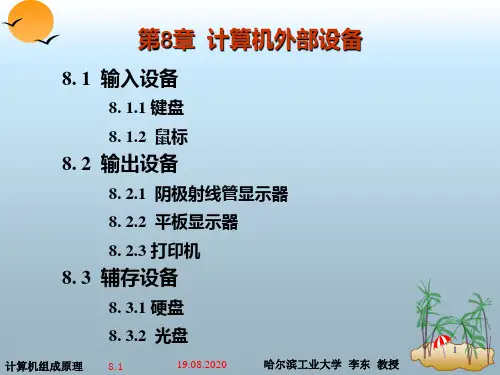

第八章CPU 的结构和功能8.1 CPU 的结构8.2 指令周期8.3 指令流水8.4 中断系统8.1 CPU 的结构一、CPU 的功能取指令分析指令执行指令,发出各种操作命令控制程序输入及结果的输出总线管理处理异常情况和特殊请求1. 控制器的功能2. 运算器的功能实现算术运算和逻辑运算指令控制操作控制时间控制数据加工处理中断二、CPU 结构框图PC IR指令控制操作控制时间控制数据加工处理中断ALU 寄存器中断系统1. CPU 与系统总线CU 时序电路寄存器ALU中断系统CUCPU控制总线数据总线地址总线8.12. CPU 的内部结构算术和布尔逻辑取反移位状态标志内部数据总线C P U 寄存器CU 中断系统ALU 控制信号…8.11. 用户可见寄存器(1) 通用寄存器三、CPU 的寄存器存放操作数可作某种寻址方式所需的专用寄存器(2) 数据寄存器存放操作数(满足各种数据类型)两个寄存器拼接存放双倍字长数据(3) 地址寄存器存放地址,其位数应满足最大的地址范围用于特殊的寻址方式段基值栈指针(4) 条件码寄存器存放条件码,可作程序分支的依据如正、负、零、溢出、进位等8.12. 控制和状态寄存器(1) 控制寄存器PC控制CPU 操作(2) 状态寄存器状态寄存器其中MAR MDR IR用户不可见存放条件码PSW 寄存器存放程序状态字PC用户可见3. 举例Z8000 8086 MC 68000MARMMDRIR8.1四、控制单元CU 和中断系统1. CU 产生全部指令的微操作命令序列组合逻辑设计微程序设计硬连线逻辑存储逻辑2. 中断系统参见第四篇五、ALU参见8.4参见第六章8.18.2 指令周期一、指令周期的基本概念1 . 指令周期取出并执行一条指令所需的全部时间完成一条指令执行取指、分析取指阶段取指周期执行阶段执行周期(取指、分析)(执行指令)指令周期取指周期执行周期2. 每条指令的指令周期不同取指周期指令周期取指周期执行阶段指令周期取指周期执行周期指令周期NOPADD mem MUL mem8.23. 具有间接寻址的指令周期4. 带有中断周期的指令周期取指周期间址周期指令周期执行周期取指周期间址周期指令周期执行周期中断周期8.25. 指令周期流程取指周期执行周期有间址吗?有中断吗?间址周期中断周期是是否否8.26. CPU 工作周期的标志CPU 访存有4 种性质取指令取地址取操作数存程序断点取指周期间址周期执行周期中断周期FEDINDDINTDCLK1FE1IND 1EX 1INTEXDCPU 的4个工作周期8.21. 取指周期数据流二、指令周期的数据流MDRCUMARPC存储器CPU 地址总线数据总线控制总线IR+18.22. 间址周期数据流CUMARCPU地址总线数据总线控制总线PCIR存储器MDR8.23. 执行周期数据流4 . 中断周期数据流不同指令的执行周期数据流不同MDRCUMARCPU 地址总线数据总线控制总线PC存储器8.28.3 指令流水一、如何提高机器速度1. 提高访存速度2. 提高I/O 和主机之间的传送速度•提高整机处理能力高速芯片Cache多体并行多总线DMAI/O 处理机通道高速器件改进系统结构,开发系统的并行性中断3. 提高运算器速度高速芯片改进算法快速进位链二、系统的并行性时间上互相重叠2. 并行性的等级指令级(指令之间)过程级(程序、进程)两个或两个以上事件在同一时刻发生两个或两个以上事件在同一时间段发生并行1. 并行的概念粗粒度软件实现细粒度硬件实现并发同时8.3取指令3执行指令3三、指令流水原理2. 指令的二级流水1. 指令的串行执行取指令取指令部件完成总有一个部件空闲指令预取若取指和执行阶段时间上完全重叠指令周期减半速度提高1 倍…执行指令执行指令部件完成取指令1执行指令1取指令2执行指令2取指令3执行指令3取指令2执行指令2取指令1执行指令18.3必须等上条指令执行结束,才能确定下条指令的地址造成时间损失3. 影响指令流水效率加倍的因素(1) 执行时间> 取指时间(2) 条件转移指令对指令流水的影响解决办法?取指令部件指令部件缓冲区执行指令部件猜测法8.34. 指令的六级流水六级流水14个时间单位串行执行 6 ×9 =54 时间单位完成一条指令 6 个时间单位CO FO EI WO DI FICOFOEIWODIFICO FO EI WODI FI CO FOEI WODIFICO FO EI WO DI FI CO FOEI WO DI FICO FO EI WODI FICO FO EI WO DI FICO FOEIWO DI FI指令1指令2指令3指令4指令5指令6指令7指令8指令91 2 3 4 5 6 7 8 9 10 11 12 13 14t8.3指令1 与指令4 冲突指令2 与指令5 冲突指令1、指令3、指令6 冲突……CO FO EI WODI FI CO FO EI WODI FI CO FO EI WODI FI CO FO EI WODI FICO FO EI WODI FI CO FO EI WODI FI CO FO EI WODI FICO FO EI WODI FICO FO EI WODI FI指令1指令2指令3指令4指令5指令6指令7指令8指令91 2 3 4 5 6 7 8 9 10 11 12 13 14t三、影响指令流水性能的因素1. 访存冲突解决办法• 指令存储器和数据存储器分开• 指令预取技术(适用于访存周期短的情况)8.32. 相关问题程序的相近指令之间出现某种关联使指令流水出现停顿影响流水线效率(1) 控制相关8.3WOEIFOCODIWO EI FO DI FIFIDI FICO FI FO CO DI FI WOEI FO CO DI FI DIFO EIWO EI FO CO FIDI CO WODIFICOFI指令1指令2指令3指令4指令5指令6指令7指令15指令161 2 3 4 5 6 7 8 9 10 11 12 13 14转移损失t设指令3 是转移指令BNE 指令必须等CPX 指令的结果才能判断出是转移还是顺序执行LDA # 0LDX # 0INX CPX #N BNE M DIV # N STA ANSADD X, DM(2) 数据相关几条相近的指令间,共用同一存储单元或同一寄存器时,会出现数据相关ADD R1,R2如:SUB R1,R3采用旁路技术解决办法寄存器组锁存器锁存器ALU8.3四、流水线的多发技术1. 超标量技术每个时钟周期内可并发多条独立指令不能调整指令的执行顺序配置多个功能部件通过编译优化技术,把可并行执行的指令搭配起来IF ID EX WR0 1 2 3 4 5 6 7 8 9 10 11 12 13t 8.32. 超流水技术在一个时钟周期内再分段(3 段)不能调整指令的执行顺序在一个时钟周期内一个功能部件使用多次(3 次)靠编译程序解决优化问题流水线速度是原来速度的3 倍IF ID EX WR0 1 2 3 4 5 6 7 8 9 10 11 12 13t 8.33. 超长指令字采用多个处理部件具有多个操作码字段的超长指令字(可达几百位) 由编译程序挖掘出指令间潜在的并行性,将多条能并行操作的指令组合成一条IF ID EX WR0 1 2 3 4 5 6 7 8 9 10 11 12 13t8.3五、流水线结构1. 指令流水线结构完成一条指令分7 段,每段需一个时钟周期若流水线不出现断流 1 个时钟周期出 1 结果不采用流水技术7 个时钟周期出 1 结果理想情况下,7 级流水的速度是不采用流水技术的7 倍地址形成部件指令译码部件取操作数部件取指令部件操作执行部件回写结果部件修改指令指针部件锁存锁存锁存锁存锁存锁存8.32. 运算流水线完成浮点加减运算可分对阶、尾数求和、规格化三段分段原则每段操作时间尽量一致锁存器对阶功能部件第一段尾数加部件锁存器第二段规格化部件锁存器第三段8.38.4 中断系统一、概述1. 引起中断的各种因素(1) 人为设置的中断(2) 程序性事故如转管指令溢出、操作码不能识别、除法非法(5) 外部事件(4) I/O 设备(3) 硬件故障用键盘中断现行程序转管指令………管理程序2. 中断系统需解决的问题(1) 各中断源如何向CPU 提出请求?(2) 各中断源同时提出请求怎么办?(5) 如何寻找入口地址?(4) 如何保护现场?(3) CPU 什么条件、什么时间、以什么方式响应中断?(6) 如何恢复现场,如何返回?(7) 处理中断的过程中又出现新的中断怎么办?硬件+软件8.4二、中断请求标记和中断判优逻辑1. 中断请求标记INTR一个请求源一个INTR 中断请求标记触发器多个INTR组成中断请求标记寄存器INTR 分散在各个中断源的接口电路中INTR 集中在CPU 的中断系统内12345n 掉电过热阶上溢内存读写校验错非法除法键盘打印机8.42. 中断判优逻辑①分散在各个中断源的接口电路中链式排队器②集中在CPU内(1) 硬件实现(排队器)1 11&1&1&参见第五章INTR1INTR2INTR3INTR4INTR1、INTR2 、INTR3 、INTR4优先级按降序排列INTP1INTP2INTP3INTP48.4A 、B 、C 优先级按降序排列(2) 软件实现(程序查询)否……是否A 请求?是否B 请求?是否C 请求?转A 的服务程序入口地址转B 的服务程序入口地址转C 的服务程序入口地址是是是否否8.4三、中断服务程序入口地址的寻找1. 硬件向量法入口地址200入口地址300入口地址40012 H 13 H 14 H主存12 H 13 H 14 HJMP 200JMP 300JMP400主存向量地址形成部件…………中断向量排队器输出向量地址12H 、13H 、14H入口地址200、300、4008.42. 软件查询法中断识别程序(入口地址M)地址说明指令MJMP 1# SR1# D = 1 转1# 服务程序SKP DZ 2# JMP 2# SR 2# D = 0 跳2# D = 1 转2# 服务程序SKP DZ 8# JMP 8# SR 8# D = 0 跳8# D = 1 转8# 服务程序八个中断源1、2、8 按降序排列…………8.4SKP DZ 1#1# D = 0 跳(D为完成触发器)四、中断响应1. 响应中断的条件允许中断触发器EINT = 12. 响应中断的时间指令执行周期结束时刻由CPU 发查询信号CPU 中断查询INTR1DQINTR2DQINTR nDQ中断源1中断源2中断源n……至排队器8.43. 中断隐指令(1) 保护程序断点(2) 寻找服务程序入口地址(3) 硬件关中断向量地址形成部件INTSQREINTSQR PC1&≥1排队器……断点存于特定地址(0 号地址)内断点进栈INT 中断标记EINT 允许中断R –S 触发器8.4向量地址PC (硬件向量法)中断识别程序入口地址MPC (软件查询法)五、保护现场和恢复现场1. 保护现场2. 恢复现场寄存器内容断点保护现场其他服务程序恢复现场中断返回PUSH视不同请求源而定POP中断服务程序完成中断服务程序中断隐指令完成中断服务程序完成8.4IRET1. 多重中断的概念k l mk+1l+1m+1第一次中断第二次中断第三次中断程序断点k+1 , l+1 , m+1六、中断屏蔽技术8.42. 实现多重中断的条件B, CA中断请求主程序(2) 优先级别高的中断源有权中断优先级别低的中断源(1) 提前设置开中断指令A B C D中断服务程序(A 、B 、C 、D 优先级按降序排列)D8.4&3. 屏蔽技术(1) 屏蔽触发器的作用MASK = 0(未屏蔽)INTR 能被置“1”1&&&1111INTP 1INTP 2INTP 3INTP 4INTR 1INTR 2INTR 3INTR 4MASK 1MASK 2MASK 3MASK 4DQ1DINTRMASKQCPU 查询MASK i = 1 (屏蔽)INTP i = 0 (不能被排队选中)8.4(2) 屏蔽字优先级屏蔽字1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 101 1 1 1 1 1 1 1 1 1 1 1 1 1 10 01 1 1 1 1 1 1 1 1 1 1 1 1 10 0 01 1 1 1 1 1 1 1 1 1 1 1 10 0 0 01 1 1 1 1 1 1 1 1 1 1 10 0 0 0 01 1 1 1 1 1 1 1 1 1 1……0 0 0 0 0 0 0 0 0 0 0 0 0 01 10 0 0 0 0 0 0 0 0 0 0 0 0 0 011234561516……16个中断源1、2、3 ……16 按降序排列8.4(3) 屏蔽技术可改变优先等级(4) 屏蔽技术的其他作用0 0 0 01 01 1 1 1 1 1 1 1 1 10 0 0 01 1 1 1 1 1 1 1 1 1 1 1 6# 比5# 优先级高便于程序控制可以人为地屏蔽某个中断源的请求8.4(1) 断点进栈(2) 断点存入“0 ”地址中断隐指令完成中断周期命令存储器写0 MAR PC MDR(MDR) 存入存储器三次中断,三个断点都存入“0 ”地址4. 多重中断的断点保护断点MDR?如何保证断点不丢失?中断隐指令完成8.4(3) 程序断点存入“0 ”地址的断点保护××××05JMP SERVE ××××SA VE ××××RETURNSTA SA VE …0 地址内容转存其他服务内容地址内容说明SERVELDA SA VEJMP @ RETURN 存程序断点5 为向量地址…保护现场恢复现场间址返回存放ACC 内容转存0 地址内容开中断ENILDA 0STA RETURN置屏蔽字8.4。

8、1 CPU有哪些功能?画出其结构框图并简要说明每个部件得作用。

解:CPU得主要功能就是执行存放在主存储器中得程序即机器指令、CPU就ALU:实现算逻运算寄存器:存放操作数CU:发出各种操作命令序列得控制部件中断系统:处理异常情况与特殊请求8、2 什么就是指令周期?指令周期就是否有一个固定值?为什么?解:指令周期:指取出并执行完一条指令所需得时间。

由于计算机中各种指令执行所需得时间差异很大,因此为了提高CPU运行效率,即使在同步控制得机器中,不同指令得指令周期长度都就是不一致得,也就就是说指令周期对于不同得指令来说不就是一个固定值。

8、3 画出指令周期得流程图,分别说明图中每个子周期得作用。

解:指令周期流程图取指周期:取指令间址周期:取有效地址执行周期:取操作数(当指令为访存指令时)中断周期:保存程序断点8、4 设CPU内有这些部件:PC、IR、SP、AC、MAR、MDR、CU。

(1)画出完成简洁寻址得取数指令“LDAX”(将主存某地址单元得内容取至AC中)得数据流(从取指令开始)。

(2)画出中断周期得数据流。

解:CPU中得数据通路结构方式有直接连线、单总线、双总线、三总线等形式,目前大多采用总线结构,直接连线方式仅适用于结构特别简单得机器中。

下面采用单总线形式连接各部件,框图如下:(1)LDAX指令周期数据流程图:(2)中断周期流程图如下:8、7 什么叫系统得并行性?粗粒度并行与细粒度并行有什么区别?解:并行性:包含同时性与并发性。

同时性指两个或两个以上得事件在同一时刻发生,并发性指两个或多个事件在同一时间段发生。

即在同一时刻或同一时间段内完成两个或两个以上性质相同或性质不同得功能,只要在时间上存在相互重叠,就存在并行性。

粗粒度并行就是指多个处理机上分别运行多个进程,由多台处理机合作完成一个程序,一般算法实现。

细粒度并行就是指在处理机得指令级与操作级得并行性。

8、8 什么就是指令流水?画出指令二级流水与四级流水得示意图,它们中哪一个更能提高处理器速度,为什么?解:指令流水:指将一条指令得执行过程分为n个操作时间大致相等得阶段,每个阶段由一个独立得功能部件来完成,这样n个部件可以同时执行n条指令得不同阶段,从而大大提高CPU得吞吐率。

第八章、输入输出系统输入输出系统测试1、8086 CPU对I/O接口的编址采用了()。

A、I/O端口和存储器统一编址B、I/O端口和寄存器统一编址C、I/O端口独立编址D、输入/输出端口分别编址2、采用DMA方式传送数据时,每传送一个数据就要用一个()时间。

A、指令周期B、机器周期C、存储周期D、总线周期3、某中断系统中,每抽取一个输入数据就要中断CPU一次,中断处理程序接收取样的数据,并将其保存到主存缓冲区内。

该中断处理需要X秒。

另一方面,缓冲区内每存储N个数据,主程序就将其取出进行处理,这种处理需要Y秒,因此该系统可以跟踪到每秒()次中断请求。

A、N /(NX + Y)B、N /(X + Y)NC、min[1 / X ,1 / Y]D、max[1 / X ,1 / Y]4、中断向量地址是()。

A、子程序入口地址B、中断服务例行程序入口地址C、中断服务例行程序入口地址的指示器D、中断返回地址5、为了便于实现多级中断,保存现场信息最有效的办法是采用()。

A、通用寄存器B、堆栈C、存储器D、外存6、在单级中断系统中,CPU一旦响应中断,则立即关闭()标志,以防本次中断服务结束前同级的其他中断源产生另一次中断进行干扰。

A、中断允许B、中断请求C、中断屏蔽D、中断保护7、周期挪用方式常用于()方式的输入/输出中。

A、DMAB、中断C、程序传送D、通道8、一台计算机对n个数据源进行分时采集,送入主存,然后分时处理。

采集数据时,最好的方案是使用()。

A、堆栈缓冲区B、一个指针的缓冲区C、两个指针的单缓冲区D、n个指针的n个缓冲区9、通道对CPU的请求形式是()。

A、自陷B、中断C、通道命令D、跳转指令10、描述PCI总线中基本概念正确的句子是()。

A、HOST 总线不仅连接主存,还可以连接多个CPUB、PCI 总线体系中有三种桥,它们都是PCI 设备C、以桥连接实现的PCI总线结构不允许许多条总线并行工作D、桥的作用可使所有的存取都按CPU 的需要出现在总线上11、如果机器采用中断方式进行输入和输出,发生中断请求条件的是()。