第8章逻辑电路习题解答

- 格式:doc

- 大小:11.10 MB

- 文档页数:25

第8章半导体存储器和可编程逻辑器件8-1存储器按读写功能以及信息的可保存性分别分为哪几类?并简述各自的特点。

解答:存储器按读写功能可分为只读存储器(ROM)和随机存储器(RAM)。

随机存取存储器在工作过程中,既可从其任意单元读出信息,又可以把外部信息写入任意单元。

因此,它具有读、写方便的优点,但由于具有易失性,所以不利于数据的长期保存。

只读存储器在正常工作时其存储的数据固定不变,只能读出,不能随时写入。

ROM为非易失性器件,当器件断电时,所存储的数据不会丢失。

存储器按信息的可保存性可分为易失性存储器和非易失性存储器。

易失性存储器在系统关闭时会失去存储的信息,它需要持续的电源供应以维持数据。

非易失存储器在系统关闭或无电源供应时仍能保持数据信息。

8-2什么是SRAM?什么是DRAM?它们在工作原理、电路结构和读/写操作上有何特点?解答:SRAM(Static Random Access Memory)为静态随机存储器,其存储单元是在静态触发器的基础上附加控制电路构成的。

DRAM(Dynamic Random Access Memory)为动态随机存储器,常利用MOS管栅极电容的电荷存储效应来组成动态存储器,为了避免存储信息的丢失,必须定时地对电路进行动态刷新。

SRAM的数据由触发器记忆,只要不断电,数据就能保存,但其存储单元所用的管子数目多,因此功耗大,集成度受到限制。

DRAM一般采用MOS管的栅极电容来存储信息,由于电荷保存时间有限,为避免存储数据的丢失,必须由刷新电路定期刷新,但其存储单元所用的管子数目少,因此功耗小,集成度高。

SRAM速度非常快,但其价格较贵;DRAM的速度比SRAM慢,不过它比ROM 快。

8-3若RAM的存储矩阵为256字⨯4位,试问其地址线和数据线各为多少条?解答:存储矩阵为256字⨯4位的RAM地址线为8根,数据线为4根。

8-4某仪器的存储器有16位地址线,8位数据线,试计算其最大存储容量是多少?解答:最大存储容量为216⨯8=524288=512k bit(位)8-5用多少片256⨯4位的RAM可以组成一片2K⨯8位的RAM?试画出其逻辑图。

第8章组合数字电路习题解答【8-1】分析图8-1所示电路的逻辑功能,写出输出的逻辑表达式,列出真值表,说明其逻辑功能。

A B &&&&&&&CY图8-1 题8-1电路图解:(0,3,5,6)Y ABC ABC ABC ABC m A B C=+++==⊕⊕∑真值表见表8.1表8.1Y C B A 10001000010011100101110111111000根据真值表可以判断该电路是三变量异或非电路。

【8-2】逻辑电路如图8-2所示:1.写出输出S 、C 、P 、L 的逻辑函数表达式;2.当取S 和C 作为电路的输出时,此电路的逻辑功能是什么?=1&&1&&11&1XYZSC P L图8-2 题8-2电路图解:1.S=X Y Z ⊕⊕C =()X Y Z YZ XY XZ YZ ⊕+=++ P =Y Z ⊕ L =YZ2.当取S 和C 作为电路的输出时,此电路为全加器。

【8-3】 图8-3为由三个全加器构成的电路,试写出其输出F 1,F 2,F 3,F 4的表达式。

A iB iC i-1S i C iA iB iC S i C iA iB iC i-1S i C iX YZ12F 3F 4i-1图8-3 题8-3电路图解:F 1=X Y Z ⊕⊕ 2()F X Y Z =⊕⋅3F XY Z =⊕ 4F XYZ =【8-4】图8-4为集成4位全加器74LS283和或非门构成的电路,已知输入DCBA 为BCD8421码,写出B 2 B 1的表达式,并列表说明输出''''A B C D 为何种编码?A 3A 2A 1A 0S 3 S 2S 1 S 0C 0C 4D' C' B' A'74LS283D C B AB 3 B 2B 1B 041>1>1>图8-4 题8-4电路图解:21B B D B A D C D CB CA ==++++=++若输入DCBA 为BCD8421码,列表可知D 'C 'B 'A '为BCD2421码。

第4章习题及解答用门电路设计一个4线—2线二进制优先编码器。

编码器输入为3210A A A A ,3A 优先级最高,0A 优先级最低,输入信号低电平有效。

输出为10Y Y ,反码输出。

电路要求加一G 输出端,以指示最低优先级信号0A 输入有效。

题 解:根据题意,可列出真值表,求表达式,画出电路图。

其真值表、表达式和电路图如图题解所示。

由真值表可知3210G A A A A =。

(a)0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 0 1 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 10000000000000000000000000010100011111010110000103A 2A 1A 0A 1Y 0Y G真值表≥1&1Y 3A 2A 1&&1A 0Y &1GA 00 01 11 100010001111000000001101113A 2A 1A 0A 03231Y A A A A =+00 01 11 1000000011110001000011103A 2A 1A 0A 132Y A A =(b) 求输出表达式(c) 编码器电路图图 题解4.1试用3线—8线译码器74138扩展为5线—32线译码器。

译码器74138逻辑符号如图(a )所示。

题 解:5线—32线译码器电路如图题解所示。

&&&&11EN01234567BIN/OCTENY 0&G 1G 2AG 2B42101234567BIN/OCTEN&G 1G 2A G 2B42101234567BIN/OCT EN&G 1G 2A G 2B42101234567BIN/OCT EN&G 1G 2A G 2B421A 0A 1A 2A 3A 4Y 7Y 8Y 15Y 16Y 23Y 24Y 31图 题解4.3写出图所示电路输出1F 和2F 的最简逻辑表达式。

自我检测题1.组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。

2.在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。

3.8线—3线优先编码器74LS148的优先编码顺序是7I 、6I 、5I 、…、0I ,输出为2Y 1Y 0Y 。

输入输出均为低电平有效。

当输入7I 6I 5I …0I 为时,输出2Y 1Y 0Y 为 010 。

4.3线—8线译码器74HC138处于译码状态时,当输入A 2A 1A 0=001时,输出07Y ~Y = 。

5.实现将公共数据上的数字信号按要求分配到不同电路中去的电路叫 数据分配器 。

6.根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。

7.一位数值比较器,输入信号为两个要比较的一位二进制数,用A 、B 表示,输出信号为比较结果:Y (A >B ) 、Y (A =B )和Y (A <B ),则Y (A >B )的逻辑表达式为B A 。

8.能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。

9.多位加法器采用超前进位的目的是简化电路结构 × 。

(√,× ) 10.组合逻辑电路中的冒险是由于 引起的。

A .电路未达到最简 B .电路有多个输出 C .电路中的时延 D .逻辑门类型不同11.用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的A .在输出级加正取样脉冲B .在输入级加正取样脉冲C .在输出级加负取样脉冲D .在输入级加负取样脉冲 12.当二输入与非门输入为 变化时,输出可能有竞争冒险。

A .01→10B .00→10C .10→11D .11→01 13.译码器74HC138的使能端321E E E 取值为 时,处于允许译码状态。

A .011 B .100 C .101 D .010 14.数据分配器和 有着相同的基本电路结构形式。

第八章习题参照答案8-1对应图8-47所示的各种情况,分别画出 F 的波形。

a)b)c)d)图8-47题 8-1图解各输出 F 的波形如题8=1 解图所示。

( a)(b)( c)(d)题 8=1 解图8-2 若是“与”门的两个输入端中, A 为信号输入端, B 为控制端。

设 A 的信号波形如图 8-48 所示,当控制端 B=1 和 B=0 两种状态时,试画出输出波形。

若是是“与非”门、“或”门、“或非”门则又如何?分别画出输出波形,最后总结上述四种门电路的控制作用。

图 8-48题8-2图解各种门电路的输出波形如图5- 4 所示。

与门与非门或门或非门图 5-4 习题 5- 2 的解图它们的控制作用分别为:(1)与门:控制端 B 为高电平时,输出为 A 信号;控制端 B 为低电平时,输出为低电平。

( 2)与非门:控制端 B 为高电平时,输出为 A 信号;控制端 B 为低电平时,输出为高电平。

( 3)或门:控制端 B 为高电平时,输出为高电平;控制端 B 为低电平时,输出为 A 信号。

( 4)或非门:控制端 B 为高电平时,输出为低电平;控制端 B 为低电平时,输出为A信号。

8-3 对应图 8-49 所示的电路及输入信号波形,分别画出 F 、 F 、 F 、 F 的波形。

1234a)b)c)d)e)图 8-49题8-3图解各电路的输出波形题8-3 解图所示。

( a)( b)( c)( d)题 8-3 解图8-4化简以下逻辑函数(方法不限)1) F AB A C C D D2) F A(C D CD) B CD A CD ACD3) F( A B)D(A B BD) C A CBD D 4) F AB CD A CDE BDE AC D EF A B A C C D D解 1)A B A C C D(屡次利用吸取率)A B A C DB AC DF A (CD CD) B CD A CD A CDA CD A CD BCD ACD A CD2)(合并同类项)CD CD BCDCD CDF A (CD CD) B CD A CD A CD或CD CD BCD A CD CDCDF(A B )D(A B BD) C A CBD D3)A B D A B C BD C A CBD DAB D A B C BD C A CBD再利用卡诺图,如题8-4 解图( a)所示。

第8章习题详解四、分析计算题1、用代数法化简下列逻辑函数。

(1).Y=AB +AC +AB C(2).Y=ABC +B C +A C (3).Y=AB C ++B C解:(1)Y=AB +AC +AB C= A B A C ABC ++++ =(11)(1)A BC B AC C +++++ =A B C ++ =ABC(2)Y =ABC +B C +A C=()A B C A B C +++gg =A B A B C ⎡⎤+++⎣⎦g=1C g=C(3) Y=AB C ++B C=AB C B C +gg =()A B C B C ++g g=A C B C B C ++gg g =A C B C B C ++gg g =()B C C A C ++g g=1B A C +g g =B A C +g2、已知A 、B 、C 的波形如题图所示。

试分析Y 1、Y 2、Y3、Y 4的输出波形。

解:Y1=ABCY2=A B C ++Y3=A B C g g Y4=A B C ++3、分析题图8.2所示逻辑图的功能。

(1)写出函数Y 的逻辑表达式;(2)将函数Y 化为最简逻辑“与或”表达式式; (3)列出真值表。

解: Y=A B A A B B +++++ =()()A B A A B B ++++g =()()AB A AB B ++g =()()A B A B ++g=AB AB + 同或逻辑---相同为1,不同为0A B Y0 0 1 0 1 0 1 0 0 1114、分析题图8.3所示电路的逻辑功能。

(1)写出与电路对应的输出函数的表达式,并变换成与或式; (2)列出真值表。

解:Y=AB AB + 异或逻辑---相同为0,不同为1A B Y0 0 0 011图8.2AB≥≥≥≥Y1&≥1&A BY5、设计一多数表决电路。

要求A、B、C三人中只要有半数以上同意,则表决就能通过。

但A 还具有否决权,即只要A 不同意,即使多数人意见也不能通过(要求用最少的与非门实现)。

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a) 2K×8位()()()()(b) 256×2位()()()()(c) 1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有( )地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是( )。

(a)256×1位(b)256×8位(c)1K×4位 (d)2K×1位答案:1.a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

第8章思考题及习题8参考答案一、填空1、AT89S51的串行异步通信口为(单工/半双工/全双工).答:全双工。

2。

串行通信波特率的单位是。

答:bit/s3。

AT89S51的串行通信口若传送速率为每秒120帧,每帧10位,则波特率为答:12004.串行口的方式0的波特率为。

答:fosc/125.AT89S51单片机的通讯接口有和两种型式。

在串行通讯中,发送时要把数据转换成数据。

接收时又需把数据转换成数据。

答:并行,串行,并行,串行,串行,并行6.当用串行口进行串行通信时,为减小波特率误差,使用的时钟频率为 MHz.答:11。

05927.AT89S51单片机串行口的4种工作方式中, 和的波特率是可调的,与定时器/计数器T1的溢出率有关,另外两种方式的波特率是固定的.答:方式1,方式38.帧格式为1个起始位,8个数据位和1个停止位的异步串行通信方式是方式 . 答:方式1.9.在串行通信中,收发双方对波特率的设定应该是的。

答:相同的。

10.串行口工作方式1的波特率是 .答:方式1波特率=(2SMOD/32)×定时器T1的溢出率二、单选1.AT89S51的串行口扩展并行I/O口时,串行接口工作方式选择。

A。

方式0 B。

方式1 C. 方式2 D。

方式3答:A2。

控制串行口工作方式的寄存器是。

A.TCON B。

PCON C。

TMOD D.SCON答:D三、判断对错1.串行口通信的第9数据位的功能可由用户定义.对2.发送数据的第9数据位的内容是在SCON寄存器的TB8位中预先准备好的。

对3.串行通信方式2或方式3发送时,指令把TB8位的状态送入发送SBUF中.错4.串行通信接收到的第9位数据送SCON寄存器的RB8中保存。

对5.串行口方式1的波特率是可变的,通过定时器/计数器T1的溢出率设定。

对6。

串行口工作方式1的波特率是固定的,为fosc/32。

错7. AT89S51单片机进行串行通信时,一定要占用一个定时器作为波特率发生器.错8。

数字电子部分习题解答第1章 数字逻辑概论1.2.2 将10进值数127、2.718转换为2进制数、16进制数解:(2) (127)D = (1111111)B 此结果由127除2取余直至商为0得到。

= (7F)H 此结果为将每4位2进制数对应1位16进制数得到。

(4) (2.718)D = (10.1011)B 此结果分两步得到:整数部分--除2取余直至商为0得到;小数部分—乘2取整直至满足精度要求.= (2.B)H 此结果为以小数点为界,将每4位2进制数对应1位16进制数得到。

1.4.1 将10进值数127、2.718转换为8421码。

解:(2) (127)D = (000100100111)8421BCD 此结果为将127中每1位10进制数对应4位8421码得到。

(4) (2.718)D = (0010.0111 0001 1000)8421BCD 此结果为将2.718中每1位10进制数对应4位8421码得到。

第2章 逻辑代数2.23 用卡诺图化简下列各式。

解:(4) )12,10,8,4,2,0(),,,(∑=m D C B A LD C AB D C B A D C B A D C B A D C B A D C B A +++++= 对应卡诺图为:化简结果: D B D C L +=解:(6) ∑∑+=)15,11,55,3,1()13,9,6,4,2,0(),,,(d m D C B A L对应卡诺图为:化简结果: D A L +=第4章 组合逻辑电路4.4.7 试用一片74HC138实现函数ACD C AB D C B A L +=),,,(4.4.7 试用一片74HC138实现函数ACD C AB D C B A L +=),,,(。

解:将输入变量低3位B 、C 、D 接至74HC138的地址码输入端A 2、A 1、A 0 ,将输入变量高位A 接至使能端E 3,令012==E E ,则有:i i i Am m E E E Y ==123。

习题写出图所示电路的逻辑表达式,并说明电路实现哪种逻辑门的功能。

习题图解:B A B A B A B A B A F ⊕=+=+= 该电路实现异或门的功能分析图所示电路,写出输出函数F 。

习题图 解:[]B A B BB A F ⊕=⊕⊕⊕=)(已知图示电路及输入A 、B 的波形,试画出相应的输出波形F ,不计门的延迟.解:B A B A B A AB B AB A AB B AB A F ⊕=•=•••=•••=由与非门构成的某表决电路如图所示。

其中A 、B 、C 、D 表示4个人,L=1时表示决议通过。

(1) 试分析电路,说明决议通过的情况有几种。

(2) 分析A 、B 、C 、D 四个人中,谁的权利最大。

习题图解:(1)ABD BC CD ABD BC CD L ++=••= (2)A C & && & L B A =1 =1 =1FF A B ? ?? ? ? F B A(3)根据真值表可知,四个人当中C 的权利最大。

分析图所示逻辑电路,已知S 1﹑S 0为功能控制输入,A ﹑B 为输入信号,L 为输出,求电路所具有的功能。

习题图解:(1)011011)(S S B S A S S B S A L ⊕⊕+⊕=⊕⊕•⊕= (2)(3)当S 1S 0=00和S 1S 0=11S 1S 0=01时,该电路实现两输入或非门,当S 1S 0=10时,该电路实现两输入与非门。

(2)A 10电路逻辑功能为:“判输入ABC 是否相同”电路。

已知某组合电路的输入A 、B 、C 和输出F 的波形如下图所示,试写出F 的最简与或表达式。

习题图 解:(1)根据波形图得到真值表:C AB BC A C B A F ++=、设∑=)14,12,10,9,8,4,2(),,,(m D C B A F ,要求用最简单的方法,实现的电路最简单。

1)用与非门实现。

2)用或非门实现。

3) 用与或非门实现。

第5章 半导体器件习题选解 P148-1505.2.1 如题5.2.1图所示电路中,试求下列几种情况下输出端Y 的电位V Y 及各元件中通过的电流:(1)V A =V B =0V ;(2)V A =+3V ,V B =0V ;(3)V A = V B = +3V ;二极管的正向压降可忽略不计。

解:(1)当V A =V B =0时,因二极管正向偏置,而使D A 、D B 处于导通状态,电流相等,电阻R 上的电流为:mA I I I DB DA R 07.39.312==+=,输出端V Y =0V 。

(2)当V A =3V,V B =0时,因二极管D B 正向偏置,而使其处于导通状态,即D B 导通,同时使D A 反向偏置,而使D A 截止,则流过D A 的电流为0;流过D B 和电阻R 上的电流相等,即:mA I I DB R 07.39.312===。

(3)当V A =V B =+3V 时,因二极管正向偏置,而使D A 、D B 处于导通状态,电流相等,电阻R 上的电流为:mA I I I DB DA R 3.29.3312=-=+=,输出端V Y = +3V 。

题5.2.1图5.2.3 题5.2.3图所示,E=5V ,,sin 10tV u i ω= 二极管的正向压降可忽略不计,试分别画出输出电压0u 的波形。

解:利用二极管的单向导电性,分析各个电路,所以它们的输出电压波形分别为:(a)、(b)对应的波形为(a );(c)、(d)对应的波形为(b )。

题5.2.3图5.3.1 现有两个稳压管D Z1、D Z2,稳定电压分别为4.5V 和9.5V ,正向电压均为0.5V ,试求如题5.3.1图所示各电路中的输出电压U 0。

解:(a )图:VU U U Z Z 145.95.4210=+=+=(b )图:V U 00= ,因为外加电压小于两个稳压管的稳压值。

(c )图:V U 15.05.00=+=, 两个稳压管的均正向导通。

第8章 触发器和时序逻辑电路及其应用习题解答8.1 已知基本RS 触发器的两输入端D S 和D R 的波形如图8-33所示,试画出当基本RS 触发器初始状态分别为0和1两种情况下,输出端Q的波形图。

图8-33 习题8.1图解:根据基本RS 触发器的真值表可得:初始状态为0和1两种情况下,Q的输出波形分别如下图所示:习题8.1输出端Q的波形图8.2 已知同步RS 触发器的初态为0,当S 、R 和CP 的波形如图8-34所示时,试画出输出端Q的波形图。

图8-34 题8.2图解:根据同步RS 触发器的真值表可得:初始状态为0时,Q的输出波形分别如下图所示:习题8.2输出端Q的波形图8.3 已知主从JK触发器的输入端CP、J和K的波形如图8-35所示,试画出触发器初始状态分别为0时,输出端Q的波形图。

图8-35 习题8.3图解:根据主从JK触发器的真值表可得:初始状态为0情况下,Q的输出波形分别如下图所示:习题8.3输出端Q的波形图8.4 已知各触发器和它的输入脉冲CP的波形如图8-36所示,当各触发器初始状态均为1时,试画出各触发器输出Q端和Q端的波形。

图8-36 习题8.4图解:根据逻辑图及触发器的真值表或特性方程,且将驱动方程代入特性方程可得状态方程。

即:(a )J =K =1;Qn +1=n Q,上升沿触发 (b)J =K =1;Qn +1=n Q, 下降沿触发 (c)K =0,J =1;Qn +1=J n Q+K Qn =1,上升沿触发 (d)K =1,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0·Qn =n Q,上升沿触发 (e)K =Qn ,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0=n Q,上升沿触发 (f)K =Qn ,J =n Q;Qn +1=J n Q+K Qn =n Qn Q+0=n Q,下降沿触发, 再根据边沿触发器的触发翻转时刻,可得当初始状态为1时,各个电路输出端Q的波形分别如图(a )、(b )、(c )、(d )、(e )和(f )所示,其中具有计数功能的是:(a )、(b )、(d )、(e )和(f )。

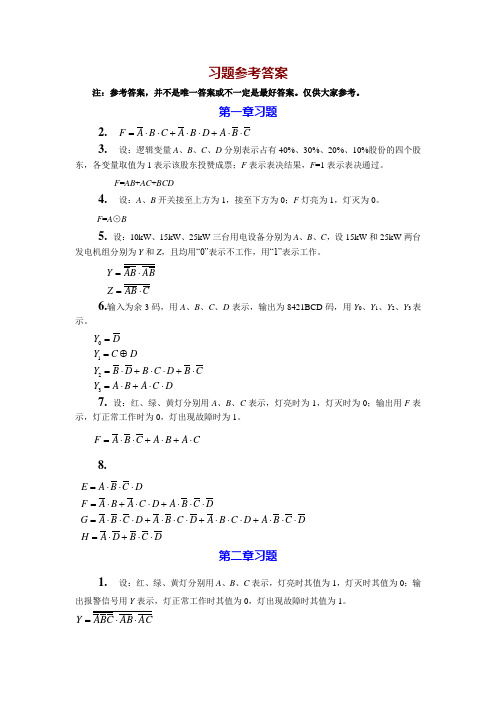

习题参考答案注:参考答案,并不是唯一答案或不一定是最好答案。

仅供大家参考。

第一章习题2. C B A D B A C B A F ⋅⋅+⋅⋅+⋅⋅=3. 设:逻辑变量A 、B 、C 、D 分别表示占有40%、30%、20%、10%股份的四个股东,各变量取值为1表示该股东投赞成票;F 表示表决结果,F =1表示表决通过。

F =AB +AC +BCD4. 设:A 、B 开关接至上方为1,接至下方为0;F 灯亮为1,灯灭为0。

F =A ⊙B5. 设:10kW 、15kW 、25kW 三台用电设备分别为A 、B 、C ,设15kW 和25kW 两台发电机组分别为Y 和Z ,且均用“0”表示不工作,用“1”表示工作。

C AB Z BA B A Y ⋅=⋅=6.输入为余3码,用A 、B 、C 、D 表示,输出为8421BCD 码,用Y 0、Y 1、Y 2、Y 3表示。

D C A B A Y CB DC BD B Y DC Y DY ⋅⋅+⋅=⋅+⋅⋅+⋅=⊕==32107. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时为1,灯灭时为0;输出用F 表示,灯正常工作时为0,灯出现故障时为1。

C A B A C B A F ⋅+⋅+⋅⋅=8. D C B D A H DC B AD C B A D C B A D C B A G DC B AD C A B A F DC B A E ⋅⋅+⋅=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅⋅+⋅⋅+⋅=⋅⋅⋅=第二章习题1. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时其值为1,灯灭时其值为0;输出报警信号用Y 表示,灯正常工作时其值为0,灯出现故障时其值为1。

AC AB C B A Y ⋅⋅=2. 设:烟、温度和有害气体三种不同类型的探测器的输出信号用A 、B 、C 表示,作为报警信号电路的输入,有火灾探测信号时用1表示,没有时用0表示。

报警信号电路的书躇用Y 表示,有报警信号时用1表示,没有时用0表示。

第七章 存储器和可编程器件7—1 填空1.半导体存储器按功能分有_RAM __和__ROM _两种。

2.ROM 主要由__存储矩阵____和__地址译码器____和输出缓冲器三部分组成,按照工作方式的不同进行分类,ROM 可分为_MROM __、_PROM __和_EPROM __三种。

3.某EPROM 有位8数据线,13位地址线,则其存储容量为_8K ×8b __。

4.随机存储器按照存储原理可以分为_____SRAM ______和___DRAM ________,其中______DRAM_____由于具有“漏电”特性,因此需要进行_____刷新______操作。

7—2 图7.2是16⨯4位ROM ,3A 2A 1A 0A 为地址输入,3D 2D 1D 0D 为数据输出,试分别写出3D 2D 1D 0D 的逻辑表达∑=)15,10,6,2(3m D ∑=)15,12,11,8,7,4,3(2m D ∑=)12,9,6,3,0(1m D ∑=)14,13,12,11,8,7,6,5,2,0(0m D7—3 由一个三位二进制加法计数器和一个ROM 构成的电路如图7.3(a )所式。

1. 写出输出1F 2F 3F 的表达式;2. 画出CP 作用下1F 2F 3F 的波形(计数器的初态为“0”)。

答:∑=)5,4,2,1(1m F ∑=)6,5,3(2m F∑=)6,5,4,2,1,0(3m F2、波形如图所示。

注意:F 为组合逻辑。

A A A A 3210图7.2123F F F 图7.3(a )123F F F 图7.3(a )图7.3(b )W 7第8章 脉冲波形的产生及整形8-1 图8.1(a )为由555定时器和D 触发器构成的电路,请问: 1. 555定时器构成的是哪种脉冲电路? 2. 在图(b )中画出C U O1U O2U 的波形; 3. 计算O1U O2U 的频率;4. 如果在555定时器的第5脚接入4V 的电压源,则O1U 的频率将为多少?答:1、该电路为多谐振荡器。

第八章半导体存储器和可编程逻辑器件一、填空题1、一个10位地址码、8位输出的ROM,其存储容量为或。

2、将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM。

该ROM有根地址线,有根数据读出线。

二、综合题1、试写出图6-1所示阵列图的逻辑函数表达式和真值表,并说明其功能。

01F2F3图6-1 例6-1逻辑图2、试用256×4位的RAM扩展成1024×8位存储器。

3、下列RAM各有多少条地址线?⑴512×2位⑵1K×8位⑶2K×1位⑷16K×1位⑸256×4位⑹64K×1位4、写出由ROM所实现的逻辑函数的表达式。

(8分)Y1Y25、四片16×4RAM 和逻辑门构成的电路如图6-7所示。

试回答:AB AB 4AB AB 0地址线数据线图6-7 多片RAM 级联逻辑图⑴单片RAM 的存储容量,扩展后的RAM 总容量是多少?⑵图6-7所示电路的扩展属位扩展,字扩展,还是位、字都有的扩展? ⑶当地址码为00010110时,RAM0~RAM3,哪几片被选中?6.用ROM 设计一个组合逻辑电路,用来产生下列一组逻辑函数。

画出存储矩阵的点阵图。

D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=1 D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=2 D C B D B A Y ⋅⋅+⋅⋅=3D B D B Y ⋅+⋅=47、画出实现下面双输出逻辑函数的PLD 表示。

D C AB CD B A D C B A D C B A D C B A f ABCC B A C B A C B A f ),,,( ),,(21+++=++=三、简答题1、可编程逻辑器件是如何进行分类的?2、GAL16V8的OLMC 中4个数据选择器各有多少功能?3、ROM 和RAM 有什么相同和不同之处?ROM 写入信息有几种方式?4、为什么用ROM 可以实现逻辑函数式?第八章 习题答案一、填空题1、2138K 2、11 16 二、综合题1、解:根据与阵列的输出为AB 的最小项和阵列图中有实心点·为1,无·为0,可以写出AB W F ==30B A AB B A B A W W W F +=++=++=3211B A B A B A F ⊕=+=2AB B A B A B A B A W W W F =+=++=++=2103从上述逻辑表达式可以看出,图6-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。

第八章习题参考答案8-1 对应图8-47所示的各种情况,分别画出F的波形。

a)b)c)d)图8-47 题8-1图解各输出F的波形如题8=1解图所示。

(a)(b)(c)(d)题8=1解图1918-2 如果“与”门的两个输入端中,A 为信号输入端,B 为控制端。

设A 的信号波形如图8-48所示,当控制端B=1和B=0两种状态时,试画出输出波形。

如果是“与非”门、“或”门、“或非”门则又如何?分别画出输出波形,最后总结上述四种门电路的控制作用。

图8-48 题8-2图解 各种门电路的输出波形如图5-4所示。

它们的控制作用分别为:(1) 与门:控制端B 为高电平时,输出为A 信号; 控制端B 为低电平时,输出为低电平。

(2) 与非门:控制端B 为高电平时,输出为A 信号; 控制端B 为低电平时,输出为高电平。

(3) 或门:控制端B 为高电平时,输出为高电平; 控制端B 为低电平时,输出为A 信号。

(4) 或非门:控制端B 为高电平时,输出为低电平; 控制端B 为低电平时,输出为A 信号。

8-3 对应图8-49所示的电路及输入信号波形,分别画出F 1、F 2、F 3、F 4的波形。

a) b) c) d)图5-4 习题5-2的解图与 门 与非门 或 门 或非门192e)图8-49 题8-3图解各电路的输出波形题8-3解图所示。

(a)1938-4 化简下列逻辑函数(方法不限)1)D D C C A B A F +++=2)D C A D C A D C B D)C D (C A F ++++= 3)D BD C A C BD)B A ()D B A (F +++++= 4)E D C A E D B DE C A D C B A F +++=解 1)DC A BD C A B A D C C A B A DD C C A B A F +++=+++=+++=+++=(反复利用吸收率)(c )题8-3解图(d )194 2)DC D C D C B D C D C D C A D C A D C B D C A D C A DC AD C A D C B D)C D (C A F +=++=++++=++++=(合并同类项)或DC D C D C A D C B D C D C DC AD C A D C B D)C D (C A F +=+++=++++=3)BDC A C BD C B A D AB D BD C A C BD C B A D B A DBD C A C BD)B A ()D B A (F ++++=++++++=+++++= 再利用卡诺图,如题8-4解图(a )所示。

ABCD0001111000011110111111111111题8-4解图(a )C AD AB F ++=或CA D AB BD)B (C AD AB BD C A C BD A C ABD C B A D AB BD C A )A (A C BD C B A D AB DBD C A C BD C B A D B A D BD C A C BD)B A ()D B A (F ++=+++=+++++=+++++=++++++=+++++=4)ED BE C A E D B E C A E D C B A DE C B A ED BE C A )E D(E C B A E D C A E D B DE C A D C B AF +=+++=+++=+++=8-5 证明下列逻辑恒等式(方法不限)。

1951)B A B A B B A +=++2)C B AB )D D)(B )(B C (A +=+++ 3)1)C B D B )(A C (B D C )C B (A =+++++4)D B D B C A C A D C B A ABCD D C B A D C B A +++=+++ 5)D C D C B A D AC D C B D)(C A ⊕=+++⊕ 证明:1)B A B B A B A B B A +=+=++ 2)CB AB DC BD C B C B ABD D AB AB )D D)(B C C B AD AB ()D D)(B )(B C (A +=+++++=++++=+++3)1C BD C B A D C C B A CB DC B AD C C B A )C BD B )(A C (B D C )C B (A =++++++=+++++=+++++4)左边右边=+++=++++=+++=ABCD D C B A D C B A D C B A )D B )(D B )()(C A (D B D B C A C A C A5)DC D C )B A B A (D C D C B A D AC D C B D C A D C A DC B AD AC D C B D)(C A ⊕=+++=++++=+++⊕8-6 用卡诺图化简法将下列函数化为最简“与或”形式。

1)D C A D C A C B A D C ABD ABC F +++++= 2)D C BC C A B A F +++= 3)ABC B A C B B A F ++++= 4)C B AC B A F ++=5)BD C D A B A C B A F ++++= 6)∑=)765210()C B,F(A,,,,,, 7)∑=)7531()C B,F(A,,,, 8)∑=)741()C B,F(A,,,9)∑=)14,11,10,9,865,3210()D C,B,F(A,,,,,,196 10)∑=)14,12,10,9,85210()D C,B,F(A,,,,,解 1)D A F += 2)D C B A F ++=题8-6-1)卡诺图 题8-6-2)卡诺图3) F =1 4)AC B A F +=题8-6-3)卡诺图 题8-6-4)卡诺图5)D C B F ++= 6)C B AC B A F ++=题8-6-5)卡诺图 题8-6-6)卡诺图ABCD00011110000111101111111111111ABC 0001111001111111111977)C F = 8)ABC C B A C B A F ++=题8-6-7)卡诺图 题8-6-8)卡诺图9)D C D C A B F ++= 10)D C A C B A D A D B F +++=题8-6-9)卡诺图 题8-6-10)卡诺图8-7 写出图8-50所示各电路的最简逻辑函数表达式。

图a ) b) 图8-50 题8-7图解:(a )各门输出端逻辑表达式分别为b a G ⊕=1A BC 00011110011111A BC 0001111001111ABCD000111100001111011111111111ABCD0001111000011110111111111198cGG•=12abG=3bcac b aabcb ab aabcbaababcbaGGF++=•++=•⊕+=••⊕==)(321bcac b acababc+++=利用卡诺图化简上式,见图5-9,得cabcabF++=1cbaF⊕⊕=2(b)各门输出端逻辑表达式为BAF=132ABFF=ABFF=3ABBAABFABBAABFABFABBAABFABFABBAFFFF+=++=++=••==3218-8 写出图8-51所示各电路的最简“与-或”表达式,列出真值表并说明各电路的逻辑功能。

解设电路中各门的输出端表示如题8-8中各门输出端表示图所示。

(a)写出逻辑表达式并化简:AB1=FBF=2A3=F(a)(b)题8-7中各门输出端表示图题8-7(a)的卡诺图199B A F F 324==FA F =+===B A AB B A AB F F 415⊙BB A B A AB F F ⊕=+==5列写逻辑真值表见题8-8(a )的真值表。

该电路的逻辑功能为“异或”:当输入A 、B 相同时, 输出F 为0;当输入A 、B 相异时,输出F 为1。

A B F 0 0 0 1 1 0 1 10 1 1 0=1=111&F 1F 2F 3F 4(a) (b)图8-51题8-8图题8-8(a )的真值表题8-8中各门输出端表示图(a ) (b )=1=111&F 1F 2200 (b )写出逻辑表达式并化简: B A B A F 3+=ABCC B A C B A C B A C F C F C B A C F F 3332+++=+=⊕⊕=⊕=(已是最简逻辑表达式)BC A C B A CF AB F F 341+=+==用卡诺图化简F 1:题8-8(b )的卡诺图BC AC AB F 1++=8-9 在输入端只给出原变量没有反变量的条件下,用“与非”门和“非”门设计实现下列函数的组合电路:1) F =C B C A D C A B A +++2) F(A 、B 、C 、D)=∑(1,5,6,7,12,13,14) 3) AC BC AB F ++= 4) BC )C B B)(A A (F +++= 5) BC A C B A C AB F ++= 6) BC )B A B A (BC A F +++=解 1)对上述逻辑表达式用摩根律进行变换:C B C AD C A B A C B C A D C A B A F •••=+++=由逻辑表达式画出逻辑电路图题8-9(1)逻辑电路图所示。

2)利用卡诺图对表达式进行化简,题8-9(2)的卡诺图,得A BC 00011110011111题8-9(1)逻辑电路图201D BC BC A C AB D C A F +++=用与非门实现,对上式进行变换D BC BC A C AB D C A F •••=得到的逻辑电路如题8-9(2)的逻辑电路所示。

3)AC B C AB AC B C AB F ⋅⋅=++= 逻辑电路如题8-9(3)的逻辑电路所示。

题8-9(3)的逻辑电路4)CB AC B A C B A C B ABC C B A BC )C B B)(A A (F ⋅⋅=++=++=+++=+++=逻辑电路如题8-9(4)的逻辑电路所示。

题8-9(4)的逻辑电路题8-9(2)的卡诺图题8-9(2)的逻辑电路&&&&A BCF&F1202 5)BC A C B A C AB BC A C B A C AB F ⋅⋅=++= 逻辑电路如题8-9(5)的逻辑电路所示。

题8-9(5)的逻辑电路6)CA B A C A B A B A BC A BC B A B A BC A BC B A B A BC A F ⋅=+=++=++++=+++=逻辑电路如题8-9(6)的逻辑电路所示。