加法器电路的设计

- 格式:ppt

- 大小:226.00 KB

- 文档页数:20

设计资料1加减法运算电路设计1.设计内容及要求1.设计一个4位并行加减法运算电路,输入数为一位十进制数,且作减法运算时被减数要大于或等于减数。

2.led 灯组成的七段式数码管显示置入的待运算的两个数,按键控制运算模式,运算完毕,所得结果亦用数码管显示。

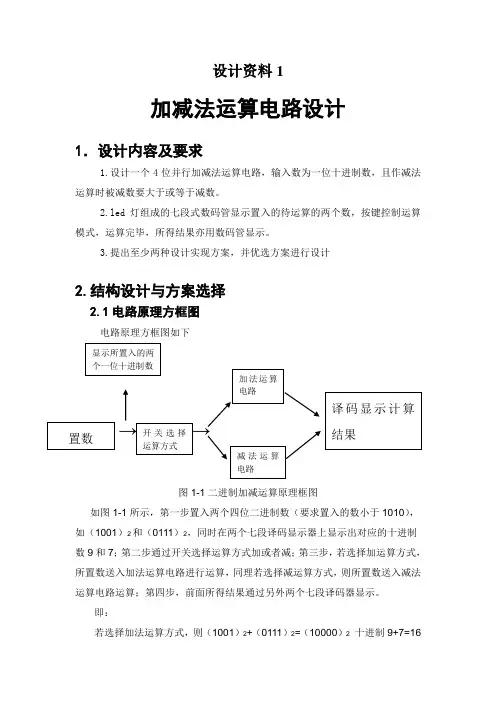

3.提出至少两种设计实现方案,并优选方案进行设计2.结构设计与方案选择2.1电路原理方框图电路原理方框图如下→ →图1-1二进制加减运算原理框图如图1-1所示,第一步置入两个四位二进制数(要求置入的数小于1010),如(1001)2和(0111)2,同时在两个七段译码显示器上显示出对应的十进制数9和7;第二步通过开关选择运算方式加或者减;第三步,若选择加运算方式,所置数送入加法运算电路进行运算,同理若选择减运算方式,则所置数送入减法运算电路运算;第四步,前面所得结果通过另外两个七段译码器显示。

即:若选择加法运算方式,则(1001)2+(0111)2=(10000)2 十进制9+7=16置数开关选择运算方式加法运算电路减法运算电路译码显示计算结果显示所置入的两个一位十进制数并在七段译码显示器上显示16.若选择减法运算方式,则(1001)2-(0111)2=(00010)2十进制9-7=2 并在七段译码显示器上显示02.2.2加减运算电路方案设计2.2.1加减运算方案一如图2-2-1所示:通过开关S2——S9接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U13和U15分别显示所置入的两个数。

数A 直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。

四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S6——S9,通过开关S6——S9控制数B的输入。

当开关S1接低电平时,B与0异或的结果为B,通过加法器74LS283完成两个数A和B的相加。

当开关S1接高电平时,B与1异或的结果为B非,置入的数B在74LS283的输入端为B的反码,且74LS283的进位信号C0为1,其完成S=A+B (反码)+1,实际上其计算的结果为S=A-B完成减法运算。

加法器课程设计电路一、课程目标知识目标:1. 学生能理解加法器的基本概念,掌握半加器、全加器的电路组成和工作原理。

2. 学生能运用所学知识,设计简单的加法器电路,并描述其功能。

3. 学生了解数字电路的基本分类,认识到加法器在数字电路中的应用。

技能目标:1. 学生能够运用所学知识,分析并解决实际加法器电路问题。

2. 学生通过小组合作,动手搭建加法器电路,提高实践操作能力。

3. 学生能够运用计算机辅助设计软件,绘制加法器电路图。

情感态度价值观目标:1. 学生对数字电路产生兴趣,培养主动探究科学知识的热情。

2. 学生在小组合作中,学会尊重他人意见,培养团队协作精神。

3. 学生通过学习加法器电路,认识到科技发展对生活的影响,增强社会责任感。

课程性质:本课程为电子技术基础课程,以理论教学和实践操作相结合的方式进行。

学生特点:学生为初中生,具有一定的物理知识和动手能力,对电子技术有一定的好奇心。

教学要求:结合学生特点,注重理论与实践相结合,提高学生的实践操作能力和创新能力。

在教学过程中,注重启发式教学,引导学生主动探究,培养科学思维。

二、教学内容1. 数字电路基础知识:介绍数字电路的基本概念、分类及特点,使学生了解加法器在数字电路中的应用。

- 教材章节:第一章 数字电路概述2. 加法器原理:讲解半加器、全加器的工作原理,引导学生理解加法器电路的组成及功能。

- 教材章节:第三章 组合逻辑电路;第四节 加法器3. 加法器电路设计:教授如何设计简单的加法器电路,让学生掌握电路设计的基本方法。

- 教材章节:第三章 组合逻辑电路;第五节 电路设计实例4. 实践操作:组织学生进行小组合作,动手搭建加法器电路,提高学生的实践操作能力。

- 教材章节:第五章 实践操作;第一节 电路搭建与测试5. 计算机辅助设计:介绍计算机辅助设计软件,教授如何绘制加法器电路图。

- 教材章节:第六章 计算机辅助设计;第一节 电路图绘制教学进度安排:第一课时:数字电路基础知识,介绍加法器在数字电路中的应用。

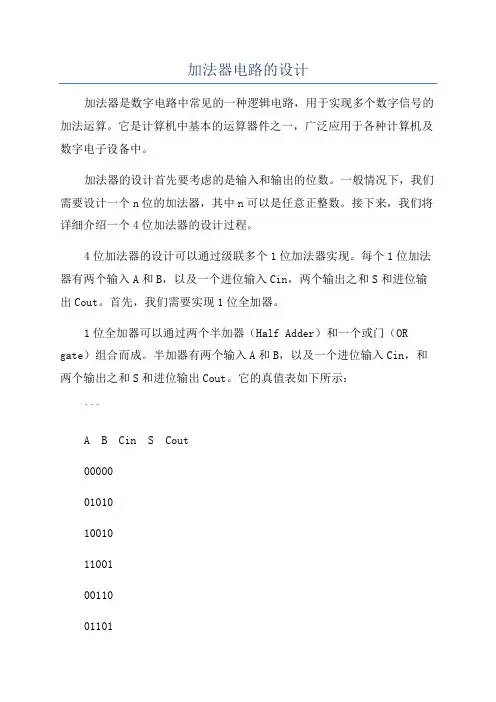

加法器电路的设计加法器是数字电路中常见的一种逻辑电路,用于实现多个数字信号的加法运算。

它是计算机中基本的运算器件之一,广泛应用于各种计算机及数字电子设备中。

加法器的设计首先要考虑的是输入和输出的位数。

一般情况下,我们需要设计一个n位的加法器,其中n可以是任意正整数。

接下来,我们将详细介绍一个4位加法器的设计过程。

4位加法器的设计可以通过级联多个1位加法器实现。

每个1位加法器有两个输入A和B,以及一个进位输入Cin,两个输出之和S和进位输出Cout。

首先,我们需要实现1位全加器。

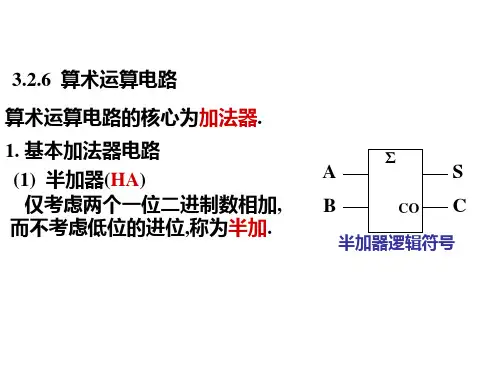

1位全加器可以通过两个半加器(Half Adder)和一个或门(OR gate)组合而成。

半加器有两个输入A和B,以及一个进位输入Cin,和两个输出之和S和进位输出Cout。

它的真值表如下所示:```A B Cin S Cout0000001010100101100100110011011010111111```其中,S代表两个输入的和,Cout代表进位输出。

半加器可以用逻辑门来实现。

S可以通过一个异或门(XOR gate)实现,Cout可以通过一个与门(AND gate)实现。

具体实现如下所示:S=A⊕BCout = A ∧ B接下来,我们将两个半加器级联成一个1位全加器。

如下所示:```__________________A---_____B--->,Half , AND ,---->CouCin->, Adder , Gate,________________________,XOR,---->, Gat,_____```在该电路中,两个输入A和B直接连接到两个半加器的对应输入上,进位输入Cin只连接到第一个半加器的进位输入上。

两个半加器的和输出S通过异或门连接在一起,同时使用与门实现进位输出Cout。

有了1位全加器的设计,我们就可以开始组合多个1位全加器来实现4位加法器了。

具体的设计思路是:1.将四个输入A0-A3和B0-B3连接到四个1位全加器的对应输入上。

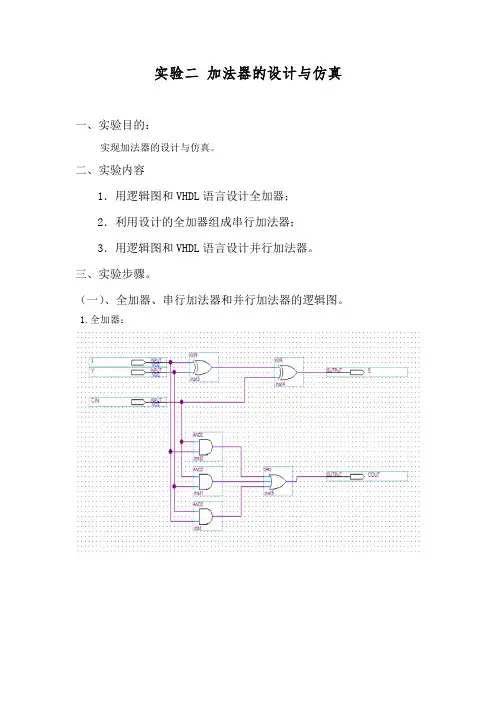

实验二加法器的设计与仿真一、实验目的:实现加法器的设计与仿真。

二、实验内容1.用逻辑图和VHDL语言设计全加器;2.利用设计的全加器组成串行加法器;3.用逻辑图和VHDL语言设计并行加法器。

三、实验步骤。

(一)、全加器、串行加法器和并行加法器的逻辑图。

1.全加器:2.串行加法器:3.74283:4位先行进位全加器逻辑框图:逻辑图:(二)、全加器、串行加法器和并行加法器的VHDL。

1.全加器:LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY quanjiaqi ISPORT(X : IN STD_LOGIC;Y : IN STD_LOGIC;CIN : IN STD_LOGIC;S : OUT STD_LOGIC;COUT : OUT STD_LOGIC);END quanjiaqi;ARCHITECTURE bdf_type OF quanjiaqi ISSIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_1 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_2 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_3 : STD_LOGIC;BEGINSYNTHESIZED_WIRE_2 <= Y AND X;SYNTHESIZED_WIRE_1 <= CIN AND Y;SYNTHESIZED_WIRE_3 <= CIN AND X;SYNTHESIZED_WIRE_0 <= X XOR Y;S <= SYNTHESIZED_WIRE_0 XOR CIN;COUT <= SYNTHESIZED_WIRE_1 OR SYNTHESIZED_WIRE_2 OR SYNTHESIZED_WIRE_3; END bdf_type;2.串行加法器:LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY chuanxingjiafaqi ISPORT(x0 : IN STD_LOGIC;y0 : IN STD_LOGIC;cin : IN STD_LOGIC;x1 : IN STD_LOGIC;x2 : IN STD_LOGIC;y2 : IN STD_LOGIC;x3 : IN STD_LOGIC;y3 : IN STD_LOGIC;y1 : IN STD_LOGIC;s0 : OUT STD_LOGIC;s1 : OUT STD_LOGIC;s2 : OUT STD_LOGIC;s3 : OUT STD_LOGIC;cout : OUT STD_LOGIC);END chuanxingjiafaqi;ARCHITECTURE bdf_type OF chuanxingjiafaqi ISCOMPONENT quanjiaqiPORT(X : IN STD_LOGIC;Y : IN STD_LOGIC;CIN : IN STD_LOGIC;S : OUT STD_LOGIC;COUT : OUT STD_LOGIC);END COMPONENT;SIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC; SIGNAL SYNTHESIZED_WIRE_1 : STD_LOGIC; SIGNAL SYNTHESIZED_WIRE_2 : STD_LOGIC;BEGINb2v_inst : quanjiaqiPORT MAP(X => x0,Y => y0,CIN => cin,S => s0,COUT => SYNTHESIZED_WIRE_0); b2v_inst1 : quanjiaqiPORT MAP(X => x1,Y => y1,CIN => SYNTHESIZED_WIRE_0,S => s1,COUT => SYNTHESIZED_WIRE_1); b2v_inst2 : quanjiaqiPORT MAP(X => x2,Y => y2,CIN => SYNTHESIZED_WIRE_1,S => s2,COUT => SYNTHESIZED_WIRE_2); b2v_inst3 : quanjiaqiPORT MAP(X => x3,Y => y3,CIN => SYNTHESIZED_WIRE_2,S => s3,COUT => cout);END bdf_type;3.74283:4位先行进位全加器LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY 74283_0 ISPORT(CIN : IN STD_LOGIC;A1 : IN STD_LOGIC;A2 : IN STD_LOGIC;B2 : IN STD_LOGIC;A3 : IN STD_LOGIC;A4 : IN STD_LOGIC;B4 : IN STD_LOGIC;B1 : IN STD_LOGIC;B3 : IN STD_LOGIC;SUM4 : OUT STD_LOGIC;COUT : OUT STD_LOGIC;SUM1 : OUT STD_LOGIC;SUM2 : OUT STD_LOGIC;SUM3 : OUT STD_LOGIC );END 74283_0;ARCHITECTURE bdf_type OF 74283_0 IS BEGIN-- instantiate macrofunctionb2v_inst : 74283PORT MAP(CIN => CIN,A1 => A1,A2 => A2,B2 => B2,A3 => A3,A4 => A4,B4 => B4,B1 => B1,B3 => B3,SUM4 => SUM4,COUT => COUT,SUM1 => SUM1,SUM2 => SUM2,SUM3 => SUM3);END bdf_type;四、实验仿真结果。

实验二一位8421BCD码加法器的设计一、实验目的1. 理解四位加法器7483和四位比较器7485的工作原理及使用2. 掌握一位8421BCD码加法器的工作过程3. 进一步熟悉Quartus软件的使用,了解设计的全过程,二、实验内容1.采用画原理图的方法设计一位8421BCD码加法器。

要求使用四位加法器7483和四位比较器7485及必要的逻辑门电路。

三、分析过程7483是四位二进制加法器,其进位规则是逢16进1。

而8421BCD 码表示的是十进制数,进位规则是逢10进1。

用7483将两个1位BCD码相加时,当和小于等于9时,结果正确;当和大于9时,需加6进行修正。

实验中要求使用7483、7485及必要的逻辑门完成。

由于7483通过输出引脚C4 S3 S2 S1 S o输出二进制的和,7485是四位比较器,关键在于如何通过7483及7485的输出判断何时应对结果修正以及如何修正。

由于两个1位十进制数相加时,和的取值范围是0—18,将该范围内各数值对应的二进制数和8421BCD码列表,以便寻找何时应对结果修正以及如何修正从表中分析可得出如下结论:当7483输出的二进制数的和为0---9时,即S3 S2 S1 SO W 9时结果正确,不需修正;当和为10-----15时S3 S2 S1 S)> 9时,需加6 修正,此种情况可将7483的输出S3 S2 S1 S0送入7485的输入引脚A3 A2 A1 A0 ,将1001(即卩9)送入7485另一组输入引脚B3 B2 B1 B0, 若7485的输出A> B=1,则说明需加6修正;当和为16、17、18时,结果需加6修正。

此种情况7483的输出S3 S2 S1 S)v 9,但C4=1。

综合以上分析,当7483输出的二进制数的和S3 S2 S1 S)> 9或C4=1时结果需修正。

此修正的条件可通过7485的输出A> B和7483 输出的C4通过逻辑或门(OR1获得。

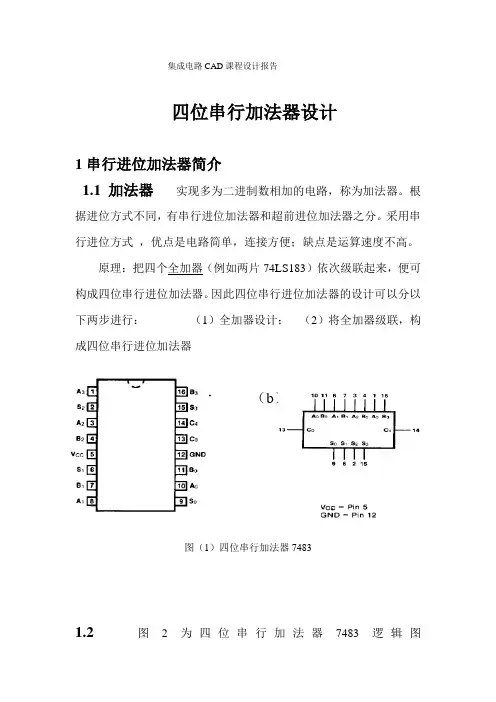

集成电路CAD课程设计报告四位串行加法器设计1串行进位加法器简介1.1加法器实现多为二进制数相加的电路,称为加法器。

根据进位方式不同,有串行进位加法器和超前进位加法器之分。

采用串行进位方式,优点是电路简单,连接方便;缺点是运算速度不高。

原理:把四个全加器(例如两片74LS183)依次级联起来,便可构成四位串行进位加法器。

因此四位串行进位加法器的设计可以分以下两步进行:(1)全加器设计;(2)将全加器级联,构成四位串行进位加法器(a)(b)图(1)四位串行加法器74831.2 图2为四位串行加法器7483逻辑图图(2)四位串行加法器2 四位串行进位加法器的设计实现:2.1 输出级电路设计与TTL电路兼容驱动10个TTL①输出高电平时|IoH|<=20uAV oHmin=4.4V②输出低点平时|IoH|<=20mAV oHmax=0.4V③输出级充放电时间tr=tf计算电路如图3所示①以15个PF的电容负载代替10个TTL电路来计算tr、tf②输入V为的前一级的输出被认为是理想的输出,即:ViL=Vss,ViH=Vdd③计算电流时,负载为电流负载,有拉电流的灌电流。

图3(1)CMOS N 管(W/L )N 的计算:当输入为高电平时(Vi=Vdd ),N 管导通后级TTL 电路有较大的灌电流输入,此时(表示成对称形式)使方括号中的值和栅电容Cox 及电子迁移率un 为最小值:o u t00f f[]200200)()(2V V V V V V C L W I tn i s tn oxN ndsn -----⎪⎭⎫ ⎝⎛=μm ax0m in 2ox SiOox t C εε=230m ax0m in-⎪⎪⎭⎫⎝⎛=TT n n μμ(2) CMOS P 管(W/P )p 的计算|IoH |<=20uA时有 V oHmin=4.4V tr=tf① 以Ioh<=20uA时V oHmin=4.4V 的条件计算最坏的情况下Vdd=4.5V ,V ohmin=4.4v,Vtp=0.8V ,经计算可得∆∆===⎪⎭⎫⎝⎛233034956.164m inn L W []202)()(2oh tp i dd tp i oxp p ohV V V V V V C L W I -----⎪⎭⎫ ⎝⎛=μm ax0m in 2ox SiOox t C εε=230m ax 0m in-⎪⎪⎭⎫⎝⎛=T T n p μμ∆∆===⎪⎭⎫⎝⎛21532227.7pL W②tr=tp 的条件计算:CMOS 中αp=αn所以2.2 输入级设计ddtp p V V =αddtn n V V =αddp L p V k C =τ()⎥⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎢⎣⎡-⎪⎪⎭⎫ ⎝⎛--+--=p n n n n f arth t αααατ111.011)1.0(2p pn n pn n p f r LW L W k k t t μμττ⎪⎭⎫⎝⎛⎪⎭⎫⎝⎛===⎪⎪⎭⎫ ⎝⎛∆∆===⎪⎭⎫⎝⎛233034956.164minn L W ∆∆==⎪⎭⎫⎝⎛275931138minn L W ∆∆===⎪⎭⎫⎝⎛233034956.164minn L W输入电平Vih 可能为2.4V(1)拉管P2为了节省面积,同时又能使Vih 较快上升,取图4(2)CMOS 反向器的P1管此P1管应取内部基本反向器的尺寸(3)CMOS 反相器的N 管TTL 的输出电平在0.4-2.4之间 V1*=ViLmax+Vihmin=1.4V∆∆===⎪⎭⎫⎝⎛223312p L W∆∆==⎪⎭⎫ ⎝⎛231.546内p L W式中βk=kn/kp,Vdd=5V ,Vtn=0.7V ,Vi*=1.4V , βk=17.162.3 内部基本反相器中各MOS 管尺寸的计算内部反相器的负载电容: ①本级漏极的PN 结电容Cpn ②下级的栅电容Cc1 ③连线杂散电容Cs Cpn+Cc1=10CsCs :铝线宽5um,长100um ,在场区上面,此铝线的电容为1K k V V k V p n TP DD p *I+++=+++=R TP DD TN R TN N V V V V k ββ)(∆∆=⎪⎭⎫⎝⎛=⎪⎭⎫ ⎝⎛2230W np R pl nl L L W μμβ∆∆==⎪⎭⎫⎝⎛22303345nlL W ∆∆==⎪⎭⎫⎝⎛231.546plL W ∆∆===⎪⎭⎫⎝⎛223312p L WCpn 和Cl :N 管 其衬底是P 型,所以 NB=2⨯1016 cm-3 设结深Xi=0.5um R □=20Ω/□对于P 管Cpn=而CC1可以由:Cc1=10Cs-Cpn 求出。

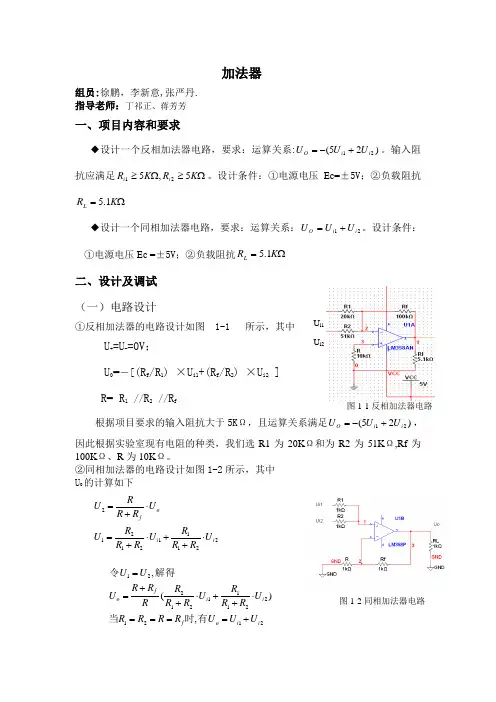

加法器组员:徐鹏,李新意,张严丹. 指导老师:丁祁正、蒋芳芳一、项目内容和要求◆设计一个反相加法器电路,要求:运算关系:)25(21i i O U U U +-=。

输入阻抗应满足Ω≥Ω≥K R K R i i 5,521。

设计条件:①电源电压Ec=±5V ;②负载阻抗Ω=K R L 1.5◆设计一个同相加法器电路,要求:运算关系:21i i O U U U +=。

设计条件: ①电源电压Ec =±5V ;②负载阻抗Ω=K R L 1.5二、设计及调试 (一)电路设计①反相加法器的电路设计如图 1-1 所示,其中U +=U -=0V ;U 0=-[(R f /R 1) ×U i1+(R f /R 2) ×U i2 ] R = R 1 //R 2 //R f根据项目要求的输入阻抗大于5K Ω,且运算关系满足)25(21i i O U U U +-=,因此根据实验室现有电阻的种类,我们选R1为20K Ω和为R2为51K Ω,Rf 为100K Ω、R 为10K Ω。

②同相加法器的电路设计如图1-2所示,其中 U 0的计算如下图1-1反相加法器电路U i1 U i22211121212i i o fU R R R U R R R U U R R RU ⋅++⋅+=⋅+=21212211121221,)(,i i o f i i f o U U U R R R R U R R R U R R R R R R U U U +====⋅++⋅++==有时当解得令图1-2同相加法器电路根据项目要求的输入阻抗大于5K Ω,且运算关系满足21i i O U U U +=,因此根据实验室现有电阻的种类,我们选R1、R2、R 和Rf 都是10K Ω.(二)电路仿真1、反相加法器的电路仿真测试A :输入信号V U V U i i 5.0,5.021±=±=,测试4种组合下的输出电压如下;①反相加法器 U i1=+0.5v ,U i2=+0.5v ,输出电压U 0=-3.464V.②反相加法器 U i1=+0.5v ,U i2=-0.5v ,输出电压U 0=-1.503V.③反相加法器U i1=-0.5v,U i2=-0.5v ,输出电压U0=3.496V.④反相加法器U i1=-0.5v,U i2=+0.5v ,输出电压U0=1.536V.B :输入信号V KHz U V U i i 1.0,1,5.021为正弦波±=信号,测试两种输入组合情况下的输出电压波形如下。

正弦波加法器电路引言正弦波加法器电路是一种电路设计,用于将多个正弦波信号进行相加。

在电子工程和通信领域中,正弦波加法器电路广泛应用于混频器、调频解调器、音频信号处理器等设备中。

本文将详细介绍正弦波加法器电路的原理、设计和应用。

原理正弦波加法器电路的原理基于电子学中的电路分析和信号处理理论。

其基本思想是将多个正弦波信号通过电路进行叠加,得到一个输出信号,该输出信号是输入信号的和。

正弦波加法器电路通常由运算放大器和电阻网络组成。

设计正弦波加法器电路的设计需要考虑以下几个方面:1. 电路拓扑正弦波加法器电路可以采用不同的电路拓扑结构,常见的有反相输入运算放大器电路和非反相输入运算放大器电路。

反相输入运算放大器电路的输入信号与运算放大器的负输入端相连,而非反相输入运算放大器电路的输入信号与运算放大器的正输入端相连。

2. 运算放大器选择在正弦波加法器电路中,运算放大器是核心元件。

选择适合的运算放大器对于电路性能至关重要。

常见的运算放大器有理想运算放大器和实际运算放大器。

理想运算放大器具有无穷大的输入阻抗、无穷大的增益和零输出阻抗,而实际运算放大器存在一定的误差和非线性。

3. 电阻网络设计电阻网络用于将多个输入信号进行叠加。

根据叠加原理,电阻网络中的电阻值需要根据输入信号的幅度和相位进行选择。

常见的电阻网络包括反馈电阻、输入电阻和输出电阻。

4. 电源和耦合电容正弦波加法器电路需要稳定的电源供电。

在设计中需要考虑电源的稳定性、噪声和纹波等因素。

此外,耦合电容用于隔离输入信号和输出信号,避免干扰和串扰。

应用正弦波加法器电路在通信、音频处理等领域有着广泛的应用。

以下是一些常见的应用场景:1. 混频器在频率转换中,混频器用于将一个信号的频率转换到另一个频率。

正弦波加法器电路可以用于混频器中的频率加法。

2. 调频解调器调频解调器用于调频通信系统,将调制信号转换为解调信号。

正弦波加法器电路可以用于调频解调器中的信号合并。

加法计数器电路设计需要考虑多个因素,包括输入信号、计数器状态、计数规则等。

以下是一个简单的加法计数器电路设计的步骤:

1. 确定计数器的位数:根据需要计数的最大值和最小值,确定计数器的位数。

例如,如果要计数的范围是0到99,则可以选择一个3位的二进制计数器。

2. 确定计数器的状态:根据确定的位数,确定计数器的所有可能状态。

例如,对于一个3位的二进制计数器,有8个可能的状态:000、001、010、011、100、101、110、111。

3. 确定计数规则:根据计数器的状态和输入信号,确定计数器的计数规则。

例如,对于一个3位的二进制加法计数器,可以采用逢十进一的规则,即当计数器的值达到最大值(111)时,下一个输入信号会使计数器的值回绕到最小值(000)。

4. 设计电路:根据上述步骤,设计加法计数器电路。

可以采用门电路、触发器等电子元件来构成加法计数器。

在设计过程中,需要考虑电路的稳定性和可靠性,以及尽量减小功耗和减小体积等问题。

5. 仿真和测试:使用仿真软件对设计的加法计数器电路进行仿真和测试,以确保其功能正确性和性能可靠性。

总之,加法计数器电路设计需要综合考虑多个因素,并采用合适的电子元件和设计方法来实现。

加法器实验报告加法器实验报告概述:本次实验旨在设计和实现一个加法器电路,通过对电路的搭建和测试,验证加法器的正确性和可行性。

加法器是计算机中最基本的算术运算器之一,其在数字逻辑电路中扮演着重要的角色。

1. 实验背景加法器是一种基本的数字逻辑电路,用于实现数字的加法运算。

在计算机中,加法器被广泛应用于算术逻辑单元(ALU)和中央处理器(CPU)等部件中,用于进行各种数值计算和逻辑运算。

因此,了解和掌握加法器的工作原理和设计方法对于理解计算机原理和数字电路设计具有重要意义。

2. 实验目的本次实验的主要目的是通过设计和实现一个4位二进制加法器电路,验证加法器的正确性和可行性。

具体要求如下:- 设计并搭建一个4位二进制加法器电路;- 对电路进行测试,验证其加法运算的正确性;- 分析电路的性能和优化空间。

3. 实验原理加法器是通过逻辑门电路实现的。

在本次实验中,我们将使用全加器电路来实现4位二进制加法器。

全加器是一种能够实现两个二进制位相加并考虑进位的电路。

通过将多个全加器连接起来,可以实现更高位数的二进制加法器。

4. 实验步骤4.1 设计加法器电路的逻辑功能首先,我们需要确定加法器电路的逻辑功能。

在这个实验中,我们需要实现两个4位二进制数的相加运算,并输出结果。

具体的逻辑功能可以通过真值表或逻辑表达式来描述。

4.2 搭建电路根据逻辑功能的要求,我们可以使用逻辑门电路来搭建加法器。

在本次实验中,我们将使用多个全加器电路来实现4位二进制加法器。

通过将多个全加器连接起来,可以实现更高位数的二进制加法器。

4.3 进行电路测试在搭建完电路后,我们需要对电路进行测试,以验证其加法运算的正确性。

可以通过输入一些测试用例,并比较输出结果与预期结果是否一致来进行测试。

5. 实验结果与分析通过对加法器电路的测试,我们可以得到加法器的输出结果。

通过比较输出结果与预期结果,可以验证加法器的正确性。

同时,我们还可以分析电路的性能和优化空间,例如进一步提高加法器的速度和减少功耗等。

4位快速加法器设计原理快速加法器是一种计算器件,可以快速地对两个二进制数进行加法运算。

相对于一般的加法器,它具有更高的速度和效率。

本文主要介绍4位快速加法器的设计原理。

1.基本概念在二进制加法中,加法器通过对两个二进制数分别进行逐位相加的方法,得到它们的和。

二进制加法的基本规则如下:0+0=0;1+0=1;0+1=1;1+1=0(进位1)。

在四位二进制数的加法中,每位相加可以得到一个位和进位两位。

4位快速加法器在计算时需要考虑到位和进位两个方面。

2.快速加法器的组成4位快速加法器可以由4个1位全加器和1个2位全加器组成。

1位全加器的输出等于输入A、B和进位C的和。

输出S等于(A xor B) xor C,进位C 等于AB+C(A xor B)。

2位全加器是由两个1位全加器和一个2选1选择器组成。

输入A和B分别与这两个全加器相连,进位C输入到这两个全加器的进位端。

选择器的选择信号是两个输入和上一个全加器的进位,选择器的输出连接到2位全加器的进位输出。

3.原理图4位快速加法器的原理图如下所示:每个1位全加器都由具有相同运算功能的逻辑门电路组成。

在1位全加器中,输入A、B和进位C分别与XOR、AND和OR门相连,这些门的输出再次进行逻辑运算得到输出S和新的进位C。

2位全加器由两个1位全加器和一个2选1选择器组成。

选择器的选择信号是上一个1位全加器的进位和两个输入的和。

这两个1位全加器的进位输出也分别与这个选择器相连。

4.流程图4位快速加法器的计算流程图如下所示:将输入的两个4位二进制数的第0位分别输入到1位全加器1和2中。

这两个全加器的进位C0均为0,得到第0位的位和(S0)和进位(C1)。

然后,将输入的两个4位二进制数的第1位分别输入到1位全加器3和4中。

全加器3的进位C1为1,因为它是在第0位加法器的进位C1的基础上进行的。

全加器4的进位C2为全加器3的进位C2与两个输入的和的2选1选择器输出的结果。

八位加法器设计实验报告实验名称:八位加法器设计实验一、实验目的:1.了解数字电路中加法器的基本原理。

2.学习八位加法器的设计和实现方法。

3.掌握八位加法器的工作过程和输出结果。

二、实验器材:数字电路实验箱、电源线、逻辑门芯片(2个8位加法器芯片、1个与门芯片、1个或门芯片)、导线、电压表,显示器。

三、实验原理:四、具体步骤:1.搭建实验电路。

将两个8位加法器芯片、一个与门芯片、一个或门芯片分别插入数字实验箱中,并使用导线连接它们。

将A和B分别连接到8位加法器芯片的A和B输入端,将进位输入端Cin接地。

然后将两个八位加法器芯片的S0-S7依次连接到特定点,作为低位数;再将与门芯片的S仅连接到A口或B口上的特定点,或门芯片的S仅连接到A口上的特定点;然后将A、B、Cin的高位输入引脚接到与门芯片的输入端上;最后将八位加法器芯片的Cout引脚接到特定点,作为进位输出;将与门芯片和或门芯片的输出引脚接到显示器上。

2.进行实验。

给定任意两个8位操作数A和B,将它们输入到加法器中,并设置进位输入端Cin为0。

观察显示器上的运算结果。

3.分析实验结果。

根据实验数据和观察结果,分析八位加法器的工作过程和输出结果,研究其工作原理。

5.总结实验。

根据实验结果和分析,总结设计和实现八位加法器的方法,并讨论可能存在的问题和改进方法。

五、注意事项:1.在搭建实验电路之前,仔细检查电路连接是否准确、导线是否插紧。

2.在实验过程中,注意实验安全,注意观察显示器上的运算结果,及时记录实验数据。

3.实验结束后,将电源关闭,清理整理实验场地,将实验器材归位。

六、实验结果:S0=1,S1=1,S2=0,S3=0,S4=0,S5=0,S6=1,S7=1,Cout=1七、实验总结:通过本次实验,我学习了数字电路中加法器的基本原理,掌握了八位加法器的设计和实现方法,了解了八位加法器的工作过程和输出结果。

我通过实际搭建电路、输入操作数并设置进位输入,观察了八位加法器的运算结果,并根据实验结果进行了分析和总结。

比较器与加法器电路的设计与分析在电子电路中,比较器(Comparator)和加法器(Adder)是常见的元件,广泛应用于各类电子设备中。

本文将对比较器和加法器的电路设计与分析进行讨论与探究。

一、比较器的设计与分析比较器是一种电子电路元件,其主要功能是将输入信号与参考信号进行比较,并将比较结果以不同的输出电平表示。

在实际应用中,比较器常被用于判断输入信号是否超过某一阈值,以实现开关、触发器等功能。

1.1 比较器的基本结构比较器的基本结构由一个差分放大器和一个输出级组成。

差分放大器(Differential Amplifier)是比较器的核心部分,其作用是放大差模信号并产生输出。

输出级则负责将差模信号转化为数字电平输出。

一般来说,比较器的输入端包括正向输入端(+IN)和反向输入端(-IN),以及一个参考电压端(REF),用于设定比较的阈值。

输出端通常标记为OUT。

1.2 比较器的工作原理比较器的工作原理可以简单描述如下:当+IN输入信号大于-IN输入信号时,输出电平为高电平,否则为低电平。

这种工作模式被称为非反相比较器(Non-Inverting Comparator)。

在实际应用中,常常需要根据具体需求选择不同类型的比较器。

例如,若需要反相输出结果,则可以使用反相比较器(Inverting Comparator)。

1.3 比较器的参数与性能指标比较器的设计需要参考一系列参数与性能指标,以便满足实际需求。

以下是一些常见的参数与性能指标:1.3.1 输入阈值(Input Threshold):指在输入信号和参考信号比较时,两者之间的电压差值。

超过该阈值的信号将产生状态转变。

1.3.2 输入电压范围(Input Voltage Range):指比较器能够接受的输入电压范围,超出范围的信号将无法正确比较。

1.3.3 响应时间(Response Time):指比较器从接收到输入信号到产生输出结果所需的时间。