第8章 DMA控制器

- 格式:ppt

- 大小:306.00 KB

- 文档页数:40

交通信息与控制工程系教案(理论教学用)

课程名称微机原理与接口技术第 18 次第 9 周 2 学时上课教室WM1310 课程类型专业基础课授课对象自动化专业章节名称第8章计数器/定时器与DMA控制器(8.1,8.2)

教学目的和要求1.了解软硬件定时的原理;2.掌握8253的原理及应用。

讲授主要内容及时间分配1.接口电路概况;(10min)

2.8253的外部引线和内部结构;(20min)

3.8253的工作方式和控制字;(30min)

4.8253的应用。

(30min)

教学重点与难点重点:

1.软硬件定时的原理;2.8253的原理及应用。

难点:

8253的原理及应用。

要求掌握知识点和分析方法1.了解软硬件定时的原理;2.掌握8253的原理及应用。

启发与提问

1.软件定时与硬件定时的区别?教学手段

多媒体

作业布置思考题:

1.了解最新的硬件定时芯片的原理及其应用,如DS12887等。

主要参考资料

备注

长安大学讲稿(第十九讲)。

微机填空题题库-2014(终极版)填空题第1章微型计算机概述1.微型计算机中各部件是通过总线构成一个整体的.2.____微处理器_____是微型计算机的核心。

3.总线按照其规模、用途和应用场合可分为_数据总线_________、_地址总线_________和___控制总线_________。

4.微型计算机由_ CPU_______ 、存储器___ 、输入/输出接口_______ 和_系统总线______ 组成。

5.以微型计算机为主体,配上系统软件、应用软件和外设之后,就成了微型计算机系统。

6.微型计算机的主要性能指标有CPU的位数、____CPU的主频__、_内存容量和速度______________、__硬盘容量________第2章 16位和32位微处理器1.Intel 8086CPU是__16_____位微处理器,有__16___根数据总线和__20__根地址总线,存储器寻址的空间为_ 1MB______,端口寻址空间为_64KB____。

8088CPU有_8_根数据总线。

2.输入/输出端口有两种编址方法,既I/O端口与存储单元统一编址和I/O单独编址。

前一种编址的主要优点是功能强和指令灵活。

后一种编址的主要优点是指令运行速度快和增强了程序的可读性。

3.所谓最小模式,就是在系统中只有8086一个微处理器。

4.所谓最大模式是在系统中包含两个或多个微处理器。

(主 8086,其他称协处理器)5.8086工作在最大模式下,引脚MN/MX*接低(高/低)电平。

6.8086/8088CPU的数据线和地址线是以__分时复用_____ 方式轮流使用的。

7.8086中的BIU由___4_______个_______16_____位段寄存器、一个___16____位指令指针、___6_______字节指令队列、__20_____位地址加法器和控制电路组成。

8.8086/8088提供的能接受外中断请求信号的引脚是INTR 和NMI 。

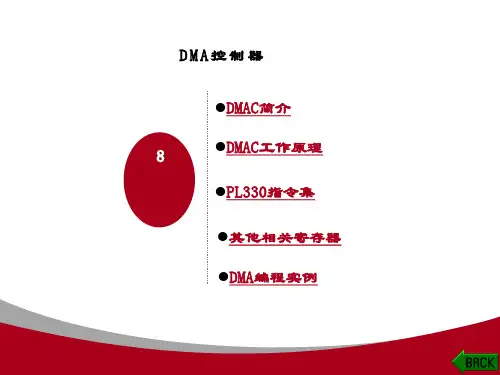

8 DMA概述S3C2410A支持位于系统总线和外设总线之间的4个通道的DMA控制器。

每一个通道的DMA控 制器都能没有约束的实现系统总线或者外设总线之间的数据传输,即每个通道都能处理下面四 种情况:1) 源器件和目的器件都在系统总线2) 源器件在系统总线,目的器件在外设总线3) 源器件在外设总线,目的器件在系统总线4) 源器件和目的器件都在外设总线DMA的主要优点是:可以不通过CPU的干预来实现数据的传输,DMA的运行可以通过软件、内 部外设或外部请求引脚信号的请求来初始化。

DMA 请求源每个通道的DMA控制器都能够从4个DMA 如果在DCON寄存器中H/W DMA请求模式被选中,请求源中选择一个 DMA 请求源。

(注意:如果 S/W 请求模式被选中,中断请求源的设置没有 任何意义)表 81 列出了每一个通道的 4 个 DMA 请求源。

Table 81. 每一个通道的DMA请求源Source0 Source1 Source2 Source3 Source4 Ch0 nXDREQ0 UART0 SDI Timer USB device EP1 Ch1 nXDREQ1 UART1 I2SSDI SPI0 USB device EP2 Ch2 I2SSDO I2SSDI SDI Timer USB device EP3 Ch3 UART2 SDI SPI1 Timer USB device EP4在这里,nXDREQ0和nXDREQ1表示两个外部源(外部设备),I2SSDO和I2SSDI分别表示IIS 的发送和接收。

DMA 工作过程DMA 使用三态 FSM(有限状态机)进行操作,以下用三个步骤描述:State1. 初始状态,DMA 等待DMA 请求。

若请求到达,进入状态 2。

此阶段,DMA ACK 和 INT REQ 都为 0。

dma控制器名词解释

DMA(Direct Memory Access)控制器是一种计算机硬件设备,

用于实现直接内存访问。

它充当了主机CPU和系统内存之间的数据

传输中介,可以在不占用CPU时间的情况下,直接将数据从外设传

输到内存,或者从内存传输到外设。

DMA控制器的主要作用是减轻CPU的负担,提高数据传输的效率。

传统上,当需要进行数据传输时,CPU需要通过程序控制来完

成数据的读取或写入操作,这会消耗大量的CPU时间和资源。

而有

了DMA控制器,数据传输可以在CPU的干预下进行,CPU只需进行

一次初始化设置,之后可以将控制权交给DMA控制器,从而释放出

更多的CPU资源来处理其他任务。

DMA控制器通常与外设设备(如硬盘、网络适配器、显卡等)

相连,通过DMA通道进行数据传输。

控制器通过直接访问系统总线,绕过了CPU,实现了高速的数据传输。

在数据传输过程中,DMA控制

器会负责处理数据的读取、写入、校验和中断等操作,以确保数据

的可靠性和完整性。

DMA控制器的工作原理大致如下,首先,CPU通过DMA控制器的

寄存器设置传输的起始地址、目的地址、数据长度等参数。

然后,DMA控制器根据这些参数控制总线的访问,直接将数据从外设读取到内存,或者从内存写入到外设。

在数据传输完成后,DMA控制器可以触发中断信号,通知CPU数据传输已完成。

总之,DMA控制器是一种重要的硬件设备,它可以提高数据传输的效率,减轻CPU的负担,实现高速、可靠的数据传输。

通过直接访问内存,它允许外设设备与内存之间进行直接的数据传输,提升系统的整体性能。

DMA控制器工作原理DMA(Direct Memory Access)控制器是一种计算机设备,用于在外设和主内存之间传输数据。

它的工作原理是通过旁路主处理器,直接在外设和内存之间进行数据传输,从而减少对主处理器的干预。

1.初始化:主处理器通过向DMA控制器发送初始化命令,设置传输参数和传输方向等。

DMA控制器根据这些参数进行设置,以确定传输的方式和范围。

2.请求DMA通道:外设在需要与主内存进行数据传输时,向DMA控制器发送请求。

DMA控制器接收到请求后,暂停主处理器的操作,开始控制数据传输。

3.确认DMA通道:DMA控制器检查请求,并通过向外设发送确认信号来确保通道可用。

如果通道不可用,DMA控制器将外设的请求排队,并在通道可用时进行传输。

4.寻址:DMA控制器从外设中读取数据的地址,并从主内存中读取或写入数据的地址。

这些地址将用于确定传输的起始位置和目的位置。

5.数据传输:DMA控制器将数据从外设读取到内存,或者从内存写入到外设。

数据传输过程中,DMA控制器通过DMA总线直接与内存进行通信,跳过主处理器。

6.中断通知:当传输完成时,DMA控制器会向主处理器发送中断请求,以便主处理器可以执行与传输相关的操作。

从以上步骤可以看出,DMA控制器在传输数据时,与主处理器并行工作,极大地提高了数据传输效率。

相比由主处理器执行的数据传输,DMA 控制器具有以下优势:1.减少主处理器负担:数据传输由DMA控制器完成,主处理器无需处理大量数据传输的细节和中断请求,从而减少了主处理器的负担,提高了系统的整体性能。

2.提高数据传输效率:DMA控制器通过直接访问内存,跳过主处理器的介入,减少了数据传输的延迟,提高了传输的效率。

3.支持多种外设:DMA控制器可以同时支持多种外设,通过适当的配置,可以使多个外设同时进行数据传输。

4.支持高速数据传输:由于DMA控制器是专门设计用于数据传输的设备,其硬件结构和数据通路优化,能够支持高速数据传输,提高系统的数据吞吐量。

《计算机接口技术》部分习题参考解答第4章 PC机的总线结构和时序4-1 答:总线周期是指CPU从存储器端口或I/O端口存取一个字节所需的时间。

8088/8086基本总线周期由4个时钟周期组成。

IBM PC/XT/A T中,CPU时钟频率是4.77MHz,时钟周期是210ns。

XT机的一个基本总线周期是4个时钟周期,一个输入或输出周期是5个时钟周期。

4-2 答:在T1状态下,8088/8086CPU数据/地址线上是地址信息。

用ALE信号可将地址信息锁存起来。

数据信息在T2开始以后送出。

XT机的AD7~AD0在ALE下降沿控制锁存后送系统地址总线A7~A0。

A19/S6~A16/S3经ALE下降沿控制锁存后送系统地址总线A15~A8;CPU的AD7~AD0在8288发出的DT/!R(数据收发控制信号)和DEN(数据允许)信号控制下,经双向总线驱动器连接到系统数据总线D7~D0,这样,实现了地址和数据及状态信号的分离,使地址信号和数据信号同时分别出现在系统地址总线和数据总线上。

(注意:这里用符号“!”表示逻辑非,对于信号则表示低电平有效,下同。

)4-3 答:PC/XT机中8088的MN/!MX引脚接地,因此工作在最大模式。

8088最大模式系统由8088CPU、8284时钟信号发生器和8288总线控制器组成。

总线控制器发出一些存储器和输出控制信号,接入系统总线后的名称为!IOW、!IOR、!MEMW、!MEMR、ALE信号,此外它还发出中断响应信号!INTA、DT/!R和DEN 等信号。

这些信号是由CPU连接8288的S2、S1、S0三线的电平决定的。

4-4 答:8284时钟发生器的作用是将晶振信号分频,向8088及计算机系统提供符号定时要求的各种时钟信号,并产生准备好和系统复位信号。

CLK信号:4.77MHz,提供XT机时钟频率。

PCLK信号:2.38MHz,分频后供8253使用。

OSC信号:14.31818MHz,供显示器使用。