信号完整性分析PPT

- 格式:ppt

- 大小:2.74 MB

- 文档页数:15

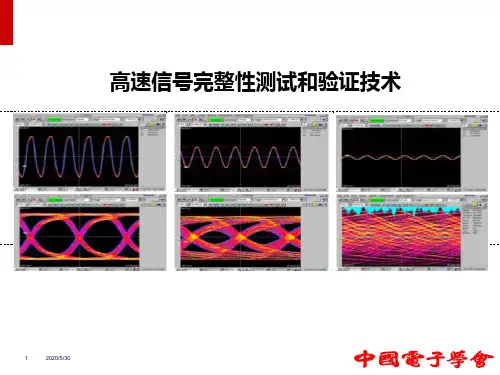

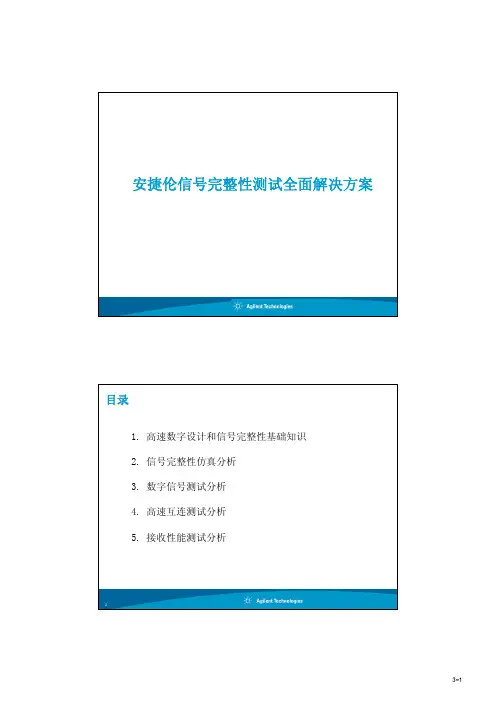

55.接收性能测试分析23PCI-E 1/2/3、RapidIOPCI-E 1/2/3AGP x8DDR2/3、FBD10/100 EthernetGig Ethernet10 Gig ESCSI SAS1/2Fiber ChannelSAS1/2SATA2/3SATA4’97 ’98 ’99 ‘00 ’01 ’02 ’03 ’Parallel SerialProprietaryIBADatacenter Clusters10 Gig E所有的I/O 总线都向串行发展数据速率越来越快(>1Gbps)上升时间越来越快反射越来越大5要在频域进行数据的分析6+5 VoltSupplyGround+5 VoltSupplyGround7。

¾过孔;8¾电磁辐射;•。

可见,信号完整性设计的考虑因素是多方面的,设计中应把握主要方面,减少不确定性。

9 10典型信号完整性现象3:串行信号眼图问题原因很多:阻抗不连续,损耗阻抗不连续,损耗 (11)眼图概念12串行数据的软件时钟恢复方式138参考: Bell Communications Research, Inc (Bellcore), “Synchrouous Optical Network (SONET) Transport Systems: Common Generic Criteria, TR-253-CORE”, Issue 2, Rev No. 1, December19971415•热噪声(RJ)•占空比失真(DCD)•电源噪声(RJ, PJ)•芯片内部耦合(PJ, ISI)•匹配错误(ISI)另外一个含义是指数字信号的上升与下降(或称信号的跳变)非常之快16,当信号的上升时间小于6倍(有说4倍)信号传输延时(电长度)时即认为信号是高速信号,而与信号的频率无关。

t rise<t prop delay• 617安捷伦信号完整性测试分析全套解决方案18Receiver M tl b V il A20CardPackage•Matlab, Verilog_A结果测量•TDR and TDT•2-port and 4-port VNA•Eye Diagram•Advanced JitterDecoder ReceiverEqualizerSignal Recovery建模——传输线Account for impedance, delay, conductor loss, dielectric loss, and couplingMultilayer Interconnect Models use a built-in field-solver, and have both layout and schematic representationsMomentum EM simulator for arbitrary planar structures. Has layout and schematic representationsAnalytic models are fast,and have a layout andschematic representation21•2D Via model vertical current•3D Via model vertical and horizontal currents •Advanced Slot Via modeling22频域通道仿真•S-Parameter Measurements•Z-Parameters Measurements•Y-Parameter Measurements•Group Delay23Monte Carlo Simulation Dielectric Constant variation (10%) High Frequency Response Degradation Rise/Fall Performance is EffectedTDR/TDT仿真24I/O驱动+ 互连仿真For illustration purpose we used Virtex-II Pro I/O simulation in this example25Allegro PCB Design Environment ADS design and simulation environment 262D/3D电磁场仿真isolated traceharmonic signal0.4 GHzoutput27S(1,1)isolated traceS(1,2)isolated trace 仿真结果查看——眼图和模板280810001E-3129-400-2000200400-6006000.20.40.60.80.0Time, fsecDDJHistDDJFHistDDJRHist-6-4-20246-88200400600800Time, psecTJHistRJPJHistDDJHist0.20.40.60.80.0 1.0UI308参考: Bell Communications Research, Inc (Bellcore), “Synchrouous Optical Network (SONET) Transport Systems: Common Generic Criteria, TR-253-CORE”, Issue 2, Rev No. 1, December19973132PeriodicJitter (PJ)Data DependentJitter (DDJ)Inter-symbolInterference (ISI)Duty CycleDistortion (DCD)Sub Rate Jitter(SRJ)UncorrelatedPJ33•热噪声(RJ)•占空比失真(DCD)•电源噪声(RJ, PJ)•芯片内部耦合(PJ, ISI)•匹配错误(ISI) 86100C 一键式抖动测试和分析34EZJIT+:基本抖动分析SignalTrendHistogramSpectrum 35EZJIT+:高级抖动分析36s3775050100150200250Actual TJ (ps)Fa数字信号的眼图38眼图模板39串行数据的时钟恢复方式40以恢复的每一个时钟累积显示可到实时眼图同时可以调用模板测试41模板测试有问题,可以定位具体有问题的数据位42以恢复的时钟为基准可以进行8b/10b解码43可以进行串行触发和搜索44并行总线时钟恢复和眼图形成例中:DDR 建立时间/保持时间模板读写分开,隔离3态45创新的图形化触发功能:InfiniiScanZone Qualify “must / must not pass” zonesGeneral Serial Software Trigger can isolate eventsup to 80 bitRunt software finder 46finds Runt signal like the hardware solutionNon-monotonic Edge finder isolates non-monotonic edge no hardware solution canDDR2Read/Write触发–InfiniiScan47READ・WRITE SignalsExisting TogetherWRITE Only Trigger48340MHz 3.4GHz均衡测试结果3.4Gb/s signal49Eye Pattern without Equalizer Eye Pattern with Equalizer示波器和逻辑分析仪集成调试90000系列示波器13 GHz16900系列逻辑分析系统9000系列示波器5016800系列逻辑分析仪5000/6000/7000 便携式示波器100 MHz4、本底噪声是同类仪器的1/3~1/2!52本底噪声是同类仪器的5、触发抖动是同类仪器的1/10;6、40GSa/s 采样下,波形捕获速率比同类仪器快100倍。