makefile的编写

- 格式:ppt

- 大小:701.00 KB

- 文档页数:67

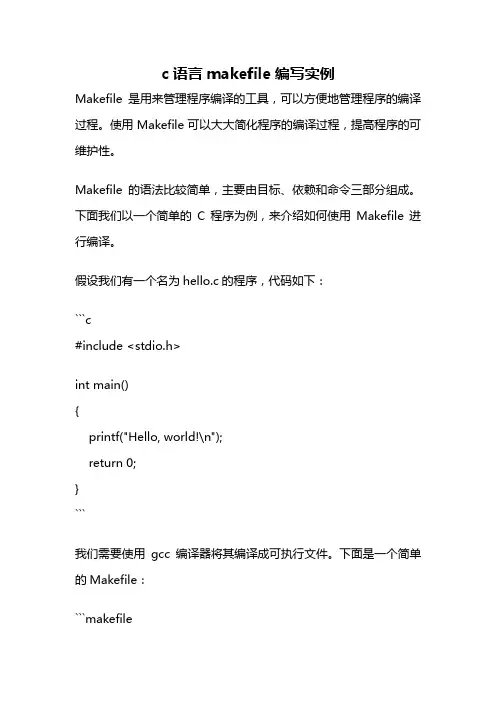

c语言makefile编写实例Makefile是用来管理程序编译的工具,可以方便地管理程序的编译过程。

使用Makefile可以大大简化程序的编译过程,提高程序的可维护性。

Makefile的语法比较简单,主要由目标、依赖和命令三部分组成。

下面我们以一个简单的C程序为例,来介绍如何使用Makefile进行编译。

假设我们有一个名为hello.c的程序,代码如下:```c#include <stdio.h>int main(){printf("Hello, world!\n");return 0;}```我们需要使用gcc编译器将其编译成可执行文件。

下面是一个简单的Makefile:```makefilehello: hello.cgcc -o hello hello.c```这个Makefile很简单,它定义了一个名为hello的目标,该目标依赖于hello.c文件,并使用gcc命令将其编译成可执行文件。

如果我们在终端中输入make命令,Makefile会自动执行编译过程:```$ makegcc -o hello hello.c```Makefile还可以定义多个目标,每个目标可以有多个依赖和多个命令。

下面是一个稍微复杂一些的Makefile:```makefileCC=gccCFLAGS=-Wall -gall: hello goodbyehello: hello.o$(CC) $(CFLAGS) -o hello hello.ogoodbye: goodbye.o$(CC) $(CFLAGS) -o goodbye goodbye.ohello.o: hello.c$(CC) $(CFLAGS) -c hello.cgoodbye.o: goodbye.c$(CC) $(CFLAGS) -c goodbye.cclean:rm -f *.o hello goodbye```这个Makefile定义了两个目标:all和clean。

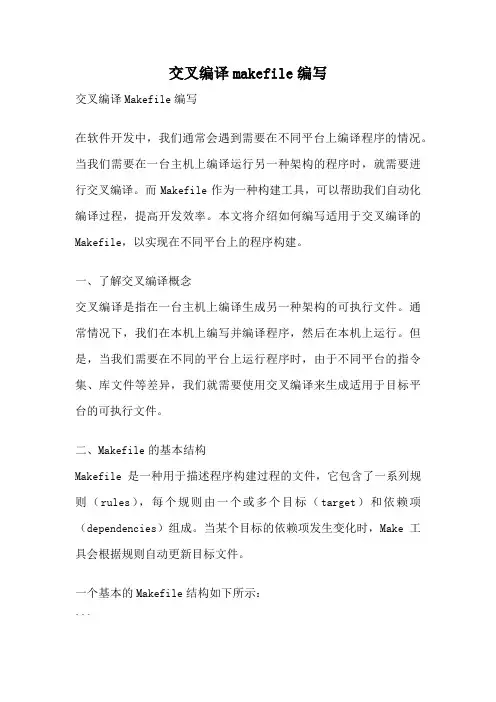

交叉编译makefile编写交叉编译Makefile编写在软件开发中,我们通常会遇到需要在不同平台上编译程序的情况。

当我们需要在一台主机上编译运行另一种架构的程序时,就需要进行交叉编译。

而Makefile作为一种构建工具,可以帮助我们自动化编译过程,提高开发效率。

本文将介绍如何编写适用于交叉编译的Makefile,以实现在不同平台上的程序构建。

一、了解交叉编译概念交叉编译是指在一台主机上编译生成另一种架构的可执行文件。

通常情况下,我们在本机上编写并编译程序,然后在本机上运行。

但是,当我们需要在不同的平台上运行程序时,由于不同平台的指令集、库文件等差异,我们就需要使用交叉编译来生成适用于目标平台的可执行文件。

二、Makefile的基本结构Makefile是一种用于描述程序构建过程的文件,它包含了一系列规则(rules),每个规则由一个或多个目标(target)和依赖项(dependencies)组成。

当某个目标的依赖项发生变化时,Make工具会根据规则自动更新目标文件。

一个基本的Makefile结构如下所示:```target: dependenciescommand```其中,target表示目标文件,dependencies表示目标文件的依赖项,command表示生成目标文件的命令。

三、交叉编译的Makefile编写在编写交叉编译的Makefile之前,我们需要了解目标平台的相关信息,如架构、编译器、库文件等。

以ARM架构为例,我们可以使用arm-linux-gnueabi-gcc作为交叉编译器。

我们需要定义一些变量,用于指定交叉编译工具链和相关参数:```CC = arm-linux-gnueabi-gccCFLAGS = -Wall -O2```其中,CC表示编译器,CFLAGS表示编译参数。

接下来,我们可以定义目标文件和依赖项:```TARGET = myprogramSRCS = main.c foo.c bar.cOBJS = $(SRCS:.c=.o)```其中,TARGET表示目标文件,SRCS表示源文件列表,OBJS表示目标文件列表。

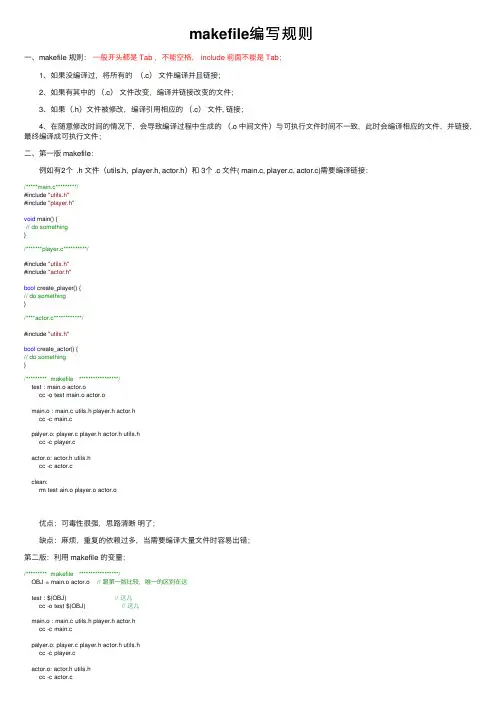

makefile编写规则⼀、makefile 规则:⼀般开头都是 Tab ,不能空格, include 前⾯不能是 Tab; 1、如果没编译过,将所有的(.c)⽂件编译并且链接; 2、如果有其中的(.c)⽂件改变,编译并链接改变的⽂件; 3、如果(.h)⽂件被修改,编译引⽤相应的(.c)⽂件, 链接; 4、在随意修改时间的情况下,会导致编译过程中⽣成的(.o 中间⽂件)与可执⾏⽂件时间不⼀致,此时会编译相应的⽂件,并链接,最终编译成可执⾏⽂件;⼆、第⼀版 makefile: 例如有2个 .h ⽂件(utils.h, player.h, actor.h)和 3个 .c ⽂件( main.c, player.c, actor.c)需要编译链接:/*****main.c*********/#include "utils.h"#include "player.h"void main() {// do something}/*******player.c**********/#include "utils.h"#include "actor.h"bool create_player() {// do something}/****actor.c************/#include "utils.h"bool create_actor() {// do something}/********* makefile *****************/test : main.o actor.occ -o test main.o actor.omain.o : main.c utils.h player.h actor.hcc -c main.cpalyer.o: player.c player.h actor.h utils.hcc -c player.cactor.o: actor.h utils.hcc -c actor.cclean:rm test ain.o player.o actor.o 优点:可毒性很强,思路清晰明了; 缺点:⿇烦,重复的依赖过多,当需要编译⼤量⽂件时容易出错;第⼆版:利⽤ makefile 的变量;/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉main.o : main.c utils.h player.h actor.hcc -c main.cpalyer.o: player.c player.h actor.h utils.hcc -c player.cactor.o: actor.h utils.hcc -c actor.c .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ) // 前⾯的(-)表⽰,执⾏过程中不 care 出错;第三版:利⽤ GUN make 的⾃动推导规则 当 make 看到(.o )⽂件,他会⾃动把(.c)⽂件加上依赖关系,包括执⾏的语句(cc -c xx.c);/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉main.o : utils.h player.h actor.hpalyer.o: player.h actor.h utils.hactor.o: actor.h utils.h .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ)第四版:对第三版的整理(有⼀些重复的 .h) 公共的⼀起依赖,单独的单独依赖/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉$(OBJ) : utils.h actor.omain.o player.o .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ)优点:简洁缺点:不好理解以上的makefike⽂件的基本写法;或许你也发现了,如果有⼏百个源⽂件咋整呢,光是⽬录就要晕死,下⾯就是针对这种情况来说⼀下⼤型⼯程 makefile 的编写设计⼆、⼤型项⽬makefile编写: Makefile 同样也有像 c / c++ 类似的include功能; 例如我们有⼀堆 a.mk , b.mk以及 foo.make和⼀个变量 $(bar),其包含了 e.mk,f.mk, 那么 include foo.make *.mk $(bar) ------- 等价-------》 include foo.make a.mk b.mk e.mk f.mk。

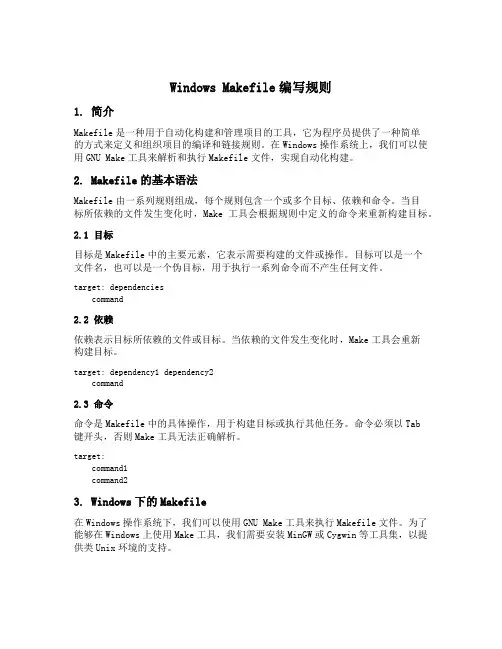

Windows Makefile编写规则1. 简介Makefile是一种用于自动化构建和管理项目的工具,它为程序员提供了一种简单的方式来定义和组织项目的编译和链接规则。

在Windows操作系统上,我们可以使用GNU Make工具来解析和执行Makefile文件,实现自动化构建。

2. Makefile的基本语法Makefile由一系列规则组成,每个规则包含一个或多个目标、依赖和命令。

当目标所依赖的文件发生变化时,Make工具会根据规则中定义的命令来重新构建目标。

2.1 目标目标是Makefile中的主要元素,它表示需要构建的文件或操作。

目标可以是一个文件名,也可以是一个伪目标,用于执行一系列命令而不产生任何文件。

target: dependenciescommand2.2 依赖依赖表示目标所依赖的文件或目标。

当依赖的文件发生变化时,Make工具会重新构建目标。

target: dependency1 dependency2command2.3 命令命令是Makefile中的具体操作,用于构建目标或执行其他任务。

命令必须以Tab键开头,否则Make工具无法正确解析。

target:command1command23. Windows下的Makefile在Windows操作系统下,我们可以使用GNU Make工具来执行Makefile文件。

为了能够在Windows上使用Make工具,我们需要安装MinGW或Cygwin等工具集,以提供类Unix环境的支持。

3.1 安装MinGWMinGW是一个Windows上的开发工具集,它提供了一系列的GNU工具,包括GCC编译器和Make工具。

我们可以通过以下步骤来安装MinGW:1.下载MinGW安装程序,可以从官方网站或镜像站点下载。

2.运行安装程序,选择需要安装的组件,包括GCC编译器和Make工具。

3.设置安装路径,并完成安装。

3.2 编写Makefile在Windows下编写Makefile与在Unix系统下基本相同,只是需要注意路径的表示方式。

makefile编写规则 ifeq什么是makefile?makefile是一种用于自动化构建程序的工具,它能够根据文件之间的依赖关系,自动决定哪些文件需要重新编译。

makefile由一系列规则组成,每个规则定义了如何生成一个或多个目标文件。

make命令会根据这些规则来执行相应的操作,从而实现自动化构建的功能。

ifeq规则的作用在makefile中,ifeq是一种条件语句,用于判断某个条件是否为真。

它的基本语法如下:ifeq (condition, value)# 条件为真时执行的操作else# 条件为假时执行的操作endifcondition是一个条件表达式,可以使用各种比较运算符来进行比较。

value是一个字符串,用于与condition进行比较。

如果condition和value相等,则条件为真,执行ifeq后面的操作;否则条件为假,执行else后面的操作。

ifeq规则的使用场景ifeq规则在makefile中的使用场景很多,下面列举了几个常见的用法:1. 根据不同的操作系统执行不同的操作在跨平台开发中,可能需要根据不同的操作系统执行不同的操作。

可以使用ifeq 规则来判断当前的操作系统,然后执行相应的操作。

ifeq ($(OS),Windows_NT)# Windows系统下的操作CC = clelse# 非Windows系统下的操作CC = gccendif上面的示例中,如果当前操作系统是Windows,则将CC变量设置为cl;否则,将CC变量设置为gcc。

2. 根据变量的值执行不同的操作有时候需要根据某个变量的值来执行不同的操作。

可以使用ifeq规则来判断变量的值,然后执行相应的操作。

ifeq ($(DEBUG),1)# 调试模式下的操作CFLAGS = -gelse# 非调试模式下的操作CFLAGS =endif上面的示例中,如果DEBUG变量的值为1,则将CFLAGS变量设置为-g;否则,将CFLAGS变量设置为空。

很高兴接到您的指示,让我来帮助您撰写关于sv中makefile文件的文章。

让我们来深入了解一下makefile文件的概念和作用。

1. 什么是makefile文件?在SV(SystemVerilog)编程中,makefile文件是用来组织和管理编译工程中的各个源文件和依赖关系的文件。

它定义了编译规则和指令,用于自动化编译和构建整个项目。

2. makefile文件的基本结构在编写makefile文件时,通常会包含以下基本元素:- 变量定义:定义编译器、编译选项、源文件列表等变量。

- 规则定义:定义编译规则,包括目标文件、依赖文件和编译指令。

- 依赖关系:明确指出各个源文件之间的依赖关系,以便make工具能够正确地进行编译。

3. sv中makefile文件的写法在SV项目中,编写makefile文件需要特别关注以下几点:- 定义变量:可以通过定义变量来指定编译器、编译选项、原文件列表等信息,使得makefile文件更加灵活和可维护。

- 设置规则:需要设置好编译规则,包括目标文件、依赖文件和编译指令。

这些规则应该准确反映出SV项目的结构和依赖关系。

- 定义依赖:在makefile文件中,需要清晰地定义各个源文件之间的依赖关系,以确保make工具能够正确地进行增量编译,提高编译效率。

4. 个人观点和理解在我看来,编写高质量的makefile文件对于SV项目的管理和维护至关重要。

一个良好的makefile文件可以提高项目的编译效率,简化编译过程,并且便于团队协作和代码管理。

在编写makefile文件时,应该注重规范和细节,以确保项目的可维护性和稳定性。

总结回顾通过编写这篇文章,我深入了解了sv中makefile文件的写法,并且通过我的个人观点和理解对这个主题进行了探讨。

在文章中多次提及了主题文字,并采用了从简到繁、由浅入深的方式来探讨主题,以便您能更深入地理解。

希望这篇文章能够对您有所帮助。

以上是我为您准备的关于sv中makefile文件的文章,希望能够满足您的要求。

Python Makefile编写规则随着Python语言的流行和应用范围的不断扩大,开发人员在日常工作中经常会用到Makefile来管理代码的编译和部署过程。

Makefile 是一个用于组织代码编译和部署流程的工具,它可以帮助开发人员自动化代码构建的过程,提高工作效率。

在Python项目中,编写规范的Makefile可以帮助开发人员管理项目中繁杂的编译和部署过程,本文将介绍Python Makefile编写的规则和技巧。

一、Makefile简介Makefile是一个包含一系列规则的文件,用于指定代码的编译和部署过程。

它通常由一系列规则、依赖关系和命令组成,它告诉make命令如何编译和信息代码。

Makefile通常用于C/C++项目的编译,但在Python项目中同样有着广泛的应用。

二、Python Makefile编写规则1. 定义变量在编写Python Makefile时,首先需要定义一些变量,这些变量可以用于存储编译器、编译选项、源文件目录、目标文件目录等。

下面是一个简单的Python Makefile示例:```MakefileCC = pythonCFLAGS = -O2SRC_DIR = srcOBJ_DIR = obj```2. 定义规则在Makefile中,可以定义一系列规则来指定如何编译和信息代码。

在Python项目中,通常会定义编译规则、信息规则和清理规则。

下面是一个简单的Python Makefile示例:```Makefileall: $(OBJ_DIR)/m本人n.o$(CC) $(CFLAGS) $(OBJ_DIR)/m本人n.o -o app$(OBJ_DIR)/m本人n.o: $(SRC_DIR)/m本人n.py$(CC) $(CFLAGS) -c $(SRC_DIR)/m本人n.py -o $(OBJ_DIR)/m本人n.oclean:rm -f $(OBJ_DIR)/*.o app```在上面的示例中,定义了三个规则:all规则用于编译信息代码生成可执行文件,$(OBJ_DIR)/m本人n.o规则用于编译源文件生成目标文件,clean规则用于清理生成的目标文件和可执行文件。

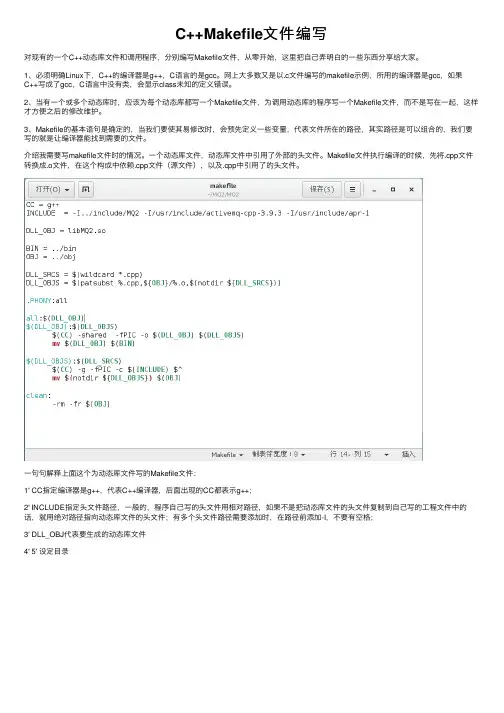

C++Makefile⽂件编写

对现有的⼀个C++动态库⽂件和调⽤程序,分别编写Makefile⽂件,从零开始,这⾥把⾃⼰弄明⽩的⼀些东西分享给⼤家。

1、必须明确Linux下,C++的编译器是g++,C语⾔的是gcc。

⽹上⼤多数⼜是以.c⽂件编写的makefile⽰例,所⽤的编译器是gcc,如果

C++写成了gcc,C语⾔中没有类,会显⽰class未知的定义错误。

2、当有⼀个或多个动态库时,应该为每个动态库都写⼀个Makefile⽂件,为调⽤动态库的程序写⼀个Makefile⽂件,⽽不是写在⼀起,这样才⽅便之后的修改维护。

3、Makefile的基本语句是确定的,当我们要使其易修改时,会预先定义⼀些变量,代表⽂件所在的路径,其实路径是可以组合的,我们要写的就是让编译器能找到需要的⽂件。

介绍我需要写makefile⽂件时的情况。

⼀个动态库⽂件,动态库⽂件中引⽤了外部的头⽂件。

Makefile⽂件执⾏编译的时候,先将.cpp⽂件转换成.o⽂件,在这个构成中依赖.cpp⽂件(源⽂件),以及.cpp中引⽤了的头⽂件。

⼀句句解释上⾯这个为动态库⽂件写的Makefile⽂件:

1' CC指定编译器是g++,代表C++编译器,后⾯出现的CC都表⽰g++;

2' INCLUDE指定头⽂件路径,⼀般的,程序⾃⼰写的头⽂件⽤相对路径,如果不是把动态库⽂件的头⽂件复制到⾃⼰写的⼯程⽂件中的话,就⽤绝对路径指向动态库⽂件的头⽂件;有多个头⽂件路径需要添加时,在路径前添加-I,不要有空格;

3' DLL_OBJ代表要⽣成的动态库⽂件

4' 5' 设定⽬录。

makefile编译流程Makefile是一种用于自动化编译的工具,它可以根据源代码文件的依赖关系自动编译出目标文件。

Makefile的编写需要遵循一定的规则和语法,下面将介绍Makefile的编译流程。

1. 编写Makefile文件Makefile文件是一个文本文件,其中包含了编译的规则和依赖关系。

在编写Makefile文件时,需要遵循一定的语法规则,如使用TAB键缩进、使用变量和函数等。

2. 执行make命令在Makefile文件所在的目录下执行make命令,make会自动读取Makefile文件,并根据其中的规则和依赖关系进行编译。

如果Makefile文件中没有指定目标,则默认编译第一个目标。

3. 分析依赖关系在执行make命令时,make会先分析Makefile文件中的依赖关系,确定哪些文件需要重新编译。

如果某个源文件被修改了,那么与之相关的目标文件也需要重新编译。

4. 编译源文件在确定需要重新编译的文件后,make会依次编译每个源文件,生成对应的目标文件。

编译过程中,make会根据Makefile文件中的规则和命令进行编译。

5. 链接目标文件在所有的源文件都编译完成后,make会将所有的目标文件链接起来,生成最终的可执行文件。

链接过程中,make会根据Makefile文件中的规则和命令进行链接。

6. 完成编译当所有的源文件都编译完成并链接成功后,make会输出编译成功的信息,并生成最终的可执行文件。

如果编译过程中出现错误,make会输出错误信息并停止编译。

总之,Makefile编译流程是一个自动化的过程,它可以大大提高编译的效率和准确性。

在编写Makefile文件时,需要注意语法规则和依赖关系,以确保编译过程的正确性。

makefile基本使用方法makefile是一种用来管理和自动化构建程序的工具。

它可以根据源代码文件的依赖关系和编译规则来自动构建目标文件和可执行文件。

makefile的基本使用方法如下:1. 创建makefile文件:在项目的根目录下创建一个名为makefile 的文件。

2. 定义变量:在makefile中,可以使用变量来存储一些常用的参数和路径,以便于后续的使用。

例如,可以定义一个名为CC的变量来指定编译器的名称,如:CC=gcc。

3. 编写规则:在makefile中,可以使用规则来指定如何编译源代码文件和生成目标文件。

一个规则由两部分组成:目标和依赖。

目标是要生成的文件,依赖是生成目标文件所需要的源代码文件。

例如,可以编写以下规则:```target: dependency1 dependency2command1command2```其中,target是目标文件,dependency1和dependency2是依赖的源代码文件,command1和command2是生成目标文件所需要执行的命令。

4. 编写默认规则:在makefile中,可以使用一个默认规则来指定如何生成最终的可执行文件。

默认规则的目标通常是可执行文件,依赖是所有的源代码文件。

例如,可以编写以下默认规则:```all: target1 target2```其中,target1和target2是生成的目标文件。

5. 编写clean规则:在makefile中,可以使用clean规则来清理生成的目标文件和可执行文件。

例如,可以编写以下clean规则: ```clean:rm -f target1 target2```其中,target1和target2是要清理的目标文件。

6. 运行make命令:在命令行中,使用make命令来执行makefile 文件。

make命令会自动根据规则和依赖关系来编译源代码文件和生成目标文件。

例如,可以运行以下命令:``````make命令会根据makefile文件中的规则和依赖关系来编译源代码文件并生成目标文件和可执行文件。

makefile gcc编译

Makefile 是一个用来组织代码编译的工具,而 GCC 是一个常用的 C 和 C++ 编译器。

在 Makefile 中使用 GCC 进行编译可以通过以下步骤完成:

1. 创建一个名为 "Makefile" 的文本文件,并确保它位于你的项目根目录下。

2. 在 Makefile 中定义你的编译规则。

例如,假设你有一个名为 "main.c" 的源文件需要编译成可执行文件 "app",你可以这样编写 Makefile:

make.

app: main.c.

gcc -o app main.c.

在这个例子中,我们定义了一个名为 "app" 的目标,它依赖于"main.c" 这个源文件。

当你运行 "make" 命令时,Make 工具会根

据这个规则来执行编译。

3. 打开终端,进入到包含 Makefile 的项目目录下。

4. 运行命令 "make"。

Make 工具会读取 Makefile 文件,并执行其中定义的编译规则。

在这个例子中,它会使用 GCC 编译器来编译 "main.c" 并生成可执行文件 "app"。

需要注意的是,Makefile 可以包含更复杂的规则和变量定义,以及支持多个源文件的编译。

你可以根据你的项目需求来进一步扩展和定制 Makefile 文件。

总之,通过合理编写 Makefile 并结合使用 GCC 编译器,你可以高效地组织和管理你的代码编译过程。

文档简要整理Android的make脚本的内容。

以供备忘和参考。

1. Build LayersBuild Layers描述的是产品的硬件配置情况,据此make时选择不同的配置和模块。

按照从上到下的顺序,Build Layer分成4层。

Layer sample NoteArch arm, x86 处理器的种类Board -板子类型的代号Device - device配置的类型代号Product -具体产品的代号2. 添加应用2.1 一个例子以calculator为例,app代码可以放到packages/apps/目录下边,一个app对应一个目录,此例,pakcages/apps/Calculator/。

创建Android.mk,已去除多余的注释行。

LOCAL_PATH := $(call my-dir)include $(CLEAR_VARS)LOCAL_MODULE_TAGS := optionalLOCAL_STATIC_JAVA_LIBRARIES := libarityLOCAL_SRC_FILES := $(call all-java-files-under, src)LOCAL_SDK_VERSION := currentLOCAL_PACKAGE_NAME := Calculatorinclude $(BUILD_PACKAGE)include $(CLEAR_VARS)LOCAL_PREBUILT_STATIC_JAVA_LIBRARIES := libarity:arity-2.1.2.jarinclude $(BUILD_MULTI_PREBUILT)# Use the folloing include to make our test apk.include $(call all-makefiles-under,$(LOCAL_PATH))至少有一个子目录,src下放源码。

Android.mk中需要赋值的几个LOCAL_XXX变量,LOCAL_PATH,调用my-dir(在defination.mk中定义),得到当前路径,即,<yourSrcPath>/ pakcages/apps/Calculator/。

vivado makefile文件编写实例如何编写Vivado Makefile 文件。

Vivado 是一款由Xilinx 公司开发的集成电路设计工具,它提供了丰富的设计和仿真功能,可以用于设计和验证各种数字电路。

Makefile 是一种用于自动化构建和管理项目的文件,它可以定义编译、链接和运行等操作的规则。

在Vivado 中使用Makefile 可以方便地管理项目的编译和仿真过程,提高开发效率。

本文将以中括号内的内容为主题,一步一步回答如何编写Vivado Makefile 文件。

一、创建Makefile 文件首先,在Vivado 工程目录下创建一个名为Makefile 的文件。

可以使用文本编辑器或者命令行工具创建该文件。

二、Makefile 基本结构Makefile 是按照一定的规则编写的,它由一系列的规则定义组成,每个规则包含一个或多个目标、依赖和命令。

规则的语法如下:target: dependenciescommand其中,target 是规则的目标,dependencies 是目标的依赖,command 是执行的命令。

三、Vivado Makefile 常用规则1. all:编译和仿真整个工程all: build sim上述规则定义了一个名为all 的目标,它依赖于build 和sim 两个目标,执行的命令为空。

2. build:编译工程build:vivado -mode batch -source build.tcl上述规则定义了一个名为build 的目标,它执行vivado 命令,并传入-mode batch 和-source build.tcl 两个参数。

这里的build.tcl 是一个Vivado Tcl 脚本,用于自动化执行编译操作。

3. sim:仿真工程sim:vivado -mode batch -source sim.tcl上述规则定义了一个名为sim 的目标,它执行vivado 命令,并传入-mode batch 和-source sim.tcl 两个参数。

makefile编写规则 ifeq【实用版】目录1.Makefile 简介2.Makefile 编写规则3.ifeq 函数的作用4.ifeq 函数的语法5.ifeq 函数的实例6.结论正文1.Makefile 简介Makefile 是一种用于自动化构建和编译软件的脚本文件。

它通常包含一系列的规则,用于指定如何构建和编译源代码。

Makefile 的主要目的是为了简化和自动化构建过程,以便开发者能够更专注于编写代码。

2.Makefile 编写规则在 Makefile 中,编写规则通常遵循以下格式:```目标:依赖文件t命令```其中,目标表示要构建的文件,依赖文件表示构建目标所需的输入文件,命令表示用于构建目标的命令。

例如,要编译一个名为“main.c”的源文件,可以编写如下规则:```main.o: main.ctgcc -c main.c```3.ifeq 函数的作用ifeq 函数是 Makefile 中的一种条件函数,用于根据某个条件决定是否执行相应的命令。

它可以帮助开发者根据不同的环境或配置选择性地执行代码。

4.ifeq 函数的语法ifeq 函数的语法如下:```ifeq (条件)ttrue-casetfalse-caseelsetelse-caseendif```其中,条件是一个逻辑表达式,true-case 和 false-case 分别表示条件为真和假时执行的命令。

else-case 是可选的,用于表示条件不满足时执行的命令。

5.ifeq 函数的实例假设我们希望根据不同的操作系统选择不同的编译器选项,可以编写如下 Makefile 规则:```%.o: %.ctifeq ($(OS), Linux)ttgcc -o $@ $< -std=gnu99telsettgcc -o $@ $< -std=ansitendif```在这个例子中,我们使用 ifeq 函数根据当前操作系统($(OS))选择不同的编译器选项。

makefile编写规则 ifeqifeq是makefile中的一个条件判断语句,用于判断变量的值是否相等。

在makefile中,ifeq语句的基本语法如下:ifeq(条件1, 条件2)条件1和条件2相等时执行的命令else条件1和条件2不相等时执行的命令endififeq语句可以用在makefile中的任何地方,用于根据条件来执行相应的命令。

在本文中,我们将重点讨论ifeq语句的用法及其在makefile 中的应用。

一、ifeq语句的基本用法ifeq语句的基本用法是用来比较两个变量的值是否相等,如果相等则执行相应的命令,否则执行另外的命令。

在makefile中,ifeq语句通常用在条件判断中,如下所示:```makefileifeq ($(VAR1), $(VAR2))echo "VAR1和VAR2相等"elseecho "VAR1和VAR2不相等"endif```上面的示例中,我们使用ifeq语句来比较变量VAR1和VAR2的值是否相等,如果相等则执行echo "VAR1和VAR2相等",否则执行echo "VAR1和VAR2不相等"。

这样我们可以根据条件来执行不同的命令,以实现makefile的灵活控制。

二、ifeq语句的扩展用法除了用来比较变量的值是否相等外,ifeq语句还可以用来比较其他条件,如下所示:```makefileifeq ($(shell uname), Linux)echo "当前系统是Linux"else ifeq ($(shell uname), Darwin)echo "当前系统是MacOS"elseecho "当前系统不是Linux也不是MacOS"endif```上面的示例中,我们使用ifeq语句来判断当前系统类型,如果是Linux则执行echo "当前系统是Linux",如果是MacOS则执行echo "当前系统是MacOS",如果既不是Linux也不是MacOS则执行echo "当前系统不是Linux也不是MacOS"。

SV(SystemVerilog)是一种硬件描述语言,用于设计和验证数字电路。

在进行SV代码编写的过程中,makefile是一种非常有用的工具,可以帮助组织和管理SV项目中的代码文件。

本文将介绍SV中makefile的写法,希望能为SV开发者提供一些参考和帮助。

1. 为什么需要makefile在SV项目中,通常会涉及到多个源文件、库文件、测试文件等。

使用makefile可以帮助我们轻松地组织和管理这些文件,实现自动化编译、信息和运行测试的功能。

makefile还可以帮助我们避免重复编译文件,提高开发效率。

2. makefile的基本结构makefile由一系列规则组成,每个规则由一个目标、依赖列表和命令组成。

一个基本的makefile看起来像这样:```makefiletarget: dependenciesmand```其中,target表示规则的目标文件,dependencies表示该目标文件的依赖文件mand表示需要执行的命令。

3. 使用变量在makefile中,我们可以使用变量来定义一些常量,方便我们在后续的规则中使用。

例如:```makefileSV_SRC = file1.sv file2.sv file3.sv```这样,我们就可以在后续的规则中使用$(SV_SRC)来表示这些文件,而不需要重复地写出它们的文件名。

4. 基本规则在SV项目中,常见的makefile规则包括编译规则、信息规则和运行测试规则。

以下是一个简单的例子:```makefileall: $(SV_SRC)vlog $(SV_SRC)sim: allvsim top_module```在这个例子中,我们定义了两个规则,分别是all和sim。

all规则依赖于$(SV_SRC)中的文件,使用vlog命令对这些文件进行编译。

sim规则依赖于all规则,使用vsim命令来运行测试。

5. 使用通配符在makefile中,我们还可以使用通配符来表示一类文件。

windows makefile编写规则【实用版】目录1.编写 Makefile 的必要性2.Makefile 的基本结构3.变量定义4.规则与依赖关系5.编写 Windows Makefile 的注意事项正文一、编写 Makefile 的必要性在软件开发过程中,我们常常需要编译和链接源代码以生成可执行文件。

尤其是在大型项目中,如何自动化地管理这些编译和链接过程就显得尤为重要。

Makefile 就是在这种情况下应运而生的一种工具,它能帮助我们简化和规范化这个过程。

二、Makefile 的基本结构一个典型的 Makefile 主要包括以下几个部分:1.变量定义:用于设置一些编译选项和路径等。

2.规则:定义了如何将源文件编译成目标文件。

3.依赖关系:描述了目标文件依赖于哪些源文件。

三、变量定义在 Makefile 中,我们可以通过“define”语句来定义变量。

例如:```CC = g++CFLAGS = -g -Wall```上述代码定义了两个变量:CC 和 CFLAGS。

CC 表示编译器,这里设置为 g++;CFLAGS 表示编译选项,这里设置为-g(输出调试信息)和-Wall (启用所有警告)。

四、规则与依赖关系规则和依赖关系是 Makefile 的核心部分,它们描述了如何将源文件编译成目标文件。

规则的一般形式为:```目标文件 : 源文件 1 源文件 2...t$(CC) $(CFLAGS) -o $@ $^```其中,$@表示目标文件,$^表示所有源文件。

依赖关系则是通过“depends”语句来描述的,例如:```target.o : source1.o source2.ot$(CC) $(CFLAGS) -c $< -o $@```五、编写 Windows Makefile 的注意事项在 Windows 系统上编写 Makefile 时,需要注意以下几点:1.路径问题:在 Windows 系统上,路径使用双反斜杠()或者单斜杠(/)表示,需要根据实际情况进行设置。