电子技术基础 模电五版 康华光 习题解答

- 格式:pdf

- 大小:4.96 MB

- 文档页数:198

第二章2.4.1电路如图题2.4.1所示。

(1)利用硅二极管恒压降模型求电路的ID和 Vo的值;(2)在室温(300K)的情况下,利用二极管的小信号模型求vo的变化范围。

解(1)求二极管的电流和电压(2)求vo的变化范围图题2.4.1的小信号模型等效电路如图解2.4.l所示,温度 T=300 K。

VDD-2vD(10-2⨯0.7)V==8.6⨯10-3A=8.6mA3R1⨯10ΩVO=2VD=2⨯0.7V=1.4V ID=当rd1=rd2=rd时,则rd=VT26mV=≈3.02ΩID8.6mA2rd2⨯3.02Ω=±1V⨯=±6mVR+2rd(1000+2⨯3.02Ω)vO的变化范围为(VO+∆vO)~(VO-∆vO),即1.406V~1.394V。

∆vO=∆VDD2.4.3二极管电路如图2.4.3所示,试判断图中的二极管是导通还是截止,并求出AO两端电压VAO。

设二极管是理想的。

解图a:将D断开,以O点为电位参考点,D的阳极电位为-6 V,阴极电位为-12 V,故 D处于正向偏置而导通,VAO=–6 V。

图b:D的阳极电位为-15V,阴极电位为-12V,D对被反向偏置而截止,VAO=-12V。

图c:对D1有阳极电位为 0V,阴极电位为-12 V,故D1导通,此后使D2的阴极电位为0V,而其阳极为-15 V,故D2反偏截止,VAO=0 V。

图d:对D1有阳极电位为12 V,阴极电位为0 V,对D2有阳极电位为12 V,阴极电位为-6V.故D2更易导通,此后使VA=-6V;D1反偏而截止,故VAO =-6V。

2.4.4 试判断图题 2.4.4中二极管是导通还是截止,为什么?解图a:将D断开,以“地”为电位参考点,这时有VA=10kΩ⨯15V=1V(140+10)kΩVB=D被反偏而截止。

图b:将D断开,以“地”为参考点,有2kΩ5kΩ⨯10V+⨯15V=3.5V(18+2)kΩ(25+5)kΩVA=10kΩ⨯15V=1V(140+10)kΩ2kΩ5kΩ⨯(-10V)+⨯15V=1.5V(18+2)kΩ(25+5)kΩ VB=D被反偏而截止。

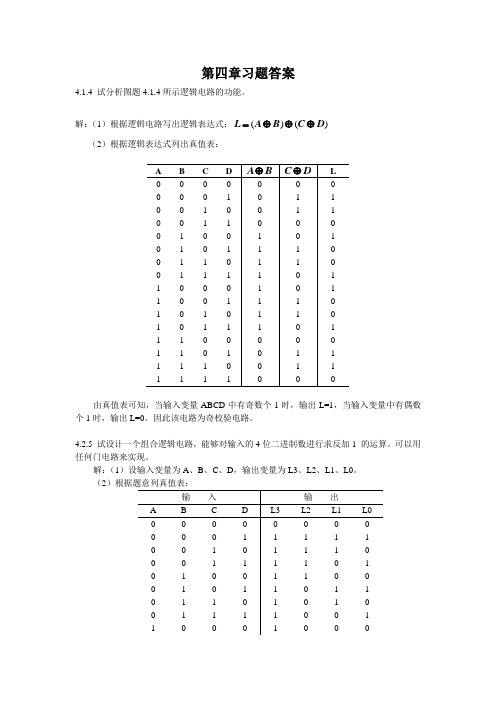

第四章习题答案4.1.4 试分析图题4.1.4所示逻辑电路的功能。

解:(1)根据逻辑电路写出逻辑表达式:()()L A B C D =⊕⊕⊕ (2)根据逻辑表达式列出真值表:由真值表可知,当输入变量ABCD 中有奇数个1时,输出L=1,当输入变量中有偶数个1时,输出L=0。

因此该电路为奇校验电路。

4.2.5 试设计一个组合逻辑电路,能够对输入的4位二进制数进行求反加1 的运算。

可以用任何门电路来实现。

解:(1)设输入变量为A 、B 、C 、D ,输出变量为L3、L2、L1、L0。

(2)根据题意列真值表:(3)由真值表画卡诺图(4)由卡诺图化简求得各输出逻辑表达式()()()3L AB A C AD ABCD A B C D A B C D A B C D =+++=+++++=⊕++ ()()()2L BC BD BCD B C D B C D B CD =++=+++=⊕+ 1L CD CD C D =+=⊕0L D =(5)根据上述逻辑表达式用或门和异或门实现电路,画出逻辑图如下:A B CDL 3L 2L 1L 04.3.1判断下列函数是否有可能产生竞争冒险,如果有应如何消除。

(2)(,,,)(,,,,,,,)2578910111315L A B C D m =∑ (4)(,,,)(,,,,,,,)4024612131415L A B C D m =∑解:根据逻辑表达式画出各卡诺图如下:(2)2L AB BD =+,在卡诺图上两个卡诺圈相切,有可能产生竞争冒险。

消除办法:在卡诺图上增加卡诺圈(虚线)包围相切部分最小项,使2L AB BD AD =++,可消除竞争冒险。

(4)4L AB AD =+,在卡诺图上两个卡诺圈相切,有可能产生竞争冒险。

消除办法:在卡诺图上增加卡诺圈(虚线)包围相切部分最小项,使4L AB AD BD =++,可消除竞争冒险。

4.3.4 画出下列逻辑函数的逻辑图,电路在什么情况下产生竞争冒险,怎样修改电路能消除竞争冒险。

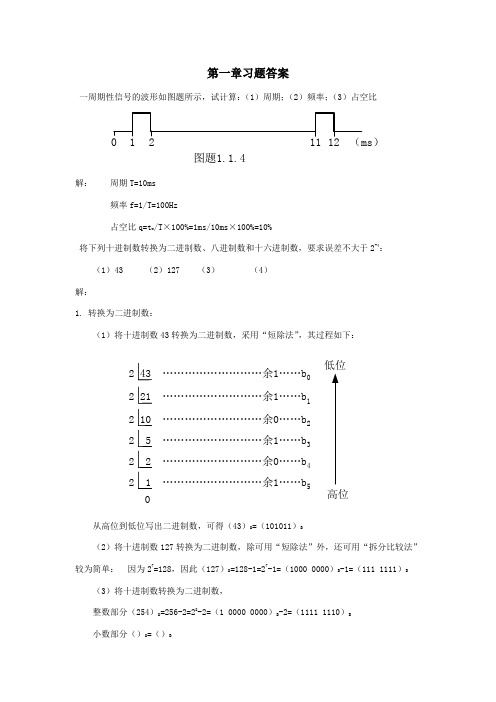

第一章习题答案一周期性信号的波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比0121112(ms)图题1.1.4解: 周期T=10ms 频率f=1/T=100Hz占空比q=t w /T ×100%=1ms/10ms ×100%=10%将下列十进制数转换为二进制数、八进制数和十六进制数,要求误差不大于2-4:(1)43(2)127(3)(4)解:1. 转换为二进制数:(1)将十进制数43转换为二进制数,采用“短除法”,其过程如下:2 43 ………………………余1……b 02 21 ………………………余1……b 12 1 ………………………余1……b 52 2 ………………………余0……b 42 5 ………………………余1……b 32 10 ………………………余0……b 2高位低位从高位到低位写出二进制数,可得(43)D =(101011)B(2)将十进制数127转换为二进制数,除可用“短除法”外,还可用“拆分比较法”较为简单: 因为27=128,因此(127)D =128-1=27-1=(1000 0000)B -1=(111 1111)B(3)将十进制数转换为二进制数,整数部分(254)D =256-2=28-2=(1 0000 0000)B -2=(1111 1110)B 小数部分()D =()B()D=(1111 )B(4)将十进制数转换为二进制数整数部分(2)D=(10)B小数部分()D=()B演算过程如下:0.718×2=1.436……1……b-1 0.436×2=0.872……0……b-2 0.872×2=1.744……1……b-3 0.744×2=1.488……1……b-4 0.488×2=0.976……0……b-5 0.976×2=1.952……1……b-6高位低位要求转换误差小于2-4,只要保留小数点后4位即可,这里算到6位是为了方便转换为8进制数。

1.2.1解:正弦波电压表达式为)sin()(θω+=t V t v m ,由于0=θ,于是得 (1)))(102sin(5)(4V t t v π⨯= (2)))(100sin(2220)(V t t v π= (3)))(2000sin(05.0)(V t t v π= (4)))(1000sin(125.0)(V t t v = 1.2.2解:(1)方波信号在电阻上的耗散功率RV dt TRV dt R t v T P S TS T S 2)(1220202===⎰⎰(2)可知直流分量、基波分量、三次谐波分量分别为2S V 、πS V 2、π32S V,所以他们在电阻上的耗散功率为直流分量:R V R V P S S O 4/222=⎪⎭⎫⎝⎛=基波分量:R V R V P S S22212/212ππ=⎪⎭⎫ ⎝⎛∙=三次谐波分量:R V R V P S S222392/2132ππ=⎪⎭⎫ ⎝⎛∙= (3)三个分量占电阻上总耗散功率的百分比: 前三者之和为:RV R V R V R V P P P P S S S S 2222223103~0475.09224≈++==++=ππ所占百分比:%95%1002//475.0%100)/(223~0=⨯≈⨯R V RV P P S S S 1.4.1解:由图可知,i vo LO Lo i s i i s v A R R R v R R R v v ∙+=+=),(,所以(1)O L S i R R R R 10,10==时,i i s i i s v R R R v v 1011)(=+=, i i vo L O L o v v A R R R v 101110⨯=∙+=,则源电压增益为26.810/1111/100≈==i i s o vs v v v v A 。

同理可得 (2)5.225===iis o vs v v v v A (3)0826.01111/10≈==i i s o vs v v v v A (4)826.010/1111/10≈==i i s o vs v v v v A 1.5.1解:电压增益 200005.01===VV v v A i o v dB A v 46200lg 20lg 20≈=电流增益 1001052000/16=⨯Ω==-AV i i A i o i dB A i 40100lg 20lg 20≈=功率增益 ()200001051052000/1632=⨯⨯⨯Ω==--AV V P P A i o p dB A p 4320000lg 10lg 10≈= 1.5.2解:设负载开路时输出电压为'o v ,负载电阻Ω=k R L 1时输出电压为o v ,根据题意 ()''8.0%201o o o v v v =-= 而 ()L O L oo R R R v v +=//'则 ()()Ω=Ω⨯⨯-=-=25010118.0/11/3'L oo O R v v R1.5.3解:设'o v 为负载电阻断开时的输出电压,即V v o 1.1'=;负载电阻Ω=k R L 1时,输出电压V v o 1=。

康华光《电子技术基础-模拟部分》(第5版)配套模拟试题及详解(一)一、选择题(15×2,共,30分)1.某放大电路在负载开路时的输出电压为4V ,接入12kΩ的负载电阻后,输出电压降为3V ,这说明放大电路的输出电阻为()。

A .19kΩB .2kΩC .4kΩD .3kΩ【答案】C【解析】输出电压为原输出电压的34,所以分压电阻值为原电阻值的34,即1231244k k k Ω=Ω+Ω2.图1电路工作于放大状态,为了使静态工作点I CQ 增大,应该()。

A .减小电阻R 和电容CB .换成β大的管子C .增大电阻R E 的阻值D .减小R B1阻值图1【答案】D【解析】电路是一个典型的利用直流电流串联负反馈稳定静态工作点的三极管分压式偏置电路。

由于i C≈i E,则由上述公式可以看出在题目给出的4个选项中,只有D项能满足题目的要求。

3.和TTL电路相比CMOS电路最突出的优势在()。

A.可靠性高B.抗干扰能力强C.速度快D.功耗低【答案】D【解析】TTL电路以速度见长,CMOS以功耗低而著名。

4.单端输出的差分放大器,能够抑制零点漂移,原因是()。

A.电路参数的对称性B.采用了正负两个直流电源供电C.射级电阻R EE(或恒流源动态电阻)的差模负反馈作用D.射级电阻R EE(或恒流源动态电阻)的共模负反馈作用【答案】A【解析】在差分电路中,无论是温度变化,还是电源电压的波动都会引起两管集电极电流以及相应的集电极电压相同的变化,其效果相当于在两个输入端加入了共模信号,由于电路的对称性和恒流源偏置,在理想情况下,可以使输出电压不变,从而抑制零点漂移。

5.由理想运放构成如图2所示电路,试判断电阻R f反馈的类型属于()。

图2A.串联电压负反馈B.串联电流负反馈C.并联电压负反馈D.并联电流负反馈【答案】A【解析】利用瞬时极性法。

输入为正,输出也为正,反馈电压也为正,使运放的输入减小,所以为负反馈。

第五章作业答案剖析图题所示电路的逻辑功能,列出功能表。

S 1& QR&Q 1图题解:方法(1)将图题所示电路与由与非门组成的基本RS锁存器比较,发现该电路与后者仅在信号输入端分别多了一个非门,尔后者为低电平有效的基本RS锁存器,所以该电路为高电平有效的RS锁存器,功能表以下:S R Q Q锁存器状态00不变不变保持01010101011100不确立方法(2)由逻辑电路图能够获得Q端和Q端的逻辑表达式Q SgQ nQ RgQ依据上边的逻辑表达式,能够获得该锁存器的功能表以下所示:(略,同上表)触发器的逻辑电路如图题所示,确立其属于何种电路构造的触发器,并剖析工作原理。

C CTG3 TG1&&1QD TG TGG3G11C QCTG4C TG2CTGC C TG CCP1CSD &G2&G4RD解:图题所示电路是由两个传输门控D锁存器组成的CMOS主从D触发器。

其中TG1、TG2和G1、G2组成主锁存器,TG3、TG4和G3、G4组成从锁存器,SD和RD分别为直接置1端和直接置0端。

当触发器处于工作状态时,应将他们置于高电平。

工作原理剖析:(1)当CP=0时,C=0,C=1,TG1、TG4导通,TG2、TG3断开。

此时D信号进入锁存器,G1输出D,并随D变化。

因为TG3断开、TG4导通,主从锁存器互相隔绝,从锁存器组成双稳态储存单元,使触发器的输出保持本来的状态不变。

(2)当CP由0跳变到1后,C=1,C=0,TG1、TG4断开,TG2、TG3导通。

此时D 信号与主锁存器之间的联系被切断,TG2的导通使主锁存器保持在CP上涨沿到来以前瞬时的状态。

同时因为TG3导通,G1输出信号送到Q端,获得Q n1D,而且在CP=1时期保持不变。

(3)当CP由1跳变到0后,再次重复(1)的过程。

上涨沿和降落沿触发的D触发器的逻辑符号实时钟信号CP(CP)的波形如图题所示,分别画出他们Q端的波形。

第一章数字逻辑习题1.1数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制2 1.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于4(2)127 (4)2.718解:(2)(127)D=72-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43 (3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1. 6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解: (a)为与非, (b)为同或非,即异或第二章 逻辑代数 习题解答2.1.1 用真值表证明下列恒等式 (3)A B AB AB ⊕=+(A ⊕B )=AB+AB 解:真值表如下A B A B ⊕ABAB A B ⊕AB +AB0 0 0 1 0 1 1 0 1 1 0 0 0 0 1 0 1 0 0 0 0 11111由最右边2栏可知,A B ⊕与AB +AB 的真值表完全相同。

第二章运算放大器2.1 集成电路运算放大器2.1.1答;通常由输入级,中间级,输出级单元组成,输入级由差分式放大电路组成,可以提高整个电路的性能。

中间级由一级或多级放大电路组成,主要是可以提高电压增益。

输出级电压增益为1,可以为负载提供一定的功率。

2.1.2答:集成运放的电压传输曲线由线性区和非线性区组成,线性区的直线的斜率即Vvo 很大,直线几乎成垂直直线。

非线性区由两条水平线组成,此时的Vo达到极值,等于V+或者V-。

理想情况下输出电压+Vom=V+,-Vom=V-。

2.1.3答:集成运算放大器的输入电阻r约为10^6欧姆,输出电阻r约为100欧姆,开环电压增益Avo约为10^6欧姆。

2.2 理想运算放大器2.2.1答:将集成运放的参数理想化的条件是:1.输入电阻很高,接近无穷大。

2.输出电阻很小,接近零。

3.运放的开环电压增益很大。

2.2.2答:近似电路的运放和理想运放的电路模型参考书P27。

2.3 基本线性运放电路2.3.1答:1.同相放大电路中,输出通过负反馈的作用,是使Vn自动的跟从Vp,使Vp≈Vn,或Vid=Vp-Vn≈0的现象称为虚短。

2.由于同相和反相两输入端之间出现虚短现象,而运放的输入电阻的阻值又很高,因而流经两输入端之间Ip=In≈0,这种现象称为虚断。

3.输入电压Vi通过R1作用于运放的反相端,R2跨接在运放的输出端和反相端之间,同相端接地。

由虚短的概念可知,Vn≈Vp=0,因而反相输入端的电位接近于地电位,称为虚地。

虚短和虚地概念的不同:虚短是由于负反馈的作用而使Vp≈Vn,但是这两个值不一定趋向于零,而虚地Vp,Vn接近是零。

2.3.2答:由于净输入电压Vid=Vi-Vf=Vp-Vm,由于是正相端输入,所以Vo为正值,Vo等于R1和R2的电压之和,所以有了负反馈电阻后,Vn增大了,Vp不变,所以Vid变小了,Vo 变小了,电压增益Av=Vo/Vi变小了。

由上述电路的负反馈作用,可知Vp≈Vn,也即虚短。