EDA考试程序(2)

- 格式:doc

- 大小:30.50 KB

- 文档页数:3

EDA设计(二)课程设计报告南京理工大学2015 年月目录1 引言 (2)2 系统总体设计 (2)2.1 系统功能概述 (2)2.2 系统总体组成结构 (2)3 系统各组成模块详细设计 (3)3.1 地址发生器模块 (3)3.2 分频预置数模块 (4)3.3 分频模块 (5)4 系统调试 (7)4.1 系统仿真调试 (7)4.2 系统实际验证 (8)4.3 调试程序遇到的问题及解决方法 (8)5 总结与体会心得 (8)6 参考文献 (9)1 引言电子设计自动化技术(Electronic Design Automation,EDA)已经成为现代电子设计技术的核心。

EDA技术就是依赖功能强大的计算机,在EDA工具平台上,对以硬件描述语言(HDL)为系统逻辑描述手段完成的设计文件,自动的完成逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至下载到可编程逻辑器件CPLD/FPGA或专用集成电路ASIC芯片中。

硬件描述语言(HDL)是EDA技术的重要组成部分,其中VHDL语言应用广泛,是电子设计主流硬件的描述语言之一,它以强大的系统描述能力、规范的程序设计结构、灵活的语句表达风格和多层次的仿真测试手段,受到了业界的普遍认同和广泛接受。

本设计采用SE-5M 型EDA 实验开发系统,以Altera 公司的MAX+PLUS II 为开发软件,用VHDL语言采用自顶向下的设计方法,实现了一个音乐播放器,实现播放完整曲目的动能。

2 系统总体设计2.1 系统功能概述本文设计的数字系统是一个音乐播放器,其主要功能如下:(1)对系统时钟频率进行分频,可以发出高音、中音、低音区任意的音符。

(2)可以播放完整的曲目《怒放的生命》,此外,也可以输入其他乐谱,演奏相应的曲目。

2.2系统总体组成结构系统由地址发生器模块、分频预置数模块、分频模块3个模块构成。

硬件电路的发生原理是利用程序来控制FPGA某个引脚输出一定频率的矩形波,接上扬声器就能发出相应频率的声音。

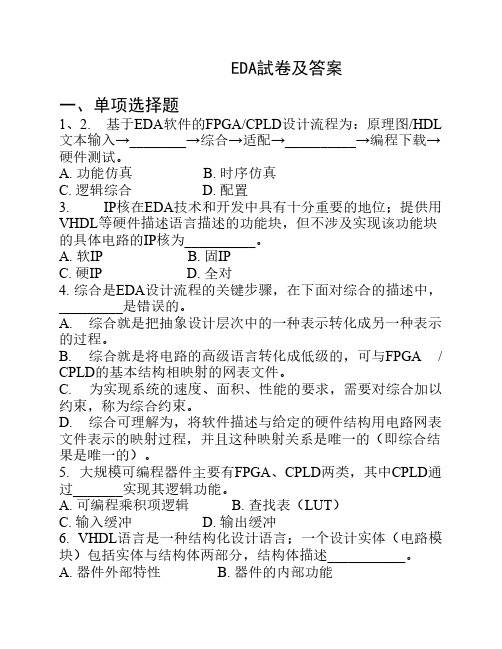

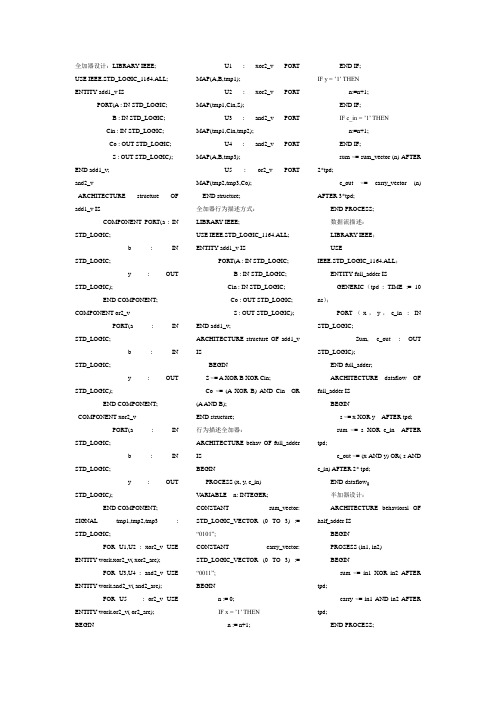

08 上EDA 复习纲要考试题分两个大题,编程题和设计题,如下面例子所示,叙述的部分需要写到试卷上,还有需要画出框图,所以需要带上铅笔和直尺!编程题一、用CASE/WHEN_ELSE/WITH_SELECT 语句设计一个一位四选一数据选择器,实体名为MUX4,要求画出设计的框图(手工),并简单叙述各端口的作用(手工);写出VDHL程序并生成符号文件(计算机)。

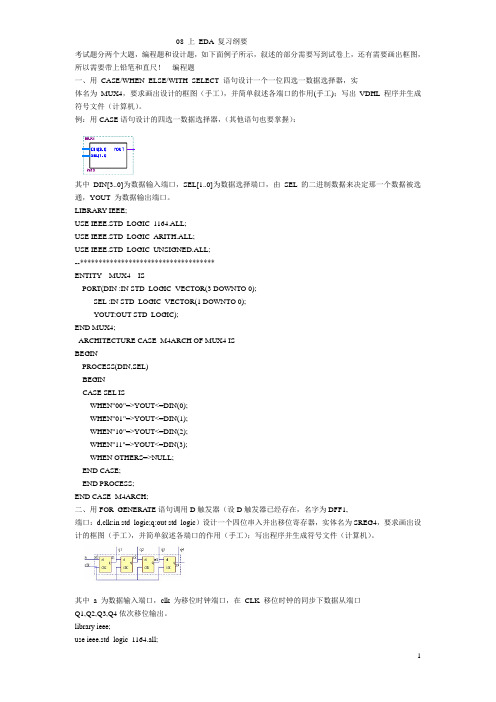

例:用CASE语句设计的四选一数据选择器,(其他语句也要掌握):其中DIN[3..0]为数据输入端口,SEL[1..0]为数据选择端口,由SEL 的二进制数据来决定那一个数据被选通,YOUT 为数据输出端口。

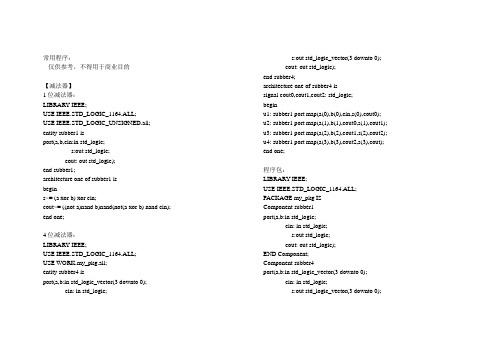

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;--************************************ENTITY MUX4 ISPORT(DIN :IN STD_LOGIC_VECTOR(3 DOWNTO 0);SEL :IN STD_LOGIC_VECTOR(1 DOWNTO 0);YOUT:OUT STD_LOGIC);END MUX4;ARCHITECTURE CASE_M4ARCH OF MUX4 ISBEGINPROCESS(DIN,SEL)BEGINCASE SEL ISWHEN"00"=>YOUT<=DIN(0);WHEN"01"=>YOUT<=DIN(1);WHEN"10"=>YOUT<=DIN(2);WHEN"11"=>YOUT<=DIN(3);WHEN OTHERS=>NULL;END CASE;END PROCESS;END CASE_M4ARCH;二、用FOR_GENERATE语句调用D触发器(设D触发器已经存在,名字为DFF1,端口:d,clk:in std_logic;q:out std_logic)设计一个四位串入并出移位寄存器,实体名为SREG4,要求画出设计的框图(手工),并简单叙述各端口的作用(手工);写出程序并生成符号文件(计算机)。

常用程序:仅供参考,不得用于商业目的【减法器】1位减法器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.all;entity subber1 isport(a,b,cin:in std_logic;s:out std_logic;cout: out std_logic);end subber1;architecture one of subber1 isbegins<= (a xor b) xor cin;cout<= ((not a)nand b)nand(not(a xor b) nand cin); end one;4位减法器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE WORK.my_pkg.all;entity subber4 isport(a,b:in std_logic_vector(3 downto 0);cin: in std_logic;s:out std_logic_vector(3 downto 0);cout: out std_logic);end subber4;architecture one of subber4 issignal cout0,cout1,cout2: std_logic;beginu1: subber1 port map(a(0),b(0),cin,s(0),cout0); u2: subber1 port map(a(1),b(1),cout0,s(1),cout1); u3: subber1 port map(a(2),b(2),cout1,s(2),cout2); u4: subber1 port map(a(3),b(3),cout2,s(3),cout); end one;程序包:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; PACKAGE my_pkg ISComponent subber1port(a,b:in std_logic;cin: in std_logic;s:out std_logic;cout: out std_logic);END Component;Component subber4port(a,b:in std_logic_vector(3 downto 0);cin: in std_logic;s:out std_logic_vector(3 downto 0);cout: out std_logic);END Component;end my_pkg;16位减法器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE WORK.my_pkg.all;entity subber16 isport( a,b:in std_logic_vector(15 downto 0);cin: in std_logic;s:out std_logic_vector(15 downto 0);cout: out std_logic);end subber16;architecture one of subber16 issignal cout0,cout1,cout2: std_logic;beginu1: subber4 port map(a(3 downto 0),b(3 downto 0),cin,s(3 downto 0),cout0);u2: subber4 port map(a(7 downto 4),b(7 downto 4),cout0,s(7 downto 4),cout1);u3: subber4 port map(a(11 downto 8),b(11 downto 8),cout1,s(11 downto 8),cout2);u4: subber4 port map(a(15 downto 12),b(15 downto 12),cout2,s(15 downto 12),cout); end one;【D触发器】LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY dchufaqi ISPORT(clk,d,clr:IN STD_LOGIC;q:OUT STD_LOGIC);END dchufaqi;ARCHITECTURE example2 OF dchufaqi IS BEGINprocess( clk,d,clr)beginif (clr='0') then q<='0';elsif (clk'event and clk='1') thenq<=d;end if;end process;END example2;【4位移位寄存器】LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY shifter ISPORT(din,clk: IN bit;dout : out bit); END shifter;ARCHITECTURE a OF shifter IScomponent dffport(d,clk: in bit;q: out bit);end component dff;signal d: bit_vector(0 to 4);BEGINd(0)<=din;u1:dff port map(d(0),clk,d(1));u2:dff port map(d(1),clk,d(2));u3:dff port map(d=>d(2),clk=>clk,q=>d(3));u4:dff port map(d=>d(3),clk=>clk,q=>d(4));dout<=d(4);END a;【8D锁存器】(1)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY latch1 IS --1位锁存器的设计PORT ( d :IN STD_LOGIC;ena :IN STD_LOGIC;q :OUT STD_LOGIC);END latch1;ARCHITECTURE example4 OF latch1 ISSIGNAL sig_save:STD_LOGIC:=…0‟;BEGINPROCESS (d,ena)BEGINIF ena='1' THENSig_save<=D;END IF;Q<=sig_save;END PROCESS;END example4;(2)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;PACKAGE my_pkg ISCOMPONENT latch1 --latch1入程序包PORT ( d :IN STD_LOGIC;ena :IN STD_LOGIC;q :OUT STD_LOGIC);END COMPONENT;END my_pkg;(3)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE WORK.my_pkg.ALL;ENTITY ct74373 IS --8D锁存器的设计PORT (d: IN STD_LOGIC_VECTOR(7 DOWNTO 0);oen, g: IN STD_LOGIC;q: OUT STD_LOGIC _VECTOR(7 DOWNTO 0));END ct74373;ARCHITECTURE one OF ct74373 ISSIGNAL sigsave: STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINGelatch: for n in 0 to 7 GENERATELatchx: latch1 port map(d(n),g,sigsave(n));END GENERA TE;Q<=sig save when oen=…0‟ else“ZZZZZZZZ”;END one;【根据逻辑表达式编程等等,如F= ABC+(D+E)+GH】LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;entity cytest isport(a,b,c,d,e,g,h: in std_logic;f: out std_logic);end cytest;architecture one of cytest issignal t1, t2,t3: std_logic;begint1<= a and b and c;t2<= d or e;t3<= g and h;f<= t1 or t2 or t3;end one;【六进制计数器】LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE. STD_LOGIC_UNSIGNED.ALL;ENTITY CNT6 ISPORT (CLK, CLRN, ENA, LDN: IN STD_LOGIC;D: IN STD_LOGIC_VECTOR(3 DOWNTO 0);Q: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT: OUT STD_LOGIC);END CNT6;ARCHITECTURE ONE OF CNT6 ISSIGNAL CI: STD_LOGIC_VECTOR(3 DOWNTO 0):="0000"; BEGINPROCESS(CLK, CLRN, ENA, LDN,CI)BEGINIF CLRN='0' THEN CI<="0000";ELSIF CLK'EVENT AND CLK='1' THENIF LDN='0' THEN CI<=D;ELSIF ENA='1' THENIF CI<5 THEN CI<=CI+1;ELSE CI<="0000";END IF;END IF;END IF;Q<=CI;END PROCESS;COUT<= CI(0) AND CI(2);END ONE;【有单个四选一,设计双四选一数据选择器】(1)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4_1 ISPORT(a,b,c,d:IN STD_LOGIC;s:IN STD_LOGIC_vector(1 downto 0);z:OUT STD_LOGIC);END mux4_1;ARCHITECTURE example3 OF mux4_1 ISBEGINPROCESS(a,b,c,d,s)BEGINCASE s ISWHEN "00" => z <= a;WHEN "01" => z <= b;WHEN "10" => z <= c;WHEN "11" => z <= d;WHEN OTHERS => z <= 'X';END CASE;END PROCESS;END example3;(2)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;PACKAGE mypkg ISCOMPONENT mux4_1PORT(a,b,c,d:IN STD_LOGIC;s:IN STD_LOGIC_vector(1 downto 0);z:OUT STD_LOGIC);END COMPONENT;END mypkg;(3)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE WORK.mypkg.ALL;ENTITY doublemux41 ISPORT(aa,bb,cc,dd:IN STD_LOGIC_VECTOR(1 DOWNTO 0);sel:IN STD_LOGIC_VECTOR(1 DOWNTO 0);q:OUT STD_LOGIC_VECTOR(1 DOWNTO 0));END doublemux41;ARCHITECTURE one OF doublemux41 ISBEGINgemux41: for n in 0 to 1 generateux: mux4_1 port map(aa(n),bb(n),cc(n),dd(n),sel,q(n));end generate;end one;updowncnt8library ieee;use ieee.std_logic_1164.all;entity updowncnt8 isport(clr,clk,ena,load,updown:in std_logic;d: in integer range 0 to 255;cout:out std_logic;q:buffer integer range 0 to 255); end updowncnt8;architecture one of updowncnt8 isbeginprocess (clk,ena,clr,d,load,updown)beginif clr='0' thenq<= 0;elsif clk'event and clk='1' then if load ='1' thenq<=d;elsif ena='1' thenif updown='0'then q<=q-1;if q = 0 then cout <='0'; end if;else q<= q+1;if q =255 then cout <='1';else cout <='0'; end if ;end if;end if;end if;end process;end one;。

EDA实验二时序逻辑电路设计一、实验目的1、熟悉EDA软件QuartusII的基本设计流程,包括设计输入、编译、综合、仿真;2、熟悉用EDA软件及FPGA器件实现数字电路设计的方法,包括引脚锁定,结构综合;3、熟悉用EDA实验箱对所设计的数字电路进行硬件验证的方法,包括验证方案。

二、实验平台1、硬件2、软件三、实验内容及结果记录1、HDL程序——十进制计数器1)程序代码module key_cnt(key,cnt); //定义模块名input key; //1端输入output reg [3:0] cnt; //4端输出always@(posedge key)beginif(cnt<4'd9) //如果输出值没有大于9cnt<= cnt + 1'b1; //输出值加1elsecnt<= 4'd0; //否则输出端归0endendmodule2)实验结果记录表2.1输入输出A0 Q3 Q2 Q1 Q02、HDL程序——0-9的计数器1)程序代码module number(in,reset,data_out, dig); //模块定义input in,reset; //输入输出定义output [7:0] data_out;output [7:0] dig = 8'b11111110;reg [7:0] data_out;reg [3:0]count ;always @ (posedge in or negedge reset)beginif (!reset) //异步清零begindata_out <= 8'b1111111;count <= 0;endelsebegin count <=count + 1; //计数case (count) //七段译码器4'b0000: data_out = 8'b11000000; // 显示0 4'b0001: data_out = 8'b11111001; // 显示1 4'b0010: data_out = 8'b10100100; // 显示2 4'b0011: data_out = 8'b10110000; // 显示3 4'b0100: data_out = 8'b10011001; // 显示4 4'b0101: data_out = 8'b10010010; // 显示5 4'b0110: data_out = 8'b10000011; // 显示6 4'b0111: data_out = 8'b11111000; // 显示7 4'b1000: data_out = 8'b10000000; // 显示8 4'b1001: data_out = 8'b10011000; // 显示9 default:data_out <= 8'b11000000;endcaseendendendmodule2)实验结果记录表2.2输入输出A1 A0 数码管显示。

全加器设计:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY add1_v ISPORT(A : IN STD_LOGIC;B : IN STD_LOGIC;Cin : IN STD_LOGIC;Co : OUT STD_LOGIC;S : OUT STD_LOGIC); END add1_v;and2_vARCHITECTURE structure OF add1_v ISCOMPONENT PORT(a : IN STD_LOGIC;b : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT; COMPONENT or2_vPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT; COMPONENT xor2_vPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;y : OUT STD_LOGIC);END COMPONENT; SIGNAL tmp1,tmp2,tmp3 : STD_LOGIC;FOR U1,U2 : xor2_v USE ENTITY work.xor2_v( xor2_arc);FOR U3,U4 : and2_v USE ENTITY work.and2_v( and2_arc);FOR U5 : or2_v USE ENTITY work.or2_v( or2_arc);BEGINU1 : xor2_v PORTMAP(A,B,tmp1);U2 : xor2_v PORTMAP(tmp1,Cin,S);U3 : and2_v PORTMAP(tmp1,Cin,tmp2);U4 : and2_v PORTMAP(A,B,tmp3);U5 : or2_v PORTMAP(tmp2,tmp3,Co);END structure;全加器行为描述方式:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY add1_v ISPORT(A : IN STD_LOGIC;B : IN STD_LOGIC;Cin : IN STD_LOGIC;Co : OUT STD_LOGIC;S : OUT STD_LOGIC);END add1_v;ARCHITECTURE structure OF add1_vISBEGINS <= A XOR B XOR Cin;Co <= (A XOR B) AND Cin OR(A AND B);END structure;行为描述全加器:ARCHITECTURE behav OF full_adderISBEGINPROCESS (x, y, c_in)V ARIABLE n: INTEGER;CONSTANT sum_vector:STD_LOGIC_VECTOR (0 TO 3) :=“0101”;CONSTANT carry_vector:STD_LOGIC_VECTOR (0 TO 3) :=“0011”;BEGINn := 0;IF x = ‟1‟ THENn := n+1;END IF;IF y = ‟1‟ THENn:=n+1;END IF;IF c_in = ‟1‟ THENn:=n+1;END IF;sum <= sum_vector (n) AFTER2*tpd;c_out <= carry_vector (n)AFTER 3*tpd;END PROCESS;数据流描述:LIBRARY IEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITY full_adder ISGENERIC(tpd : TIME := 10ns);PORT(x,y,c_in : INSTD_LOGIC;Sum, c_out : OUTSTD_LOGIC);END full_adder;ARCHITECTURE dataflow OFfull_adder ISBEGINs <= x XOR y AFTER tpd;sum <= s XOR c_in AFTERtpd;c_out <= (x AND y) OR( s ANDc_in) AFTER 2* tpd;END dataflow;半加器设计:ARCHITECTURE behavioral OFhalf_adder ISBEGINPROSESS (in1, in2)BEGINsum <= in1 XOR in2 AFTERtpd;carry <= in1 AND in2 AFTERtpd;END PROCESS;END behavioral;警告系统:LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY alarm ISPORT(smoke,door,water:INstd_logic;en,alarm_en :IN std_logic;fire_alarm,burg_alarm,water_alarm:OU T std_logic);END alarm;ARCHITECTURE alarm_arc OF alarm ISBEGINPROCESS(smoke,door,water,en,alarm_e n)BEGINIF ((smoke= …1‟) AND (en= …0‟)) THENfire_alarm <= …1‟;ELSEfire_alarm <= …0‟;END IF;IF ((door= …1‟) AND ((en= …0‟) AND (alarm_en= …0‟))) THENburg_alarm <= …1‟;ELSEburg_alarm <= …0‟;END IF;IF ((water= …1‟) AND (en= …0‟)) THENwater_alarm <= …1‟;ELSEwater_alarm <= …0‟;END IF;END PROCESS;END alarm_arc四选一数据选择器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4 ISPORT(d0 :INSTD_LOGIC_VECTOR (7 DOWNTO1);d1 :INSTD_LOGIC_VECTOR (7 DOWNTO1);d2 :INSTD_LOGIC_VECTOR (7 DOWNTO1);d3 :INSTD_LOGIC_VECTOR (7 DOWNTO1);s0 :INSTD_LOGIC;s1 :INSTD_LOGIC;y :OUTSTD_LOGIC_VECTOR (7 DOWNTO1) );END mux4 ;:ARCHITECTURE behave OFmux4 ISBEGINlable:PROCESS(d0,d1,d2,d3,s0,s1)V ARIABLE tmp:INTEGER;BEGINtmp := 0;IF(s0=…1‟)THENtmp := tmp+1;END IF;IF(s1=…1‟)THENtmp := tmp+2;END IF;CASE tmp ISWHEN 0 => y <=d0;WHEN 1 => y <=d1;WHEN 2 => y <=d2;WHEN 3 => y <=d3;WHEN OTHERS=> NULL;END CASE;END PROCESS;END behave;3数最大值比较器:;LIBRARY IEEE;USE IEEE. STD_LOGIC_1164.ALL;USE IEEE. STD_LOGIC_UNSIGNED.ALL;ENTITY max ISPORT(in1:IN STD_LOGIC_VECTOR (7 DOWNTO 0);in2:IN STD_LOGIC_VECTOR (7 DOWNTO 0);in3:INSTD_LOGIC_VECTOR (7 DOWNTO0);q:OUTSTD_LOGIC_VECTOR (7 DOWNTO0) );END max ;ARCHITECTURE rtl OF max ISPROCEDURE maximum(a,b:IN STD_LOGIC_VECTOR;c:OUT STD_LOGIC_VECTOR)ISV ARIABLE temp:STD_LOGIC_VECTOR(a‟RANGE);BEGINIF(a > b)THENtemp := a;ELSEtemp := b;END IF;c := temp;END maximum;BEGINPROCESS(in1,in2,tmp1)V ARIABLE tmp1,tmp2:STD_LOGIC_VECTOR (7 DOWNTO 0) ;BEGINmaximum(in1,in2,tmp1);maximum(tmp1,in3,tmp2);q <= tmp2;END PROCESS;END rtl;四位移位寄存器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY shift_reg ISPORT(di:IN STD_LOGIC;cp:IN STD_LOGIC;do:OUTSTD_LOGIC);END shift_reg;ARCHITECTURE structure OFshift_reg ISCOMPONENT dffPORT(d:INSTD_LOGIC;clk:INSTD_LOGIC;q:OUTSTD_LOGIC);END COMPONENT;SIGNAL q:STD_LOGIC_VECTOR(4 DOWNTO0);BEGINdff1:dff PORT MAP (d1,cp,q(1));dff2:dff PORT MAP (q(1),cp,q(2));dff3:dff PORT MAP (q(2),cp,q(3));dff4:dff PORT MAP (q(3),cp,do);END structure;用VHDL 语言设计同步60 进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;library altera;use altera.maxplus2.all;library lpm;use lpm.lpm_components.all;entity count60 isport(clk,clr,en:in std_logic;cy:out std_logic;qh,ql:out std_logic_vector(3 downto 0));end count60;architecture behavior of count60 is signal qh_tmp,ql_tmp:std_logic_vector(3 downto 0);beginqh<=qh_tmp;ql<=ql_tmp;cy<='1'when(ql_tmp="1001"andqh_tmp="0101")else '0';--²¢ÐÐÓï¾äÃèÊö½øλprocess(clr,clk,en)beginif clr='0'thenqh_tmp<=(others=>'0');--µÈ¼ÛÓëqh_tmp<="0000";ql_tmp<=(others=>'0');elsif (clk'event and clk='1')thenif en='1'thenif (ql_tmp=9)thenql_tmp<="0000";if(qh_tmp=5)thenqh_tmp<="0000";elseqh_tmp<=qh_tmp+1;end if;elseql_tmp<=ql_tmp+1;end if;end if;--END IF (EN)end if;--END IF(clr)end process;end behavior;状态机:LIBRARY IEEE;USEIEEE.std_logic_1164.ALL;USEIEEE.std_logic_unsigned.ALL; --operator '-' IS overwrited IN the packageentity timer ISport ( data_in: INstd_logic_vector( 7 DOWNTO 0 );reset, CLK, start:IN std_logic;ring : OUTstd_logic);END timer;architecture behav OF timerISBEGINPROCESS( reset, clk )V ARIABLEcounter: std_logic_vector( 7DOWNTO 0 );V ARIABLE state: integer RANGE 0 TO 3;BEGINIF reset = '0' THENring <= '0';state := 0;ELSIF clk'event AND clk = '1' THENCASE state ISWHEN 0 =>ring <= '0';counter := "00000000";IF start = '1' THENstate := 1;ELSEstate := 0;END IF;WHEN 1 =>counter := data_in; IF start = '1' THEN state := 1; ELSEstate := 2; END IF;WHEN 2 =>IF counter < 3 THENcounter := "00001000"state := 3;ELSEcounter := counter - 1;state := 2;END IF;WHEN 3 =>ring <= '1';IF counter = 1 THENstate := 0;ELSECountter := counter - 1;state := 3;END IF;END CASE;END IF;END PROCESS;END behav;四--七library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--************************************entity yima47 isport(in47:in std_logic_vector(3 downto 0);seg:out std_logic_vector(6 downto 0));end yima47;--************************************************ architecture a of yima47 isbeginseg<="1000000"when in47=0 else"1111001"when in47=1 else"0100100"when in47=2 else"0110000"when in47=3 else"0011001"when in47=4 else"0010010"when in47=5 else"0000010"when in47=6 else"1111000"when in47=7 else"0000000"when in47=8 else"0010000";--=>seg<="0010000";end a;。

配置:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux21b ISPORT( a,b:IN STD_LOGIC;s:IN STD_LOGIC;y:OUT STD_LOGIC);END mux21b;ARCHITECTURE mux_arch1 OF mux21b ISBEGINy <= a WHEN s = '0' ELSE b ;END mux_arch1 ;ARCHITECTURE mux_arch2 OF mux21b ISBEGINProcess(a,b,s)BEGINIF (s='1') THEN y <= a;ELSE y <= b ;END IF;END Process;END mux_arch2;CONFIGURA TION first OF mux21b ISFOR mux_arch1END FOR;END first;CONFIGURA TION second OF mux21b ISFOR mux_arch2END FOR;END second;(3)W AIT UNTIL 条件--条件等待语句这种形式的W AIT语句使进程暂停,直到预期的条件为真。

W AIT UNTIL后面跟的是布尔表达式,在布尔表达式中隐式地建立一个敏感信号量表,当表中任何一个信号量发生变化时,就立即对表达式进行一次测评。

如果其结果使表达式返回一个“真”值,则进程脱离挂起状态,继续执行下面的语句。

即W AIT UNTIL语句需满足以下条件:✓在条件表达式中所含的信号发生了变化;✓此信号改变后,且满足W AIT UNTIL语句中表达式的条件。

这两个条件缺一不可,且必须按照上述顺序来完成。

W AIT UNTIL语句有以下三种表达方式:✓W AIT UNTIL 信号= V ALUE;✓W AIT UNTIL RISING_EDGE(信号)= V ALUE;✓W AIT UNTIL 信号’EVENT AND 信号= V ALUE;或W AIT UNTIL 信号’ST ABLE AND 信号= V ALUE;LIBRARY IEEE;USE IEEE. STD_LOGIC_1164.ALL;USE IEEE. STD_LOGIC_UNSIGNED.ALL;ENTITY CNT101 ISPORT(CLK,CLR:IN STD_LOGIC;CNT:BUFFER STD_LOGIC_VECTOR (3 DOWNTO 0));END CNT101;ARCHITECTURE ART OF CNT101 ISBEGINPROCESSBEGINW AIT UNTIL clk ='1'AND clk'EVENT; ;;;;;;;IF(clr='0'OR CNT="1001") THENCNT<="0000";ELSECNT<= CNT+1;END IF;END PROCESS;END ART;设计一个从两个整数中求取最大值的过程。

1、流水灯(简易)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity roll isport ( clk :in std_logic;dout:out std_logic_vector(0 to 7));end roll;architecture behave of roll issignal count:std_logic_vector(0 to 7):="00000001";begindout<=count;process(clk)variable x:integer range 0 to 19999999;beginif rising_edge(clk) thenif x<19999999 then x:=x+1;else x:=0;count<=count(1 to 7)&count(0);end if;end if;end process;end behave;2、流水灯(模板)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led_water isport(clk:in std_logic;qout:out std_logic_vector(7 downto 0));end;architecture a of led_water issignal num:integer range 0 to 7 :=0;signal q0 :std_logic:='0';beginprocess(clk)variable count :integer range 0 to 10000000;beginif rising_edge(clk) thenif count<10000000 then count:=count+1;else q0<= NOT q0;count:=0;end if;end if;end process;process(q0)beginif rising_edge(q0) thenif num<7 then num<=num+1;else num<=0;end if;case num iswhen 0=> qout<="00000001";when 1=> qout<="00000010";when 2=> qout<="00000100";when 3=> qout<="00001000";when 4=> qout<="00010000";when 5=> qout<="00100000";when 6=> qout<="01000000";when 7=> qout<="10000000";end case;end if;end process;end;3、1到8同时显示library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity easy isport ( clk :in std_logic;cou:out std_logic_vector(2 downto 0);seg:out std_logic_vector(7 downto 0));end easy;architecture behave of easy issignal clkms :std_logic:='0';signal count:std_logic_vector(2 downto 0):="000";beginwith count selectseg <= "00000110" when "000", --可以修改代码实现不同数字显示"01011011" when "001","01001111" when "010","01100110" when "011","01101101" when "100","01111101" when "101","00000111" when "110","01111111" when "111","00100000" when others;process(clk)variable x:integer range 0 to 9999;beginif rising_edge (clk) thenif x<9999 then x:=x+1;else x:=0;clkms<= NOT clkms;end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif count<7 then count<=count+1;else count<="000";end if;end if;end process;cou<=count;end behave;4、点阵(模板)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dian isport ( clk :in std_logic;Q :out std_logic_vector(0 to 15);din:out std_logic_vector(3 downto 0));end;architecture behave of dian issignal count:std_logic_vector(3 downto 0):="1111";signal clkms :std_logic:='0';beginwith count selectQ<= x"0000" when "1111", --改成相应代码x"0000" when "1110",x"0000" when "1101",x"0000" when "1100",x"0000" when "1011",x"0000" when "1010",x"0000" when "1001",x"0000" when "1000",x"0000" when "0111",x"0000" when "0110",x"0000" when "0101",x"0000" when "0100",x"0000" when "0011",x"0000" when "0010",x"0000" when "0001",x"0000" when "0000",x"0000" when others;process(clk)variable x :integer range 0 to 9999;beginif rising_edge(clk) thenif x<9999 then x:=x+1;else clkms<= NOT clkms;x:=0;end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif count>0 then count<=count-1;else count<="1111";end if;end if;din<=count;end process;end behave;5、秒表(1)去抖library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity qudou isport ( clk :in std_logic;key :in std_logic;q :out std_logic);end qudou;architecture behave of qudou isbeginprocess(clk)variable x:integer range 0 to 3;beginif rising_edge(clk) thenif key='0' then q<='0';x:=0;elseif x<3 then x:=x+1;q<='0';else q<='1';end if;end if;end if;end process;end behave;(2)主程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity seconds isport ( clk :in std_logic;key1,key2:in std_logic; --清零/开始count:buffer std_logic_vector(2 downto 0); --数码管位选seg:out std_logic_vector(7 downto 0); --段选beep:out std_logic); --蜂鸣器(可以设定一定时间响)end seconds;architecture behave of seconds iscomponent qudouport ( clk :in std_logic;key :in std_logic;q :out std_logic);end component;signal clks,clkms,clksms:std_logic;signal out1,out2,flag:std_logic:='0';signal shi,ge,data:integer range 0 to 9;beginM1:qudou port map(clksms,key1,out1);M2:qudou port map(clksms,key2,out2);with data selectseg<="00111111" when 0,"00000110" when 1,"01011011" when 2,"01001111" when 3,"01100110" when 4,"01101101" when 5,"01111101" when 6,"00000111" when 7,"01111111" when 8,"01101111" when 9,"00000000" when others;process(clk)variable x:integer range 0 to 9999999;variable y:integer range 0 to 9999;variable z:integer range 0 to 99990;beginif rising_edge(clk) thenif x<9999999 then x:=x+1;else x:=0;clks<= NOT clks;end if;if y<9999 then y:=y+1;else y:=0;clkms<= NOT clkms;end if;if z<99999 then z:=z+1;else z:=0;clksms<= NOT clksms;end if;end if;end process;process(clks,flag)variable n:integer range 0 to 99;beginif flag='0' then n:=0;elsif rising_edge(clks) thenif n<99 then n:=n+1;else n:=0;end if;end if;shi<=n/10;ge<=n rem 10;end process;process(out1,out2)beginif out1='1' then flag<='0'; --清零elsif out2='1' then flag<='1'; --开始end if;end process;process(clkms)beginif rising_edge(clkms) thenif count<1 then count<=count+1;else count<="000";end if;end if;end process;beep<= clkms when (shi=5 AND ge=9) else'0';data<=shi when count="001" elsege;end behave;6、电子琴(去抖模块同4)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dianziqin isport ( clk :in std_logic;key1,key2,key3,key4,key5,key6,key7,key8:in std_logic;q :out std_logic); --蜂鸣器end dianziqin;architecture behave of dianziqin issignal clksms,q0:std_logic:='0';signal con1,con2,con3,con4,con5,con6,con7,con8:std_logic:='0';signal mus:integer range 0 to 38221;COMPONENT qudouport ( clk :in std_logic;din :in std_logic;q :out std_logic);end COMPONENT;beginM1:qudou PORT MAP(clksms,key1,con1);M2:qudou PORT MAP(clksms,key2,con2);M3:qudou PORT MAP(clksms,key3,con3);M4:qudou PORT MAP(clksms,key4,con4);M5:qudou PORT MAP(clksms,key5,con5);M6:qudou PORT MAP(clksms,key6,con6);M7:qudou PORT MAP(clksms,key7,con7);M8:qudou PORT MAP(clksms,key8,con8);q<=q0 AND (con1 OR con2 OR con3 OR con4 OR con5 OR con6 OR con7 OR con8);process(clk)variable count :integer range 0 to 49999;beginif rising_edge(clk) thenif count<49999 then count:=count+1;else clksms<= NOT clksms;count:=0;end if;end if;end process;process(clk)variable count :integer range 0 to 38221;beginif rising_edge(clk) thenif count<38221 then count:=count+1;else count:= mus;q0<= NOT q0;end if;end if;end process;process(con1,con2,con3,con4,con5,con6,con7,con8)beginif con1='1' then mus<=0;elsif con2='1' then mus<=4170;elsif con3='1' then mus<=7885;elsif con4='1' then mus<=9587;elsif con5='1' then mus<=12712;elsif con6='1' then mus<=15495;elsif con7='1' then mus<=17974;elsif con8='1' then mus<=19102;else NULL;end if;end process;end behave;7、数字钟(去抖模块同4)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity shuzi isport ( clk :in std_logic;key1 :in std_logic; --调时key2 :in std_logic; --调分fuc :in std_logic; --暂停sss :in std_logic; --秒清零beep :out std_logic; --蜂鸣器segout :out std_logic_vector (7 downto 0); --数码管段选count :out std_logic_vector (2 downto 0));--位选end shuzi;architecture behave of shuzi iscomponent qudouport ( clk :in std_logic;din :in std_logic;q :out std_logic);end component;signal clks,clkms,clksms,tm,th,tf,ss,beep1,beep2,flag0:std_logic:='0';signal outs,outss,outm,outsm,outh,outsh:integer range 0 to 11;signal count0:std_logic_vector (2 downto 0):="000";signal segout0:integer range 0 to 10;beginM1:qudou PORT MAP(clksms,fuc,tf);M2:qudou PORT MAP(clksms,key1,th);M3:qudou PORT MAP(clksms,key2,tm);M4:qudou PORT MAP(clksms,sss,ss);count<=count0;beep<=beep1 when outsm=5 AND outm=9 AND outss=5 AND (outs=0 OR outs=2 OR outs=4OR outs=6 OR outs=8) elsebeep2 when outsm=0 AND outm=0 AND outss=0 AND outs=0 else'0';with count0 selectsegout0<=outs when "000",outss when "001",10 when "010",outm when "011",outsm when "100",10 when "101",outh when "110",outsh when "111";with segout0 selectsegout <= "00111111" when 0,"00000110" when 1,"01011011" when 2,"01001111" when 3,"01100110" when 4,"01101101" when 5,"01111101" when 6,"00000111" when 7,"01111111" when 8,"01101111" when 9,"01000000" when 10,"00000000" when others;process(clk)variable cts:integer range 0 to 9999999;variable ctms:integer range 0 to 4999;variable ctsms:integer range 0 to 99999;variable ctb1:integer range 0 to 19999;variable ctb2:integer range 0 to 9999;beginif rising_edge(clk) thenif ctms<4999 then ctms:=ctms+1; else ctms:=0;clkms<= NOT clkms; end if;if ctb2<9999 then ctb2:=ctb2+1; else ctb2:=0;beep2<= NOT beep2; end if;if ctb1<19999 then ctb1:=ctb1+1; else ctb1:=0;beep1<= NOT beep1; end if;if ctsms<99999 then ctsms:=ctsms+1; else ctsms:=0;clksms<= NOT clksms; end if;if cts<9999999 then cts:=cts+1; else cts:=0;clks<= NOT clks; end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif count0<7 then count0<=count0+1;else count0<="000";end if;end if;end process;process(tf)beginif rising_edge(tf) then flag0<= NOT flag0;end if;end process;process(clks,th,tm,ss)variable min,sec:integer range 0 to 59;variable hour:integer range 0 to 23;beginif ss='1' then sec:=0;elsif rising_edge(clks) thencase flag0 iswhen '0'=> if sec<59 then sec:=sec+1;else sec:=0;if min<59 then min:=min+1;else min:=0;if hour<23 then hour:=hour+1;else hour:=0;end if;end if;end if;when '1'=> if th='1' thenif hour<23 then hour:=hour+1;else hour:=0;end if;end if;if tm='1' thenif min<59 then min:=min+1;else hour:=0;end if;end if;end case;end if;outsh<=hour/10;outh<=hour rem 10;outsm<=min/10;outm<=min rem 10;outss<=sec/10;outs<=sec rem 10;end process;end behave;8、点阵(上)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dianzhen isport ( clk :in std_logic;q :out std_logic_vector (3 downto 0);q1 :out std_logic_vector (0 to 15));end dianzhen;architecture behave of dianzhen istype str is array (0 to 79) of std_logic_vector(0 to 15);signal clkms :std_logic;signal q0:std_logic_vector(3 downto 0):="1111";signal n:integer range 0 to 79;signal num:integer range 0 to 15;signal ziku:str:=(x"0100",x"0100",x"0100",x"3FF8",x"2108",x"2108",x"2108",x"3FF8",x"2108",x"2108",x"2108",x"3FF8",x"210A",x"0102",x"0102",x"00FE",x"0000",x"7FF8",x"0010",x"0020",x"0040",x"0180",x"0100",x"FFFE",x"0100",x"0100",x"0100",x"0100",x"0100",x"0100",x"0500",x"0200",x"1000",x"087C",x"FF44",x"0048",x"7E48",x"4250",x"7E48",x"0048",x"7E44",x"0444",x"0844",x"0F68",x"F850",x"0840",x"2840",x"1040",x"0000",x"1FF0",x"1010",x"1010",x"1210",x"1110",x"1110",x"1010", x"FFFE",x"1010",x"1010",x"1010",x"2010",x"2010",x"4050",x"8020",x"0000",x"7C00",x"45FC",x"4904",x"4904",x"5104",x"4904",x"4904", x"45FC",x"4504",x"4504",x"6904",x"5104",x"4104",x"41FC",x"4104" );beginprocess(clk)variable count:integer range 0 to 2499;beginif rising_edge (clk) thenif count<2499 then count:=count+1;else count:=0;clkms<= NOT clkms;end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif q0>0 then q0<=q0-1;else q0<="1111";end if;if num<15 then num<=num+1;else num<=0;end if;end if;end process;process(q0(3))variable x:integer range 0 to 40;beginif rising_edge(q0(3)) thenif x<40 then x:=x+1;else x:=0;if n<79 then n<=n+1;else n<=0;end if;end if;end if;end process;q1<=ziku(n+num) when n+num<80 elseziku(n+num-80);q<=q0;end behave;9、点阵(左)library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dianzhen isport ( clk :in std_logic;q :out std_logic_vector (3 downto 0);q1 :out std_logic_vector (0 to 15));end dianzhen;architecture behave of dianzhen istype stru is array (0 to 79) of std_logic_vector( 0 to 15);signal clkms :std_logic;signal flag,num:integer range 0 to 15;signal n:integer range 0 to 4;signal q0:std_logic_vector(3 downto 0):="1111";signal data1:std_logic_vector(0 to 31);signal ziku:stru:=(x"0100",x"0100",x"0100",x"3FF8",x"2108",x"2108",x"2108",x"3FF8", x"2108",x"2108",x"2108",x"3FF8",x"210A",x"0102",x"0102",x"00FE",x"0000",x"7FF8",x"0010",x"0020",x"0040",x"0180",x"0100",x"FFFE", x"0100",x"0100",x"0100",x"0100",x"0100",x"0100",x"0500",x"0200",x"1000",x"087C",x"FF44",x"0048",x"7E48",x"4250",x"7E48",x"0048", x"7E44",x"0444",x"0844",x"0F68",x"F850",x"0840",x"2840",x"1040", x"0000",x"1FF0",x"1010",x"1010",x"1210",x"1110",x"1110",x"1010", x"FFFE",x"1010",x"1010",x"1010",x"2010",x"2010",x"4050",x"8020",x"0000",x"7C00",x"45FC",x"4904",x"4904",x"5104",x"4904",x"4904", x"45FC",x"4504",x"4504",x"6904",x"5104",x"4104",x"41FC",x"4104");begindata1<=ziku(n*16+num)&ziku(n*16+16+num) when n<4 elseziku(n*16+num)&ziku(num);process(clk)variable count:integer range 0 to 2499;beginif rising_edge (clk) thenif count<2499 then count:=count+1;else count:=0;clkms<= NOT clkms;end if;end if;end process;process(clkms)beginif rising_edge(clkms) thenif q0>0 then q0<=q0-1;else q0<="1111";end if;if num<15 then num<=num+1;else num<=0;end if;end if;end process;with flag selectq1<=data1(15 to 30) when 15,data1(14 to 29) when 14,data1(13 to 28) when 13,data1(12 to 27) when 12,data1(11 to 26) when 11,data1(10 to 25) when 10,data1(9 to 24) when 9,data1(8 to 23) when 8,data1(7 to 22) when 7,data1(6 to 21) when 6,data1(5 to 20) when 5,data1(4 to 19) when 4,data1(3 to 18) when 3,data1(2 to 17) when 2,data1(1 to 16) when 1,data1(0 to 15) when 0,(others=>'0') when others; process(q0(3))variable x :integer range 0 to 40;beginif rising_edge(q0(3)) thenif x<40 then x:=x+1;else x:=0;if flag<15 then flag<=flag+1;elseif n<4 then n<=n+1;else n<=0;end if;flag<=0;end if;end if;end if;end process;q<=q0;end behave;10、频率计library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity plj isport ( start:in std_logic; --复位信号clk :in std_logic; --系统时钟clk1:in std_logic; --被测时钟yy1:out std_logic_vector(7 downto 1); --八段码w1 :out std_logic_vector(2 downto 0)); --位选信号end plj;architecture behav of PLj issignal b1,b2,b3,b4,b5,b6,b7,b8:std_logic_vector(3 downto 0); --十进制计数器signal v1,v2,v3,v4,v5,v6,v7,v8:std_logic_vector(3 downto 0);signal bcd:std_logic_vector(3 downto 0); --BCD码寄存器signal q :integer range 0 to 39999999; --秒分频系数signal qq : integer range 0 to 79999; --动态扫描分频系数signal en,bclk,e1:std_logic; --使能信号,有效被测信号signal sss : std_logic_vector(3 downto 0); --小数点signal bcd0,bcd1,bcd2,bcd3 : std_logic_vector(3 downto 0); --寄存7位十位计数器中有效的高4位数据beginsecond:process(clk) --此进程产生一个持续时间为一秒的的闸门信号beginif start='1' then q<=0;elsif clk'event and clk='1' thenif q<39999999 then q<=q+1;else q<=0;end if;end if;if q<19999999 and start='0' then en<='1';else en<='0';end if;if q=0 then e1<='0';else e1<='1';end if;end process;com:process(en,start,clk1) --此进程完成对被测信号计脉冲数beginif (start='1' or e1='0') and en='1' thenb1<="0000";b2<="0000";b3<="0000";b4<="0000";b5<="0000";b6<="0000";b7<="0000";b8<="0000";elsif clk1'event and clk1='1' and en='1' thenif b1="1001" then b1<="0000"; --完成个位十进制计数if b2="1001" then b2<="0000"; --完成百位十进制计数if b3="1001" then b3<="0000"; --完成千位十进制计数if b4="1001" then b4<="0000"; --完成万位十进制计数if b5="1001" THEN b5<="0000"; --完成十万位十进制计数if b6="1001" then b6<="0000"; --完成百万位十进制计数if b7="1001" then b7<="0000"; --完成千万位十进制计数if b8="1001" then b8<="0000"; --完成千万位十进制计数else b8<=b8+1;end if;else b7<=b7+1;end if;else b6<=b6+1;end if;else b5<=b5+1;end if;else b4<=b4+1;end if;else b3<=b3+1;end if;else b2<=b2+1;end if;else b1<=b1+1;end if;end if;if en='0' then v1<=b1;v2<=b2;v3<=b3;v1<=b4;v5<=b5;v6<=b6;v7<=b7;v8<=b8;else v1<=v1;v2<=v2;v3<=v3;v4<=v4;v5<=v5;v6<=v6;v7<=v7;v8<=v8;end if;end process;weixuan:process(clk) --此进程完成数据的动态显示beginif clk'event and clk='1' thenif qq< 9999 then qq<=qq+1;bcd<=v1; w1<="000";elsif qq<19999 then qq<=qq+1;bcd<=v2; w1<="001";elsif qq<29999 then qq<=qq+1;bcd<=v3; w1<="010";elsif qq<39999 then qq<=qq+1;bcd<=v4; w1<="011";elsif qq<49999 then qq<=qq+1;bcd<=v5; w1<="100";elsif qq<59999 then qq<=qq+1;bcd<=v6; w1<="101";elsif qq<69999 then qq<=qq+1;bcd<=v7; w1<="110";elsif qq<79999 then qq<=qq+1;bcd<=v8; w1<="111";else qq<=0;end if;end if;end process;m0: process (bcd) --译码begincase bcd iswhen "0000"=>yy1(7 downto 1)<="1111110";when "0001"=>yy1(7 downto 1)<="0110000";when "0010"=>yy1(7 downto 1)<="1101101";when "0011"=>yy1(7 downto 1)<="1111001";when "0100"=>yy1(7 downto 1)<="0110011";when "0101"=>yy1(7 downto 1)<="1011011";when "0110"=>yy1(7 downto 1)<="1011111";when "0111"=>yy1(7 downto 1)<="1110000";when "1000"=>yy1(7 downto 1)<="1111111";when "1001"=>yy1(7 downto 1)<="1111011";when others=>yy1(7 downto 1)<="0000000";end case;end process;end behav;11、抢答器library ieee;use ieee.std_Logic_1164.all;use ieee.std_Logic_unsigned.all;use ieee.std_Logic_arith.all;entity xuan81 isport(rst,clk:in std_logic;--复位,时钟接口key:in std_logic_vector(8 downto 1);--选手抢答的按键segout :out std_logic_vector (0 to 6);count:out std_logic_vector(2 downto 0);d:out std_logic);--不同频率的叫声end;architecture a of xuan81 issignal count2 :integer range 0 to 3:=1;signal en :std_logic:='1';signal c3,c4 :std_logic:='1';signal c1,c2: std_logic;signal qh,ql:integer range 0 to 10;signal sz:integer range 0 to 10:=10;signal ld :std_LOGIC:='1';--一个控制数码管计数显示的信号量signal q0:integer range 0 to 10000000;signal q1:integer range 0 to 10000;signal q2:integer range 0 to 20000;signal clk0,clk1,clk2:std_logic;signal count1 : integer range 0 to 2 ;signal Q: integer range 0 to 10;signal CQI:std_logic_vector(2 downto 0):="000";beginprocess(clk)beginif clk'event and clk='1' thenif q0<10000000 then q0<=q0+1;else clk0<=not clk0; q0<=0;end if;if q1<10000 then q1<=q1+1;else clk1<=not clk1; q1<=0;end if;if q2<20000 then q2<=q2+1;else clk2<=not clk2; q2<=0;end if;end if;end process;process(c1,c2)beginif c1='1' and c3='1' then d<=clk1;en<='1';elsif c2='1' and c4='1' then d<=clk2;en<='1';else d<='0';en<='0';end if;end process;process(clk0,en)beginif clk0'event and clk0='1' thenif en='1' thenif count2<3 then count2<=count2+1;else c3<='0';c4<='0';count2<=0;end if;end if;end if;if c1='0' then c3<='1';end if;if c2='0' then c4<='1';end if;end process;process(clk0,rst,key)variable m:integer range 1 to 31:=30;beginif rst='1' then m:=31;sz<=10;ld<='1';c1<='0';c2<='1';elsif rst='0' thenif ld='0' then m:=31;elsif ld<='1' thenif clk0'event and clk0='1' thenif m=1 then c1<='1';ld<='0';else m:=m-1;c1 <='0';end if ;if (key(1)='1') then sz<=1; c2<='1';ld<='0';elsif (key(2)='1') then sz<=2; c2<='1';ld<='0';elsif (key(3)='1') then sz<=3; c2<='1';ld<='0';elsif (key(4)='1') then sz<=4; c2<='1';ld<='0';elsif (key(5)='1') then sz<=5; c2<='1';ld<='0';elsif (key(6)='1') then sz<=6; c2<='1';ld<='0';elsif (key(7)='1') then sz<=7; c2<='1';ld<='0';elsif (key(8)='1') then sz<=8; c2<='1';ld<='0';else c2<='0';end if;END IF;END IF;if m=31 then qh<=10;ql<=10;elseqh<=m/10;ql<=m rem 10;end if;END IF;end process;process(clk1)beginif clk1'event and clk1='1' thenif count1<2 then count1<=count1+1;else count1<=0;end if;if CQI<2 THEN CQI<=CQI+1;ELSE CQI<="000";end if;end if;case CQI iswhen "000"=> count<="001";when "001"=> count<="000";when "010"=> count<="011";when others=>null;end case;case count1 iswhen 0=>Q<=qh;when 1=>Q<=ql;when 2=>Q<=sz;end case;end process;process (Q)begincase Q iswhen 0 => segout<="1111110";when 1 => segout<="0110000";when 2 => segout<="1101101";when 3 => segout<="1111001";when 4 => segout<="0110011";when 5 => segout<="1011011";when 6 => segout<="1011111";when 7 => segout<="1110000";when 8 => segout<="1111111";when 9 => segout<="1111011";when others=>segout<="0000000";end case;end process;end;。

module JSQ(clk,q,clr);input clk;input clr;output[6:0]q;reg[6:0]q;always@(posedge clk)beginif(!clr)q<=6'd0;elsebeginif(q==6'd59)q<=6'd0;elseq<=q+1;endendendmoduleE D A1、数字钟程序:秒程序:module miao (clk,clr,pause,ml,mh,lcn);input clk,clr,pause;output [3:0] ml,mh;output lcn;reg [3:0] ml,mh;reg lcn;always @(posedge clk or posedge clr)begin{ml,mh}<=8'h00;lcn<=0;endelse if(!pause)beginif(ml==9)beginml<=0;if (mh==5)beginmh<=0;lcn<=1;endelse mh<=mh+1;endelsebeginml<=ml+1;lcn<=0;endendendendmodule分钟程序:module fen(lcn,clr,hcn,fl,fh);input lcn,clr;output [3:0] fl,fh;output hcn;reg [3:0] fl,fh;reg hcn;always @(posedge lcn or posedge clr)beginif(clr)begin{fl,fh}<=8'h00;hcn<=0;endelse if (fl==9)beginfl<=0;if(fh==5)beginfh<=0;hcn<=1;endelsefh<=fh+1;endfl<=fl+1;hcn<=0;endendendmodule小时程序:module shi(hcn,clr,sl,sh);input hcn,clr;output [3:0] sl,sh;reg [3:0] sl,sh;always @(posedge hcn or posedge clr)beginif(clr) {sh,sl}<=8'h00;else if (sl==3)beginif (sh==2)beginsl<=0;sh<=0;endelse sl<=sl+1;endelse if (sl==9)beginsl<=0;sh<=sh+1;endelse sl<=sl+1;endendmoduleSEL程序:module sel(clk,q);input clk;output [2:0] q;reg [2:0] q;always@(posedge clk)beginq<=q+1;endendmodule片选程序:module pianxuan (ml,mh,fl,fh,sl,sh,sel,qout);input [3:0] ml,mh,fl,fh,sl,sh;input [2:0] sel;output [3:0] qout;reg [3:0] qout;always @(ml or mh or fl or fh or sl or sh or sel)begincase(sel)3'b000: qout=ml;3'b001: qout=mh;3'b010: qout=fl;3'b011: qout=fh;3'b100: qout=sl;3'b101: qout=sh;default: qout=4'b0000;endcaseendendmodule显示译码程序:module ymq (in,out);input [3:0] in;output [6:0] out;reg [6:0] out;always @(in)begincase(in)4'b0000: out=7'b1111110;4'b0001: out=7'b0110000;4'b0010: out=7'b1101101;4'b0011: out=7'b1111001;4'b0100: out=7'b0110011;4'b0101: out=7'b1011011;4'b0110: out=7'b1011111;4'b0111: out=7'b1110000;4'b1000: out=7'b1111111;4'b1001: out=7'b1111011;default: out=7'bxxxxxxx;endcaseendendmodule各部分连接电路图:(2)、16进制计数器:module jz16(clk,q);input clk;output[3:0]q;reg[3:0]q;always@(posedge clk)beginif(q==4'd15)q<=4'd0;elseq<=q+1;endendmodule128进制计数器:module jsq128(clk,clr,st,pc,q);input clk,clr,pc,st;output[6:0]q;reg[6:0]q;always@(posedge clk or negedge clr)beginif(!clr)q<=0;elseif(st)beginif(!pc)beginif(q==127)q<=0;elseq<=q+1;endelseif(q==0)q<=127;elseq<=q-1;endendendmodule加法器:module jfq(a1,a2,y1);input [3:0]a1;input[6:0]a2;output[6:0]y1;reg[6:0]y1;always@(a1 or a2)beginy1=a1+a2;endendmodule3-8译码器:(case语句)module ym(in,out);input[2:0] in;output[7:0] out;reg [7:0] out;always@(in)begincase(in)3'd0: out=8'b11111110;3'd1: out=8'b11111101;3'd2: out=8'b11111011;3'd3: out=8'b11110111;3'd4: out=8'b11101111;3'd5: out=8'b11011111;3'd6: out=8'b10111111;3'd7: out=8'b01111111;default:out=8'bx;endcaseendendmoduleJK触发器(带清零和复位功能IF语句的描述):module cf(clk,clr,set,j,k,q);input clk,clr,set,j,k;output q;reg q;always@(posedge clk or negedge clr or negedge set)beginif(!clr)q<=0;else if(!set)q<=1;elsebeginif({j,k}==2'b00)q<=q;else if ({j,k}==2'b01)q<=0;else if ({j,k}==2'b10)q<=1;else q<=~q;endendendmoduleJK触发器:(带清零和复位功能case语句编写):module cf(clk,clr,set,j,k,q);input clk,clr,set,j,k;output q;reg q;always@(posedge clk or negedge clr or negedge set)beginif(!clr)q<=0;else if(!set)q<=1;else case({j,k})2'b00: q<=q;2'b01: q<=0;2'b10: q<=1;2'b11: q<=~q;default: q<=1'bx;endcaseendendmodule可以扩展任意进制的加减计数器:module jsq(clk,q,clr,load,d,ud);input clk,clr,load,ud;input[4:0]d;output[4:0]q;reg[4:0]q;always@(posedge clk)beginif(!clr)q<=0;else if(load)q<=d;else if(ud)beginif(q==23)q<=0;elseq<=q+1;endelse if(q==0)q<=23;elseq<=q-1;endendmodule4-1选择器:module xzq(out,in0,in1,in2,in3,sel);input in0,in1,in2,in3;input[1:0] sel;output out;reg out;always@(sel or in0 or in1 or in2 or in3)beginif(sel==2'b00) out=in0;else if(sel==2'b01) out=in1;else if(sel==2'b10) out=in2;else out=in3;endendmodule4_7数码管译码显示程序:module ym(a,b,c,d,e,f,g,D3,D2,D1,D0);input D3,D2,D1,D0;output a,b,c,d,e,f,g;reg a,b,c,d,e,f,g;always @( D3,D2,D1,D0)begincase ({D3,D2,D1,D0} ) //用case语句进行译码4'd0: { a,b,c,d,e,f,g }= 7'b1111110;4'd1: { a,b,c,d,e,f,g }= 7'b0110000;4'd2: { a,b,c,d,e,f,g }= 7'b1101101;4'd3: { a,b,c,d,e,f,g }= 7'b1111001;4'd4: { a,b,c,d,e,f,g }= 7'b0110011;4'd5: { a,b,c,d,e,f,g }= 7'b1011011;4'd6: { a,b,c,d,e,f,g }= 7'b1011111;4'd7: { a,b,c,d,e,f,g }= 7'b1110000;4'd8: { a,b,c,d,e,f,g }= 7'b1111111;4'd9: { a,b,c,d,e,f,g }= 7'b1111011;default: { a,b,c,d,e,f,g } = 7'bx;endcaseendendmodule两位计数译码:module jsq(clk,clr,pause,sh,sl,cn);input clk,clr,pause;output[3:0]sh,sl;output cn;reg [3:0]sh,sl;reg cn;always@(posedge clk or posedge clr)beginif(clr)begin{sh,sl}<=8'd00;cn<=0;endelse if(!pause)beginif(sl==9)beginsl<=0;if(sh==9)beginsh<=0;cn<=1;endelsesh<=sh+1;endelsebeginsl<=sl+1;cn<=0;endendendendmodulemodule ym(a,b,c,d,e,f,g,D3,D2,D1,D0);input D3,D2,D1,D0;output a,b,c,d,e,f,g;reg a,b,c,d,e,f,g;always @( D3,D2,D1,D0)begincase ({D3,D2,D1,D0} )//用case语句进行译码4'd0: { a,b,c,d,e,f,g }= 7'b1111110;4'd1: { a,b,c,d,e,f,g }= 7'b0110000;4'd2: { a,b,c,d,e,f,g }= 7'b1101101;4'd3: { a,b,c,d,e,f,g }= 7'b1111001;4'd4: { a,b,c,d,e,f,g }= 7'b0110011;4'd5: { a,b,c,d,e,f,g }= 7'b1011011;4'd6: { a,b,c,d,e,f,g }= 7'b1011111;4'd7: { a,b,c,d,e,f,g }= 7'b1110000;4'd8: { a,b,c,d,e,f,g }= 7'b1111111;4'd9: { a,b,c,d,e,f,g }= 7'b1111011;default: { a,b,c,d,e,f,g } = 7'bx;endcaseendendmodulemodule px(sel,sh,sl,y);input sel;input[3:0]sh,sl;output[3:0]y;reg [3:0]y;always@(sel)begincase(sel)1'b0: y<=sl;1'b1: y<=sh;default:y<=4'bx;endcaseendendmoduleRS触发器:抢答器:全加器:抢答器及显示电路:电子琴程序:module dd(clk,cx,f,nf);input clk;input[15:0]cx;output f,nf;reg[15:0]cnt;reg f,nf;always@(posedge clk)beginif(cnt==(cx-1))begincnt<=0;f<=~f;nf<=f;endelsecnt<=cnt+1;endendmodulemodule tz(in,reset,cx);input[6:0]in;input reset;output[15:0]cx;reg [15:0]cx;always@(in)beginif(!reset)cx<=0;elsebegincase(in)7'b0111111:cx=16'b0010010101101010;7'b1011111:cx=16'b0010000101010100;7'b1101111:cx=16'b0001110110010111;7'b1110111:cx=16'b0001101111111011;7'b1111011:cx=16'b0001100011101001;7'b1111101:cx=16'b0001011000110001;7'b1111110:cx=16'b0001001111000100;default:cx=16'bx;endcaseendendendmodulemodule zdtz(clk,in);input clk;output[6:0]in;reg[6:0]in;reg[3:0]cnt;always@(cnt)begincase(cnt)4'b0000:in=7'b0111111;4'b0001:in=7'b1011111;4'b0010:in=7'b1101111;4'b0011:in=7'b0111111;4'b0100:in=7'b0111111;4'b0101:in=7'b1011111;4'b0110:in=7'b1101111;4'b0111:in=7'b0111111;4'b1000:in=7'b1111011;4'b1001:in=7'b1111101;4'b1010:in=7'b1111110;default:in=7'bx;endcaseendalways@(posedge clk)beginif(cnt==10)cnt<=0;else cnt<=cnt+1;endendmodule。

数码管动态扫描

Library ieee;

use ieee.std-logic-1164.all;

Entity displaydecoder is

Port(hourH,hourL,minuteH,minuteL,secondH,secondL: in std_logic_vector(3downto0);

clk:in std_logic_vector(7downto0);

seg:out std_logic_vector(5downto0));

End Entity displaydecoder;

architecture Art1 of displaydecoder is

type states is(s0,s1,s2,s3,s4,s5);

signal current_state,next_state:state=s0;

signal bcd:std_logic_vector(3downto0)

P1:process(clk)

begin

if(rising_edge(clk) then

current_state<=next_state;

end process P1;

P2:process(current_state)

begin

case current_state is

when s0=>next_state<=s1;bcd<=secondL;com<="000001"; when s1=>next_state<=s2;bcd<=secondH;com<="000010"; when s2=>next_state<=s3;bcd<=minuteL;com<="000100"; when s3=>next_state<=s4;bcd<=minuteH;com<="001000"; when s4=>next_state<=s5;bcd<=hourL;com<="010000"; when s5=>next_state<=s0;bcd<=hourH;com<="100000"; when others=>next_state<=s0;bcd<=secondL;com<="000000"; end case;

end process P2;

P3:process(bcd)

begin

case bcd is

when B"0000"=>seg<=x"3f";

when B"0001"=>seg<=x"06";

when B"0010"=>seg<=x"5b";

when B"0011"=>seg<=x"4f ";

when B"0100"=>seg<=x"66 ";

when B"0101"=>seg<=x" 6d";

when B"0110"=>seg<=x"7d ";

when B"0111"=>seg<=x" 07";

when B"1000"=>seg<=x"7f ";

when B"1001"=>seg<=x"6f ";

when others=>seg<=x"00";

end case;

end process P3;

end Architecture Art1;

分频器设计(100hz-2hz)

Library ieee;

use ieee.std_logic_1164.all ;

use ieee.std_logic_unsigned.all;

Entity dividefrequency is

port (clk_in:in std_logic;

clk_out:out std_logic);

end Entity dividefrequency;

Architecture Art1 of dividefrequency

signal m:intger range 0 to 49:=0;

begin

P1:process(clk_in)

begin

if(rising_edge(clk_in) then

if(m=49) then

m<=0;

else m<=m+1;

end if;

end if;

end process P1;

P2:process(m)

begin

if(m<=4)then

clk_out<='0';

else clk_out<='0';

end if;

end process P2;

end ArchitectureArt1;

设计八bit移位寄存器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all; EntityShiftRegister is

port(clk,clr,leftdata,rightdata:in std_logic;

s1s2:in std_logic_vector(1downto0);

prein:instd_logic_vector(7downto0);

outdata:out std_logic_vector(7downto0);

serialout:out std_logic

);

ArchitectureArt1 of shift Register is

signal tmp:std_logic_vector(7downto0);

process(clk)

Begin

if(clk='0')then

tmp:std_logic_vector(7downto0);

process(clk)

Begin

if(clr='0')then

tmp<="0000_0000"serialout<='0';

elsif (rising_edge(clk))then

case s1s2 is

when"00"=>serialout<=tmp(7);tmp(7downto1)<=tmp(6downto0);tmp(0)<=leftdata; when"01"=>serialout<=tmp(0);tmp(6downto0)<=tmp(7downto1);tmp(7)<=rightdata; when"00"=>tmp<=prein;

whenothers=>null;

end case;

end if;

end process;

end ArchitectureArt1。