d触发器输出方程

- 格式:docx

- 大小:18.53 KB

- 文档页数:1

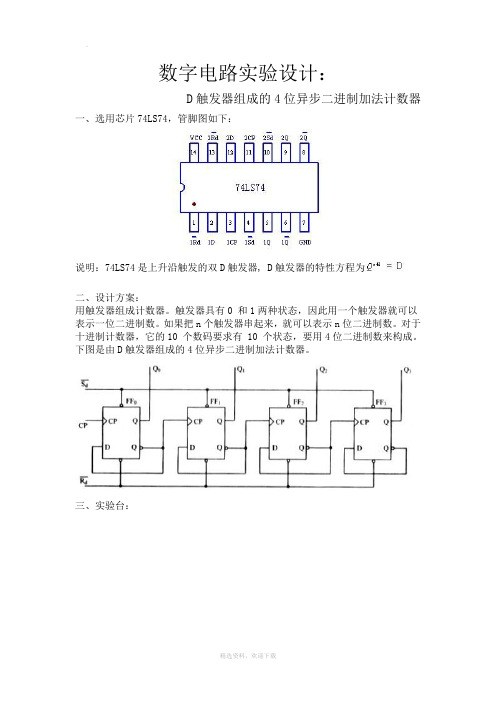

数字电路实验设计:D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下:说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为二、设计方案:用触发器组成计数器。

触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。

如果把n个触发器串起来,就可以表示n位二进制数。

对于十进制计数器,它的10 个数码要求有 10 个状态,要用4位二进制数来构成。

下图是由D触发器组成的4位异步二进制加法计数器。

三、实验台:四、布线:1、将芯片(1)的引脚4、10连到一起,2、将芯片(2)的引脚4、10连到一起,3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,4、将芯片(1)的引脚10连到+5V;5、将芯片(1)的引脚1、13连到一起,6、将芯片(2)的引脚1、13连到一起,7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,8、将芯片(1)的引脚13连到+5V;9、将芯片(1)的引脚3接到时钟信号CP10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚1111、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚312、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚1113、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q314、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

五、验证:接通电源on,默认输出原始状态0000每输入一个CP信号(单击CP),的状态就会相应的变化,变化规律为0000(原始状态)、1000、0100、1100、0010、1010、0110、1110、0001、1001、0101、1101、0011、1011、0111、1111Welcome !!! 欢迎您的下载,资料仅供参考!。

d触发器整形电路

d触发器是一种数字电路元件,常用于存储和传输数据。

它有两个输入端和两个输出端,称为D端和Q端。

D端是数据输入端,Q端是数据输出端。

当d触发器的时钟信号上升沿到来时,它会根据D 端的电平状态来改变输出端Q的电平状态。

d触发器的工作原理如下:当时钟信号上升沿到来时,如果D端为高电平,则Q端将保持高电平;如果D端为低电平,则Q端将保持低电平。

换句话说,d触发器会将D端的电平状态存储在自己的内部,然后在时钟信号上升沿到来时将其传输到输出端。

d触发器的作用非常广泛。

它可以用于存储数据,实现数据的暂存和传输功能。

在计算机中,d触发器常常被用作存储单元,用于存储二进制数据。

此外,d触发器还可以用于时序电路的设计,例如计数器和状态机。

除了存储和传输数据的功能外,d触发器还具有一些特殊的性质。

例如,它可以实现边沿检测功能,即在时钟信号的上升沿或下降沿到来时产生输出信号。

这种特性使得d触发器可以用于设计各种触发器、计数器和时序电路。

d触发器是一种非常重要的数字电路元件,它在存储和传输数据、实现边沿检测等方面具有广泛的应用。

通过合理的电路设计和使用d触发器,我们可以实现各种复杂的数字功能,提高电路的性能和

可靠性。

第4章习题及解答用门电路设计一个4线—2线二进制优先编码器。

编码器输入为3210A A A A ,3A 优先级最高,0A 优先级最低,输入信号低电平有效。

输出为10Y Y ,反码输出。

电路要求加一G 输出端,以指示最低优先级信号0A 输入有效。

题 解:根据题意,可列出真值表,求表达式,画出电路图。

其真值表、表达式和电路图如图题解所示。

由真值表可知3210G A A A A =。

(a)0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 0 1 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 10000000000000000000000000010100011111010110000103A 2A 1A 0A 1Y 0Y G真值表≥1&1Y 3A 2A 1&&1A 0Y &1GA 00 01 11 100010001111000000001101113A 2A 1A 0A 03231Y A A A A =+00 01 11 1000000011110001000011103A 2A 1A 0A 132Y A A =(b) 求输出表达式(c) 编码器电路图图 题解4.1试用3线—8线译码器74138扩展为5线—32线译码器。

译码器74138逻辑符号如图(a )所示。

题 解:5线—32线译码器电路如图题解所示。

&&&&11EN01234567BIN/OCTENY 0&G 1G 2AG 2B42101234567BIN/OCTEN&G 1G 2A G 2B42101234567BIN/OCT EN&G 1G 2A G 2B42101234567BIN/OCT EN&G 1G 2A G 2B421A 0A 1A 2A 3A 4Y 7Y 8Y 15Y 16Y 23Y 24Y 31图 题解4.3写出图所示电路输出1F 和2F 的最简逻辑表达式。

fpgad触发器微分

FPGA(现场可编程门阵列)触发器微分是指FPGA内部具有丰富的触发器,这些触发器在FPGA的设计中发挥着重要的作用。

以D触发器为例,其功能是在复位无效时,在时钟上升沿将输入d的值赋给输出q。

这意味着,只有在时钟上升沿之后,q的值才会发生变化。

这是一个非常重要的概念,即q的值是在时钟上升沿之后发生变化的。

FPGA触发器微分是FPGA设计的基础,所有的FPGA电路都是基于触发器的结构来进行设计的。

通过使用FPGA触发器微分,工程师可以精确地构建所需的硬件,而不必使用标准集成电路,从而节省了时间、成本和风险。

第三章 时序逻辑1.写出触发器的次态方程,并根据已给波形画出输出 Q 的波形。

解:2. 说明由RS 触发器组成的防抖动电路的工作原理,画出对应输入输出波形解:3. 已知JK 信号如图,请画出负边沿JK 触发器的输出波形(设触发器的初态为0)1)(1=+++=+c b a Qa cb Q nn4. 写出下图所示个触发器次态方程,指出CP 脉冲到来时,触发器置“1”的条件。

解:(1),若使触发器置“1”,则A 、B 取值相异。

(2),若使触发器置“1”,则A 、B 、C 、D 取值为奇数个1。

5.写出各触发器的次态方程,并按所给的CP 信号,画出各触发器的输出波形(设初态为0)解:6. 设计实现8位数据的串行→并行转换器。

B A B A D +=DC B A K J ⊕⊕⊕==Q AQ B Q D Q C Q E Q F Q7. 分析下图所示同步计数电路解:先写出激励方程,然后求得状态方程状态图如下:该计数器是五进制计数器,可以自启动。

8. 作出状态转移表和状态图,确定其输出序列。

解:求得状态方程如下故输出序列为:000119. 用D 触发器构成按循环码(000→001→011→111→101→100→000)规律工作的六进制同步计数器解:先列出真值表,然后求得激励方程PS NS 输出N0 0 0 0 0 1 00 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 1 1 0 1 0 1 0 1 1 0 0 0 1 0 0 0 0 0 1化简得:逻辑电路图如下:n Q 2n Q 1n Q 012+n Q 11+n Q 10+n Q n n n nn n n n n n nnQ Q Q Q Q Q Q Q Q Q Q Q Z 121002*********+==+==+++nnn nnn nnnn QQ Q D QQ Q D QQ Q Q D 121211121122+====+==+++10. 用D 触发器设计3位二进制加法计数器,并画出波形图。

反相器构建的d触发器

反相器构建的D触发器。

D触发器是数字电路中常用的一种触发器,用于存储和传输数据。

它的特点是可以在时钟信号的作用下,将输入信号的数值在时

钟沿发生变化时,传输到输出端。

而反相器构建的D触发器是一种

常见的实现方式。

反相器是一种基本的逻辑门电路,它可以将输入信号进行反相,即将输入的高电平转换为低电平,低电平转换为高电平。

在构建D

触发器时,可以利用反相器的特性来实现数据的存储和传输。

一个简单的反相器构建的D触发器可以由两个反相器和一个与

门构成。

首先,将输入信号通过一个反相器,得到它的反相信号。

然后将原始输入信号和反相信号分别连接到与门的两个输入端,这

样当时钟信号到来时,只有在时钟信号为高电平的时候,与门的输

出才会改变。

这样就实现了D触发器的功能,即在时钟信号的作用下,将输入信号的数值传输到输出端。

反相器构建的D触发器具有简单、稳定的特点,适用于数字电

路中的各种应用场合。

它可以用于时序电路中的数据存储、时序逻

辑电路中的状态转换等。

同时,由于反相器本身是一种常见的逻辑门,因此反相器构建的D触发器也易于集成和扩展,可以方便地应

用于大规模集成电路中。

总之,反相器构建的D触发器是数字电路中常用的一种触发器,它利用反相器的特性实现了数据的存储和传输。

它具有简单、稳定

的特点,适用于各种数字电路中的应用场合。

在实际应用中,可以

根据具体的需求和电路规模,灵活地选择反相器构建的D触发器来

实现各种功能。

第5章 锁存器与触发器 习题与参考答案[题5-1] 画出图题5-1所示的SR 锁存器输出端Q 、Q 端的波形,输入端S 与R 的波形如图所示。

(设Q 初始状态为0)S RSRSRQQ....图题5-1解:SR.QQ....[题5-2] 画出图题5-2所示的SR 锁存器输出端Q 、Q 端的波形,输入端S 与R 的波形如图所示。

(设Q 初始状态为0)S RS RQQ...SR....图题5-2解:SR.Q Q......[题5-3] 画出图题5-3所示的电平触发SR 触发器输出端Q 、Q 端的波形,输入端S 、R 与CLK 的波形如图所示。

(设Q 初始状态为0)C1S RSRQQ....CLKS RCLK...图题5-3解:S RCLK..Q Q..[题5-4] 画出图题5-4所示的电平触发D 触发器输出Q 端的波形,输入端D 与CLK 的波形如图所示。

(设Q 初始状态为0)C1D DQQ....CLKDCLK..图题5-4解:DCLK..QQ....[题5-5] 画出图题5-5所示的边沿触发D 触发器输出端Q 端的波形,输入端D 与CLK 的波形如图所示。

(设Q 初始状态为0)C11DD QQ....CLKDCLK ...DQQ....CLKDCLK...C11D (1)(2)图题5-5解:DCLK ...DCLK...(1)(2)QQ....[题5-6] 画出图题5-6所示的边沿D 触发器输出Q 端的波形,CLK 的波形如图所示。

(设Q 初始状态为0)C11D Q 1CLK....CLK.1C11D Q 2CLK .CLK .图题5-6解:CLK....Q1Q2Q3...[题5-7] 试画出图题5-7所示电路输出端Q 1、Q 0端的波形,CLK 的波形如图所示。

(设Q 初始状态为0)CLK.....图题5-7解:..CLK...Q0Q1[题5-8] 画出图题5-8所示的JK 触发器输出Q 端的波形,输入端J 、K 与CLK 的波形如图所示。

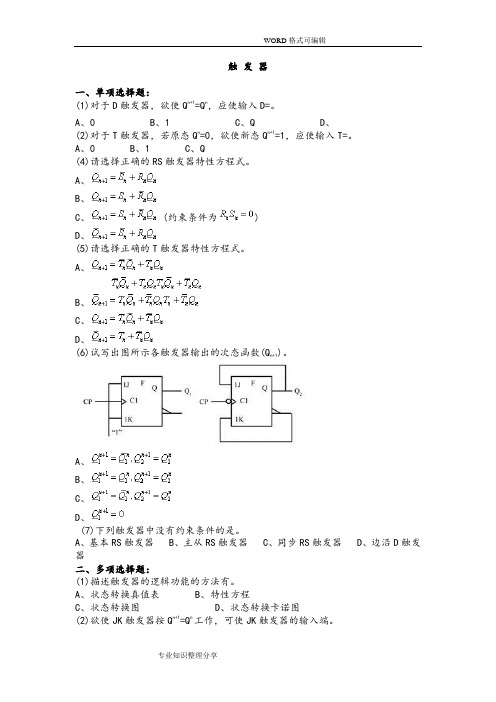

触发器一、单项选择题:(1)对于D触发器,欲使Q n+1=Q n,应使输入D=。

A、0B、1C、QD、(2)对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T=。

A、0B、1C、Q(4)请选择正确的RS触发器特性方程式。

A、B、C、 (约束条件为)D、(5)请选择正确的T触发器特性方程式。

A、B、C、D、(6)试写出图所示各触发器输出的次态函数(Q)。

n+1A、B、C、D、(7)下列触发器中没有约束条件的是。

A、基本RS触发器B、主从RS触发器C、同步RS触发器D、边沿D触发器二、多项选择题:(1)描述触发器的逻辑功能的方法有。

A、状态转换真值表B、特性方程C、状态转换图D、状态转换卡诺图(2)欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A、J=K=0B、J=Q,K=C、J=,K=QD、J=Q,K=0(3)欲使JK触发器按Q n+1=0工作,可使JK触发器的输入端。

A、J=K=1B、J=0,K=0C、J=1,K=0D、J=0,K=1(4)欲使JK触发器按Q n+1=1工作,可使JK触发器的输入端。

A、J=K=1B、J=1,K=0C、J=K=0D、J=0,K=1三、判断题:(1)D触发器的特性方程为Q n+1=D,与Q无关,所以它没有记忆功能。

()n(2)同步触发器存在空翻现象,而边沿触发器和主从触发器克服了空翻。

()(3)主从JK触发器、边沿JK触发器和同步JK触发器的逻辑功能完全相同。

()(8)同步RS触发器在时钟CP=0时,触发器的状态不改变( )。

(9)D触发器的特性方程为Q n+1=D,与Q n无关,所以它没有记忆功能( )。

(10)对于边沿JK触发器,在CP为高电平期间,当J=K=1时,状态会翻转一次( )。

四、填空题:(1)触发器有()个稳态,存储8位二进制信息要()个触发器。

(2)在一个CP脉冲作用下,引起触发器两次或多次翻转的现象称为触发器的(),触发方式为()式或()式的触发器不会出现这种现象。

t’触发器的特征方程

触发器是数字电路中常用的一种元件,用于存储和传输信息。

它们在计算机和电子设备中广泛应用,常用于存储和处理数据。

触发器的特征方程是描述其工作原理和行为的数学表达式。

在数字电路中,触发器的特征方程可以由其输入和输出之间的逻辑关系来表示。

这种关系可以通过真值表、逻辑符号或布尔代数等方式来表示。

触发器的特征方程通常使用逻辑门的代数表达式来描述。

特征方程由触发器的输入和输出之间的逻辑关系决定。

触发器可以分为不同类型,如RS触发器、D触发器、JK触发器等,每种类型的触发器都有不同的特征方程。

以D触发器为例,其特征方程可以表示为:

Q(t+1) = D

其中,Q(t+1)表示触发器在下一个时间步的输出,D表示触发器的输入。

这个方程表示了D触发器的工作原理,即将输入信号直接传递到输出。

特征方程可以帮助我们理解触发器的工作方式,并在设计数字电路时

起到指导作用。

通过触发器的特征方程,我们可以分析和预测触发器的输出行为,优化电路设计,提高系统性能。

总结而言,触发器的特征方程是描述其输入和输出之间逻辑关系的数学表达式。

它是数字电路设计和分析中的重要工具,能够帮助我们理解和优化电路的行为。

d触发器的激励方程理论说明1. 引言1.1 概述在数字电路中,d触发器是一种重要的时序元件,常被用于存储和传输数据。

它具有两个稳定状态,在给定时钟脉冲的作用下,能够对输入信号进行采样并将其保存,在时钟的上升沿或下降沿进行更新。

本文将深入研究d触发器的激励方程,探讨其在数字电路设计中的应用。

1.2 文章结构本文共分为五个部分。

首先是引言部分,概述了本文的主题和目标。

接下来是第二部分,详细介绍了d触发器的基本知识和定义,并着重探讨了激励方程的含义与作用。

然后,第三和第四部分将进一步阐述激励方程中的要点一和要点二。

最后,在结论部分对整篇文章进行总结并提出未来可能的研究方向。

1.3 目的本文旨在全面剖析d触发器的激励方程,并讨论其在数字电路设计中的理论意义及实际应用价值。

通过深入理解激励方程所包含的关键因素和计算方法,读者将具备对d触发器的正确使用和设计能力。

此外,本文还将指出激励方程中的关键要点,帮助读者更好地理解该方程的内涵和作用。

通过本文的阅读和研究,读者将能够掌握d触发器激励方程的原理,并能够灵活应用于实际工程项目中。

以上是关于“1. 引言”部分内容的详细描述,请根据需要对其进行修改和完善。

2. d触发器的激励方程理论说明:2.1 d触发器简介:d触发器是一种数字电路元件,通常用于存储和控制信息流。

它具有两个稳定的输入端(称为数据(D)和时钟(C)),以及一个输出端(Q)。

d触发器可以在时钟的作用下捕捉并存储来自数据输入端的信号,并将其输出到输出端。

2.2 激励方程定义:激励方程是描述在给定输入条件下d触发器输出状态的数学表达式。

对于d触发器而言,激励方程可以表示为:Q(t+1) = D(t)其中,Q(t+1)表示下一个时钟周期结束时的输出状态,D(t)表示当前时钟周期中的数据输入。

2.3 激励方程的作用和意义:激励方程具有重要的作用和意义。

首先,它可以帮助我们理解和分析d触发器在不同输入条件下的行为。

D 触发器是数字电路中的一种时序逻辑电路,其输出取决于输入和时钟信号。

D 触发器的输出方程可以根据其工作原理和逻辑表达式来确定。

D 触发器的工作原理是在时钟信号的边沿上更新输出。

当时钟信号处于上升沿(rising edge)或下降沿(falling edge)时,根据输入D 的值来更新输出。

具体输出的更新方式取决于是D 触发器采用的是正极性触发(positive edge-triggered)还是负极性触发(negative edge-triggered)。

以正极性触发的D 触发器为例,其输出方程可以表示为:

Q(t+1) = D

其中Q(t+1) 表示输出在时钟的下一个时刻的值,D 表示输入。

这个输出方程假设D 触发器没有时钟延迟或噪声等因素的影响,并且是理想的情况。

在实际应用中,还需要考虑电路的延迟、时序设计等因素。

所以具体的D 触发器输出方程可能会因电路实现的细节而有所不同。