基于FPGA的卡尔曼滤波器的设计

- 格式:docx

- 大小:559.25 KB

- 文档页数:7

基于_FPGA_的卡尔曼滤波器的设计与实现FPGA(Field Programmable Gate Array)是一种可以重新编程的可编程逻辑器件,可以根据用户的需要进行重新配置和编程,从而实现不同的应用。

卡尔曼滤波器是一种用于估计系统状态的滤波器,能够通过利用过去观测值和当前的测量值来估计未来的状态。

在本文中,我们将探讨基于FPGA的卡尔曼滤波器的设计与实现。

卡尔曼滤波器是一种递归的估计算法,用于估计状态变量的最优估计。

它将过去的观测值和当前的测量值进行加权平均,得到对未来状态的估计。

在实时应用中,常常需要高速和高准确度的数据处理,这就需要一种高效的硬件实现方法。

基于FPGA的卡尔曼滤波器可以提供高性能的实时数据处理,同时还能够灵活地适应不同的实时应用的需求。

基于FPGA的卡尔曼滤波器的设计与实现主要包括以下几个方面:首先,需要设计FPGA的硬件结构。

硬件结构通常包括状态估计器、卡尔曼增益计算器和误差估计器等关键模块。

状态估计器用于估计当前系统的状态变量,卡尔曼增益计算器用于计算卡尔曼增益矩阵,误差估计器用于估计状态估计器的误差。

这些模块之间需要进行数据传递和计算,因此需要设计合适的数据通路和控制信号。

其次,需要进行FPGA的编程和配置。

FPGA可以通过硬件描述语言(如VHDL或Verilog)进行编程和配置。

在设计过程中,需要将卡尔曼滤波器的算法转化为相应的硬件描述,并利用FPGA的配置工具将其加载到FPGA芯片中。

然后,需要进行系统级的仿真和验证。

在设计过程中,可以通过使用仿真工具对系统进行仿真和验证。

通过仿真可以检查系统的功能和性能,并进行必要的调试和优化。

最后,需要进行性能评估和优化。

FPGA的设计和实现需要考虑多个指标,如延迟、功耗和面积等。

通过性能评估和优化可以找出系统的瓶颈,并进行相应的改进,以提高系统的性能。

总结起来,基于FPGA的卡尔曼滤波器的设计与实现是一个复杂的过程,需要进行硬件结构设计、FPGA编程和配置、系统仿真和验证以及性能评估和优化等多个步骤。

摘要自适应滤波器是统计信号处理的一个重要组成部分。

在现代滤波处理技术中,自适应滤波器的处理效果尤为突出。

在众多滤波器中,特别是在一些对信号处理的实时性要求比较高,体积功耗有严格限制的场合,使用FPGA硬件实现的数字滤波器更为广泛。

本论文从自适应滤波器研究的重要意义入手,介绍了线性自适应滤波器的算法,对几种基于最小均方误差准则或最小平方误差准则的自适应滤波器算法进行研究,就滤波器的基本原理及设计方法做了简单的介绍,最终设计基于FPGA的LMS算法设计复数自适应滤波器,对设计方法进行叙述,并以VHDL语言编写程序进行仿真测试。

关键词:自适应滤波器;FPGA;自适应算法LMS;有限冲激响应滤波器FPGA-based design of adaptive filterStudent:TAN xx Teacher:CHEN xxAbstract:Adaptive filter is a statistical signal processing as an important component. Processing technology in the modern filter, the adaptive filter, particularly in the treatment effect. Among the filters, especially in some of the real-time signal processing requirements of higher power, there are strict restrictions on the size of the occasion, the use of FPGA hardware to achieve a wider range of digital filters.In this paper, adaptive filter from the importance of research to start to introduce the linear adaptive filter algorithm, based on several criteria MMSE or least square error criteria for the study of adaptive filter algorithm, it filters The basic principle and design method of a brief introduction, the final design of FPGA-based design of complex LMS adaptive filter algorithm, the design methods described, and VHDL languages in maxplus simulation test platform.Keywords: adaptive filter;FPGA;LMS adaptive algorithm;finite impulse response filter目录摘要 (I)1 绪论 (1)1.1 引言 (1)2 自适应算法研究及分析 (1)2.1 自适应滤波基本概念 (1)2.2 变步长自适应滤波算法 (2)2.3 仿射投影算法 (3)2.4 RLS自适应滤波算法 (3)2.5 LMS算法及其推广 (3)2.6小结 (6)3 滤波器原理介绍 (7)3.1 自适应滤波器原理 (7)3.2 本文滤波器的工作原理 (8)4 基于FPGA的自适应滤波器的设计 (11)4.1 基本设计方法 (11)4.2 设计流程 (12)4.2.1 设计准备 (13)4.2.2 设计输入 (13)4.2.3 功能仿真 (14)4.2.4 设计处理 (14)4.2.5 时序仿真 (14)4.2.6 器件编程测试 (14)4.3 自适应滤波器设计 (15)4.3.1 自适应滤波器结构 (16)4.3.2 复数滤波器设计与实现 (18)4.3.3 基本设计准备 (19)4.3.4 复数自适应滤波器设计防真 (22)4.4小结 (24)5 结论 (25)致谢 (26)参考文献 (27)1 绪论1.1 引言随着信号处理技术的不断发展,对信号处理速度的要求也不断提高。

基于FPGA分布式算法的滤波器设计摘要:本文介绍了一种基于FPGA分布式算法的滤波器设计。

该算法的思路是将原始信号划分为多个子信号,每个子信号在不同的FPGA上运算,在计算完成后,在各个FPGA上的结果被收集并进行合并。

这种算法可以大大提高计算效率,适用于需要处理大量数据的信号处理应用。

本文通过实验验证了该算法的有效性,并进行了性能比较。

关键词:FPGA、分布式算法、滤波器设计正文:引言滤波器是一种对信号进行处理的重要工具,它能够去除信号中的噪音,并提高信号的质量。

随着信号处理应用的不断发展,越来越多的数据需要被处理,因此提高滤波器的计算效率变得尤为重要。

FPGA作为一种快速灵活的硬件平台,可以提供高效并行计算的能力,因此在滤波器设计中得到了广泛的应用。

本文提出了一种基于FPGA分布式算法的滤波器设计。

该算法的思路是将原始信号划分为多个子信号,每个子信号在不同的FPGA上运算,在计算完成后,在各个FPGA上的结果被收集并进行合并。

这种算法可以大大提高计算效率,适用于需要处理大量数据的信号处理应用。

本文通过实验验证了该算法的有效性,并进行了性能比较。

算法设计FPGA分布式算法可以将一个大问题分解成多个小问题并行处理,在处理单个小问题时,CPU将其发送到FPGA,FPGA在本地完成处理后将结果返回给CPU。

这种算法可以大大提高计算效率,适用于需要处理大量数据的信号处理应用。

在滤波器设计中,我们可以将输入信号分为多个子信号,每个子信号在不同的FPGA上运算,在计算完成后,各个FPGA上的结果被收集并进行合并。

下面我们将介绍该算法的详细步骤。

1.将输入信号分割成多个子信号对于一个长为N的原始信号,我们将其划分为m个长度为L 的子信号:S1,S2,…,Sm。

其中,m=N/L。

这种划分方式可以平均分配计算量,并且每个FPGA处理的数据量不会过大,在保证精度的前提下,可以充分利用FPGA的并行计算能力。

2.在FPGA上滤波对于每个子信号Si,我们将其发送到不同的FPGA上进行处理。

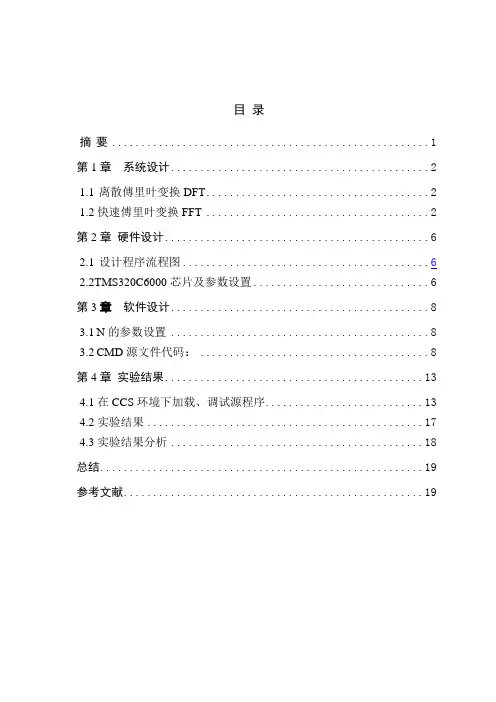

目录摘要 (1)第1章系统设计 (2)1.1离散傅里叶变换DFT (2)1.2快速傅里叶变换FFT (2)第2章硬件设计 (6)2.1设计程序流程图 (6)2.2TMS320C6000芯片及参数设置 (6)第3章软件设计 (8)3.1N的参数设置 (8)3.2CMD源文件代码: (8)第4章实验结果 (13)4.1在CCS环境下加载、调试源程序 (13)4.2实验结果 (17)4.3实验结果分析 (18)总结 (19)参考文献 (19)摘要本次课程设计主要运用CCS这一工具实现快速傅里叶变换(FFT)。

CCS(Code Composer Studio)是一种针对TM320系列DSP的集成开发环境,在Windows操作系统下,采用图形接口界面,提供环境配置、源文件编辑、程序调试、跟踪和分析等工具,可以帮助用户在一个软件环境下完成编辑、编译、链接、调试和数据分析等工作。

CCS有两种工作模式,即软件仿真器和硬件在线编程。

软件仿真器工作模式可以脱离DSP芯片,在PC上模拟DSP的指令集和工作机制,主要用于前期算法实现和调试。

硬件在线编程可以实时运行在DSP芯片上,与硬件开发板相结合进行在线编程和调试应用程序。

关键词:CCS ; 快速傅里叶变换(FFT);第1章 系统设计快速傅里叶变换FFT快速傅里叶变换(FFT )是一种高效实现离散傅里叶变换(DFT )的快速算法,是数字信号处理中最为重要的工具之一,它在声学,语音,电信和信号处理等领域有着广泛的应用。

1.1 离散傅里叶变换DFT对于长度为N 的有限长序列x(n),它的离散傅里叶变换(DFT )为1,1,0,)()(10-==∑-=N k W n x k X n n nkN (1)式中,Nj N e W /2π-= ,称为旋转因子或蝶形因子。

从DFT 的定义可以看出,在x(n)为复数序列的情况下,对某个k 值,直接按(1)式计算X(k) 只需要N 次复数乘法和(N-1)次复数加法。

卡尔曼滤波器的设计卡尔曼滤波器是一种由卡尔曼(Kalman)提出的用于时变线性系统的递归滤波器。

这个系统可用包含正交状态变量的微分方程模型来描述,这种滤波器是将过去的测量估计误差合并到新的测量误差中来估计将来的误差。

状态估计是卡尔曼滤波的重要组成部分。

一般来说,根据观测数据对随机量进行定量推断就是估计问题,特别是对动态行为的状态估计,它能实现实时运行状态的估计和预测功能。

比如对飞行器状态估计。

状态估计对于了解和控制一个系统具有重要意义,所应用的方法属于统计学中的估计理论。

最常用的是最小二乘估计,线性最小方差估计、最小方差估计、递推最小二乘估计等。

其他如风险准则的贝叶斯估计、最大似然估计、随机逼近方法也都有应用。

2.1程序设计%------------产生正弦波信号------------%t=0:0.1:20-0.1;T=0.1;y=5*sin(pi*t*0.5);figure;plot(t,y,’or’);axis([0,20,-8,8]);xlabel('时间/s');ylabel('质点位移/mm');title('理想质点偏离中心位移图');%------------添加噪声---------------%a=randn(1,200); Z=y+a;figure;plot(t,Z,’or’);axis([0,20,-8,8]);xlabel('时间/s ');ylabel('质点位移/mm');title(‘测量所得质点偏离中心位移图'); %----------建立系统模型------------%X=zeros(2,200);X(:,1)=[0,1];A=[1,T;0,1];B=[1/2*(T)^2 T]';H=[1,0];C=[0,0;0,1];Q=(0.25)^2;R=(0.25)^2;%--------卡尔曼算法----------------%for n=1:200Kg=C*H'/(H*C*H'+R);X(:,n)=X(:,n)+Kg*(Z(:,n)-H*X(:,n));X(:,n+1)=A*X(:,n);C=(eye(2,2)-Kg*H)*C;C=A*C*A'+B*Q*B';end%------------------------------------------% figuret=0:0.1:20;Y=X(1,:);plot(t,Y,'or');grid;axis([0,20,-8,8]);xlabel('时间/s ');ylabel('质点位移/mm ');title(‘卡尔曼滤波后输出质点最优化偏离中心位移'); 1.、理想质点偏离中心位移如下图1所示。

卡尔曼滤波器设计1.定义状态方程和观测方程:卡尔曼滤波器的设计首先需要明确过程和观测模型。

状态方程描述了系统的演化过程,通常是一个线性动力学模型。

观测方程表示测量值与状态之间的关系,也通常是一个线性模型。

2.估计系统的噪声统计性质:卡尔曼滤波器的性能与对系统噪声的准确估计密切相关。

系统噪声通常包括过程噪声和测量噪声,它们的统计性质可以通过实验或经验得到。

噪声的估计结果将用于卡尔曼滤波器的设计和参数配置。

3.初始化滤波器状态:卡尔曼滤波器需要一个初始系统状态估计值。

如果初始状态估计值比较准确,那么滤波器将更快地收敛到准确的状态估计结果。

初始状态估计可以通过历史数据、经验或其他先验知识来得到。

4.状态预测:根据系统的状态方程,可以通过对当前状态估计值进行预测,得到下一时刻的状态预测值。

预测过程中考虑了系统的动力学模型和过程噪声。

5.更新状态估计:当有新的测量数据时,可以将其与状态预测值进行比较,并通过更新状态估计来融合测量信息。

卡尔曼滤波器通过最小均方误差原理来计算综合后的状态估计值和协方差矩阵,以提供对系统状态的更准确估计。

6.重复预测和更新步骤:通过反复进行状态预测和更新步骤,可以得到系统的连续状态估计序列。

随着时间的推移,卡尔曼滤波器可以收敛到对系统状态的准确估计。

卡尔曼滤波器的设计涉及到对系统模型、噪声统计性质和初始状态的合理选择。

在实际应用中,设计者需要根据具体系统和应用需求来进行调整和优化。

此外,还可以通过引入扩展卡尔曼滤波器、无迹卡尔曼滤波器等变种算法来处理非线性系统或非高斯噪声的情况。

卡尔曼滤波器作为一种经典的状态估计算法,广泛应用于导航、控制、信号处理等领域。

它具有计算效率高、收敛速度快、适用于线性系统等优点,但也存在对模型假设的敏感性和局限性。

在实际应用中,设计者需要结合具体系统和应用场景的特点,合理选择和调整卡尔曼滤波器的参数和设计。

基于FPGA的卡尔曼滤波器的设计

时间:2010-04-12 12:52:33 来源:电子科技作者:米月琴,黄军荣西安电子科技大学摘要:针对电路设计中经常碰到数据的噪声干扰现象,提出了一种Kalman滤波的FPGA实现方法。

该方法采用了TI公司的高精度模数转换器ADSl25l以及Altera公司的EPlCl2,首先用卡尔曼滤波算法

设计了一个滤波器,然后将该滤波器分解成简单的加、减、乘、除运算。

通过基于FPGA平台的硬件与

软件的合理设计,成功地实现了数据噪声的滤除设计,并通过实践仿真计算,验证了所实现滤波的有效性。

关键词:卡尔曼;FPGA;最小方差估计

卡尔曼滤波是一个“Optimal Recursive Data Processing Algorithm(最优化自回归数据处

理算法)”,对于解决很大部分的问题,是最优化的,效率最高甚至是最有用的。

传统的卡尔曼滤波是

在DSP上实现的。

但是DSP成本相对较高,而且指令是串行执行的,不能满足有些要求较高的场合。

而FPGA由于其硬件结构决定了它的并行处理方式,无论在速度还是实时性都更胜一筹。

文中以基于FPGA

器件和A/D转换器的数据采集系统为硬件平台,进行了卡尔曼滤波算法设计,详述了基于FPGA的卡尔

曼滤波器的设计实现。

1 卡尔曼滤波算法

工程中,为了了解工程对象(滤波中称为系统)的各个物理量(滤波中称为状态)的确切数值,或为了

达到对工程对象进行控制的目的,必须利用测量手段对系统的各个状态进行测量。

但是,量测值可能仅

是系统的部分状态或是部分状态的线性组合,且量测值中有随机误差(常称为量测噪声)。

最优估计就是

针对上述问题的一种解决方法。

它能将仅与部分状态有关的测量进行处理,得出从统计意义上讲误差最

小的更多状态的估值。

误差最小的标准常称为估计准则,根据不同的估计准则和估计计算方法,有各种

不同的最优估计,卡尔曼滤波是一种递推线性最小方差估计的最优估计。

系统的状态方程可设定为

式(3)为系统噪声。

设设备的量测噪声为Vk,系统得量测方程为

式中,是利用当前状态预测的结果,是当前状态最优的结果,Pk+1/k是

*对应的covariance,Rk是对应的covanance,表示A的转置矩阵,Q是系统过程的covariance。

式(1),式(2)就是卡尔曼滤波器5个公式中的前两个,也就是对系统的预测。

可以得到将来状态k+l的最优化估算值。

式(9)中I为单位矩阵,对于单模型单测量,I=1。

当系统进入k+2状态时,Pk+1就是式(2)的Pk。

这样,算法就可以自回归的运算下去。

R为测量数据的方差;Q为系统过程噪声的方差,取值为,根据经验可设置为测量数据方差的1/10;P的初值可选为单位阵,I为单位阵,X的处置可选为(0,0)T。

算法示意图,如图1所示。

将算法矩阵展开并写成乘加形式,令

这些公式包含了一些加、减、乘、除的数学运算,用FPGA实现卡尔曼滤波就是用FPGA实现这些运算。

2 硬件设计

2.1 A/D选择

ADSl251是TI公司生产的一种高精度、宽动态范围的24位△~∑乏结构的模数转换器。

采样保持器的输入形式采用差分模拟输入方式,设计了一个简单的电平转换电路使得端和端之间的电压波动范围为士2.5 V。

ADSl251的时钟频率由8 MHz的外部晶振提供,系统时钟由FPGA给出。

ADSl251的内部结构图,如图2所示。

输出有3种模式:同步、异步及掉电模式,异步模式与Kalman滤波器数据输入接口连接比较方便。

其时序如图3所示。

2.2 FPGA设计

FPGA的特点在于灵活,通用。

如果资源够用,可以实现各种数字组合,包括CPU。

本系统采用的:FPGA是Ahera公司低价位的EP1C12,该芯片内含有两个PLLs,12060LEs及239616 Total RAMbits。

在

本系统的设计中,FPGA内主要实现以下几个功能:Kalman状态控制信号、Kalm-an滤波运算、A/D控

制模块、时钟及波特率设置等。

卡尔曼滤波器的系统结构图,如图4所示。

通过A/D转换芯片采集转换数据后,进入FPGA的A/D控制模块,在Kalman状态控制信号的作用下,进行滤波运算,然后通过控制接口将滤波数据输出。

由此可见,卡尔曼滤波的实现包括两部分:Kalman状态控制信号和Kalman滤波运算。

3 Kalmaft滤波器的设计

在FPGA中实现Kalman滤波器,重点在于平衡资源利用率和处理速度、数据运算精度之间的矛盾,

难点在于浮点加、减、乘、除的硬逻辑及卡尔曼滤波流程控制的实现。

一般地,实际应用中,数字采样

重复频率是待采样信号最高频率成分的5倍以上能保证较好恢复原信号,本设计中出于后期升级的考虑,将采样率设置在800次/s,是输出信号带宽的20倍。

通过第2节中的分解,Kalman滤波器由16次加法、20次乘法、1次除法以及必要的输入、输出及

循环控制组成,共45步。

状态控制器(Kal-man状态控制信号)实际是一个有限状态机,分别控制滤波器

中的45步运算,决定其执行顺序,每一步利用计数器为其提供必要的时钟周期。

Kalman滤波运算主要是浮点计算,浮点表示常用的标准是IEEE 754,IEEE二进制浮点数算术标准(IEEE754)是最广泛使用的浮点数运算标准,为许多CPU与浮点运算器所采用。

IEEE 754规定了4种表

示浮点数值的方式:单精确度(32位元)、双精确度(64位元)、延伸单精确度(43位元以上,较少使用)

与延伸双精确度(79位元以上,通常以80位元实做)。

二进制浮点数是以符号数值表示法格式储存,将最高效位元指定为符号位元(Sign Bit);“指数部分”,即次高效的e位元,为浮点数中经指数偏差(Exponent Bias)处理过后的指数;“小数部分”,

即剩下的f位元,为有效位数(Significand)减掉有效位数本身的最高效位元,如图5所示。

文中采用的单精度二进制小数,使用32个位元存储,如图6所示。

其中,31位是符号位;0表示正;1表示负;30~23位为阶数;22~0表示数值的有效位。

偏正值为

+127。

其表示的具体值可用式(27)表示

指数部分采用一个无符号的正数值存储。

单精度的指数部分是-126~+127加上127,指数值的大小

为1~254(0和255是特殊值)。

浮点小数计算时,指数值减去偏正值将是实际的指数大小。

由于资源的限制,滤波中的运算过程只能以有限的精度进行,但过低的精度容易引起滤波发散,同

时为了兼顾A/D高达24 bit的分辨率精度,在IEEE754单精度浮点数格式的基础上按照浮点表示的原

则做了改造,将指数部分减少到6位,尾数增加到25位,25位尾数可以完全表示A/D输出的24位采

样值,并削弱舍入误差的影响,其格式如图7所示。

本系统对处理速度的要求并不高,运算部件的设计并不考虑速度优化。

加法器按以下通用的规则设计:

(1)阶码相减:两个操作数阶码相减,求得阶差d=|Ea-Eb|;

(2)尾数对齐:阶码小的操作数的尾数右移d位;

(3)尾数相加:完成移位处理后的尾数相加运算;

(4)转换:尾数相加的结果为负数时,转换为符号尾数的表示方式;

(5)前导0/1的判定:判定由于减法结果产生的左移位数,对于加法判定是否右移一位或不移,对

前导0/1判定的结果进行编码以驱动规格化移位;

(6)规格化:规格化有效位并且根据移位的方向和位数修改最终的阶码Ef;

(7)舍入:根据IEEE标准判定最终结果的舍入,如果需要入,则最末有效位加1;如舍入引起溢出,则需要有效位右移1位,同时阶码Ef加1。

乘法器的设计相对简单,与加法器一样采用简单的设计规则:

(1)指数相加:完成两个操作数的指数相加运算;

(2)尾数调整:将尾数f调整为l/f的补码格式;

(3)尾数相乘:完成两个操作数的尾数相乘运算;

(4)规格化:根据尾数运算结果调整指数位,对尾数进行舍入截位操作,规格化输出结果。

采用Altera提供的IP核,除法器能完成IEEE754单精度除法运算。

数据进入该除法器前需要将自

定义的浮点格式的阶码扩展为8位加上95,尾数右移两位,转换为标准单精度浮点,计算结果再由标准

单精度浮点的按相反的方法转换为自定义浮点。

文中硬件编程语言是用Verilog实现的。

4 实测结果分析与结论

从系统输出数据中随机抽取一段数据用Matlab分析,其结果如图8所示。

实线C表示的是滤波前

的噪声:虚线B表示的是滤波后的噪声。

很容易看出经过滤波后噪声降低了很多。

仿真与实测对比分析

如表1所示。

5 结束语

卡尔曼滤波器在很多领域具有重要的作用,可以实现数字信号处理功能,并能满足实时性的要求。

用FPGA实现Kalman滤波过程,实现简便、成本较低、滤波效果好,被广泛应用于图像视频、陀螺惯导去噪、电子罗盘、雷达接收机目标跟踪处理、目标预测等图像、数据采集与处理领域。