Orcad16.5原理图转PADS_Logic原理图方法

- 格式:docx

- 大小:14.57 KB

- 文档页数:2

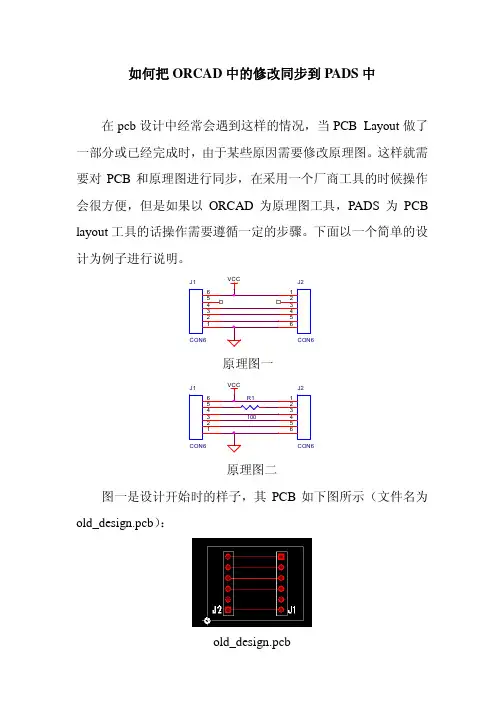

如何把ORCAD中的修改同步到PADS中在pcb设计中经常会遇到这样的情况,当PCB Layout做了一部分或已经完成时,由于某些原因需要修改原理图。

这样就需要对PCB和原理图进行同步,在采用一个厂商工具的时候操作会很方便,但是如果以ORCAD为原理图工具,PADS 为PCB layout工具的话操作需要遵循一定的步骤。

下面以一个简单的设计为例子进行说明。

原理图一原理图二图一是设计开始时的样子,其PCB如下图所示(文件名为old_design.pcb):old_design.pcb原理图二是修改后原理图的样子。

和原理图相比增加了一个电阻R1。

在修改完原理图后,需要重新生成asc文件,如何生成asc 文件相信大家都已经非常清楚,这里就不作说明了。

接下来用新生成asc文件的文件产生新的PCB文件,新生成的PCB如下图所示(可以看到比old_design.pcb中多了电阻R1和R1到J1和J2的网络):new_design.pcb不对新生成的pcb做任何的修改,直接保存文件,这里把新文件命名为new_design.pcb。

再下来是产生eco 文件,先打开old_design.pcb,然后选择Tools -> Compare/ECO,如下图所示。

面。

如下图所示:在Original Design to Compare and Update 中把Use Current PCB Design前面的选项选中,意思把当前文件做为原始的比对文件。

然后在在New Design With Change中找到新生成的PCB 文件,这里是new_design.pcb。

接着在Output Options选中Generate ECO file(*.eco),eco文件的默然保存地址是在pads的安装目录下(可修改eco文件的保存目录),这里把eco文件保存在桌面并命名为old.eco。

选择好后点击Run。

运行后会产生一个如下的对话框。

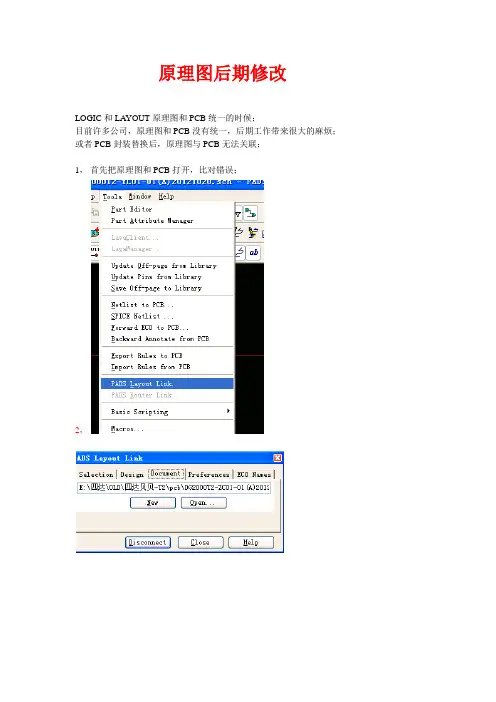

原理图后期修改LOGIC和LAYOUT原理图和PCB统一的时候;目前许多公司,原理图和PCB没有统一,后期工作带来很大的麻烦;或者PCB封装替换后,原理图与PCB无法关联;1,首先把原理图和PCB打开,比对错误;2,首先,Compare PCB,找出差异点;这个不会对文件进行修改;而EOC TO PCB和EOC from PCB,则会修改文件;前者直接修改PCB,后者直接修改原理图;批量修改封装及和原理图对应如果需要替换PCB文件中所以的RC0402封装;方法一:不改PART name,只改DECAL方法操作过程如下;1,首先,在PCB中选择一个PART 叫RES,decal叫:RC0402DS的元件;2,然后再进入元件编辑界面下;在FILE中选择库文件;在滤波器中,输入新的DECALS,如:RC0603*;找到相应替换后的封装;双击;再CLOSE 封装界面;提示:新的样式名字:部件名TYPE:RES下增加了DECAL;RC0603DS 如果点确定;那么出现如下界面;提示:是否所有的DECAL=RC0402DS的都变更RC0603DS切记:选择保留属性;以上变更,PART name 没有修改,只修改了DECAL name;那么比较的时候,是不会出比对信息的;需要把:PART “打钩”,Compare PCB Decal Assignment “打钩”然后,选择从EOC from PCB,发现,所以的原理图封装里面,DECAL对应成新的封装;PCB中的DECAL变更了,对于原理图来说,只是一个文字关联上的变更;所以推荐用这个方法一;方法二:PART和DECAL同时替换;在FIND中寻找;选择PCB已经有的元件;这个元件在原理图里面也有对应关系的;这种方式连PART也一起修改了;然后,选择EOC from PCB;那么发现,原理图同步修改了;但是需要原理图里面有INDUCTOR库文件;-------------------------但是如果使用的新的元件是原来PCB里面没有的库,如MTC的“PART CC0402,decal:CC0402DS;”那么就无法从PCB同步进原理图里面;那么就需要手动在SCH建立一个封装,PART NAME: CC0402,decal:CC0402,(PS:DECAL可以不管;)直接在原理图库文件编辑中,把Name of修改成RC0402就可以了;。

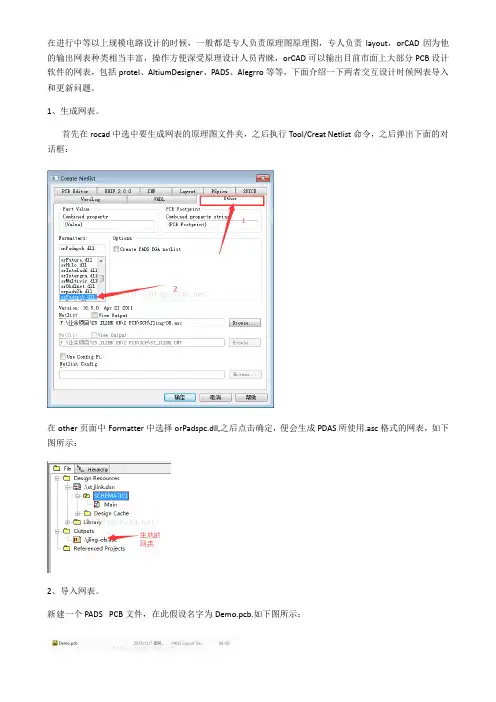

在进行中等以上规模电路设计的时候,一般都是专人负责原理图原理图,专人负责layout,orCAD因为他的输出网表种类相当丰富,操作方便深受原理设计人员青睐,orCAD可以输出目前市面上大部分PCB设计软件的网表,包括protel、AltiumDesigner、PADS、Alegrro等等,下面介绍一下两者交互设计时候网表导入和更新问题。

1、生成网表。

首先在rocad中选中要生成网表的原理图文件夹,之后执行Tool/Creat Netlist命令,之后弹出下面的对话框:在other页面中Formatter中选择orPadspc.dll,之后点击确定,便会生成PDAS所使用.asc格式的网表,如下图所示:2、导入网表。

新建一个PADS PCB文件,在此假设名字为Demo.pcb.如下图所示:新建文件之后,首先要有自己的PCB封装库,并且设置好自己的PCB封装库路径,设置PCB封装库路径发方法如下:工具/选项之后弹出来如下界面:点击右侧的库列表文件夹,如下图所示,之后选择自己的PCB封装库所在位置:这样自己的封装库路径设置完成了。

之后可以在PADS layout软件中导入网表了。

打开刚才创建的Demo.pcb文件,执行"文件/导入"命令,打开刚才用orcad生成的.asc文件。

之后会弹出一个检验文本,提示所有的错误和警告,如下图所示:之后还会弹出一个警告对话框,可以忽略之。

之后所有的原件就导入进来了,如下图所示,此时元件是堆放在一起的:执行命令:“工具/分散元器件”,之后元器件被分散开来,如下图所示:这样,就完成了PCB的导入,之后可以进行布线工作。

3、更新原理图中修改的网表。

在PCB布线的时候可能会修改原理图中的部分器件或者连线,这时候就要进行网表更新。

步骤如下:a、更改好原理图之后,重新生成网表,然后新建一个空的PCB文件,给这个pcb文件起一个名字(名字随便起),这里就叫做temp.pcb.b、打开temp.pcb文件,执行"文件/导入"命令,导入新生成的.asc网表,之后关闭temp.pcb。

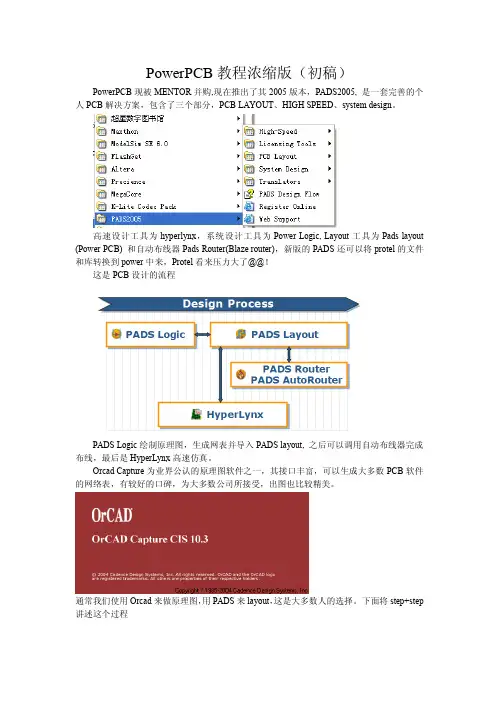

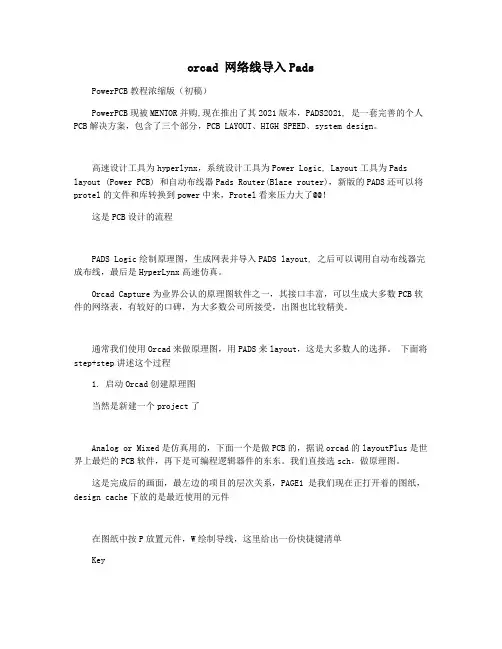

orcad 网络线导入PadsPowerPCB教程浓缩版(初稿)PowerPCB现被MENTOR并购,现在推出了其2021版本,PADS2021, 是一套完善的个人PCB解决方案,包含了三个部分,PCB LAYOUT、HIGH SPEED、system design。

高速设计工具为hyperlynx,系统设计工具为Power Logic, Layout工具为Pads layout (Power PCB) 和自动布线器Pads Router(Blaze router),新版的PADS还可以将protel的文件和库转换到power中来,Protel看来压力大了@@!这是PCB设计的流程PADS Logic绘制原理图,生成网表并导入PADS layout, 之后可以调用自动布线器完成布线,最后是HyperLynx高速仿真。

Orcad Capture为业界公认的原理图软件之一,其接口丰富,可以生成大多数PCB软件的网络表,有较好的口碑,为大多数公司所接受,出图也比较精美。

通常我们使用Orcad来做原理图,用PADS来layout,这是大多数人的选择。

下面将step+step讲述这个过程1. 启动Orcad创建原理图当然是新建一个project了Analog or Mixed是仿真用的,下面一个是做PCB的,据说orcad的layoutPlus是世界上最烂的PCB软件,再下是可编程逻辑器件的东东。

我们直接选sch,做原理图。

这是完成后的画面,最左边的项目的层次关系,PAGE1 是我们现在正打开着的图纸,design cache下放的是最近使用的元件在图纸中按P放置元件,W绘制导线,这里给出一份快捷键清单KeyMouse click equivalent Select All Ascend hierarchy Descend hierarchy Place bus Place bus entry Place power Place ground Place junction Place net alias Place part Place text Place wire Place polyline Place No connect symbol Record macro Play macro Configure macro Add parts(s) to group Remove part(s) from groupCTRL+A SHIFT+A or A SHIFT+D or D SHIFT+B or B SHIFT+E or E SHIFT+F or F SHIFT+G or G SHIFT+J or J SHIFT+N or N SHIFT+P or P SHIFT+T or T SHIFT+W or W SHIFT+Y or Y SHIFT+X or XF7 F8 F9CTRL+SHIFT+A CTRL+SHIFT+R同时说明一下Orcad的库文件,常用的元件在Discrete.olb里,其他的东西可以搜索,实在没有就自己做了。

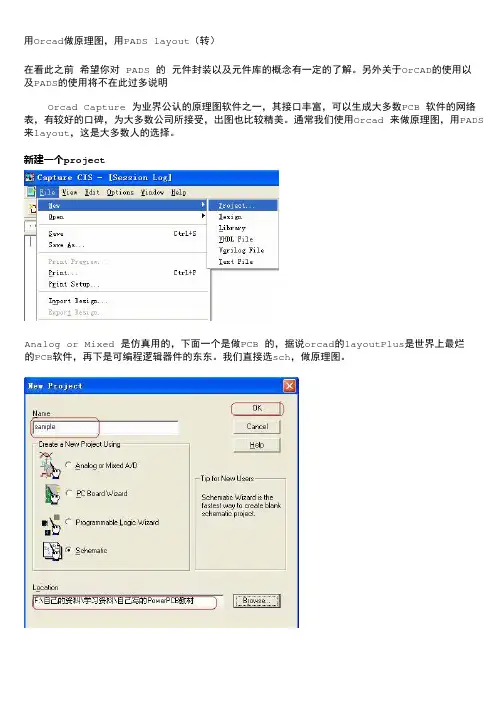

用Orcad做原理图,用PADS layout(转)在看此之前希望你对PADS的元件封装以及元件库的概念有一定的了解。

另外关于OrCAD的使用以及PADS的使用将不在此过多说明Orcad Capture为业界公认的原理图软件之一,其接口丰富,可以生成大多数PCB软件的网络表,有较好的口碑,为大多数公司所接受,出图也比较精美。

通常我们使用Orcad来做原理图,用PADS 来layout,这是大多数人的选择。

新建一个projectAnalog or Mixed是仿真用的,下面一个是做PCB的,据说orcad的layoutPlus是世界上最烂的PCB软件,再下是可编程逻辑器件的东东。

我们直接选sch,做原理图。

这是完成后的画面,最左边的项目的层次关系,PAGE1是我们现在正打开着的图纸,design cache下放的是最近使用的元件。

在图纸中按P放置元件,W绘制导线,这里给出一份快捷键清单同时说明一下Orcad的库文件,常用的元件在Discrete.olb里,其他的东西可以搜索,实在没有就自己做了。

按键盘上的P进入元件选择选择合适的库,以及需要的元件放一个无极性电容再放一个电阻按键盘上的W进行连线修改一下元件的Value填写封装信息对原理图中某一元件双击,出现了一个属性页,看看这个电阻是怎么填的需要说明的是,这里的FootPrint要填写PADS中的PartType。

把另外的元件的封装也都填写上将原理图最小化,同时在项目里选中.dsn这时右边的工具可用第一个U?给元件编号的第二个是反向标注,用于PCB-àSCH的反向修改第三个DRC design rule check第四个用于生成网表,第五个生成次项目中所设计的元件,最后一个生成报表,这个比较有用,可以用来产生元件清单,照着这个单子就可以采购了!按下生成网表一定要选择Pads2k.dll或是padspcb.dll,只有这两个dll才能生成PADS的网络表,且生成的文件名是.asc。

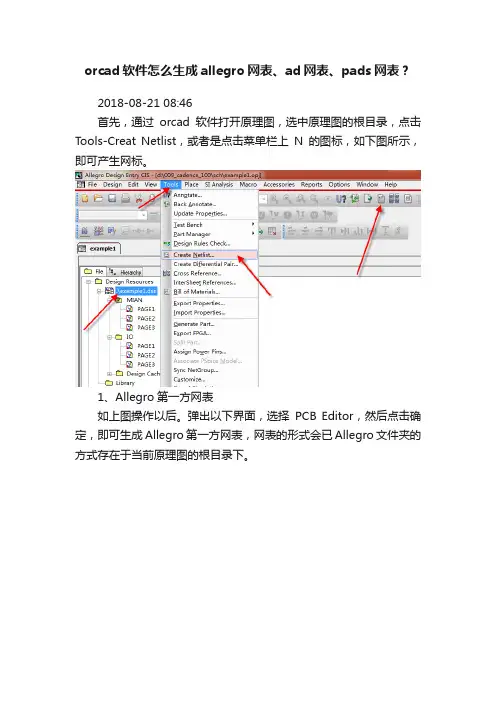

orcad软件怎么生成allegro网表、ad网表、pads网表?

2018-08-21 08:46

首先,通过orcad软件打开原理图,选中原理图的根目录,点击Tools-Creat Netlist,或者是点击菜单栏上N的图标,如下图所示,即可产生网标。

1、Allegro第一方网表

如上图操作以后。

弹出以下界面,选择PCB Editor,然后点击确定,即可生成Allegro第一方网表,网表的形式会已Allegro文件夹的方式存在于当前原理图的根目录下。

2、Allegro第三方网表

如上图操作以后,弹出以下界面,选择Other,然后下面的Fotmatters中选中orTelesis.dll,点击确定即可生成Allegro第三方网表,产生的网表位于当前原理图的根目录下。

3、AD的网表

如上图操作以后,弹出以下界面,选择Other,然后下面的Fotmatters中选中orProtel2.dll,点击确定即可生成AD的网表,产生的网表位于当前原理图的根目录下。

4、PADS的网表

如上图操作以后,弹出以下界面,选择Other,然后下面的Fotmatters中选中orPads2k.dll,点击确定即可生成PADS的网表,产生的网表位于当前原理图的根目录下。

-----------------------------------------------------

每天学习一个技巧,日积月累你也是专家!

使用前请您先阅读以下条款:

1、转载本站提供的资源请勿删除本说明文件。

2、分享技术文档源自凡亿教育技术经验总结分享!

3、表述观点仅代表我方建议,不对直接引用造成损失负责!更多精彩技术文章请参考:PCB联盟网。

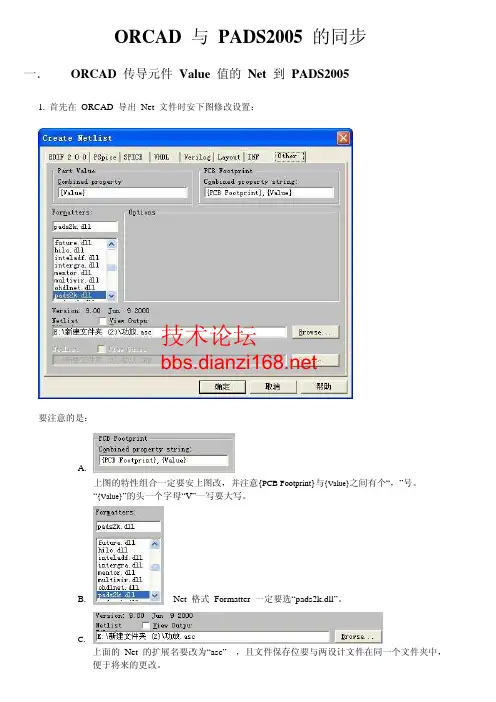

ORCAD 与 PADS2005 的同步一. ORCAD 传导元件 Value 值的 Net 到 PADS20051. 首先在 ORCAD 导出 Net 文件时安下图修改设置:技术论坛要注意的是:A.B.C.上图的特性组合一定要安上图改,并注意{PCB Footprint}与{Value}之间有个“,”号。

“{Value}”的头一个字母“V”一写要大写。

Net 格式 Formatter 一定要选“pads2k.dll”。

上面的 Net 的扩展名要改为“asc” ,且文件保存位要与两设计文件在同一个文件夹中, 便于将来的更改。

2. 新建一个 PADS Layout 文件,并安下图导入上述的 Net 文件:注意:导入 Net 文件时是否弹出错误提示,并查看文本文件是否有错。

技术论坛3. 安下图滩开所有元器件4. 右键如下图点选 Component,框选所有的元器件或选一个按 Ctrl+A 全选。

5. 全选所有元器件后,再如下图右键点选 Query/Modify技术论坛6. 在弹出的对话框中选 Labels ,如下图技术论坛7. 在 Label: 下接项选 New,如下图8. 再点一下图标系统会对所有元器件进行处理。

9. 系统处理完后弹出个对话框,如下图设置:技术论坛注意:Attribu:下接选ValueShow:下接选 ValueX 与 Y 座标输入0 , 0 (这样做是为了让等一下显示出来的值定位在元器件的原点上)Size: 输入 50 Line: 输入 5 (这样是统一显示值的字体大小)点 OK 即可,但此时还是没有看到有元件的值,怎么办?等等。

我们还要设一下颜色就可以看到啦。

10. 按 Ctrl+Alt+C 打开颜色属性对话框,把 Attribu 列中原来是黑色设为另一种颜色,如下图:11. 点 OK ,这时再看画面,是不是多了 Value 的值显示出来了呢。

如下图:技术论坛另一种方法:很简单的,不过在做 PCB 封装器件时要把“Tepy” 改为“Value”。

OrCAD与PADS交互设计详解(有图有真相)2011-01-21 11:01说明:作者是tanganrong此文发表在中国电子开发网我把它copy下来,整理成WORD了,我当时看到这篇文章,就按作者的方法做了,效果还不错,在ORCAD设计原理图,转换为PADS Logic再与PADS layout 同步。

原理图修改也在ORCAD里面进行,再转,再同步。

其实网上有那种在ORCAD里面设计原理图,然后导出网表,在LAYOUT里面布板的方法,这里面有个布局的麻烦,要是元器件少还好办,要是有几百个甚至上千个元器件,布局岂不是非常麻烦?所以还是要靠Logic与Layout交互布局。

当然在ORCAD10.5转PADS logic 9.1的时候,由于软件使用方法,规则的不同,会有一些error和warning,不过不会影响大局,转过来以后,会出现logic的电源符号问题,也不必理会,没有大碍。

作者用的软件版本是ORCAD10.3和PADS2007SP1,这个版本作者直接打开ORCAD文件了。

我用的版本软件版本是ORCAD10.5和PADS9.1,PADS9.1自带了转换器,需要转换一下,然后再用Logic打开,最后也通过了。

tanganrong在论坛上看到有一些喜欢用PADS和ORCAD的人问如何进行交互设计,确实觉得关于这方面的资料网上找到的不是很多,好多都是ORCAD+PCBNaigator +PADS的方法,但是PCBNaigator支持ORCAD和PADS的版本都有点低,并且交互的时候同时选中几个元件的时候会发现交互不起作用,所以本人参考网上一些方法在一些环节上做了变动,用起来还算马马虎虎。

啰嗦了半天现在说点正事了(以下是基于ORCAD10.3和PADS2007SP1的实例):第一步:用Logic打开ORCAD文档,检查是否有错误(一般不会出错),第二步:打开文档后右键弹出菜单选SELECT PARTS,接着CTRL+A选中所有元件,第三步:在任意选中元件上右键-SAVE TO LIBRARY命令(让所有PARTS变为decal,只有这样才能把封装同步到PCB)在弹出的对话框里选SELECT NOT IN LIB(那些已经存在的decal可以忽略)第四步:同步PCB(很简单,没必要多说)以下就是效果了如果有朋友有更好的方法,希望拿出来交流一下。

ORCAD 与 PADS2005 的同步一. ORCAD 传导元件 Value 值的 Net 到 PADS20051. 首先在 ORCAD 导出 Net 文件时安下图修改设置:技术论坛要注意的是:A.B.C.上图的特性组合一定要安上图改,并注意{PCB Footprint}与{Value}之间有个“,”号。

“{Value}”的头一个字母“V”一写要大写。

Net 格式 Formatter 一定要选“pads2k.dll”。

上面的 Net 的扩展名要改为“asc” ,且文件保存位要与两设计文件在同一个文件夹中, 便于将来的更改。

2. 新建一个 PADS Layout 文件,并安下图导入上述的 Net 文件:注意:导入 Net 文件时是否弹出错误提示,并查看文本文件是否有错。

技术论坛3. 安下图滩开所有元器件4. 右键如下图点选 Component,框选所有的元器件或选一个按 Ctrl+A 全选。

5. 全选所有元器件后,再如下图右键点选 Query/Modify技术论坛6. 在弹出的对话框中选 Labels ,如下图技术论坛7. 在 Label: 下接项选 New,如下图8. 再点一下图标系统会对所有元器件进行处理。

9. 系统处理完后弹出个对话框,如下图设置:技术论坛注意:Attribu:下接选ValueShow:下接选 ValueX 与 Y 座标输入0 , 0 (这样做是为了让等一下显示出来的值定位在元器件的原点上)Size: 输入 50 Line: 输入 5 (这样是统一显示值的字体大小)点 OK 即可,但此时还是没有看到有元件的值,怎么办?等等。

我们还要设一下颜色就可以看到啦。

10. 按 Ctrl+Alt+C 打开颜色属性对话框,把 Attribu 列中原来是黑色设为另一种颜色,如下图:11. 点 OK ,这时再看画面,是不是多了 Value 的值显示出来了呢。

如下图:技术论坛另一种方法:很简单的,不过在做 PCB 封装器件时要把“Tepy” 改为“Value”。

ORCAD原理图更新到PADS的方法

2011-04-01 22:45:43| 分类:默认分类| 标签:原理图 orcad pads pcb 文件|举报|字号大中小订

阅

在ORCAD中对电路原理图进行Modify,通常需要Update相应的PCB Layout。

具体方法:

1、打开原理图文件,(ORCAD中打开),输出修改后的原理图的网表(PADS格式)。

2.在PADS中新建一个设计,先导入LIBRARY,再导入ORCAD中输出的网表,无任何错误后保

存此PCB文件。

3.打开原来设计好的PCB Layout文件,执行TOOLs\Compare/ECO Tools 弹出比对对话框。

原始文件选择当前文件;新设计文件就选择刚才导入网表的那个PCB文档。

输出选项选择产生ECO文件,设置好ECO文件的路径和名称后按RUN.生成ECO文件!

4.完成后,关掉设计文件。

重新打开原有的PCB文件,选择导入ECO文件,然后选择刚才产生

的ECO文件,导入PCB。

5.导入PCB后,PCB文件中的网络连接就与当前原理图设计中的一致了,至此完成了Orcad到PADS

layout的Update!

这个ECO文件就是你更新了的原理图信息。

千万不要象protel那样直接用netlist更新,在pads里那样的话就惨了-它不支持直接netlist update,会把你的设计重新加载一遍,原来的都覆盖掉了。

PADS比较严谨,注重流程化和分工、记录,不可以随意的对设计进行更改,以免出错。

ECO文件就是这个目的!。

Orcad16.5原理图转PADS logic原理图方法在将Cadence公司的Orcad16.5原理图文件转成PADS logic原理图时,需要经过以下三个步骤:(1)将Orcad16.5原理图文件另存为低版本Orcad16.2原理图文件,文件后缀名为.dsn;(2)在PADS logic软件中打开Orcad16.2原理图文件,并将其另存为PADS logic原理图文件,文件后缀名为.sch;转换后得到的PADS logic原理图文件除了在文件属性方面是Logic原理图文件后,其仍然具备Orcad16.2原理图文件的特点。

例如,在Orcad16.2原理图文件中存在原理图分层结构,而Logic 不存在该结构。

但是由于两种软件的原理图兼容,因此,在Orcad16.2原理图中出现的符号仍然可以在PADS logic中打开,但是PADS Logic本身可能没有该符号或者该符号异于Orcad16.2原理图符号(例如,两种软件的接地符号、电源符号、换页连接符等就不一样)。

因此,转换后得到的Logic原理图文件并不能直接使用,需要进一步修改为标准PADS logic原理图文件。

(3)在PADS logic中新建一个原理图文件,然后将转换后得到的Logic原理图文件复制到该原理图中,这时发生一个很有意思的现象:将原有Logic 原理图文件粘贴到该原理图中时,原Orcad16.2原理图符号竟然变成了Logic 本身的原理图符号(例如,接地符号、电源符号、换页连接符变成Logic原理图符号)。

在此基础上,用Logic中的元件替换转换后原理图文件中的符号即可。

将该文件进行修改并保存,即可得到最终的标准Logic原理图文件。

对于由Protel99se原理图文件转换后得到的PADS logic原理图文件,也存在上述步骤(2)提到的问题,因此也可以用上述步骤(3)来解决。

温馨提示:在将Orcad16.2原理图文件转换后得到的PADS logic原理图文件在局部一些地方跟原有Orcad16.2原理图文件有差异,这时需要对转换后得到的原理文件进行小范围修改,以保证原始设计文件在Logic中真实展现。

Orcad16.5原理图转PADS logic原理图方法

在将Cadence公司的Orcad16.5原理图文件转成PADS logic原理图时,需要经过以下三个步骤:

(1)将Orcad16.5原理图文件另存为低版本Orcad16.2原理图文件,文件后缀名为.dsn;

(2)在PADS logic软件中打开Orcad16.2原理图文件,并将其另存为PADS logic原理图文件,文件后缀名为.sch;转换后得到的PADS logic原理图文件除了在文件属性方面是Logic原理图文件后,其仍然具备Orcad16.2原理图文件的特点。

例如,在Orcad16.2原理图文件中存在原理图分层结构,而Logic 不存在该结构。

但是由于两种软件的原理图兼容,因此,在Orcad16.2原理图中出现的符号仍然可以在PADS logic中打开,但是PADS Logic本身可能没有该符号或者该符号异于Orcad16.2原理图符号(例如,两种软件的接地符号、电源符号、换页连接符等就不一样)。

因此,转换后得到的Logic原理图文件并不能直接使用,需要进一步修改为标准PADS logic原理图文件。

(3)在PADS logic中新建一个原理图文件,然后将转换后得到的Logic原理图文件复制到该原理图中,这时发生一个很有意思的现象:将原有Logic 原理图文件粘贴到该原理图中时,原Orcad16.2原理图符号竟然变成了Logic 本身的原理图符号(例如,接地符号、电源符号、换页连接符变成Logic原理图符号)。

在此基础上,用Logic中的元件替换转换后原理图文件中的符号即可。

将该文件进行修改并保存,即可得到最终的标准Logic原理图文件。

对于由Protel99se原理图文件转换后得到的PADS logic原理图文件,也存在上述步骤(2)提到的问题,因此也可以用上述步骤(3)来解决。

温馨提示:

在将Orcad16.2原理图文件转换后得到的PADS logic原理图文件在局部一些地方跟原有Orcad16.2原理图文件有差异,这时需要对转换后得到的原理文件进行小范围修改,以保证原始设计文件在Logic中真实展现。

需要特别注意的几个地方是:

⏹电源网络的名称:将Orcad16.2原理图文件转换成PADS logic原理图文

件后,原有文件的电源网络可能会发生变化,这时需要特别注意;

⏹换页连接符:将Orcad16.2原理图文件转换成PADS logic原理图文件后,

原有文件的换页连接符被完整保留,而它并不是Logic中的换页连接符,

因此要对换页连接符进行修改;

⏹接地符号:将Orcad16.2原理图文件转换成PADS logic原理图文件后,

原有文件的接地符号被完整保留,而它并不是Logic中的接地符号,因

此要对接地符号进行修改;

⏹电阻和电容:将Orcad16.2原理图文件转换成PADS logic原理图文件后,

原有文件的电阻和电容符号被完整保留,而它并不是Logic中的电阻和

电容符号,因此要对电阻和电容符号进行修改;

⏹元件类型的替换:将Orcad16.2原理图文件转换成PADS logic原理图文

件后,原有文件的元件符号被完整保留,而该元件在Logic中可能不存

在,因此要对原理图中的元件进行替换。

⏹如果Orcad16.5原理图文件是分层结构,要特别注意顶层模块相互之间

的连接关系,如果两个模块中直接相连的网络的名称不一致,在PADS

Logic文件中则要进行等价修改替换,使它们的网络名称一致。

这是因为PADS Logic软件不允许将不同名称的网络连接在一起,而Orcad16.5软件允许这样做。