chapter 6 modulation techniques for mobile radio(16-04)

- 格式:pdf

- 大小:3.00 MB

- 文档页数:83

AgilentDigital Modulation in Communications Systems—An IntroductionApplication Note 1298This application note introduces the concepts of digital modulation used in many communications systems today. Emphasis is placed on explaining the tradeoffs that are made to optimize efficiencies in system design.Most communications systems fall into one of three categories: bandwidth efficient, power efficient, or cost efficient. Bandwidth efficiency describes the ability of a modulation scheme to accommodate data within a limited bandwidth. Power efficiency describes the ability of the system to reliably send information at the lowest practical power level.In most systems, there is a high priority on band-width efficiency. The parameter to be optimized depends on the demands of the particular system, as can be seen in the following two examples.For designers of digital terrestrial microwave radios, their highest priority is good bandwidth efficiency with low bit-error-rate. They have plenty of power available and are not concerned with power efficiency. They are not especially con-cerned with receiver cost or complexity because they do not have to build large numbers of them. On the other hand, designers of hand-held cellular phones put a high priority on power efficiency because these phones need to run on a battery. Cost is also a high priority because cellular phones must be low-cost to encourage more users. Accord-ingly, these systems sacrifice some bandwidth efficiency to get power and cost efficiency. Every time one of these efficiency parameters (bandwidth, power, or cost) is increased, another one decreases, becomes more complex, or does not perform well in a poor environment. Cost is a dom-inant system priority. Low-cost radios will always be in demand. In the past, it was possible to make a radio low-cost by sacrificing power and band-width efficiency. This is no longer possible. The radio spectrum is very valuable and operators who do not use the spectrum efficiently could lose their existing licenses or lose out in the competition for new ones. These are the tradeoffs that must be considered in digital RF communications design. This application note covers•the reasons for the move to digital modulation;•how information is modulated onto in-phase (I) and quadrature (Q) signals;•different types of digital modulation;•filtering techniques to conserve bandwidth; •ways of looking at digitally modulated signals;•multiplexing techniques used to share the transmission channel;•how a digital transmitter and receiver work;•measurements on digital RF communications systems;•an overview table with key specifications for the major digital communications systems; and •a glossary of terms used in digital RF communi-cations.These concepts form the building blocks of any communications system. If you understand the building blocks, then you will be able to under-stand how any communications system, present or future, works.Introduction25 5 677 7 8 8 9 10 10 1112 12 12 13 14 14 15 15 16 17 18 19 20 21 22 22 23 23 24 25 26 27 28 29 29 30 311. Why Digital Modulation?1.1 Trading off simplicity and bandwidth1.2 Industry trends2. Using I/Q Modulation (Amplitude and Phase Control) to Convey Information2.1 Transmitting information2.2 Signal characteristics that can be modified2.3 Polar display—magnitude and phase representedtogether2.4 Signal changes or modifications in polar form2.5 I/Q formats2.6 I and Q in a radio transmitter2.7 I and Q in a radio receiver2.8 Why use I and Q?3. Digital Modulation Types and Relative Efficiencies3.1 Applications3.1.1 Bit rate and symbol rate3.1.2 Spectrum (bandwidth) requirements3.1.3 Symbol clock3.2 Phase Shift Keying (PSK)3.3 Frequency Shift Keying3.4 Minimum Shift Keying (MSK)3.5 Quadrature Amplitude Modulation (QAM)3.6 Theoretical bandwidth efficiency limits3.7 Spectral efficiency examples in practical radios3.8 I/Q offset modulation3.9 Differential modulation3.10 Constant amplitude modulation4. Filtering4.1 Nyquist or raised cosine filter4.2 Transmitter-receiver matched filters4.3 Gaussian filter4.4 Filter bandwidth parameter alpha4.5 Filter bandwidth effects4.6 Chebyshev equiripple FIR (finite impulse response) filter4.7 Spectral efficiency versus power consumption5. Different Ways of Looking at a Digitally Modulated Signal Time and Frequency Domain View5.1 Power and frequency view5.2 Constellation diagrams5.3 Eye diagrams5.4 Trellis diagramsTable of Contents332 32 32 33 33 34 3435 35 3637 37 37 38 38 39 39 39 40 41 41 42 434344466. Sharing the Channel6.1 Multiplexing—frequency6.2 Multiplexing—time6.3 Multiplexing—code6.4 Multiplexing—geography6.5 Combining multiplexing modes6.6 Penetration versus efficiency7. How Digital Transmitters and Receivers Work7.1 A digital communications transmitter7.2 A digital communications receiver8. Measurements on Digital RF Communications Systems 8.1 Power measurements8.1.1 Adjacent Channel Power8.2 Frequency measurements8.2.1 Occupied bandwidth8.3 Timing measurements8.4 Modulation accuracy8.5 Understanding Error Vector Magnitude (EVM)8.6 Troubleshooting with error vector measurements8.7 Magnitude versus phase error8.8 I/Q phase error versus time8.9 Error Vector Magnitude versus time8.10 Error spectrum (EVM versus frequency)9. Summary10. Overview of Communications Systems11. Glossary of TermsTable of Contents (continued)4The move to digital modulation provides more information capacity, compatibility with digital data services, higher data security, better quality communications, and quicker system availability. Developers of communications systems face these constraints:•available bandwidth•permissible power•inherent noise level of the systemThe RF spectrum must be shared, yet every day there are more users for that spectrum as demand for communications services increases. Digital modulation schemes have greater capacity to con-vey large amounts of information than analog mod-ulation schemes. 1.1 Trading off simplicity and bandwidthThere is a fundamental tradeoff in communication systems. Simple hardware can be used in transmit-ters and receivers to communicate information. However, this uses a lot of spectrum which limits the number of users. Alternatively, more complex transmitters and receivers can be used to transmit the same information over less bandwidth. The transition to more and more spectrally efficient transmission techniques requires more and more complex hardware. Complex hardware is difficult to design, test, and build. This tradeoff exists whether communication is over air or wire, analog or digital.Figure 1. The Fundamental Tradeoff1. Why Digital Modulation?51.2 Industry trendsOver the past few years a major transition has occurred from simple analog Amplitude Mod-ulation (AM) and Frequency/Phase Modulation (FM/PM) to new digital modulation techniques. Examples of digital modulation include•QPSK (Quadrature Phase Shift Keying)•FSK (Frequency Shift Keying)•MSK (Minimum Shift Keying)•QAM (Quadrature Amplitude Modulation) Another layer of complexity in many new systems is multiplexing. Two principal types of multiplex-ing (or “multiple access”) are TDMA (Time Division Multiple Access) and CDMA (Code Division Multiple Access). These are two different ways to add diversity to signals allowing different signals to be separated from one another.Figure 2. Trends in the Industry62.1 Transmitting informationTo transmit a signal over the air, there are three main steps:1.A pure carrier is generated at the transmitter.2.The carrier is modulated with the informationto be transmitted. Any reliably detectablechange in signal characteristics can carryinformation.3.At the receiver the signal modifications orchanges are detected and demodulated.2.2 Signal characteristics that can be modified There are only three characteristics of a signal that can be changed over time: amplitude, phase, or fre-quency. However, phase and frequency are just dif-ferent ways to view or measure the same signal change. In AM, the amplitude of a high-frequency carrier signal is varied in proportion to the instantaneous amplitude of the modulating message signal.Frequency Modulation (FM) is the most popular analog modulation technique used in mobile com-munications systems. In FM, the amplitude of the modulating carrier is kept constant while its fre-quency is varied by the modulating message signal.Amplitude and phase can be modulated simultane-ously and separately, but this is difficult to gener-ate, and especially difficult to detect. Instead, in practical systems the signal is separated into another set of independent components: I(In-phase) and Q(Quadrature). These components are orthogonal and do not interfere with each other.Figure 3. Transmitting Information (Analog or Digital)Figure 4. Signal Characteristics to Modify2. Using I/Q Modulation to Convey Information72.3 Polar display—magnitude and phase repre-sented togetherA simple way to view amplitude and phase is with the polar diagram. The carrier becomes a frequency and phase reference and the signal is interpreted relative to the carrier. The signal can be expressed in polar form as a magnitude and a phase. The phase is relative to a reference signal, the carrier in most communication systems. The magnitude is either an absolute or relative value. Both are used in digital communication systems. Polar diagrams are the basis of many displays used in digital com-munications, although it is common to describe the signal vector by its rectangular coordinates of I (In-phase) and Q(Quadrature).2.4 Signal changes or modifications inpolar formFigure 6 shows different forms of modulation in polar form. Magnitude is represented as the dis-tance from the center and phase is represented as the angle.Amplitude modulation (AM) changes only the magnitude of the signal. Phase modulation (PM) changes only the phase of the signal. Amplitude and phase modulation can be used together. Frequency modulation (FM) looks similar to phase modulation, though frequency is the controlled parameter, rather than relative phase.Figure 6. Signal Changes or Modifications8One example of the difficulties in RF design can be illustrated with simple amplitude modulation. Generating AM with no associated angular modula-tion should result in a straight line on a polar display. This line should run from the origin to some peak radius or amplitude value. In practice, however, the line is not straight. The amplitude modulation itself often can cause a small amount of unwanted phase modulation. The result is a curved line. It could also be a loop if there is any hysteresis in the system transfer function. Some amount of this distortion is inevitable in any sys-tem where modulation causes amplitude changes. Therefore, the degree of effective amplitude modu-lation in a system will affect some distortion parameters.2.5 I/Q formatsIn digital communications, modulation is often expressed in terms of I and Q. This is a rectangular representation of the polar diagram. On a polar diagram, the I axis lies on the zero degree phase reference, and the Q axis is rotated by 90 degrees. The signal vector’s projection onto the I axis is its “I” component and the projection onto the Q axisis its “Q” component.Figure 7. “I-Q” Format92.6 I and Q in a radio transmitterI/Q diagrams are particularly useful because they mirror the way most digital communications sig-nals are created using an I/Q modulator. In the transmitter, I and Q signals are mixed with the same local oscillator (LO). A 90 degree phase shifter is placed in one of the LO paths. Signals that are separated by 90 degrees are also known as being orthogonal to each other or in quadrature. Signals that are in quadrature do not interfere with each other. They are two independent compo-nents of the signal. When recombined, they are summed to a composite output signal. There are two independent signals in I and Q that can be sent and received with simple circuits. This simpli-fies the design of digital radios. The main advan-tage of I/Q modulation is the symmetric ease of combining independent signal components into a single composite signal and later splitting such a composite signal into its independent component parts. 2.7 I and Q in a radio receiverThe composite signal with magnitude and phase (or I and Q) information arrives at the receiver input. The input signal is mixed with the local oscillator signal at the carrier frequency in two forms. One is at an arbitrary zero phase. The other has a 90 degree phase shift. The composite input signal (in terms of magnitude and phase) is thus broken into an in-phase, I, and a quadrature, Q, component. These two components of the signal are independent and orthogonal. One can be changed without affecting the other. Normally, information cannot be plotted in a polar format and reinterpreted as rectangular values without doing a polar-to-rectangular conversion. This con-version is exactly what is done by the in-phase and quadrature mixing processes in a digital radio. A local oscillator, phase shifter, and two mixers can perform the conversion accurately and efficiently.Figure 8. I and Q in a Practical Radio Transmitter Figure 9. I and Q in a Radio Receiver102.8 Why use I and Q?Digital modulation is easy to accomplish with I/Q modulators. Most digital modulation maps the data to a number of discrete points on the I/Q plane. These are known as constellation points. As the sig-nal moves from one point to another, simultaneous amplitude and phase modulation usually results. To accomplish this with an amplitude modulator and a phase modulator is difficult and complex. It is also impossible with a conventional phase modu-lator. The signal may, in principle, circle the origin in one direction forever, necessitating infinite phase shifting capability. Alternatively, simultaneous AM and Phase Modulation is easy with an I/Q modulator. The I and Q control signals are bounded, but infi-nite phase wrap is possible by properly phasing the I and Q signals.This section covers the main digital modulation formats, their main applications, relative spectral efficiencies, and some variations of the main modulation types as used in practical systems. Fortunately, there are a limited number of modula-tion types which form the building blocks of any system.3.1 ApplicationsThe table below covers the applications for differ-ent modulation formats in both wireless communi-cations and video. Although this note focuses on wireless communica-tions, video applications have also been included in the table for completeness and because of their similarity to other wireless communications.3.1.1 Bit rate and symbol rateTo understand and compare different modulation format efficiencies, it is important to first under-stand the difference between bit rate and symbol rate. The signal bandwidth for the communications channel needed depends on the symbol rate, not on the bit rate.Symbol rate =bit ratethe number of bits transmitted with each symbol 3. Digital Modulation Types and Relative EfficienciesBit rate is the frequency of a system bit stream. Take, for example, a radio with an 8 bit sampler, sampling at 10 kHz for voice. The bit rate, the basic bit stream rate in the radio, would be eight bits multiplied by 10K samples per second, or 80 Kbits per second. (For the moment we will ignore the extra bits required for synchronization, error correction, etc.)Figure 10 is an example of a state diagram of a Quadrature Phase Shift Keying (QPSK) signal. The states can be mapped to zeros and ones. This is a common mapping, but it is not the only one. Any mapping can be used.The symbol rate is the bit rate divided by the num-ber of bits that can be transmitted with each sym-bol. If one bit is transmitted per symbol, as with BPSK, then the symbol rate would be the same as the bit rate of 80 Kbits per second. If two bits are transmitted per symbol, as in QPSK, then the sym-bol rate would be half of the bit rate or 40 Kbits per second. Symbol rate is sometimes called baud rate. Note that baud rate is not the same as bit rate. These terms are often confused. If more bits can be sent with each symbol, then the same amount of data can be sent in a narrower spec-trum. This is why modulation formats that are more complex and use a higher number of states can send the same information over a narrower piece of the RF spectrum.3.1.2 Spectrum (bandwidth) requirementsAn example of how symbol rate influences spec-trum requirements can be seen in eight-state Phase Shift Keying (8PSK). It is a variation of PSK. There are eight possible states that the signal can transi-tion to at any time. The phase of the signal can take any of eight values at any symbol time. Since 23= 8, there are three bits per symbol. This means the symbol rate is one third of the bit rate. This is relatively easy to decode.Figure 10. Bit Rate and Symbol Rate Figure 11. Spectrum Requirements3.1.3 Symbol ClockThe symbol clock represents the frequency and exact timing of the transmission of the individual symbols. At the symbol clock transitions, the trans-mitted carrier is at the correct I/Q(or magnitude/ phase) value to represent a specific symbol (a specific point in the constellation).3.2 Phase Shift KeyingOne of the simplest forms of digital modulation is binary or Bi-Phase Shift Keying (BPSK). One appli-cation where this is used is for deep space teleme-try. The phase of a constant amplitude carrier sig-nal moves between zero and 180 degrees. On an I and Q diagram, the I state has two different values. There are two possible locations in the state dia-gram, so a binary one or zero can be sent. The symbol rate is one bit per symbol.A more common type of phase modulation is Quadrature Phase Shift Keying (QPSK). It is used extensively in applications including CDMA (Code Division Multiple Access) cellular service, wireless local loop, Iridium (a voice/data satellite system) and DVB-S (Digital Video Broadcasting — Satellite). Quadrature means that the signal shifts between phase states which are separated by 90 degrees. The signal shifts in increments of 90 degrees from 45 to 135, –45, or –135 degrees. These points are chosen as they can be easily implemented using an I/Q modulator. Only two I values and two Q values are needed and this gives two bits per symbol. There are four states because 22= 4. It is therefore a more bandwidth-efficient type of modulation than BPSK, potentially twice as efficient.Figure 12. Phase Shift Keying3.3 Frequency Shift KeyingFrequency modulation and phase modulation are closely related. A static frequency shift of +1 Hz means that the phase is constantly advancing at the rate of 360 degrees per second (2 πrad/sec), relative to the phase of the unshifted signal.FSK (Frequency Shift Keying) is used in many applications including cordless and paging sys-tems. Some of the cordless systems include DECT (Digital Enhanced Cordless Telephone) and CT2 (Cordless Telephone 2).In FSK, the frequency of the carrier is changed as a function of the modulating signal (data) being transmitted. Amplitude remains unchanged. In binary FSK (BFSK or 2FSK), a “1” is represented by one frequency and a “0” is represented by another frequency.3.4 Minimum Shift KeyingSince a frequency shift produces an advancing or retarding phase, frequency shifts can be detected by sampling phase at each symbol period. Phase shifts of (2N + 1) π/2radians are easily detected with an I/Q demodulator. At even numbered sym-bols, the polarity of the I channel conveys the transmitted data, while at odd numbered symbols the polarity of the Q channel conveys the data. This orthogonality between I and Q simplifies detection algorithms and hence reduces power con-sumption in a mobile receiver. The minimum fre-quency shift which yields orthogonality of I and Q is that which results in a phase shift of ±π/2radi-ans per symbol (90 degrees per symbol). FSK with this deviation is called MSK (Minimum Shift Keying). The deviation must be accurate in order to generate repeatable 90 degree phase shifts. MSK is used in the GSM (Global System for Mobile Communications) cellular standard. A phase shift of +90 degrees represents a data bit equal to “1,”while –90 degrees represents a “0.” The peak-to-peak frequency shift of an MSK signal is equal to one-half of the bit rate.FSK and MSK produce constant envelope carrier signals, which have no amplitude variations. This is a desirable characteristic for improving the power efficiency of transmitters. Amplitude varia-tions can exercise nonlinearities in an amplifier’s amplitude-transfer function, generating spectral regrowth, a component of adjacent channel power. Therefore, more efficient amplifiers (which tend to be less linear) can be used with constant-envelope signals, reducing power consumption.Figure 13. Frequency Shift KeyingMSK has a narrower spectrum than wider devia-tion forms of FSK. The width of the spectrum is also influenced by the waveforms causing the fre-quency shift. If those waveforms have fast transi-tions or a high slew rate, then the spectrumof the transmitter will be broad. In practice, the waveforms are filtered with a Gaussian filter, resulting in a narrow spectrum. In addition, the Gaussian filter has no time-domain overshoot, which would broaden the spectrum by increasing the peak deviation. MSK with a Gaussian filter is termed GMSK (Gaussian MSK).3.5 Quadrature Amplitude ModulationAnother member of the digital modulation family is Quadrature Amplitude Modulation (QAM). QAM is used in applications including microwave digital radio, DVB-C (Digital Video Broadcasting—Cable), and modems.In 16-state Quadrature Amplitude Modulation (16QAM), there are four I values and four Q values. This results in a total of 16 possible states for the signal. It can transition from any state to any other state at every symbol time. Since 16 = 24, four bits per symbol can be sent. This consists of two bits for I and two bits for Q. The symbol rate is one fourth of the bit rate. So this modulation format produces a more spectrally efficient transmission. It is more efficient than BPSK, QPSK, or 8PSK. Note that QPSK is the same as 4QAM.Another variation is 32QAM. In this case there are six I values and six Q values resulting in a total of 36 possible states (6x6=36). This is too many states for a power of two (the closest power of two is 32). So the four corner symbol states, which take the most power to transmit, are omitted. This reduces the amount of peak power the transmitter has to generate. Since 25= 32, there are five bits per sym-bol and the symbol rate is one fifth of the bit rate. The current practical limits are approximately256QAM, though work is underway to extend the limits to 512 or 1024 QAM. A 256QAM system uses 16 I-values and 16 Q-values, giving 256 possible states. Since 28= 256, each symbol can represent eight bits. A 256QAM signal that can send eight bits per symbol is very spectrally efficient. However, the symbols are very close together and are thus more subject to errors due to noise and distortion. Such a signal may have to be transmit-ted with extra power (to effectively spread the symbols out more) and this reduces power efficiency as compared to simpler schemes.Figure 14. Quadrature Amplitude ModulationCompare the bandwidth efficiency when using256QAM versus BPSK modulation in the radio example in section 3.1.1 (which uses an eight-bit sampler sampling at 10 kHz for voice). BPSK uses80 Ksymbols-per-second sending 1 bit per symbol.A system using 256QAM sends eight bits per sym-bol so the symbol rate would be 10 Ksymbols per second. A 256QAM system enables the same amount of information to be sent as BPSK using only one eighth of the bandwidth. It is eight times more bandwidth efficient. However, there is a tradeoff. The radio becomes more complex and is more susceptible to errors caused by noise and dis-tortion. Error rates of higher-order QAM systems such as this degrade more rapidly than QPSK as noise or interference is introduced. A measureof this degradation would be a higher Bit Error Rate (BER).In any digital modulation system, if the input sig-nal is distorted or severely attenuated the receiver will eventually lose symbol lock completely. If the receiver can no longer recover the symbol clock, it cannot demodulate the signal or recover any infor-mation. With less degradation, the symbol clock can be recovered, but it is noisy, and the symbol locations themselves are noisy. In some cases, a symbol will fall far enough away from its intended position that it will cross over to an adjacent posi-tion. The I and Q level detectors used in the demodulator would misinterpret such a symbol as being in the wrong location, causing bit errors. QPSK is not as efficient, but the states are much farther apart and the system can tolerate a lot more noise before suffering symbol errors. QPSK has no intermediate states between the four corner-symbol locations, so there is less opportunity for the demodulator to misinterpret symbols. QPSK requires less transmitter power than QAM to achieve the same bit error rate.3.6 Theoretical bandwidth efficiency limits Bandwidth efficiency describes how efficiently the allocated bandwidth is utilized or the ability of a modulation scheme to accommodate data, within a limited bandwidth. The table below shows the theoretical bandwidth efficiency limits for the main modulation types. Note that these figures cannot actually be achieved in practical radios since they require perfect modulators, demodula-tors, filter, and transmission paths.If the radio had a perfect (rectangular in the fre-quency domain) filter, then the occupied band-width could be made equal to the symbol rate.Techniques for maximizing spectral efficiency include the following:•Relate the data rate to the frequency shift (as in GSM).•Use premodulation filtering to reduce the occupied bandwidth. Raised cosine filters,as used in NADC, PDC, and PHS, give thebest spectral efficiency.•Restrict the types of transitions.Modulation Theoretical bandwidthformat efficiencylimitsMSK 1bit/second/HzBPSK 1bit/second/HzQPSK 2bits/second/Hz8PSK 3bits/second/Hz16 QAM 4 bits/second/Hz32 QAM 5 bits/second/Hz64 QAM 6 bits/second/Hz256 QAM 8 bits/second/HzEffects of going through the originTake, for example, a QPSK signal where the normalized value changes from 1, 1 to –1, –1. When changing simulta-neously from I and Q values of +1 to I and Q values of –1, the signal trajectory goes through the origin (the I/Q value of 0,0). The origin represents 0 carrier magnitude. A value of 0 magnitude indicates that the carrier amplitude is 0 for a moment.Not all transitions in QPSK result in a trajectory that goes through the origin. If I changes value but Q does not (or vice-versa) the carrier amplitude changes a little, but it does not go through zero. Therefore some symbol transi-tions will result in a small amplitude variation, while others will result in a very large amplitude variation. The clock-recovery circuit in the receiver must deal with this ampli-tude variation uncertainty if it uses amplitude variations to align the receiver clock with the transmitter clock. Spectral regrowth does not automatically result from these trajectories that pass through or near the origin. If the amplifier and associated circuits are perfectly linear, the spectrum (spectral occupancy or occupied bandwidth) will be unchanged. The problem lies in nonlinearities in the circuits.A signal which changes amplitude over a very large range will exercise these nonlinearities to the fullest extent. These nonlinearities will cause distortion products. In con-tinuously modulated systems they will cause “spectral regrowth” or wider modulation sidebands (a phenomenon related to intermodulation distortion). Another term which is sometimes used in this context is “spectral splatter.”However this is a term that is more correctly used in asso-ciation with the increase in the bandwidth of a signal caused by pulsing on and off.3.7 Spectral efficiency examples inpractical radiosThe following examples indicate spectral efficien-cies that are achieved in some practical radio systems.The TDMA version of the North American Digital Cellular (NADC) system, achieves a 48 Kbits-per-second data rate over a 30 kHz bandwidth or 1.6 bits per second per Hz. It is a π/4 DQPSK based system and transmits two bits per symbol. The theoretical efficiency would be two bits per second per Hz and in practice it is 1.6 bits per second per Hz.Another example is a microwave digital radio using 16QAM. This kind of signal is more susceptible to noise and distortion than something simpler such as QPSK. This type of signal is usually sent over a direct line-of-sight microwave link or over a wire where there is very little noise and interference. In this microwave-digital-radio example the bit rate is 140 Mbits per second over a very wide bandwidth of 52.5 MHz. The spectral efficiency is 2.7 bits per second per Hz. To implement this, it takes a very clear line-of-sight transmission path and a precise and optimized high-power transceiver.。

无线通信英文版教学设计1. IntroductionWireless communication is the exchange of information between two or more devices without the use of cables or wires. Wireless communication is an essential part of modern life and has transformed the way we communicate. This course is designed to provide students with a solid foundation in wireless communication principles, practices, and technologies.2. Course ObjectivesThe objectives of this course are: - To introduce the fundamental principles of wireless communication. - To expln the different types of wireless communication systems and their applications. - To teach the basic concepts of radio frequency (RF) technology and wireless network architecture. - To discuss the various communication standards that govern wireless communication. - To provide hands-on experience in building wireless communication systems.3. Course OutlineThe course will cover the following topics:Week 1: Introduction to Wireless Communication•Overview of wireless communication•Types of wireless communication systems•Applications of wireless communicationWeek 2: Basic Concepts of Radio Frequency (RF) Technology•RF waves and signals•Modulation techniques•Demodulation techniquesWeek 3: Wireless Network Architecture•Wireless network topologies•Wireless access points and routers•Wireless network securityWeek 4: Wireless Communication Standards•IEEE 802.11 (Wi-Fi)•Bluetooth•Cellular networks (GSM, CDMA)Week 5: Building Wireless Communication Systems•Basic hardware components of a wireless communication system•Installing and configuring a wireless access point•Troubleshooting wireless network issues4. Teaching MethodologyThis course will be delivered through a combination of lectures, readings, assignments, and hands-on projects. Lectures will provide an introduction to the topic and cover the theoretical aspects of wireless communication. Readings will supplement the lectures and provide additional information on the course topics. Assignments will be given to evaluate the student’s understandin g of the course material. Hands-on projects will provide practical experience in building wireless communication systems.5. Assessment and GradingThe grade for this course will be based on the following components: Component WeightageAssignments 40%Hands-on Projects 30%Final Exam 30%6. References•Andreas F. Molisch,。

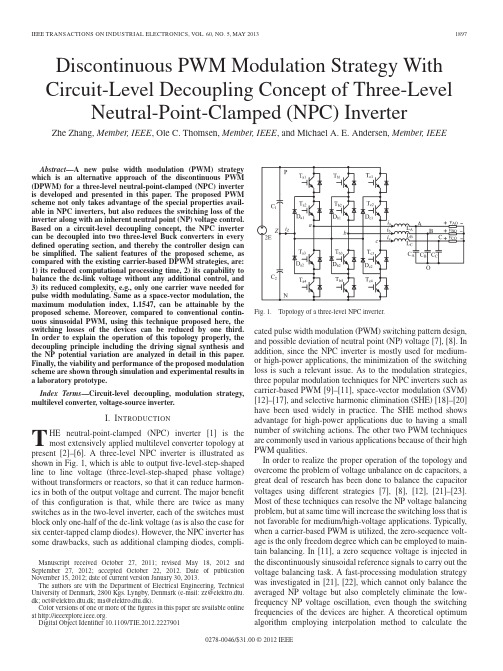

A Novel Drive Method for High-Speed BrushlessDC Motor Operating in a Wide RangeChenjun Cui,Gang Liu,and Kun WangAbstract—In this paper,a novel drive method,which is differ-ent from the traditional motor drive techniques,for high-speed brushless DC(BLDC)motor is proposed and verified by a series of experiments.It is well known that the BLDC motor can be driven by either pulse-width modulation(PWM)techniques with a constant dc-link voltage or pulse-amplitude modulation(PAM) techniques with an adjustable dc-link voltage.However,to our best knowledge,there is rare study providing a proper drive method for a high-speed BLDC motor with a large power over a wide speed range.Therefore,the detailed theoretical analysis comparison of the PWM control and the PAM control for high-speed BLDC motor isfirst given.Then,a conclusion that the PAM control is superior to the PWM control at high speed is obtained because of decreas-ing the commutation delay and high-frequency harmonic wave. Meanwhile,a new high-speed BLDC motor drive method based on the hybrid approach combining PWM and PAM is proposed. Finally,the feasibility and effectiveness of the performance analy-sis comparison and the new drive method are verified by several experiments.Index Terms—Brushless DC(BLDC)motor,commutation delay, drive method,high-speed,pulse-amplitude modulation(PAM).I.I NTRODUCTIONR ECENTLY,high-speed brushless DC(BLDC)motor, which is with the advantages of high efficiency,compact-ness,low cost,and maintenance compared with the traditional brush dc motor[1]–[3],is getting more and more interest in industrial automation area,especially on blowers and compres-sors.Because the rotation speed of high-speed motor can reach up to tens of thousands revolutions per minute(r/min)due to the development of bearing technology[4],[5],a proper drive method to ensure low loss and high efficiency in a wide speed range is a critical issue.Generally,the BLDC motor can be driven by either pulse-width modulation(PWM)or pulse-amplitude modulation (PAM)techniques.However,it is well known that the inverter, which is applied to most of the BLDC motor drive systems,Manuscript received March17,2014;revised June14,2014and August19, 2014;accepted October1,2014.Date of publication October8,2014;date of current version April15,2015.This work was supported in part by the National Nature Science Funds of China under Grant61374029and Grant61403015, and in part by the National Major Project for the Development and Applica-tion of Scientific Instrument Equipment of China under Grant2012YQ040235. Recommended for publication by Associate Editor P.C.Loh.(Corresponding author:G.Liu).C.Cui and K.Wang are with the School of Instrumentation Science and Optoelectronics Engineering,BeiHang University,Beijing100191,China (e-mail:cuichenjunupc@;wangkunggg@).G.Liu is with the School of Instrumentation Science and Optoelectronics Engineering,BeiHang University,Beijing100191,China(e-mail:lgang@buaa. ).Color versions of one or more of thefigures in this paper are available online at .Digital Object Identifier10.1109/TPEL.2014.2361752is controlled by the PWM scheme for varying the voltage. Moreover,the PWM control is extensively used in high-power/ low-power BLDC motor drives[6],[7],and the motor per-formance is decided by the commutation control techniques. The common PWM control contains six different PWM tech-niques namely,H-PWM-L-ON[8]–[10],H-ON-L-PWM[9]–[12],PWM-ON[13],[14],ON-PWM[15],H-PWM-L-PWM, and PWM-ON-PWM[16],[17],respectively.For example, when H-PWM-L-ON is employed,the high-side power device is controlled by the PWM chopper signal every consecutive120°in a fundamental period.Meanwhile,the low side of the same leg control signal is shifted by180°without the PWM chopper signal,as compared to its high-side one,to clamp the related inverter output to the negative dc-link rail.The control signals for the other two legs are shifted by120°and240°,respectively. Unfortunately,the PWM techniques can induce serious cur-rent and torque ripples for the ironless stator motor that will tend to very low inductance[18].Moreover,the high-frequency and large-range current ripple will inevitably increase the copper and iron losses[18],[19]at high speed.The assessment of the aforementioned PWM techniques for the BLDC motor drives at low speed is given in[20].The criteria for assessment include the drive circuit,reversal dc-link current,circulating current of thefloating phase,and back electromotive force(back-EMF)de-tection.In addition,the advantages and disadvantages of these PWM techniques for the BLDC motor drives are analyzed by several experimental results.A comprehensive analysis on the generated torque ripples of trapezoidal back-EMF due to the phase commutation in the six-switch three-phase inverter BLDC drives is proposed in[21].The consultation that the PWM-ON pattern achieves the smallest torque ripple due to the current commutation is also given.The performances of the PWM tech-niques at low speed are compared in the efficiency,reliability, torque ripple,EMC,and vibration[16]through the theoreti-cal analysis and simulation verification.It is shown that the PWM_ON_PWM method is superior to the other PWM meth-ods.A novel PWM technique is introduced in[22]to reduce the motor loss,but only suits for the motor with very small power. In summary,the aforementioned studies are all based on the low-speed operations instead of the high-speed performance. Moreover,there are no detailed analyses about the performance improvement.The PAM control is another popular control method for the BLDC motor.For PAM control,120°commutation control,i.e., the so-called six-step mode is generally used and the dc-link voltage can be adjusted according to the error between the speed and its reference.It is shown that the PAM control is superior to the PWM control[23].Due to the PWM period0885-8993©2014IEEE.Personal use is permitted,but republication/redistribution requires IEEE permission.See /publications standards/publications/rights/index.html for more information.interruption caused by the commutation and limitation of the res-olution of PWM generator,more torque ripple can be produced in the performance of PWM-controlled BLDC motor drives. This phenomenon will become more serious when the motors work at high speed.Moreover,it will lead to high motor loss. But it does not give enough theoretical analysis.The advantages and disadvantages of PWM and PAM are assessed in[24]using BLDC motor drives which are applied to the refrigerator.The result shows that the PAM control can provide higher efficiency than the PWM control.However,it only gives several low-power experimental results without any detailed analysis.A so-called PAM/PWM method[25]is proposed to control the adjustable speed drives.The realization of PAM relies on a current source rectifier which adjusts the dc-link voltage.As compared to the conventional PWM inverter with a constant dc-link voltage,this method can reduce the dc-link current ripples and prolong the lifetime of the capacitor effectively.However,the performance of controlling a BLDC motor is not involved.In order to improve the motor efficiency and provide the desired current waveform, a quasi-current source inverter is employed in[26]to adjust the dc-link voltage.The high-speed performance is improved,but the analysis and performance comparison with the PWM con-trol are not mentioned.A PWM-controlled buck-type dc-to-dc power converter in front of the three-phase bridge inverter is employed for the low-inductance and low-power BLDC mo-tor[27]–[29].The variable dc voltage is adjusted by the buck converter,and the inverter legs participate only in commutation instead of involved in modulation.But the detailed analysis is not discussed although the power consumption is reduced.To the best knowledge of the authors,the detailed analysis of whether the PWM control is suitable for the high-speed BLDC motor in a large speed range or not has not been fully inves-tigated.Therefore,it attracts the authors to give the analysis and performance comparison between the PWM control and the PAM control at high-speed region,thus providing a proper drive method in a wide speed range.In this paper,the theoretical analysis comparison between the PWM control and the PAM control at high-speed region isfirst given.Then,a new BLDC motor drive method over a wide speed range based on the analysis results is proposed.Therefore,the organization of this paper is as follows.Section II describes the detailed analysis about the advantages and disadvantages of the PWM control and the PAM control.Section III presents the new high-speed BLDC motor drive method.Section IV introduces the experimental results to validate the effectiveness and feasi-bility of the performance comparison analysis and the new drive method.Some important conclusions can be found in Section V.II.P ERFORMANCE A NALYSIS C OMPARISON B ETWEEN THE PWM C ONTROL AND THE PAM C ONTROLThe criteria of the performance comparison include the com-mutation delay analysis,harmonic component analysis,and mo-tor power factor analysis.mutation Delay AnalysisIn this paper,TI TMS320F28335digital signal processor (DSP)is taken as the controller to generate the PWMsignals.Fig.1.Scheme of the PWM generator based on the DSP.The frequency of PWM events is controlled by the time-base period(TBPRD)register and the mode of the time-base counter. The time-base counter has three modes of operation selected by the time-base control register,i.e.,up-down-count mode,up-count mode,and down-count mode.The up-down-count mode is selected to generate the triangu-lar carrier as shown in Fig.1.In this mode,the time-base counter starts from zero and increments until the period(TBPRD)value is reached.When the period value is reached,the time-base counter will decrement until it reaches zero.At this point, the counter repeats the pattern and begins to increment.When the time-base counter value is increasing to the counter-compare value,the output signal will be active high.On the contrary, when the time-base counter value is decreasing to the counter-compare value,the output signal will be active low.In the BLDC motor control system,if the PWM control is selected,the period value and the PWM period will be constant. The speed adjustment is achieved by changing the counter-compare value(counter-compare A/B register)to modulate the pulse width,i.e.,the duty ratio D.If a high-speed is needed,a large counter-compare value will be set to increase the output voltage.On the other hand,if a low speed is needed,a small counter-compare value will be set to decrease the output voltage. However,it is noted that if a new counter-compare value is written,the new value will not work immediately.Because the new value will befirst written to the shadow register associated with the counter-compare A/B register.Only when the counter value reaches zero,the new value will be loaded into the counter-compare A/B register from the shadow register.Assuming at a particular commutation process that the current transfers from phase C to phase A.This transfer is performed by switching OFF VT2and switching ON VT4.Before the transfer, VT3is ON and VT2is controlled by the chopper signal.When a commutation signal interruption occurs at t2as shown in Fig.1, theoretically,VT2should be turned OFF and VT4should be turned ON simultaneously.However,because the new counter value cannot work immediately until t4,the ideal conduction signal of VT4as shown in the dashed line of Fig.1cannot besatisfied.If the new counter-compare is loaded at t4,the counter starts from zero and increments until the new counter-compare value at t5when the actual conduction signal of VT4works and VT4is ON.Therefore,there is a lag time deviationΔt between the ideal conduction signal and the actual conduction signal, which can be expressed asΔt=t5−t2.(1) The lag angleδcaused byΔt can be expressed asδ=360T k·Δt(2)where T k is the electrical period of the motor.From(2),we can see that if the speed is low,δwill be very small and negligible due toΔt<T s<<T k(T s is the PWM period).However,if the speed is too high to ensure T s<T k,δwill be large enough becauseΔt may be close to the PWM period T k which is the same order of magnitude with T s.For example,for a motor with two pole pairs,if it runs at30000 r/min with a10k carrier frequency,T k will be1ms(T k=1/ 1000Hz)andδmay be close to36°.The largeδwill result in a large commutation delay.Even though this commutation delay can be neglected for a medium speed range,it has a significant influence on the phase current and drive performance at high speed,since the60°interval in which the commutation arises is relatively small.Moreover,the large lag angleδwill increase the motor loss and decrease the motor efficiency[29].In Fig.1,assuming that a commutation signal interruption occurs in the interval(t1,t4],we can also see that if the inter-ruption near t1,the largeΔt will lead to a largeδ,while if the interruption near t4,the smallΔt will lead to a smallδ.More-over,δis variable because the commutation signal interruption time varies with the speed.However,if the PAM control is employed,the PWM chopper signal will be no longer needed,sinceδcan be eliminated by set-ting the PWM generator port as the general-purpose input/output (I/O)port.When a commutation signal interruption occurs,the associated(I/O)port will immediately output a high/low level to turn ON/OFF the power device without delay.B.Harmonic Component AnalysisIn this paper,the adopted drive circuit structure for high-speed BLDC motor control is shown in Fig.2.For facilitate analysis,only the fundamental waves of the back-EMFs are considered,which can be expressed as⎧⎪⎨⎪⎩e Af=√2E sin(ωt)=E max sin(ωt)e Bf=√2E sin(ωt−2π/3)=E max sin(ωt−2π/3)e Cf=√2E sin(ωt+2π/3)=E max sin(ωt+2π/3)(3)where e Af,e Bf,and e Cf are the fundamental waves of the back-EMFs,E is the virtual value of the fundamental wave,E max=√2E is the maximum value of the fundamentalwave.Fig.2.Adopted drive circuit structure for high-speed BLDC motor control. u d is the output voltage of the rectifier,e A,e B,and e C are the back-EMFs, R is the phase-winding resistance,L is the phase-winding inductance,“N”is the neutral point,“S”is the virtual neutral point,“O”is the midpoint of the dc bus,and the voltage betwee n“S”and“O”is used to generated the sensorless commutation signals[30].Fig.3.Scheme of the PWM generator.Also,the fundamental waves of the line-to-line back-EMFs can be obtained as⎧⎪⎨⎪⎩e ABf=√6E sin(ωt+π/6)=√3E max sin(ωt+π/6)e BCf=√6E sin(ωt−π/2)=√3E max sin(ωt−π/2)e CAf=√6E sin(ωt+5π/6)=√3E max sin(ωt+5π/6)(4) where e ABf,e BCf,and e CAf are the fundamental waves of the line-to-line back-EMFs.For PWM control,the line-to-line voltages are modulated by the chopper signals.In this paper,u AB is taken as an example to be analyzed,and its fundamental wave can be expressed asu ABf=MU max sin(ωt+θ)(5)where u ABf is the fundamental wave of u AB,U max is the max-imum value of u ABf,0≤M≤1is the modulation ratio,andθis the angle between u ABf and e Af.The scheme of the PWM generator is shown in Fig.3,where α1andα2can be described as⎧⎪⎪⎨⎪⎪⎩α1=−π2−Mπsin(ωt+θ)2α2=π2+Mπsin(ωt+θ)2.(6)From Fig.3,u AO can be obtained by the Fourier decomposi-tion asu AO=u d2M sin(ωt+θ)+∞n=14nπ×sinMnπ2sin(ωt+θ)+nπ2cos(nωs t)(7)whereωs is the carrier angular frequency. Also,u BO can be obtained asu BO=u d2M sinωt−2π3+θ+∞n=14nπ×sinMnπ2sinωt−2π3+θ+nπ2cos(nωs t).(8)Therefore,u AB can be expressed asu AB=u AO−u BO=u ABf+u ABh(9) where u ABf and u ABh are the fundamental wave and the har-monic wave of u AB,respectively.From(7)–(9),u ABf and u ABh can be described asu ABf=u d2M sin(ωt+θ)−M sinωt−23π+θ=√32Mu d sinωt+θ+16π(10)u ABh=⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩u d2∞n=1(−1)(n+1)/24nπ∞k=2J kMnπ2×2sinkπ3sin(kω±nωs)t+kθ−π3(n=1,3,5,...,k=2,4,6,...,)u d2∞n=2(−1)n/24nπ∞k=1J kMnπ2×2sinkπ3cos(kω±nωs)t+kθ−π3(k=1,3,5,...,n=2,4,6,...,)(11)where J k is the k-order Bessel function.From(11),we can see that the harmonic waves with the frequency of kω±nωs are introduced because of the PWM control.The equivalent circuit of the fundamental wave and the har-monic wave are shown in Fig.4(a)and(b),respectively.It can be seen that the distorted voltage u ABh will induce the distorted current i ABh,which will inevitably increase the copper loss of the motor.It is well known that the iron loss of the motor also increases with the frequency.Therefore,the harmonic wave will increase both the copper loss and the iron loss.C.Motor Power Factor AnalysisThe vector diagram illustrating the relationship between u AB and i AB(i AB=i A)after the transfer is shown in Fig.5.Fig.4.Equivalent circuit of the fundamental wave and the harmonic wave.(a)Fundamental wave equivalent circuit.(b)Harmonic wave equivalentcircuit. Fig.5.Vector diagram about the relationship between u A B and i A B after thetransfer.Generally,the power factor of the fundamental component, i.e.,the displacement factor,can be obtained from the angle between U AB and I AB as shown in Fig.5and expressed asγ=cosψ1(12) whereγis the displacement factor andψ1is the displacement factor angle.However,if the PWM control is employed,the actual current I AB will lag the ideal current I AB of aboutδelectrical degrees due to the lag angle mentioned above.Therefore,the actual displacement factor angle equalsψ1+δ,and the displacement factor can be expressed asγ=cos(ψ1+δ).(13) It is obvious that the PWM control decreases the displacement factor.In addition,we should note that(12)and(13)are only asso-ciated with the fundamental component.If the harmonics wave is considered,the motor power factor can be expressed as PF=PS=U1I1cosΦ1+nh=2U h I h cosΦhUI(14) where PF is the power factor,P is the active power,S is the ap-parent power,andΦ1=ψ1+δis the displacement factor angle. U is the RMS magnitude of the line-to-line voltage and U1is the RMS magnitude of the fundamental component,I is the RMS magnitude of the total current and I1is the RMS magnitude of the fundamental component,U h is the RMS magnitude of the line-to-line voltage harmonic component and I h is the RMS magnitude of the current harmonic component,andΦh is the angle between U h and I h.TABLE IM OTOR P ARAMETERSSurface Mounted BLDC MotorRated DC voltage480VRated current218ARated speed,n32000r/minNumber of pole pairs,P2Phase resistance,R 1.5mΩPhase inductance,L0.053mHLine-to-line back-EMF constant,K e-l i n e0.0127V/r/minMoment of inertia,J0.024059kg·m2mon drive circuit structure for the BLDC motor control.Thefirst term,i.e.,U1I1cosΦ1,shows the main power term, which is associated with the fundamental frequency.The second (summation)term accounts for the harmonics powers absorbed by the loads and other system components.Because of the PWM control,the lag angleδand the harmonic component decrease the power factor.It is well known that when the active power is constant,the small power factor will increase the reactive power,apparent power,and motor loss.III.P ROPOSED D RIVE M ETHODA.Drive Circuit Selection of High-Speed BLDC MotorAs analyzed above,the PAM control for the BLDC motor can provide less motor loss and higher efficiency than the PWM control at high speed.So the PAM control should be employed, especially at high speed.However,from the specification of the experimental BLDC motor as shown in Table I,it is interesting tofind that the phase-winding resistance and the phase-winding inductance of high-speed BLDC motor are far smaller than those of the common low-speed BLDC motor.When the motor starts, the initial DC voltage of the three-phase inverter should be smaller enough to limit the startup current,as the back-EMF is too small to counteract a large dc voltage at the very low speed.Therefore,a suitable drive circuit should befirst selected to reduce the initial dc voltage and guarantee the safe motor starting process.During the experimental process,the authors have tried three drive circuit structures to limit the startup current as shown in Figs.2,6,and7.Fig.6shows the common drive circuit structure for the BLDC motor control.The dc voltage,i.e.,the output voltage of the three-phase uncontrolled rectifier,is more than500V.Though the three-phase inverter is controlled by the PWM scheme for reducing the voltage,the startup current is still far larger thanthe Fig.7.Drive circuit structure based on the dc–dc converter for the BLDC motor control.rated current.Moreover,the inverter cannot work anymore,as the protection circuit blocks the inverter due to the large current. So this common circuit structure is not employed.Fig.7shows the drive circuit structure based on a front-end PWM-controlled dc–dc converter.A buck converter is taken to reduce the dc voltage of the three-phase inverter.Moreover, the motor starts normally.Unfortunately,the buck converter in-creases the complexity mainly due to the dc inductance,L B,as marked in Fig.7.Let us assume that the working frequency of the buck converter is6kHz.As the rated power of the exper-imental motor is up to100kW,the normal dc currentflowing through L B may be more than250A which will cause the bulky size and weight as shown in Fig.7.Moreover,the bulky L B will increase the difficulty of the whole circuit layout design because the unreasonable layout will induce strong electromagnetic in-terference,which may affect the normal operation of high-speed and high-power BLDC motor.Finally,taking into account the subsequent PAM control and the disadvantages of the above-mentioned circuit structures,a motor drive circuit as shown in Fig.2is employed in this pa-per.The front-end phase-controlled rectifier can provide an ad-justable dc-link voltage to limit the startup current and achieve the PAM control,while the back-end three-phase inverter can achieve the commutation control.B.Proposed Drive MethodIn order to satisfy the commutation control of high-speed BLDC motor in a wide speed range and improve the motor ef-ficiency,a hybrid drive method combining PWM and PAM is proposed.When the motor runs at low speed,the PWM control is adopted with afixed dc-link voltage.With the motor accel-erating,the back-EMF will increase with the speed.When the motor speed reaches a threshold value,i.e.,the enough back-EMF can counteract the dc-link voltage,the PAM control works with an adjustable dc-link voltage.It should be noted that though the PAM control for the BLDC motor is superior to the PWM control,the PAM control is not employed in the whole speed range for the following two reasons.Thefirst one is that the larger dc-link voltagefluctuation of the rectifier limits its application at low and medium speed. Moreover,at low speed,it may be unable to produce a small enough dc voltage to achieve the PAM control due to the smallFig.8.Hysteresis loop schematic diagram.phase-winding resistance and phase-winding inductance.There-fore,if we want to take the PAM control in a wide speed range, the range of dc-link voltage should be expanded at medium and low speed.Meanwhile,a front-end PWM-controlled dc–dc con-verter as shown in Fig.7is needed to produce such a low dc voltage.But the complexity of the system design is increased as explained above.The second one is that,to our best knowledge,the PWM control is the auxiliary drive method of high-speed BLDC motor, while the PAM control is the main drive method,since the high-speed region is the most common working range.The aim of the PWM control is merely to guarantee that the high-speed motor can be accelerated to a high speed.Therefore,the operation time of the PWM control is far shorter than that of the PAM control, thus mitigating the disadvantage of the PWM control.However, both the two drive methods are indispensable.The transition process between PWM and PAM is achieved by a hysteresis comparator expressed asτ(n(k+1))=⎧⎪⎨⎪⎩1,(n(k+1)>n+)τ(n(k)),(n−≤n(k+1)≤n+)0,(n(k+1)<n−)(15)whereτ(n(k+1))is the(k+1)th hysteresis comparator out-put value,τ(n(k))is the(k)th hysteresis comparator output value, n−and n+are the two endpoint speeds of the hysteresis com-parator,n(k+1)is the(k+1)th calculated speed value,and n(k)is the(k)th calculated speed value.The hysteresis loop schematic diagram is shown in Fig.8.The region between n−and n+is defined as the transition region. Ifτ(n(k+1))=1,the PAM control mode will start to work, while ifτ(n(k+1))=0,the PWM control mode will start to work.C.Calculation Principle for n+From Fig.2,we can obtain⎧⎪⎨⎪⎩u AN=Ri A+Ldi A/dt+e Au BN=Ri B+Ldi B/dt+e Bu CN=Ri C+Ldi C/dt+e C(16)where u AN,u BN,and u CN are the three phase voltages.Let us assume that VT1and VT6are switched ON,i.e., phases A and B are conducted simultaneously with i A=−i B and i C=0.So the equivalent circuit can be shown in Fig.9.Fig.9.Equivalent circuit when VT1and VT6are switchedON.Fig.10.Experimental platform.(a)Control system.(b)Experimental motors.From Fig.9,the line-to-line voltage can be obtained asu d(0)=u AB=2Ri A+2Ldi A/dt+e ABe AB=k e-line n+(17)where u d(0)is the initial voltage of the rectifier,i.e.,thefixed dc-link voltage when the PWM control works,and k e-line is the line-to-line back-EMF constant.Therefore,we can obtain the online result of n+by solving (17).In this paper,n+is about10000r/min.Meanwhile,n−can be obtained as n−=n+−Δn(Δn is the hysteresis width).D.Calculation Principle forΔnThe motor torque balance equation of the BLDC motor can be obtained asT M−T Z=JdΩdt=2π60Jdndt(18) where T M is the electromagnetic torque,T Z is the load torque, J is the moment of inertia,andΩis the mechanical angular velocity of the motor.Generally,for a BLDC motor,T M can be expressed asT M=(e A i A+e B i B+e C i C)/Ω=60(e A i A+e B i B+e C i C)/(2πn).(19) Considering(17),i A=−i B,and i C=0,we can also obtain T M asT M=60i A(u AB−2Ri A−Ldi A/dt)/(2πn).(20) It can be deduced from[29]that the commutation delay in-duced by the PWM control will lead to a serious torque ripple. So when the drive method transfers from the PWM control to the PAM control,a torque ripple,ΔT M,will be introduced,and (18)can be expressed asT M+ΔT M−T Z=JdΩdt=2π60Jdndt.(21)Fig.11.Waveform of i A and u A B at different speeds.(a)PWM n=6000r/min.(b)PWM n=24000r/min.(c)PAM n=24000r/min. From(21),we canfind that ifΔT M>0,the speed willincrease,while ifΔT M<0,the speed will decrease.Unfortu-nately,ΔT M is uncertain during the transition.It can be seenfrom Fig.8that when the speed reaches n+,if the speed is decel-erating,the drive method may switch between the PAM controland the PWM control repetitiously which aggravates the cur-rent ripple.Therefore,a proper hysteresis width is critical toeliminate the unexpected repetitious switching.The proper hysteresis width is selected from many initial ex-periments,of which accelerate and decelerate the motor to passthe transition region with different hysteresis widths automat-ically,when the motorfirst runs.OnceΔn is selected,it willbe saved and does not need to be calculated in the subsequentexperiments.Considering(21),Δn can be obtained asΔn=λΔt·dndt+λ1Δn1=λΔt·602πJ×(T M+ΔT M−T Z)+λ1Δn1(22) whereλ=1.5−2is the experiential safety factor of the speed fluctuation during the transition,Δt=T s/6is the commutation interval,T M is the electromagnetic torque that can be obtained from(20),ΔT M=−(1−2)T Z is a experiential worst torque ripple that the motor can endure,λ1=1.2−1.5is the experi-ential rate accuracy safety factor,andΔn1=(1−3%)n+is the rate accuracy.In this paper,Δn is set500r/min according to(22).IV.E XPERIMENTAL E V ALUATIONA.Experiment SetupThe experiment about the performance analysis comparison and the proposed drive method has been successfully imple-mented on the experimental high-speed magnetically suspended BLDC motor that coupled to a magnetically suspended gener-ator by aflexible coupling.A variable resistance is taken as the load.The specification of the experimental BLDC motor is shown in Table I,while the experimental platform is shown in mutation Delay ValidationFig.11(a)shows the waveform of i A and u AB at6000r/min under PWM control with the dc voltage equal to450V,while Fig.11(b)shows that at24000r/min under PWM control.As explained above,the PWM control will lead to a commutation delay.Moreover,although this commutation delay can be ne-glected in a medium speed range,it has a significant influence on the phase current and the drive performance at high speed. When the speed is low as shown in Fig.11(a),the commuta-tion delay is unconspicuous.However,when the speed is high as shown in Fig.11(b),the commutation delay is so obvious that i A and u AB are seriously distorted.It is well in accord with the operation given in[31]–[33]when the lagged commu-tation occurs.Fig.11(c)shows the operation at24000r/min with PAM control.It can be seen that the commutation delay is eliminated and the distortion of i A and u AB is improved greatly.C.Harmonic Content ValidationFig.12shows the spectrum map comparison of i A and u AB between the PAM control and the PWM control at different speeds.Fig.12(a)and(b)shows the spectrums at12000r/min. We can see that the harmonic component under PWM control is larger than that under PAM control.The THD of i A decreases from1.245to0.663,while that of u AB decreases from1.955 to0.679.Meanwhile,Fig.12(c)and(d)shows the spectrums at20000r/min.Also,the harmonic component under PWM control is serious.We can alsofind from these fourfigures that when the PWM control is employed,the THD will decreases at high speed.To our best knowledge,this is because that the duty ratio can be maintained at higher level at high speed with the same generator load resistor.However,the improvement of THD is more insignificant than that under PAM control.Fig.12(e) and(f)shows the spectrums at24000r/pared with the conditions at12000and20000r/min,the load is heavy due to the high speed.Nevertheless,the PAM control can still decrease the harmonic content greatly.In addition,it is noted that the THD under PAM control at20000r/min is lower than that at24000r/min.Therefore,for PAM control,the THD is not decreased with speed.The relationship between the THD and the speed under PAM control needs further research.。