CMOS放大器频率特性仿真实验报告

- 格式:doc

- 大小:2.33 MB

- 文档页数:6

CMOS放大器设计实验报告一、实验目的1.培养学生分析、解决问题的综合能力;2.熟悉计算机进行集成电路辅助设计的流程;3.学会适应cadence设计工具;4.掌握模拟电路仿真方法6.掌握电子电路、电子芯片底层版图设计原则和方法;7.掌握使用计算机对电路、电子器件进行参数提取及功能模拟的过程;8.熟悉设计验证流程和方法。

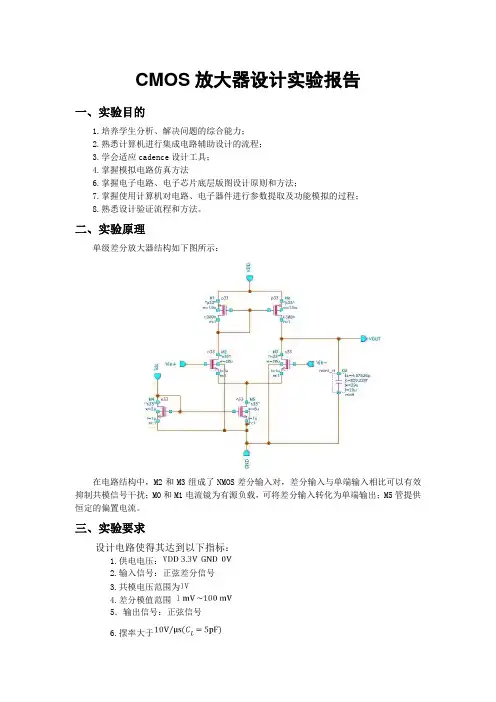

二、实验原理单级差分放大器结构如下图所示:在电路结构中,M2和M3组成了NMOS差分输入对,差分输入与单端输入相比可以有效抑制共模信号干扰;M0和M1电流镜为有源负载,可将差分输入转化为单端输出;M5管提供恒定的偏置电流。

三、实验要求设计电路使得其达到以下指标:1.供电电压:2.输入信号:正弦差分信号3.共模电压范围为4.差分模值范围5.输出信号:正弦信号6.摆率大于7.带宽大于8.幅值增益:9.相位裕度:10.功耗:11.工作温度:四、差分放大器分析1、直流分析为了使电路正常工作,电路中的MOS管都应处于饱和状态。

1.1 M2管的饱和条件:1.2 M4管的饱和条件:2.小信号分析小信号模型如下:由图可得:2.1 增益分析其中2.2 频率响应分析由小信号模型易知:其中3.电路参数计算3.1确定电流根据摆率指标:根据功耗指标易知:根据带宽指标:综上,取:3.2宽长比的确定M4与M5:电流源提供的电流为,参数设为,根据电流镜原理,可以算出M2与M3:带入数据可得取值为20,则取M0与M1:这两个PMOS管对交流性能影响不大,只要使其下方的管子正常开启即可,实验中取值:五、仿真结果1、幅频特性信号名称信号类型参数VDD 直流V=3.3VGND 直流V=0VVin+ 交流小信号幅值1mV,频率50KHz 直流电压1.65V,初相0Vin- 交流小信号幅值1mV,频率50KHz 电压1.65V,初相180增益,,相位裕度为,满足指标要求。

2、摆率仿真信号名称信号类型参数VDD 直流V=3.3VGND 直流V=0VV1=0V,V2=3.3V Vin+ 方波周期2,占空比50%V1=3.3V,V2=0V Vin- 方波周期2,占空比50%仿真结果如下:得到:满足指标要求。

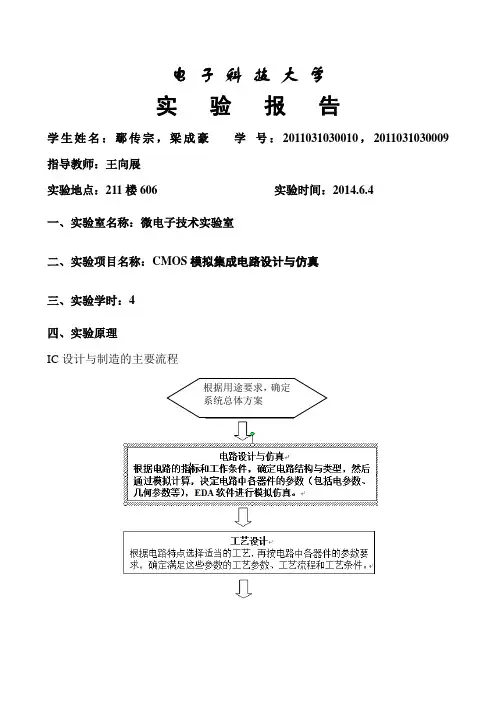

电子科技大学实验报告学生姓名:鄢传宗,梁成豪学号:2011031030010,2011031030009 指导教师:王向展实验地点:211楼606 实验时间:2014.6.4一、实验室名称:微电子技术实验室二、实验项目名称:CMOS模拟集成电路设计与仿真三、实验学时:4四、实验原理IC设计与制造的主要流程五、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:∙根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

∙学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

六、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、设计一个运算放大器电路,要求其增益大于40dB, 相位裕度大于60º,功耗小于10mW。

3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。

4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。

5、电路性能的优化与器件参数调试,要求达到预定的技术指标。

6、整理仿真数据与曲线图表,撰写并提交实验报告。

七、实验仪器设备(1)工作站或微机终端一台(2)局域网(3)EDA仿真软件 1套八、实验步骤1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。

2、根据设计指标要求,设计出如下图所示的电路结构。

并进行计算分析,确定其中各器件的参数。

调用Symbol生成命令,生成符号如下图。

3、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分析的参数设置方法。

电源电压设置:输入信号设置:建立时间测试信号设置:4、电路性能的优化与器件参数调试,要求达到预定的技术指标。

模拟CMOS集成电路设计研究生课程实验报告一、概述在现代集成电路设计领域,模拟CMOS集成电路设计一直是一个备受关注的课题。

本实验旨在通过对模拟CMOS集成电路设计相关内容的学习和实践,加深对该领域的理解,并提升设计实践能力。

本文将介绍实验内容、实验过程和实验结果,并结合个人观点对模拟CMOS集成电路设计进行探讨。

二、实验内容1. 实验名称:基于CMOS工艺的运算放大器设计与仿真2. 实验目的:通过对基本运算放大器的设计与仿真,理解模拟CMOS 集成电路设计的基本原理和方法。

3. 实验要求:设计一个基于CMOS工艺的运算放大器电路,并进行仿真验证。

4. 实验器材与软件:PSPICE仿真软件、计算机、基本电路元件。

三、实验过程1. 设计基本运算放大器电路a. 根据理论知识,选择合适的CMOS工艺器件,并进行电路拓扑设计。

b. 计算电路的主要参数,如增益、带宽、输入输出阻抗等。

c. 优化设计,满足实际应用需求。

2. 运算放大器电路仿真a. 在PSPICE软件中建立电路模型。

b. 分析仿真结果,验证设计参数是否符合预期。

c. 优化设计,使得电路性能达到最佳状态。

四、实验结果经过反复设计与仿真,最终得到了一个基于CMOS工艺的运算放大器电路。

在PSPICE软件中进行仿真测试,结果表明设计的运算放大器电路性能良好,能够满足设计要求。

在输入端加入正弦波信号,输出端得到经过放大和处理的信号,验证了电路的正常工作。

五、总结与回顾通过本次实验,我深刻理解了模拟CMOS集成电路设计的基本原理和方法。

从初步设计到最终仿真,我逐步掌握了电路设计与优化的过程,并将理论知识应用到实践中。

在今后的学习和工作中,我将继续深入研究模拟CMOS集成电路设计,不断提升自己的技能。

六、个人观点与理解模拟CMOS集成电路设计是一个复杂而又具有挑战性的领域。

在实验过程中,我深刻意识到了理论知识与实际应用的紧密通联,只有不断实践与探索,才能够更好地理解与掌握。

CMOS高性能运算放大器探究与设计引言:随着科技的不息进步和应用的广泛推广,运算放大器(Operational Amplifier,简称Op-Amp)作为一种重要的模拟电路器件,得到了广泛的关注和应用。

CMOS (Complementary Metal-Oxide-Semiconductor)技术由于其功耗低、集成度高等优势,被广泛应用于运算放大器的探究和设计中。

本文将介绍CMOS高性能运算放大器的探究与设计,主要包括运算放大器的基本原理、运算放大器的基本电路结构、CMOS技术的特点和优势、CMOS高性能运算放大器的设计方法和优化技术等方面。

一、运算放大器的基本原理运算放大器是一种特殊的差动放大器,它能够实现电压放大、电流放大、功率放大等功能。

运算放大器有两个输入端,一个非反相输入端和一个反相输入端;有一个输出端和一个电源端,电源端一般有正电源和负电源两个。

在抱负状况下,运算放大器具有无限的增益、无限的输入阻抗和零的输出阻抗。

但实际状况下,由于运算放大器的内部结构等因素的限制,无法完全满足抱负的条件。

因此,在运算放大器的设计中,需要思量如何提高增益、输入阻抗和输出阻抗等性能指标。

二、运算放大器的基本电路结构运算放大器的基本电路结构由差动放大器、电压放大器和输出级组成。

差动放大器用于实现输入信号的差分放大,电压放大器用于实现信号的放大,输出级用于驱动负载电阻。

差动放大器由两个晶体管组成,一个晶体管作为非反相输入端,另一个晶体管作为反相输入端。

通过调整两个晶体管的尺寸比例,可以实现不同的放大倍数。

电压放大器由级联的共源放大器组成,通过逐级放大,实现信号的放大。

输出级由差分放大器和输出级筛选电路组成,通过差分放大器将信号转化为可驱动负载电阻的电流信号,再经过输出级筛选电路,将电流信号转化为电压信号。

三、CMOS技术的特点和优势CMOS技术是一种基于金属-氧化物-半导体(MOS)结构的半导体制造技术。

与传统的bipolar技术相比,CMOS技术具有以下特点和优势:(1)功耗低:CMOS电路在静态状态下几乎不消耗电流,功耗分外低,适合于低功耗应用的场合。

模拟CMOS集成电路设计课程设计报告--------二级运算放大器的设计信息科学技术学院电子与科学技术系一、概述:运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二、设计任务:设计一个二级运算放大器,使其满足下列设计指标:工艺Smic40nm电源电压 1.1v负载100fF电容增益20dB 至少40dB3dB带宽20MHz输入小信号幅度5uV 共模电平自己选取输出共模电平自己选取电路结构两级放大器相位裕度60~70度功耗无要求三、电路分析:1.电路结构:最基本的二级运算放大器如下图所示,主要包括四部分:第一级放大电路、第二级放大电路、偏置电路和相位补偿电路。

2.电路描述:输入级放大电路由PM2、PM0、PM1和NM0、NM1组成。

PM0和PM1构成差分输入对,使用差分对可以有效地抑制共模信号干扰;NM0和NM1构成电流镜作为有源负载;PM2作为恒流源为放大器第一级提供恒定的偏置电流。

第二级放大电路由NM2和PM3构成。

NM2为共源放大器;PM3为恒流源作负载。

相位补偿电路由电阻R0和电容C0构成,跨接在第二级输入输出之间,构成RC米勒补偿。

此外从电流电压转换角度来看,PM0和PM1为第一级差分跨导级,将差分输入电压转换为差分电流。

NM0和NM1为第一级负载,将差模电流恢复为差模电压。

NM2为第二级跨导级,将差分电压信号转换为电流,而PM3再次将电流信号转换成电压信号输出。

偏置电压由V0和V2给出。

3.静态特性对第一级放大电路:构成差分对的PM0和PM1完全对称,故有G m1=g mp0=g mp1 (1)第一级输出电阻R out1=r op1||r on1 (2)则第一级电压增益A1=G m1Rout1=g mp0,1(r op1||r on1) (3) 对第二级放大电路:电压增益A2=G m2R out2= -g mn2(r on2||r op3) (4) 故总的直流开环电压增益A0=A1A2= -g mp0,1g mn2(r op1||r on1)(r on2||r op3) (5)由于所有的管子都工作在饱和区,所以对于gm 我们可以用公式 g m =D I L W )/(Cox 2μ (6) 进行计算;而电阻r o 可由下式计算 r o =DI 1λ (7)其中λ为沟道长度调制系数且λ∝1/L 。

南通大学电子信息学院模拟CMOS集成电路设计报告书班级学号姓名指导教师共源级放大器一.实验目的共源极放大器的特征为电压增益与电流增益大,其缺点为频宽过窄。

我们以实验探索共源级放大器的电压增益及电流增益及频宽,包括小信号电路分析。

二.实验内容如图,共源级放大器中若含有R S电阻,则此电路会形成串反馈形成,增益下降,但是频宽会增加。

V thn =0.55V,U n C ox =143ua/v2,R O=100kΩ,g m=1.136356(mA/V),试求其电压增益与频宽。

计算过程:R G=R1||R2=12.453kΩR P=R D||R L=4.2kΩV o=-G m V G S×(R O||R P)Vo/V GS=-G m×(R O||R P)Vo/V in =-G m R S /(R S + R G) (R O||R P)三.实验过程程序:.OPTIONS POST=2 LIST.MODEL MN NMOS(LEVEL=1 KP=40u GAMMA=0.5+ PHI=0.6 VTO=1 LAMBDA=0.02)M1 3 1 vss vss MN W=20U L=2URD vdd 3 6kR1 vdd 1 33kR2 1 vss 20kRL gnd vo 14kRS vin 2 1kCS 2 1 100UCL 3 vo 100Uvdd vdd gnd dc 3.3vvss gnd vss dc 0vvin vin gnd ac 1 sin(1.2453 1M 1k).tran 10u 2m.ac dec 10 100 1g.Print tran I(RL) I(RD) I(R1).probe vdb(vo).end四.实验结果Hspice模拟结果:1、输入输出电压波形2、输入输出电流波形,此输出电流为短路电流3、频率特性利用上述的公式可得电压增益,电流增益。

将图形线性转换成LOG刻度的波形(鼠标右击Frequency,选择log)得波形如图:差动放大器一、实验目的有源负载差动放大器具有电压增益大,使用面积小的特性。

cmos实验报告CMOS 实验报告一、实验目的本次实验的主要目的是深入了解互补金属氧化物半导体(CMOS)的工作原理和特性,通过实际操作和测量,掌握 CMOS 电路的基本性能参数和测试方法,为今后在电子电路设计和应用方面打下坚实的基础。

二、实验原理(一)CMOS 简介CMOS 是一种集成电路制造工艺,它由 P 型和 N 型 MOS 晶体管组成。

CMOS 电路具有低功耗、高集成度、抗干扰能力强等优点,广泛应用于数字电路、模拟电路和混合信号电路中。

(二)CMOS 反相器CMOS 反相器是 CMOS 电路中最基本的单元,它由一个 P 型 MOS 晶体管(PMOS)和一个 N 型 MOS 晶体管(NMOS)组成。

当输入为高电平时,NMOS 导通,PMOS 截止,输出为低电平;当输入为低电平时,PMOS 导通,NMOS 截止,输出为高电平。

(三)CMOS 传输门CMOS 传输门由一个PMOS 晶体管和一个NMOS 晶体管并联组成。

当控制信号为高电平时,传输门导通,信号可以通过;当控制信号为低电平时,传输门截止,信号无法通过。

三、实验设备与材料(一)实验设备1、数字示波器2、直流电源3、信号发生器4、逻辑分析仪5、面包板6、万用表(二)实验材料1、 CD4007 芯片(包含多个 CMOS 器件)2、电阻、电容等分立元件四、实验内容与步骤(一)CMOS 反相器的测试1、在面包板上搭建 CMOS 反相器电路,使用 CD4007 芯片中的PMOS 和 NMOS 晶体管。

2、将直流电源连接到电路,设置输入电压分别为 0V 和 5V,使用万用表测量输出电压。

3、使用信号发生器产生频率为 1kHz 的方波信号作为输入,用示波器观察输入和输出信号的波形,记录上升时间和下降时间。

(二)CMOS 传输门的测试1、按照电路原理图在面包板上搭建 CMOS 传输门电路。

2、用直流电源提供控制信号和输入信号,分别设置控制信号为 0V 和 5V,测量输出信号的电压。

南通大学CMOS模拟集成电路设计实验报告姓名:班级:学号:指导老师:实验一 HSPICE实践1、Vgs固定时,NMOS的I/V特性曲线*nmos_I-V_testmn0 vout vin 0 0 NM w=2u l=1u.lib 'C:\synopsys\h06mixddct02v23.lib'ttv1 vin 0 2v2 vout 0 1.dc v2 0 5 0.1.probe i1(mn0).end2、改变W/L,W/L=4u/0.6u*nmos_I-V_testmn0 vout vin 0 0 NM w=4u l=0.6u.lib 'C:\synopsys\h06mixddct02v23.lib'ttv1 vin 0 2v2 vout 0 1.dc v2 0 5 0.1.probe i1(mn0).end3.在不同Vgs下,Vgs从0到5v验证I/V特性曲线*nmos_I-V_testmn0 vout vin 0 0 NM w=4u l=0.6u.lib'C:\synopsys\h06mixddct02v23.lib'ttv1 vin 0 2 0v2 vout 0 1 5.dc v2 0 5 0.1 v1 0 5 0.5.plot dc v(vout) id(mn0).probe.end1.4 温度从0到80℃仿真I/V特性曲线*nmos_I-V_testmn0 vout vin 0 0 NM w=2u l=1u.Model NM NMOS vt0=0.7 kp=110u gamma=0.4 lambda=0.04 phi=0.7 v1 vin 0 2v2 vout 0 1.dc v2 0 5 0.1 temp 0 80 20.probe i1(mn0).end1.5、Vds固定时,仿真NMOS的I/V特性曲线*nmos_I-V_testmn0 vout vin 0 0 NM w=2u l=1u.lib'C:\synopsys\h06mixddct02v23.lib'ttv1 vin 0 2v2 vout 0 1.dc v1 0 5 0.1.probe i1(mn0).end1.6 COMS反相器,Pmos的w/l为4u/0.6u,Nmos的w/l为2u/0.6u,Vdd为5v,输入pwl(0 0 5u 5)仿真得输出波形。

一:实验目的

1、掌握电阻负载、带源极负反馈的共源级的性能仿真方法

2、掌握源跟随器、共源共栅级的性能仿真方法。

二:实验数据

1:电阻负载共源电路图如下:

2:带源极负反馈的共源接法电路图如下:

3:源跟随器

4:共源共栅极

二:实验思考题

1:

区别:带反馈的当输入电压增大时,漏源电流增加的没有不带反馈的快,即跨导变小了。

原因:输入端是栅极,输出端是漏极,若带了源级负反馈电阻,当栅极输入电压升高时,漏源电流会增大,其中电流经过源级负反馈电阻,使源端的电压升高,导致栅源电压减小,漏源电流电流降低。

2:在R=1000时跨导变小了!

Vdd,所以随着Vdd的增加,N1各点的电压也会随着增加。

模拟CMOS集成电路实验实验四实验四运放的仿真方法实验运放:仿真前,直流扫描,确定工作点sp文件(部分).GLOBAL VDDIREF VDD NET3 DC=25uM1 NET1 1 NET2 NET2 NMOS L=2u W=47uM2 VOUT 2 NET2 NET2 NMOS L=2u W=47uM3 NET1 NET1 VDD VDD PMOS L=2u W=22uM4 VOUT NET1 VDD VDD PMOS L=2u W=22uM5 NET2 NET3 GND GND NMOS L=2u W=20uM6 NET3 NET3 GND GND NMOS L=2u W=20uV1 1 VIN 0V2 2 VOUT 0VGND GND 0 0VVDD VDD 0 3.3VVIN VIN 0 0.DC VVIN 0 3.3 0.05.options post acct probe.probe V(Vout) I(M5).END结果如下图图1.运放直流工作点扫描工作点选定为 2.0VAMP文件.GLOBAL VDD GND.SUBCKT AMP1 GND VDD Vin+ Vin- VOUTIREF VDD NET3 DC=25E-6M1 NET1 Vin+ NET2 GND NMOS L=2E-6 W=47E-6M2 VOUT Vin- NET2 GND NMOS L=2E-6 W=47E-6M3 NET1 NET1 VDD VDD PMOS L=2E-6 W=22E-6M4 VOUT NET1 VDD VDD PMOS L=2E-6 W=22E-6M5 NET2 NET3 GND GND NMOS L=2E-6 W=20E-6M6 NET3 NET3 GND GND NMOS L=2E-6 W=20E-6.ENDS AMP1LIB文件**********************model NMOS**********************.MODEL NMOS NMOS(+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11 +MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**********************model PMOS**********************.MODEL PMOS PMOS(+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)一、输入失调电压(Voltage Offset)的仿真1.sp文件.title test1.include './lib.txt'.include './'XI0 0 VDD VIN VOUT VOUT AMP1******************************************************VVDD VDD 0 3.3VVIN VIN 0 0.DC VVIN 0 3.3 0.05*.DC temp -40 120 1.options post acct probe.PROBE V(VOUT) *V(VIN) VOS=par‘V(VOUT)-V(VIN)’.op.END2.仿真结果温度对失调电压的影响1.sp文件.title test1.include './lib.txt'.include './'XI0 0 VDD VIN VOUT VOUT AMP1******************************************************VVDD VDD 0 3.3VVIN VIN 0 0*.DC VVIN 0 3.3 0.05.DC temp -40 120 1.options post acct probe.PROBE V(VOUT) *V(VIN) VOS=par‘V(VOUT)-V(VIN)’.op.END2.仿真结果二、开环增益的仿真1.sp文件.title test2.include './lib.txt'.include './'XI0 0 VDD VIN VOUT VOUT AMP1****************************************************** R0 VIN- VOUT 1GC0 VIN- 0 1GVVDD VDD 0 3.3VVIN VIN 0 DC=2 AC=1, 0.ac dec 100 0.001 10G.options post acct probe.probe Vdb(Vout) Vp(Vout).op.END2.仿真结果三、CMRR的仿真1.sp文件.title test3.include './lib.txt'.include './'XI1 0 VDD VIN VOUT1 VOUT1 AMP1XI2 0 VDD VIN VOUT2 VOUT2 AMP1******************************************************R0 VIN1- VOUT1 1GR1 VIN2- VOUT2 1GC0 VIN1- 0 1GC1 VIN VIN2- 1GVVDD VDD 0 3.3VVIN VIN 0 DC=2 AC=1, 0.ac dec 100 0.001 10G.options post acct probe.PROBE VDB(VOUT1) VDB(VOUT2) CMRR=Vdb(V out1)-Vdb(Vout2) ∠∮=Vp(V out1)-Vp(Vout2).op.END2.仿真结果四、PSRR的仿真1.sp文件.title test4.include './lib.txt'.include './'XI0 0 VDD VIN VOUT VOUT AMP1****************************************************** VVDD VDD 0 3.3 AC=1,0VVIN VIN 0 2.ac dec 100 0.001 10G.options post acct probe.PROBE VDB(VOUT) VP(VOUT).op.END2.仿真结果五、输出阻抗的分析1.sp文件.title test5.include './lib.txt'.include './'XI0 0 VDD VIN VOUT VOUT AMP1****************************************************** VVDD VDD 0 3.3 AC=1,0VVIN VIN 0 2I0 VOUT 0 DC=5U AC=1,0.ac dec 100 0.001 10G.options post acct probe.PROBE VDB(VOUT) VP(VOUT).op.END2.仿真结果六、SR及建立时间的仿真1.sp文件.title test6.include './lib.txt'.include './'XI0 0 VDD VIN VOUT VOUT AMP1****************************************************** VVDD VDD 0 3.3VVIN VIN 0 PULSE ( 2 3 5NS 0NS 0NS 50NS 100NS ) .TRAN 0.1NS 150NS 0NS.options post acct probe.PROBE V(VOUT) V(VIN).op.END2.仿真结果输入小信号10mv仿真结果:建立时间:5ns输入大信号1v仿真结果: 建立时间:4.2ns。

《CMOS高性能运算放大器研究与设计》篇一一、引言运算放大器(OpAmp)在各种电子设备中起着关键作用,尤其在信号处理和数据分析中。

随着科技的发展,对运算放大器的性能要求也越来越高。

CMOS(互补金属氧化物半导体)技术因其低功耗、高集成度等优点,在高性能运算放大器的设计中得到了广泛应用。

本文将探讨CMOS高性能运算放大器的研究与设计。

二、CMOS运算放大器的基本原理CMOS运算放大器主要由差分输入对、电流镜、输出级等部分组成。

其基本原理是通过差分输入对接收输入信号,利用电流镜进行电流放大,最后由输出级输出放大的信号。

CMOS技术由于其特殊的结构,能够提供较高的增益、低噪声以及优秀的线性度。

三、CMOS高性能运算放大器的设计要求设计高性能的CMOS运算放大器,需要满足以下几个要求:1. 高增益:保证信号在传输过程中的损失最小。

2. 低噪声:减小信号的干扰,提高信噪比。

3. 高线性度:保证信号在放大过程中不失真。

4. 低功耗:在保证性能的同时,尽量降低功耗。

5. 高集成度:适应现代电子设备小型化的趋势。

四、CMOS高性能运算放大器的设计方法1. 差分输入对的设计:选择合适的晶体管尺寸和偏置电流,以提高输入差分对的跨导和带宽。

2. 电流镜的设计:采用电流镜结构,以实现电流的精确复制和放大。

3. 输出级的设计:选择合适的负载电容和输出级晶体管,以提高输出驱动能力和带宽。

4. 电路的优化:通过调整电路的偏置电压和反馈网络,优化电路的性能。

五、CMOS高性能运算放大器的实现与测试根据上述设计要求和方法,我们设计了一款CMOS高性能运算放大器。

通过仿真和实际测试,该放大器具有高增益、低噪声、高线性度等特点,且功耗较低,符合设计要求。

此外,我们还对该放大器进行了长期稳定性的测试,证明了其良好的可靠性和稳定性。

六、结论本文对CMOS高性能运算放大器的研究与设计进行了探讨。

通过了解其基本原理、设计要求、设计方法以及实现与测试,我们可以看到CMOS技术在高性能运算放大器设计中的优势。

CMOS运放的仿真经验总结CMOS运放是一种常用的电路元件,可以在模拟电路中扮演放大、滤波、控制以及信号处理等重要角色。

在实际应用中,了解和掌握CMOS运放的仿真方法是十分重要的。

以下是我在进行CMOS运放仿真时的一些经验总结。

首先,在进行CMOS运放的仿真时,需要使用一款较为成熟且功能丰富的电路仿真软件,如Cadence、Pspice等。

这些软件提供了各种CMOS 运放模型,可以方便地进行仿真和分析。

在进行仿真前,需要确定仿真的目的和仿真电路的参数,包括工作电压、负载电阻、放大倍数等。

可以根据需要选择不同的CMOS运放电路结构,如共源共栅结构、共源共栅共排极结构等。

在进行仿真时,首先需要验证CMOS运放电路的基本工作电路,如差分输入、单端输出等。

可以通过给输入端施加电压、控制电流等方式,观察输出端的电压变化。

可以通过改变输入电压,观察输出电压的变化,从而确定CMOS运放的放大倍数和频率响应等参数。

在验证基本工作电路后,可以进行更复杂的功能仿真,如频率响应、相位响应、输入输出特性等。

可以使用正弦波输入信号,观察输出信号的波形变化。

可以根据需要选择不同的输入频率、幅值和相位,观察输出信号的变化。

在进行仿真时,需要注意电路中的最大功耗、最大温度、最大电流等参数是否处于允许的范围内。

如果超出了允许范围,需要优化电路结构或调整电路参数,以保证电路的可靠性和稳定性。

在进行仿真时,需要关注电路中的噪声和失调问题。

可以通过加入噪声源和失调源,观察输出信号的噪声和失调情况。

可以通过改变电路结构或优化电路参数,降低噪声和失调的影响。

最后,在进行仿真结果的分析时,需要综合考虑电路的性能、稳定性、可靠性等因素,进行全面评估。

可以比较不同电路结构的性能差异,选择最优的电路结构和参数。

总的来说,在进行CMOS运放的仿真时,需要系统地进行设计、验证和分析。

需要充分了解CMOS器件的特性和工作原理,合理选择电路结构和参数。

通过验算和优化,保证电路的性能和稳定性。

一:实验目的

1、复习基本差动对的电路结构、特点及工作原理。

2、学会使用tanner软件对差动放大器的基本性能进行仿真。

二:实验数据

基本差动电路图

网表文件

仿真结果

Vdc =0.5v,vin1、vin2振幅改成1.5v 仿真如下

Vdc=0.5v,vin1、vin2频率=0;

三:实验思考题

1、比较图3.6和图3.7,解释图3.7中两个输出电压波形失真的原因。

答:由于图3.7中输入的共模电平太低,就使的V in1和V in2处在负半轴时使得M1和M2管出现截止,导致底部出现失真。

另外由于每端的输出最大只能是VDD,所以当输入幅度信号

大时,输出正半轴时也会出现失真。

2、观察图3.9,读出输出电压的最大和最小值,验证仿真结果和理论分析的一致性。

答:有图可知,Vout(max)= 2.5v; V out(min) = -2.5v

当V in1很小时,M1管截止,M2管导通,V out1 = VDD,

V out2 = VDD – R D I ss;当V in2很小时,M2管截止,M1管导通,V out2 = VDD, V out2= VDD –R D I ss;故仿真结果与理论分析一致。

一:实验目的

1、复习CMOS单级放大器和差动放大器的频率特性。

2、学习单级放大器和差动放大器的性能仿真方法。

二:实验数据

2.1 电阻负载共源级的频率特性

2.2源跟随器的频率特性

2.3共源共栅放大器的频率特性

2.4基本差动对的频率特性

三:实验思考题

1、将图5.2中的MOS管宽度改为10u,再进行仿真,给出

仿真结果,并将其与图5.3比较,说出其区别及原因。

我们知道栅和沟道之间的氧化层电容C1=WLC ox;在饱和区时,C GS=C GD=WLC ox/ 2 + WC ov;当沟道的宽变小后,结电容也会跟着变小,所有曲线向高频移动,另外频率越高电阻负载共源的影响越大!

2、带宽大概5000MHZ左右。