Cadence原理图输入

- 格式:pdf

- 大小:247.97 KB

- 文档页数:21

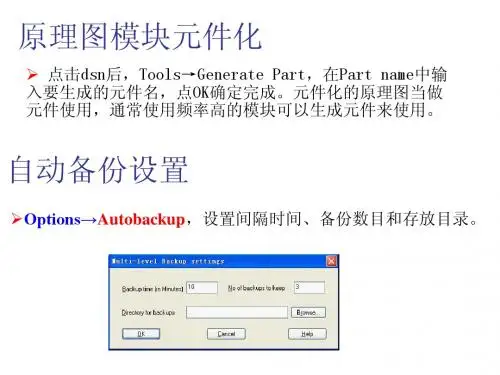

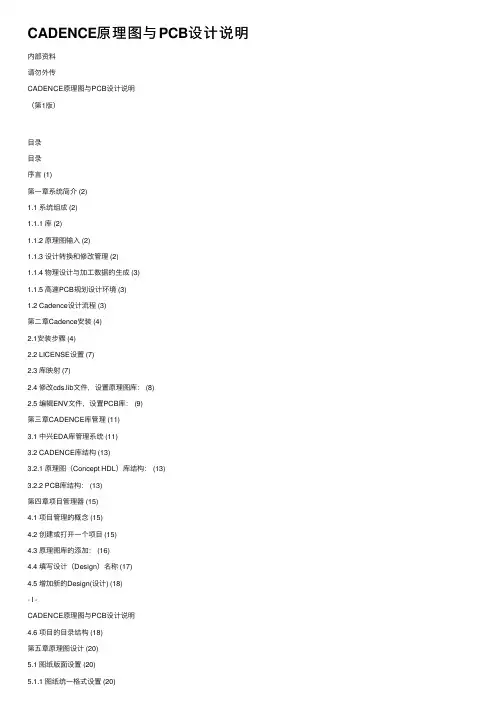

CADENCE原理图与PCB设计说明内部资料请勿外传CADENCE原理图与PCB设计说明(第1版)⽬录⽬录序⾔ (1)第⼀章系统简介 (2)1.1 系统组成 (2)1.1.1 库 (2)1.1.2 原理图输⼊ (2)1.1.3 设计转换和修改管理 (2)1.1.4 物理设计与加⼯数据的⽣成 (3)1.1.5 ⾼速PCB规划设计环境 (3)1.2 Cadence设计流程 (3)第⼆章Cadence安装 (4)2.1安装步骤 (4)2.2 LICENSE设置 (7)2.3 库映射 (7)2.4 修改cds.lib⽂件,设置原理图库: (8)2.5 编辑ENV⽂件,设置PCB库: (9)第三章CADENCE库管理 (11)3.1 中兴EDA库管理系统 (11)3.2 CADENCE库结构 (13)3.2.1 原理图(Concept HDL)库结构: (13)3.2.2 PCB库结构: (13)第四章项⽬管理器 (15)4.1 项⽬管理的概念 (15)4.2 创建或打开⼀个项⽬ (15)4.3 原理图库的添加: (16)4.4 填写设计(Design)名称 (17)4.5 增加新的Design(设计) (18)- I -CADENCE原理图与PCB设计说明4.6 项⽬的⽬录结构 (18)第五章原理图设计 (20)5.1 图纸版⾯设置 (20)5.1.1 图纸统⼀格式设置 (20)5.1.2 栅格设置 (22)5.2Concept-HDL的启动 (23)5.3添加元件 (24)5.3.1 逻辑⽅式添加器件 (24)5.3.2 物理⽅式添加器件 (25)5.4画线 (26)5.4.1 Draw⽅式 (26)5.4.2 Route⽅式 (27)5.5 添加信号名 (27)5.6 画总线 (28)5.7 信号名命名规则 (29)5.8 元件位号 (31)5.8.1 元件位号⼿⼯标注 (31)5.8.2 元件位号的⾃动标注 (32)5.8.3 元件位号的⾃动排序 (33)5.9 Cadence属性 (34)5.10 组操作 (36)5.10.1 组定义: (36)5.10.2 组命名 (36)5.10.3 组操作 (37)5.11 常⽤命令 (38)5.11.1 常⽤的快捷键 (38)5.11.2 检查连接关系 (39)5.11.3 点画命令 (39)5.11.4 查找元件和⽹络 (39)5.11.5 两个不同⽹络名的⽹络连接的⽅法 (40)5.11.6 错误检查 (40)5.11.7 检查Cadence原理图单个⽹络名 (40)- II -⽬录5.11.8 对隐藏了电源和地腿的器件定义电源和地信号 (41)5.12 增加新的原理图页 (41)5.13 原理图多页⾯操作 (42)5.14 信号的页区位置交叉标注(Cross Reference) (42)5.14.1 信号的页区位置交叉标注(Cross Reference)的作⽤ (42) 5.14.2 交叉标注需注意的⼏点: (43)5.14.3 信号的交叉标注(Cross Refrence)的⽅法 (43)5.14.4 层次设计中出模块信号的交叉标注 (43)5.14.5 出页信号的交叉标注的要求 (44)5.15 在不同的project下实现原理图拷贝 (44)5.16 打印图纸 (47)5.17 ⾃动⽣成料单 (48)5.18 原理图归档 (50)5.19 原理图评审 (51)第六章从原理图到PCB (52)6.1从原理图到PCB的实现 (52)6.1 .1 原理图到PCB的转换过程: (52)第七章PCB设计 (55)7.1 导⼊数据 (55)7.2 Allegro⽤户界⾯ (55)7.2.1 控制⾯板的作⽤ (56)7.2.2 ⼯具栏的显⽰ (57)7.3 Layout准备 (58)7.3.1 创建PCB图的物理外形 (58)7.3.1.2 在Allegro界⾯下创建板外框: (61) 7.3.2 设置板图尺⼨参数 (62)7.3.3 设置版图的栅格值: (63)7.3.4 设置板图选项 (63)7.3.5 设置PCB板的叠层 (64)7.3.6 设置约束条件 (65)7.3.6.1 设置板的缺省间距: (65)- III -CADENCE原理图与PCB设计说明7.3.6.2 设置扩展的距离规则 (66)7.3.6.3 设置扩展的物理规则 (69)7.3.6.4 编辑属性 (69)7.3.7 可视性和颜⾊设置 (70)7.4 PCB布局 (70)7.5 PCB布线: (73)7.6 添加过孔和替换过孔 (74)7.6.1 添加过孔 (74)7.6.2 替换过孔 (75)7.7 优化⾛线 (76)7.8 覆铜处理 (77)7.8.1 阴版覆铜 (77)7.8.2 阳版覆铜 (78)7.9 分割电源平⾯ (80)7.10 位号标注 (83)7.11 加测试点 (83)7.12 DRC检查 (83)7.13 ⽣成报告⽂件 (84)7.14 V ALOR检查 (85)7.15 ⽣成光绘⽂件和钻孔⽂件 (85)7.15.1 ⽣成光圈⽂件(art-aper.txt),即D码表 (85)7.15.2 ⽣成钻孔⽂件 (86)7.15.3 ⽣成光绘⽂件 (86)7.15.3.1 在Artwork中加⼊所需的层 (86)7.15.3.2 ⽣成光绘⽂件 (90)7.16 PCB评审 (93)第⼋章公司的PCB设计规范 (94)- IV -序⾔序⾔Cadence软件是我们公司统⼀使⽤的原理图设计、PCB设计、⾼速仿真的EDA⼯具。

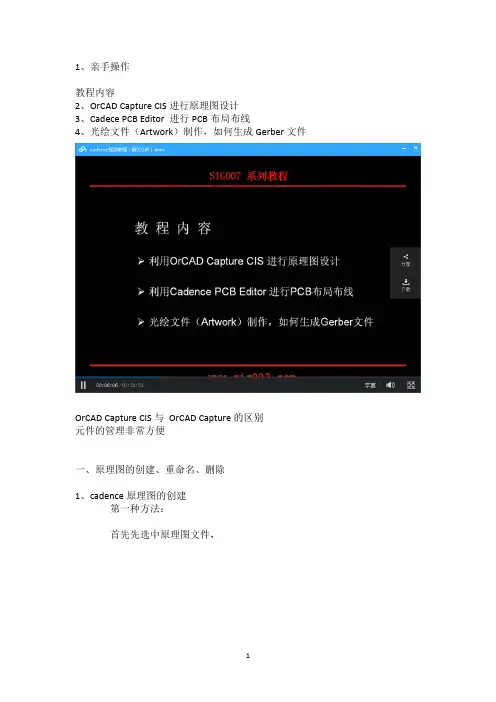

1、亲手操作教程内容2、OrCAD Capture CIS进行原理图设计3、Cadece PCB Editor 进行PCB布局布线4、光绘文件(Artwork)制作,如何生成Gerber文件OrCAD Capture CIS与OrCAD Capture的区别元件的管理非常方便一、原理图的创建、重命名、删除1、cadence原理图的创建第一种方法:首先先选中原理图文件,然后点击菜单栏上的Design--New Schematic Page输入原理图名称第二种方法:先选中原理图文件,然后右键单击,选择New Page输入原理图名称2、删除原理图文件第一种方法:首先选择你要删除的原理图文件,然后点击菜单栏上的Edit---Delete,点击Delete之后,就会弹出下面的对话框。

点击确定之后,原理图2就删除了。

第二种方法:首先选择你要删除的原理图文件,然后鼠标右键点击Delete,如下图所示弹出如下所示,点击确定,原理图即删除。

3、cadence原理图的重命名第一种方法:选择需要更改原理图文件名的文件,然后点击菜单栏中的Design---Rename在弹出的对话框中,输入名称,点击OK即可。

第二种方法:选择需要更改原理图文件名的文件,然后右键点击Rename弹出对话框,在弹出的对话框中,输入名称,点击OK即可。

二、原理图的放大、缩小方法一: 直接按下快捷---i /o方法二:选择需要放大、缩小的原理图,然后选择菜单栏上的View---Zoom----In 放大Out 缩小方法三:按住键盘上的CTRL键,鼠标上的滑轮,向前滑动,原理图放大;向后滑动,原理图缩小。

如果原理图放的很大,可以移动滚动条进行原理图的上下左右的滚动。

也可以利用快捷键进行滚动条的移动,按住CTRL+PAGEUP,原理图向左移动;按住CTRL+PAGEDOWN,原理图向右移动;按住PAGEUP,原理图向上移动;按住PAGEDOWN,原理图向下移动。

Allegro Design Entry HDL原理图输入方式海峰Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

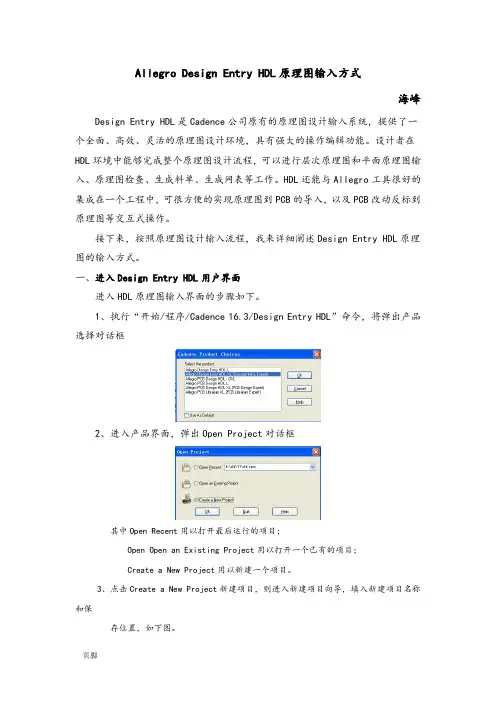

一、进入Design Entry HDL用户界面进入HDL原理图输入界面的步骤如下。

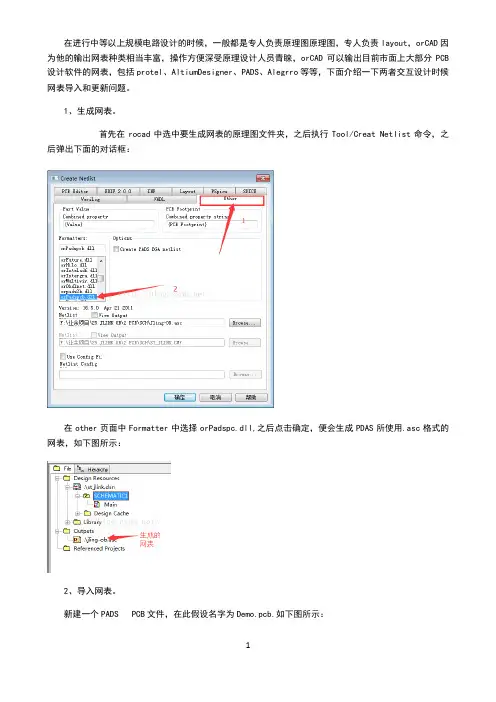

1、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中Open Recent用以打开最后运行的项目;Open Open an Existing Project用以打开一个已有的项目;Create a New Project用以新建一个项目。

3、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置的所有容。

7、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径和文件名称;(2)菜单栏——项目所有相关操作的集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗口菜单和帮助菜单。

在进行中等以上规模电路设计的时候,一般都是专人负责原理图原理图,专人负责layout,orCAD因为他的输出网表种类相当丰富,操作方便深受原理设计人员青睐,orCAD可以输出目前市面上大部分PCB 设计软件的网表,包括protel、AltiumDesigner、PADS、Alegrro等等,下面介绍一下两者交互设计时候网表导入和更新问题。

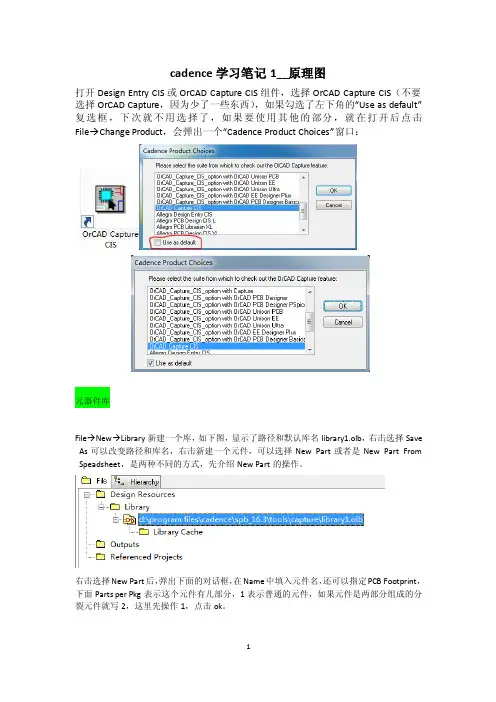

1、生成网表。

首先在rocad中选中要生成网表的原理图文件夹,之后执行Tool/Creat Netlist命令,之后弹出下面的对话框:在other页面中Formatter中选择orPadspc.dll,之后点击确定,便会生成PDAS所使用.asc格式的网表,如下图所示:2、导入网表。

新建一个PADS PCB文件,在此假设名字为Demo.pcb.如下图所示:新建文件之后,首先要有自己的PCB封装库,并且设置好自己的PCB封装库路径,设置PCB封装库路径发方法如下:工具/选项之后弹出来如下界面:点击右侧的库列表文件夹,如下图所示,之后选择自己的PCB封装库所在位置:这样自己的封装库路径设置完成了。

之后可以在PADS layout软件中导入网表了。

打开刚才创建的Demo.pcb文件,执行"文件/导入"命令,打开刚才用orcad生成的.asc文件。

之后会弹出一个检验文本,提示所有的错误和警告,如下图所示:之后还会弹出一个警告对话框,可以忽略之。

之后所有的原件就导入进来了,如下图所示,此时元件是堆放在一起的:执行命令:“工具/分散元器件”,之后元器件被分散开来,如下图所示:这样,就完成了PCB的导入,之后可以进行布线工作。

3、更新原理图中修改的网表。

在PCB布线的时候可能会修改原理图中的部分器件或者连线,这时候就要进行网表更新。

步骤如下:a、更改好原理图之后,重新生成网表,然后新建一个空的PCB文件,给这个pcb文件起一个名字(名字随便起),这里就叫做temp.pcb.b、打开temp.pcb文件,执行"文件/导入"命令,导入新生成的.asc网表,之后关闭temp.pcb。

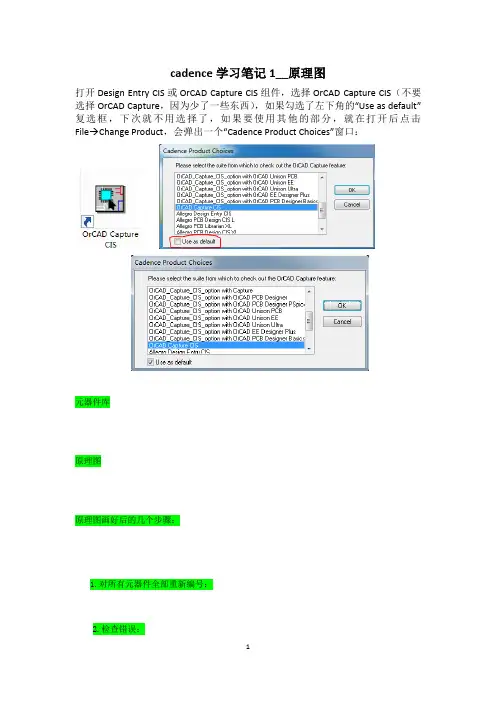

cadence学习笔记1__原理图打开Design Entry CIS或OrCAD Capture CIS组件,选择OrCAD Capture CIS(不要选择OrCAD Capture,因为少了一些东西),如果勾选了左下角的“Use as default”复选框,下次就不用选择了,如果要使用其他的部分,就在打开后点击File→Change Product,会弹出一个“Cadence Product Choices”窗口:元器件库File→New→Library新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是New Part From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCB Footprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

中间的虚线框是这个元件的区域,右边会有一个工具栏,画直线、方框、圆、曲线,也可以输入一些字符,或者点放置一组引脚,放置结束后鼠标右击选择End Mode或按键盘左上角Esc键使命令结束,放置一组引脚的时候,还可以设置引脚的类型,比如输入、输出、双向、电源等等,这个没有区分电源和地,电源和地都是power型的,现在输入下面的几个数字,线型都是默认的Passive,引脚间距Pin Spacing设为1,点击ok,放置好后成为下面的样子,有些部分不需要显示,双击空白处弹出一个属性对话框,虚框里面的数字是PinName,虚框外面的数字是PinNumber,如果可视属性改成False就不显示了。

如果想改变其中一个引脚的引脚名、引脚编号、引脚类型,选中该引脚,右击选择Edit Properties,或者双击该引脚,如下图:画直线的时候,这里默认是按照栅格点为最小单位的,可以改变这种限制,画出任意长度任意角度的线,在工具栏Options Grid Display中,不要勾选Pointer snap to grid就可以了,记得画完想要的任意直线后,再将这里勾选,这是一个好习惯,可以让画出的线更规则整齐。

![[笔记]CadenceConceptHDL原理图输入](https://uimg.taocdn.com/036686030a4e767f5acfa1c7aa00b52acfc79c10.webp)

Allegro Design Entry HDL原理图输入方式00孙海峰00Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL 环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

00接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

00一、进入Design Entry HDL用户界面00进入HDL原理图输入界面的步骤如下。

001、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框002、进入产品界面,弹出Open Project对话框00其中Open Recent用以打开最后运行的项目;0Open Open an Existing Project用以打开一个已有的项目;00Create a New Project用以新建一个项目。

003、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保00存位置,如下图。

004、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库005、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可00以填写新建项目名称,也可以选择已有元件,对其进行修改。

06、点击下一步,进入Summary对话框,显示前面步骤所设置的所有内容。

007、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,00并出现原理图工作界面。

00其中:(1)标题栏——显示文件所在路径和文件名称;00(2)菜单栏——项目所有相关操作的集合;00包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、00模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗00口菜单和帮助菜单。

一、基本操作(一)电路图绘制1、登陆到UNIX系统。

在登陆界面,输入用户名***和密码***** 。

2、Cadence的启动。

登录进去之后,点击Terminal出现窗口,输入icfb命令,启动Cadence软件。

3、根据设计指标及电路结构,估算电路参数。

4、利用Candence原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号,根据不同的仿真电路设置不同的电源参数。

(7)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

如果有,察看CIW窗口的提示。

4、利用Candence原理图的输入。

(二)电路图仿真(1)启动模拟仿真环境。

在comparator schematic窗口,选择Tools-Analog Environment,弹出模拟仿真环境界面。

(2)设置模型库。

(3)设置分析类型。

在仿真窗口,点击Choose Analyses按钮,弹出Choose Analyses窗口,该窗口中列出了各种仿真类型,依次进行各种仿真,如ac、dc、tran,进行交流仿真、直流仿真、瞬态仿真。

(4)设置波形显示工具。

Cadence中有两种波形显示工具:AWD和wavescane,在仿真窗口选择Session-assign,在弹出的窗口中可以选择波形显示工具为AWD或wavescane。

原理图工程的建立1、打开OrCAD Capture CIS打开OrCAD Capture CIS弹出一个Cadence Product Choices对话框,选择OrCAD Capture CIS(比Capture CIS功能强大)点击OK。

2、新建工程File-New-Project。

选择Schematic给工程取一个名字(最好为纯英文、数字。

而且随后的PCB文件名称需与原理图的名称一致,否则不能成功地从PCB中回注编号),选择保存路径。

这里也可以选择PC Board Wizard,不知道两者有什么区别。

3、创建元件库file -> new ->library,元件库被自动加入到工程中4、放置元器件cadence原理图库在\Cadence\SPB_16.6\tools\capture\library这个路径下面。

放置元器件,快捷键P,输入原器件名,enter放置。

(封装名要与库中相同)。

5、重新编号对原理图重新编号:选.dsn 文件,tool->annotate弹出annotate 对话框,其中把Action 这一项先设置为Reset part reference to“?”确定。

然后再重来一次Action选择Incremental reference update,确定。

即先取消所有索引编号,再重新编号。

6、规则检查回到.opj窗口,选中.dsn-SCHEMA TIC1下的原理图文件,Tools-DRC进行DRC规则检查。

7、生成网表选中.dsn文件,Tools-create Netlist(有时生成错误可能是有元器件未导入封装)。

原理图技巧1、鱼眼功能:点击小眼睛,再按Q键2、原理图文件夹的创建鼠标选择.dsn 文件,选design –〉new schematic 或鼠标右键-> new schematic。

原理图文件的创建选择原理图文件夹,选design –〉new schematic page 或鼠标右键->new page。

Cadence 电路编辑 简易使用手册东南大学IC学院实验室2005年11月前言作为流行的EDA工具之一,Cadence一直以来都受到了广大EDA工程师的青睐。

然而Cadence的使用之繁琐,又给广大初学者带来了不少麻烦。

本册子的本意在于为初学者指路,故不会对个别工具进行很详细的介绍,只是对初学者可能经常使用的一些工具加以粗略的介绍。

IC学院实验室工作站安装有Xmanager,本手册将从Xmanager的启动开始介绍。

一、从客户端Xmanger登陆UNIX服务器1、从“开始”—“所有程序”—“Xmanager”—“Xbrowser”,客户端程序找到实验室装载有CANDANCE工具包的Sun-B2500服务器,如图1-1所示:图1-12、双击“Sun-B2500”,显示服务器登陆窗口图1-2,输入网管给你的帐号,确认后出现图1-3,输入密码,并确认(注意:你输入密码时,对话框中不显示任何信息)。

图1-2图1-3如果你输入的帐号密码正确,经过服务器确认后,你就远程登陆到服务器上了(显示图1-4)。

图1-4二、启动Candence在屏幕空白处点击鼠标右键并如图2-1选择“hosts”—“Terminal Console”;图2-1出现Console对话窗口图2-2,图2-2输入icfb&并回车就运行Candence了;运行Candence后就会出现CIW窗口,图2-3;图2-3三、库文件的管理3.1建立自己的工作库启动了Cadence后,就可以利用File菜单建立自己的工作库,点击CIW窗口上的File 菜单,选定其中的New lib项,弹出如图3-1所示的对话框;图3-1输入库名并选择相应的工艺库,然后选择ok,这时在CIW的显示区会出现如下提示:Created library "mylib" as "/space/home/zch/mylib"!3.2在库中生成自己所需的单元新建的库是一个空的库,里面什么也没有,用户可在库中生成自己所需的单元。

原理图工程的建立1、打开OrCAD Capture CIS打开OrCAD Capture CIS弹出一个Cadence Product Choices对话框,选择OrCAD Capture CIS(比Capture CIS功能强大)点击OK。

2、新建工程File-New-Project。

选择Schematic给工程取一个名字(最好为纯英文、数字。

而且随后的PCB文件名称需与原理图的名称一致,否则不能成功地从PCB中回注编号),选择保存路径。

这里也可以选择PC Board Wizard,不知道两者有什么区别。

3、创建元件库file -> new ->library,元件库被自动加入到工程中4、放置元器件cadence原理图库在\Cadence\SPB_16.6\tools\capture\library这个路径下面。

放置元器件,快捷键P,输入原器件名,enter放置。

(封装名要与库中相同)。

5、重新编号对原理图重新编号:选.dsn 文件,tool->annotate弹出annotate 对话框,其中把Action 这一项先设置为Reset part reference to“?”确定。

然后再重来一次Action选择Incremental reference update,确定。

即先取消所有索引编号,再重新编号。

6、规则检查回到.opj窗口,选中.dsn-SCHEMA TIC1下的原理图文件,Tools-DRC进行DRC规则检查。

7、生成网表选中.dsn文件,Tools-create Netlist(有时生成错误可能是有元器件未导入封装)。

原理图技巧1、鱼眼功能:点击小眼睛,再按Q键2、原理图文件夹的创建鼠标选择.dsn 文件,选design –〉new schematic 或鼠标右键-> new schematic。

原理图文件的创建选择原理图文件夹,选design –〉new schematic page 或鼠标右键->new page。

一、基本操作(一)电路图绘制1、登陆到UNIX系统。

在登陆界面,输入用户名***和密码***** 。

2、Cadence的启动。

登录进去之后,点击Terminal出现窗口,输入icfb命令,启动Cadence软件。

3、根据设计指标及电路结构,估算电路参数。

4、利用Candence原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号,根据不同的仿真电路设置不同的电源参数。

(7)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

如果有,察看CIW窗口的提示。

4、利用Candence原理图的输入。

(二)电路图仿真(1)启动模拟仿真环境。

在comparator schematic窗口,选择Tools-Analog Environment,弹出模拟仿真环境界面。

(2)设置模型库。

(3)设置分析类型。

在仿真窗口,点击Choose Analyses按钮,弹出Choose Analyses窗口,该窗口中列出了各种仿真类型,依次进行各种仿真,如ac、dc、tran,进行交流仿真、直流仿真、瞬态仿真。

(4)设置波形显示工具。

Cadence中有两种波形显示工具:AWD和wavescane,在仿真窗口选择Session-assign,在弹出的窗口中可以选择波形显示工具为AWD或wavescane。