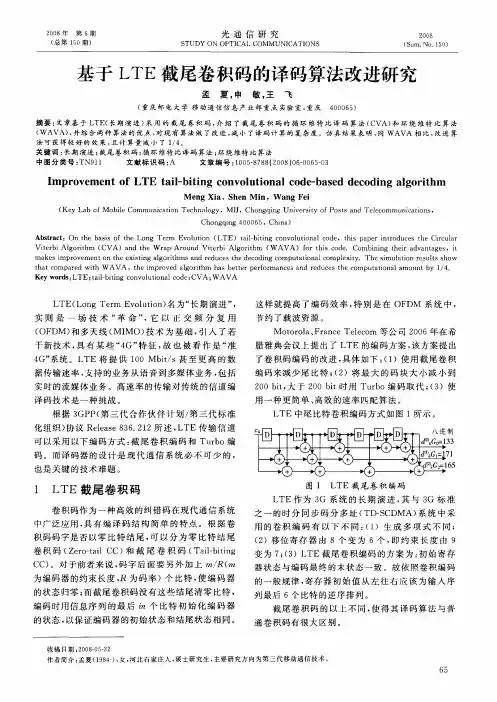

卷积码的译码算法研究

- 格式:pdf

- 大小:1.77 MB

- 文档页数:56

卷积码的一种译码方法的研究摘要:卷积码是一种在深空通信和移动通信系统中使用较多的信道编码方案。

cdma is-95标准和wcdma 3gpp标准将卷积码作为实时要求较高业务的信道纠错编码。

本文是在现有卷积码译码方法较为复杂的情况下,对卷积码的译码方法进行了分析,对于五位以内突发错误的译码进行纠错的方法进行了探索性研究。

关键词:卷积码译码纠错中图分类号:tp3 文献标识码:a 文章编号:1672-3791(2012)10(b)-0002-011 卷积码基础1948年香农提出了噪声信道编码理论,其核心是通过适当的编码后,当信息传输率小于信道容量时,能够高效无误地传输。

卷积码是一个有限记忆系统,它是将信息序列分割成长度为k的一个个分组,然后将k个信息比特编成n个比特,但k和n通常很小,特别适合以串行形式进行传输,时延小。

与分组码不同的是,在某一分组编码时,不仅参看本时刻的分组而且参看本时刻以前的m+1个分组,编码过程中互相关联的码元个数为n(m+1)。

n=m+1称为约束长度。

n-1是卷积码的重要参数为了突出特征参数常把卷积码写成(n,k,m)卷积码[1]。

1.1 卷积码的原理卷积码的编码器的一般结构如图1所示。

它包括:一个由n段组成的输入移位寄存器,每段k个,共kn个寄存器;一组n个模2和相加器,一个由n级组成的输出移位寄存器。

对应于每段k个比特的输入序列,输出n个比特。

整个编码过程可以看成是输入信息序列与由移位寄存器和模2加法器之间连接所决定的另一个序列的卷积码,卷积码即由此得名。

在(n,k,m)卷积码中,n为码长,k为码组中信息码元的个数,它的编码效率为r=k/n[2]。

正因为卷积码在编码过程中,充分利用了各组之间的相关性,无论是从理论上还是实际上均已证明其性能要优于分组码,因此在通信领域应用得越来越多。

但目前尚未找到较为严密的数学手段,将码的构成与其纠/检错能力有规律的联系起来,另外,卷积码的译码算法也有待于进一步研究与完善。

实验二卷积码编码及译码实验一、实验目的通过本实验掌握卷积编码的特性、产生原理及方法,卷积码的译码方法,尤其是维特比译码的原理、过程、特性及其实现方法。

二、实验内容1、观察NRZ基带信号及其卷积编码信号。

2、观察帧同步信号的生成及巴克码的特性。

3、观察卷积编码信号打孔及码速率匹配方法。

4、观察接收端帧同步过程及帧同步信号。

5、观察译码结果并深入理解维特比译码的过程。

6、观察随机差错及突发差错对卷积译码的影响。

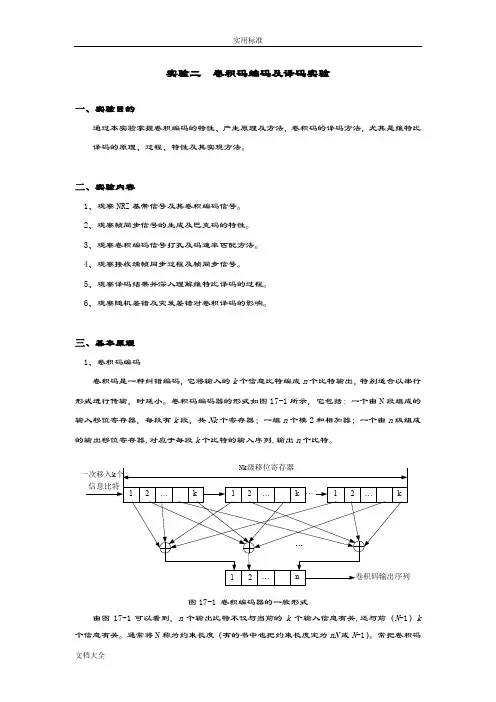

三、基本原理1、卷积码编码卷积码是一种纠错编码,它将输入的k个信息比特编成n个比特输出,特别适合以串行形式进行传输,时延小。

卷积码编码器的形式如图17-1所示,它包括:一个由N段组成的输入移位寄存器,每段有k段,共Nk个寄存器;一组n个模2和相加器;一个由n级组成的输出移位寄存器,对应于每段k个比特的输入序列,输出n个比特。

图17-1 卷积编码器的一般形式由图17-1可以看到,n个输出比特不仅与当前的k个输入信息有关,还与前(N-1)k 个信息有关。

通常将N称为约束长度(有的书中也把约束长度定为nN或N-1)。

常把卷积码记为:(n 、k 、N ),当k =1时,N -1就是寄存器的个数。

编码效率定义为:/c R k n =(17-1)卷积码的表示方法有图解表示法和解析表示法两种:解析法,它可以用数学公式直接表达,包括离散卷积法、生成矩阵法、码生成多项式法;图解表示法,包括树状图、网络图和状态图(最的图形表达形式)三种。

一般情况下,解析表示法比较适合于描述编码过程,而图形法比较适合于描述译码。

(1)图解表示法 (2)解析法下面以(2,1,3)卷积编码器为例详细讲述卷积码的产生原理和表示方法。

(2,1,3)卷积码的约束长度为3,编码速率为1/2,编码器的结构如图17-2所示。

jj图17-2 (2,1,3)卷积编码器这里我们主要介绍码多项式法。

我们可以用多项式来表示输入序列、输出序列、编码器中移位寄存器与模2和的连接关系。

请简述卷积码译码的维特比算法

卷积码译码的维特比算法是一种概率译码方法,通过计算接收序列的每个可能的发送序列的概率,然后选择具有最大概率的发送序列作为译码输出。

具体步骤如下:

1. 计算每个时刻每个状态下的分支度量。

2. 对于每个时刻,计算每个状态下的部分路径和。

3. 将部分路径和与该时刻的接收路径进行比较,计算汉明码距离。

4. 选择具有最小汉明码距离的状态作为幸存路径。

5. 将幸存路径的最后一个时刻作为输出,并删除所有其他路径。

6. 重复步骤3-5,直到所有接收序列都被译码。

该算法的核心思想是“加、比、选”,即先将每个时刻每个状态下的分支度量进行累积,然后比较每个时刻每个状态下的部分路径和,选择具有最小汉明码距离的状态作为幸存路径。

通过重复执行这些步骤,最终得到译码输出。

卷积码编码和维特比译码的原理、性能与仿真分析1.引言卷积码的编码器是由一个有k位输入、n位输出,且具有m位移位寄存器构成的有限状态的有记忆系统,通常称它为时序网络。

编码器的整体约束长度为v,是所有k个移位寄存器的长度之和。

具有这样的编码器的卷积码称作[n,k,v]卷积码。

对于一个(n,1,v)编码器,约束长度v等于存储级数m.卷积码是由k个信息比特编码成n(n>k)比特的码组,编码出的n比特码组值不仅与当前码字中的k个信息比特值有关,而且与其前面v个码组中的v*k个信息比特值有关。

卷积码有三种译码方式:序列译码、门限译码和概率译码。

其中,概率译码根据最大似然译码原理在所有可能路径中求取与接收路径最相似的一条路径,具有最佳的纠错性能,维特比译码是概率译码中极重要的一种方式。

序列译码和门限译码则不一定能找出与接收路径最相似的一条路径。

不同于维特比译码,门限译码与序列译码所需的计算量是可变的且对于给定信息分组的最终判决仅仅基于(m+1)个接收分组,而不是基于整个接收序列。

与维特比译码所使用的对数似然量度不同,序列译码所使用的量度为Fano量度。

在接收序列受扰严重的情况下,序列译码的计算量大于维特比译码所需的固定计算量,虽然序列译码要求的平均计算次数通常小于维特比译码。

在采用并行处理的情况下,维特比译码的速度会优于序列译码。

在同样码率和存储级数的条件下,门限译码的性能比维特比译码低大约3dB.维特比译码的数据输出方式有硬判决及软判决两种方式,本文选取生成多项式为561,753的(2,1,8)卷积码对硬判决的性能进行分析,并依据维特比译码的原理以及卷积码的特性,对卷积码编码和维特比译码过程在加性高斯白噪声(AWGN)信道下进行仿真,并且根据仿真结果对维特比译码(硬判决)的结果进行分析。

由于卷积码的生成可以看做一个马尔科夫过程,因此,不同状态间的转移概率对描述这个过程有极关键的作用。

本文则基于MATLAB对不同状态间的转移概率进行求解,从而更准确地分析维特比译码的性能。

卷积码编码及译码实验浅谈卷积编码下的FPGA实现

卷积编码是现代数字通信系统中常见的一种前向纠错码,区别于常规的线性分组码,卷积编码的码字输出不仅与当前时刻的信息符号输入有关,还与之前输入的信息符号有关。

本文主要是关于卷积码编码及译码实验的相关介绍,并着重分析阐述了基于卷积编码下的FPGA实现。

卷积编码卷积码的编码分为两类:前馈和反馈,在每类中又可分为系统和非系统形式。

我们这里只考虑非系统形式的前馈编码器。

‘

上图是WLAN 802.11a协议中采用的卷积编码器结构,输入比特k=1,输出n=2,存储器长度m=6,编码输出不仅与当前输入有关,还与存储器存储的之前的输入数据有关,具体由之前的哪些数据得到编码输出呢,由生成多项式确定其连接关系。

这里,生成多项式为g0=133(八进制)和g1=171(八进制)(右边是最高位),输出数据A的生成多项式为:

输出数据B的生成多项式为:

生成多项式确定了卷积编码器输出的连接关系。

根据多项式的系数,在相应项进行连接。

生成多项式写成二进制序列的形式分别为:g0 = [1 0 1 1 0 1 1]和g1 = [1 1 1 1 0 0 1](右边是最高位)。

我们假设信息序列u,两个编码器输出序列分别为v(0)和v(1),编码器可以看成一个线性系统,系统的信道响应脉冲最多持续m+1个时间单元,编码输出可以写成编码输入与信道脉冲响应的卷积(即生成多项式),即

其中需要注意的是,所有的加法都是模2加运算。

卷积码编码及译码实验基本原理

1、卷积码编码

卷积码是一种纠错编码,它将输入的k个信息比特编成n个比特输出,特别适合以串行形。

一、概述卷积码是一种常用的编码技术,用于提高数字通信系统的可靠性和抗干扰能力。

而编码的解码过程则需要运用编译码技术,以恢复原始数据。

Matlab作为一种强大的工程仿真软件,可以用来对卷积码编译码进行仿真分析,帮助工程师们更好地理解和优化卷积码系统,提高通信系统的性能。

二、卷积码原理1. 卷积码的概念卷积码是一种线性块码,它采用移位寄存器和模2加法器进行编码,通过引入冗余比特来提高信号的可靠性。

卷积码的编码过程可以简单描述为:将输入信息数据与特定的生成多项式进行卷积运算,得到编码后的输出数据。

2. 卷积码的特点卷积码具有较高的编码效率和能够很好地控制码长、纠错能力等特性,因此在实际通信系统中得到广泛应用。

三、编译码原理1. Viterbi算法卷积码的译码过程通常采用Viterbi算法,它是一种最大似然译码算法,通过计算最小距离路径的方式来进行译码。

Viterbi算法能够有效地对卷积码进行解码,提高译码的准确性。

2. 编译码的实现在Matlab中,编译码的实现通常是通过编写一定的程序来模拟Viterbi算法的译码过程。

通过仿真分析,可以评估不同的编码方案对通信系统性能的影响。

四、Matlab仿真环境1. Matlab的特点Matlab作为一种强大的仿真软件,具有丰富的工具和函数库,能够方便地进行数字通信系统设计与仿真分析。

Matlab提供了直观的图形界面和强大的数据处理能力,可用于展示仿真结果和进行数据分析。

2. 使用Matlab进行卷积码编译码仿真在Matlab环境中,可以编写程序来实现卷积码的编码和Viterbi算法的译码过程。

通过调用Matlab中的工具函数和绘图函数,可以直观地展示通信系统的性能指标,并对比不同编码方式的性能差异。

五、仿真实例分析1. 卷积码编码仿真我们可以编写Matlab程序,实现对卷积码的编码过程。

通过模拟不同的编码率和约束长度,可以观察到编码后的效果,并评估编码的性能。

卷积码是一种纠错编码技术,通常用于无线通信和数字通信系统中,以提高数据传输的可靠性。

卷积码的编码和译码是两个关键步骤,下面分别介绍这两个步骤:**编码:**1. **选择卷积码的参数:** 在编码之前,您需要确定卷积码的参数,包括约束长度(constraint length)、生成多项式(generator polynomial)和码率(code rate)。

这些参数将决定编码器的结构和性能。

2. **构建编码器:** 卷积码编码器通常是一个有限状态自动机(Finite State Machine,FSM)。

根据所选的生成多项式,配置编码器的状态转移图。

编码器的输入是要编码的数据位,输出是编码后的码字。

3. **编码操作:** 对每个输入位进行编码操作。

编码器的状态会根据输入位的不同而变化,从而生成不同的编码输出。

通常,每个输入位都会产生多个输出位,这是卷积码的特点之一。

4. **输出码字:** 编码器将生成的码字传送出来,以便传输或存储。

**译码:**1. **构建译码器:** 卷积码的译码器通常是使用一种称为Viterbi算法的最大似然译码方法来实现的。

译码器需要与编码器具有相同的约束长度和生成多项式。

2. **接收和测量:** 译码器接收传输的码字,并测量接收到的码字与每个可能的发送码字之间的距离或差异。

这些度量值用于决定哪个发送码字最有可能是原始数据。

3. **路径追踪:** Viterbi算法使用路径追踪技术来跟踪可能的状态序列,并根据度量值来选择最有可能的路径。

这个过程可以看作是在状态图上搜索最佳路径的过程。

4. **译码操作:** 根据最佳路径上的状态序列,译码器重建原始数据位。

这些数据位就是译码器的输出。

卷积码的译码是一种计算密集型的过程,通常需要高效的硬件支持,特别是在高速通信系统中。

Viterbi算法是一种复杂的算法,但它在纠错性能方面非常出色,可以大大提高数据传输的可靠性。

串行级联卷积码的差分解调译码算法本文将介绍串行级联卷积码的差分解调译码算法。

首先,我们将简要介绍卷积码的基本概念和特点,然后详细阐述串行级联卷积码的结构和特点,最后介绍差分解调译码算法的原理和实现方法。

一、卷积码的基本概念和特点卷积码是一种线性块码,它通过对信息序列进行卷积运算得到码序列。

卷积码的特点是码率低、纠错能力强,适合在无线通信、数字广播和卫星通信等领域应用。

卷积码的编码过程可以通过一个状态机来描述。

状态机的状态表示编码器的寄存器状态,状态转移表示编码器的输出。

卷积码的编码器有多种不同的结构,其中最常用的是用两个寄存器和三个异或门构成的结构,称为(2,1,3)卷积码编码器。

卷积码的解码过程是将接收到的码序列与一组备选码序列进行比较,找到与接收到的码序列最相似的备选码序列作为解码结果。

常用的解码方法有Viterbi算法和BCJR算法。

二、串行级联卷积码的结构和特点串行级联卷积码(SCCC)是一种将多个卷积码级联起来的编码结构。

它将多个卷积码串行连接起来,形成一个长卷积码。

SCCC的优点是码率可调、纠错能力强,适合在高速数据传输和数字电视等领域应用。

SCCC的编码过程是将信息序列分成若干段,每段通过一个卷积码编码器进行编码,然后将输出码序列连接起来,形成一个长码序列。

SCCC的解码过程是将接收到的码序列分成若干段,每段通过一个卷积码解码器进行解码,然后将解码结果连接起来,得到原始信息序列。

SCCC的结构有多种不同的实现方式,其中最常用的是串行级联(2,1,3)卷积码编码器。

该编码器由多个(2,1,3)卷积码编码器级联而成,每个编码器的输出作为下一个编码器的输入。

SCCC的解码器通常采用Viterbi算法进行解码。

三、差分解调译码算法的原理和实现方法差分解调译码算法是一种适用于SCCC的解调译码算法。

差分解调译码算法的基本思想是利用码序列的差分特性进行解调和译码。

差分解调译码算法的优点是解码速度快、硬件实现简单、适合应用于低功耗的移动设备中。

卷积码译码

卷积码译码是一种将编码后的数据流转换回原始数据的过程。

卷

积码是一种纠错编码方式,它将输入数据流转换为输出数据流,并在

输出流中插入冗余数据以实现数据纠错。

在卷积码译码过程中,接收

端会接收到带有噪声的编码数据,并通过对输入数据流应用卷积码解

码算法来纠正位于输入数据流中的错误。

卷积码译码主要包括软判决译码和硬判决译码两种方法。

软判决

译码是指接收端使用带有噪声的编码数据计算出每个输入位被置为1

的概率,并将该概率作为输入进入卷积码解码器中进行译码。

硬判决

译码则是指接收端对每个接收到的编码数据比特进行直接解码,得到

二进制值并将其作为输入进入卷积码解码器中进行译码。

在卷积码译码过程中,卷积码解码器通常使用Viterbi算法进行

译码。

该算法通过动态规划的方法来寻找最短路径,并从中选取最优解。

在硬判决译码中,Viterbi算法可以应用于求解输入比特误码率最低的译码结果。

而在软判决译码中,Viterbi算法可以应用于求解最大似然路径,从而得到最优译码结果。

综上所述,卷积码译码是通过使用卷积码解码算法将带有噪声的

编码数据转换回原始数据的过程。

卷积码译码中通常使用Viterbi算

法进行动态规划,找到最短路径或最大似然路径,并从中选取最优解。

卷积码的编译原理及仿真摘 要 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab 软件进行设计与仿真,并进行误码率分析。

实验原理QPSK :QPSK 是英文QuadraturePhaseShiftKeying 的缩略语简称,意为正交相移键控,是一种数字调制方式。

四相相移键控信号简称“QPSK ”。

它分为绝对相移和相对相移两种。

卷积码:又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

积码将k 个信息比特编成n 个比特,但k 和n 通常很小,特别适合以串行形式进行传输,时延小。

卷积码是在一个滑动的数据比特序列上进行模2和操作,从而生成一个比特码流。

卷积码和分组码的根本区别在于,它不是把信息序列分组后再进行单独编码,而是由连续输入的信息序列得到连续输出的已编码序列。

卷积码具有误码纠错的能力,首先被引入卫星和太空的通信中。

NASA 标准(2,1,6)卷积码生成多项式为:346134562()1()1g D D D D Dg D D D D D=++++=++++ 其卷积编码器为:输入序列++输出c1输出c2图1.1 K=7,码率为1/2的卷积码编码器维特比译码:采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。

如果接收到L 组信息比特,每个符号包括v 个比特。

接收到的Lv 比特序列与2L 条路径进行比较,汉明距离最近的那一条路径被选择为最有可能被传输的路劲。

当L 较大时,使得译码器难以实现。

维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。

它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。

下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。

BPSK调制信道卷积码的BCJR译码过程1. 引言在数字通信系统中,为了提高可靠性和传输效率,通常会采用调制和编码技术。

BPSK调制是一种常用的数字调制方式,而卷积码则是一种常用的编码方式。

BCJR (Bahl, Cocke, Jelinek, Raviv)算法是一种经典的软判决译码算法,广泛应用于卷积码的解码过程中。

本文将详细介绍BPSK调制信道卷积码的BCJR译码过程,包括相关理论背景、算法原理、步骤和实现方法等内容。

2. 背景知识2.1 BPSK调制BPSK(Binary Phase Shift Keying)是一种二进制相位调制方式,使用两个不同的相位表示二进制数据0和1。

具体而言,在BPSK调制中,将二进制数据0映射为相位为0°的载波信号,将二进制数据1映射为相位为180°(或π)的载波信号。

2.2 卷积码卷积码是一种线性时不变系统,在编码过程中利用一个或多个寄存器进行状态转移,并通过线性组合生成输出。

卷积码的编码过程是一种冗余度增加的操作,可以提高系统的抗干扰和纠错能力。

卷积码由三个参数表示:n、k和m。

其中,n表示每个码字的比特数,k表示信息比特数,m表示寄存器数。

通过这些参数,可以得到一个(n, k, m)卷积码。

2.3 BCJR算法BCJR算法是一种基于概率图模型的软判决译码算法,适用于线性时不变系统中的序列译码问题。

它利用前向和后向变量计算路径概率,并通过最大后验概率准则进行判决。

3. BCJR译码算法原理BCJR译码算法是一种迭代解码算法,主要包括前向过程、后向过程和路径更新三个步骤。

3.1 前向过程前向过程用于计算给定观测序列下每条路径的前向变量α。

首先,定义t时刻状态为s_i(i为状态索引),观测为o_t,则前向变量α在t时刻、状态s_i下的定义如下:α(t, s_i) = P(o_1, o_2, …, o_t, s_t = s_i)接着,根据递推关系计算前向变量α(t, s_i):α(t, s_i) = Σ[α(t-1, s_j) * a_ij * b_j(o_t)] (j为状态索引)其中,a_ij表示状态转移概率,b_j(o_t)表示观测到o_t时处于状态s_j的概率。