卷积码的译码

- 格式:pptx

- 大小:394.76 KB

- 文档页数:47

No.15 (2,1,3)卷积码的编码及译码摘要:本报告对于(2,1,3)卷积码原理部分的论述主要参照啜刚教材和课件,编程仿真部分绝对原创,所有的程序都是在Codeblocks 8.02环境下用C语言编写的,编译运行都正常。

完成了卷积码的编码程序,译码程序,因为对于短于3组的卷积码,即2 bit或4 bit纠错是没有意义的,所以对正确的短序列直接译码,对长序列纠错后译码,都能得到正确的译码结果。

含仿真结果和程序源代码。

如果您不使用Codeblocks运行程序,则可能不支持中文输出显示,但是所有的数码输出都是正确的。

一、 卷积码编码原理卷积码编码器对输入的数据流每次1bit 或k bit 进行编码,输出n bit 编码符号。

但是输出的分支码字的每个码元不仅于此时可输入的k 个嘻嘻有关,业余前m 个连续式可输入的信息有关,因此编码器应包含m 级寄存器以记录这些信息。

通常卷积码表示为 (n,k,m). 编码率 k r n=当k=1时,卷积码编码器的结构包括一个由m 个串接的寄存器构成的移位寄存器(成为m 级移位寄存器、n 个连接到指定寄存器的模二加法器以及把模二加法器的输出转化为穿行的转换开关。

本报告所讲的(2,1,3)卷积码是最简单的卷积码。

就是2n =,1k =,3m =的卷积码。

每次输入1 bit 输入信息,经过3级移位寄存器,2个连接到指定寄存器的模二加法器,并把加法器输出转化为串行输出。

编码器如题所示。

二、卷积码编码器程序仿真 C 语言编写的仿真程序。

为了简单起见,这里仅仅提供数组长度30 bit 的仿真程序,当然如果需要可以修改数组大小。

为了更精练的实现算法,程序输入模块没有提供非法字符处理过程,如果需要也可以增加相应的功能。

进入程序后,先提示输入数据的长度,请用户输入int (整型数)程序默认用户输入的数据小于30,然后提示输入01数码,读入数码存储与input 数组中,然后运算输出卷积码。

实验九 (2,1,5)卷积码编码译码技术一、实验目的1、掌握(2,1,5)卷积码编码译码技术2、了解纠错编码原理。

二、实验内容1、(2,1,5)卷积码编码。

2、(2,1,5)卷积码译码。

三、预备知识1、纠错编码原理。

2、(2,1,5)卷积码的工作原理。

四、实验原理/卷积码是将发送的信息序列通过一个线性的,有限状态的移位寄存器而产生的编码。

通常卷积码的编码器由K级(每级K比特)的移位寄存器和n个线性代数函数发生器(这里是模2加法器)组成。

若以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n 为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。

卷积码将k 元组输入码元编成n元组输出码元,但k和n通常很小,特别适合以串行形式进行传输,时延小。

与分组码不同,卷积码编码生成的n元组元不仅与当前输入的k元组有关,还与前面m-1个输入的k元组有关,编码过程中互相关联的码元个数为n*m。

卷积码的纠错性能随m的增加而增大,而差错率随N的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

编码器随着信息序列不断输入,编码器就不断从一个状态转移到另一个状态并同时输出相应的码序列,所以图3所示状态图可以简单直观的描述编码器的编码过程。

因此通过状态图很容易给出输入信息序列的编码结果,假定输入序列为110100,首先从零状态开始即图示a状态,由于输入信息为“1”,所以下一状态为b并输出“11”,继续输入信息“1”,由图知下一状态为d、输出“01”……其它输入信息依次类推,按照状态转移路径a->b->d->c->b->c->a输出其对应的编码结果“”。

译码方法⒈代数代数译码是将卷积码的一个编码约束长度的码段看作是[n0(m+1),k0(m+1)]线性分组码,每次根据(m+1)分支长接收数字,对相应的最早的那个分支上的信息数字进行估计,然后向前推进一个分支。

(2,1,3)卷积码的编码及译码摘要:¥本报告对于(2,1,3)卷积码原理部分的论述主要参照啜刚教材和课件,编程仿真部分绝对原创,所有的程序都是在Codeblocks 环境下用C语言编写的,编译运行都正常。

完成了卷积码的编码程序,译码程序,因为对于短于3组的卷积码,即2 bit或4 bit纠错是没有意义的,所以对正确的短序列直接译码,对长序列纠错后译码,都能得到正确的译码结果。

含仿真结果和程序源代码。

如果您不使用Codeblocks运行程序,则可能不支持中文输出显示,但是所有的数码输出都是正确的。

一、 卷积码编码原理卷积码编码器对输入的数据流每次1bit 或k bit 进行编码,输出n bit 编码符号。

但是输出的分支码字的每个码元不仅于此时可输入的k 个嘻嘻有关,业余前m 个连续式可输入的信息有关,因此编码器应包含m 级寄存器以记录这些信息。

通常卷积码表示为 (n,k,m). 编码率 k r n=(当k=1时,卷积码编码器的结构包括一个由m 个串接的寄存器构成的移位寄存器(成为m 级移位寄存器、n 个连接到指定寄存器的模二加法器以及把模二加法器的输出转化为穿行的转换开关。

本报告所讲的(2,1,3)卷积码是最简单的卷积码。

就是2n =,1k =,3m =的卷积码。

每次输入1 bit 输入信息,经过3级移位寄存器,2个连接到指定寄存器的模二加法器,并把加法器输出转化为串行输出。

编码器如题所示。

二、卷积码编码器程序仿真 C 语言编写的仿真程序。

为了简单起见,这里仅仅提供数组长度30 bit 的仿真程序,当然如果需要可以修改数组大小。

为了更精练的实现算法,程序输入模块没有提供非法字符处理过程,如果需要也可以增加相应的功能。

进入程序后,先提示输入数据的长度,请用户输入int (整型数)程序默认用户输入的数据小于30,然后提示输入01数码,读入数码存储与input 数组中,然后运算输出卷积码。

经过实验仿真,编码完全正确。

实验九 (2,1,5)卷积码编码译码技术一、实验目的1、掌握(2,1,5)卷积码编码译码技术2、了解纠错编码原理。

二、实验内容1、(2,1,5)卷积码编码。

2、(2,1,5)卷积码译码。

三、预备知识1、纠错编码原理。

2、(2,1,5)卷积码的工作原理。

四、实验原理卷积码是将发送的信息序列通过一个线性的,有限状态的移位寄存器而产生的编码。

通常卷积码的编码器由K级(每级K比特)的移位寄存器和n个线性代数函数发生器(这里是模2加法器)组成。

若以(n,k,m)来描述卷积码,其中k为每次输入到卷积编码器的bit数,n 为每个k元组码字对应的卷积码输出n元组码字,m为编码存储度,也就是卷积编码器的k元组的级数,称m+1= K为编码约束度m称为约束长度。

卷积码将k 元组输入码元编成n元组输出码元,但k和n通常很小,特别适合以串行形式进行传输,时延小。

与分组码不同,卷积码编码生成的n元组元不仅与当前输入的k元组有关,还与前面m-1个输入的k元组有关,编码过程中互相关联的码元个数为n*m。

卷积码的纠错性能随m的增加而增大,而差错率随N的增加而指数下降。

在编码器复杂性相同的情况下,卷积码的性能优于分组码。

编码器随着信息序列不断输入,编码器就不断从一个状态转移到另一个状态并同时输出相应的码序列,所以图3所示状态图可以简单直观的描述编码器的编码过程。

因此通过状态图很容易给出输入信息序列的编码结果,假定输入序列为110100,首先从零状态开始即图示a状态,由于输入信息为“1”,所以下一状态为b并输出“11”,继续输入信息“1”,由图知下一状态为d、输出“01”……其它输入信息依次类推,按照状态转移路径a->b->d->c->b->c->a输出其对应的编码结果“110101001011”。

译码方法⒈代数代数译码是将卷积码的一个编码约束长度的码段看作是[n0(m+1),k0(m+1)]线性分组码,每次根据(m+1)分支长接收数字,对相应的最早的那个分支上的信息数字进行估计,然后向前推进一个分支。

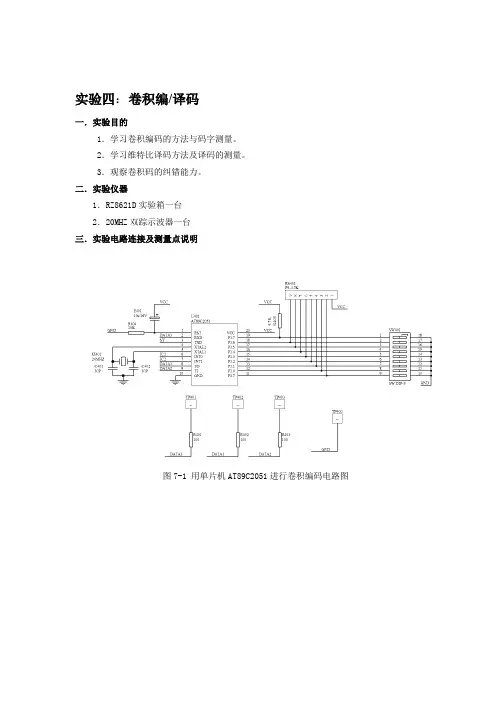

实验四:卷积编/译码一.实验目的1.学习卷积编码的方法与码字测量。

2.学习维特比译码方法及译码的测量。

3.观察卷积码的纠错能力。

二.实验仪器1.RZ8621D实验箱一台2.20MHZ双踪示波器一台三.实验电路连接及测量点说明图7-1 用单片机AT89C2051进行卷积编码电路图图7-2 用单片机AT89C2051进行维特比译码电路图差错控制编码的方法很多,卷积码是一种既能纠随机错,又能纠实发错的编码,在同样的传输速率和设备复杂的条件下,性能较优良的一种编码。

卷积码常采用维特比软判决译码,具有较好的纠错功能。

本实验为卷积码的编译码,它是由一片AT80C2051芯片用软件编程方法实现。

其编译码电路框图如下:图中各主要测量点说明如下:TP401—源码序列TP402—卷积码序列TP403—加错或不加错卷积码序列(模拟信道的传输)TP405—卷积码译码输出序列四.实验步骤及内容(一)卷积码编码1.拨线开关介绍。

用拨动开关SW401设置输入信息。

开关拨动至上面为1,下面为0。

拨动开关共9位,左起1-8位为信息位,第九位为状态位。

第九位为“1”表示无错误,第九位为“0”表示有错误。

2.信息码设置。

如上所述,信息码设置共8位,由SW401开关位置决定,例如设置信息为DCH则八位码为1101 1100。

3.信息码观察。

为了示波器上能看到周期性的信息码和编出的卷积码,本机规定在信息位第一位前加一个“1”,在末位加两个“0”。

因此信息码序列变成1 1101 110000,我们称它们为源码序列。

将示波器1通道探头接于TP401(DTAT3),便可看到该序列波形。

4.卷积编码序列手工编码。

根据源码序列和(2.1.3)卷积码编码规秩,写出卷积码编码序列。

上述源码序列的卷积码为1101 1001 0001 1001 110000。

5.无错卷积码编码序列观察。

将拨动开关第九位(状态位)置于“1”表示无错码。

示波器1通道探头接至TP402(DATA1),2通道探头接至TP403(DATA2),观察示波器上显示的波形,看看它是否与上述卷积编码的码型一致。

实验二--卷积码编码及译码实验实验二卷积码编码及译码实验一、实验目的通过本实验掌握卷积编码的特性、产生原理及方法,卷积码的译码方法,尤其是维特比译码的原理、过程、特性及其实现方法。

二、实验内容1、观察NRZ基带信号及其卷积编码信号。

2、观察帧同步信号的生成及巴克码的特性。

3、观察卷积编码信号打孔及码速率匹配方法。

4、观察接收端帧同步过程及帧同步信号。

5、观察译码结果并深入理解维特比译码的过程。

6、观察随机差错及突发差错对卷积译码的影响。

三、基本原理1、卷积码编码卷积码是一种纠错编码,它将输入的k个信息比特编成n个比特输出,特别适合以串行形式进行传输,时延小。

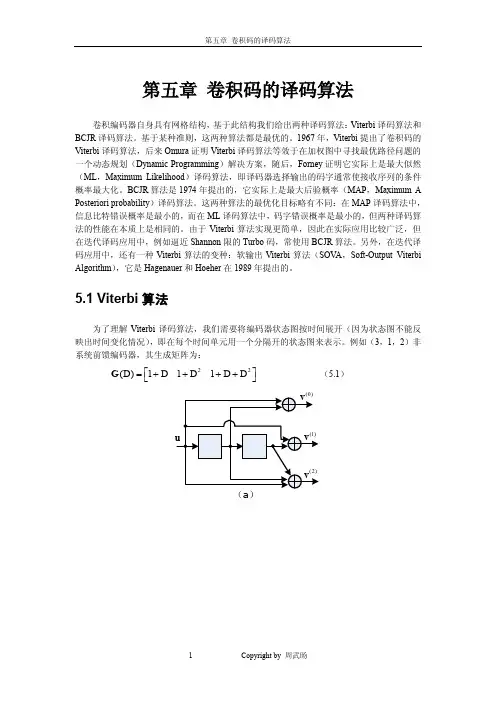

卷积码编码器的形式如图17-1所示,它包括:一个由N段组成的输入移位寄存器,每段有k 段,共Nk 个寄存器;一组n 个模2和相加器;一个由n 级组成的输出移位寄存器,对应于每段k 个比特的输入序列,输出n 个比特。

12…k 12…k …12…k12…n 卷积码输出序列信息比特一次移入k 个Nk 级移位寄存器…图17-1 卷积编码器的一般形式由图17-1可以看到,n 个输出比特不仅与当前的k 个输入信息有关,还与前(N -1)k 个信息有关。

通常将N 称为约束长度(有的书中也把约束长度定为nN 或N -1)。

常把卷积码记为:(n 、k 、N ),当k =1时,N -1就是寄存器的个数。

编码效率定义为:/c R k n (17-1)卷积码的表示方法有图解表示法和解析表示法两种:解析法,它可以用数学公式直接表达,包括离散卷积法、生成矩阵法、码生成多项式法;图解表示法,包括树状图、网络图和状态图(最的图形表达形式)三种。

一般情况下,解析表示法比较适合于描述编码过程,而图形法比较适合于描述译码。

(1)图解表示法(2)解析法下面以(2,1,3)卷积编码器为例详细讲述卷积码的产生原理和表示方法。

(2,1,3)卷积码的约束长度为3,编码速率为1/2,编码器的结构如图17-2所示。

卷积码是一种纠错编码技术,通常用于无线通信和数字通信系统中,以提高数据传输的可靠性。

卷积码的编码和译码是两个关键步骤,下面分别介绍这两个步骤:**编码:**1. **选择卷积码的参数:** 在编码之前,您需要确定卷积码的参数,包括约束长度(constraint length)、生成多项式(generator polynomial)和码率(code rate)。

这些参数将决定编码器的结构和性能。

2. **构建编码器:** 卷积码编码器通常是一个有限状态自动机(Finite State Machine,FSM)。

根据所选的生成多项式,配置编码器的状态转移图。

编码器的输入是要编码的数据位,输出是编码后的码字。

3. **编码操作:** 对每个输入位进行编码操作。

编码器的状态会根据输入位的不同而变化,从而生成不同的编码输出。

通常,每个输入位都会产生多个输出位,这是卷积码的特点之一。

4. **输出码字:** 编码器将生成的码字传送出来,以便传输或存储。

**译码:**1. **构建译码器:** 卷积码的译码器通常是使用一种称为Viterbi算法的最大似然译码方法来实现的。

译码器需要与编码器具有相同的约束长度和生成多项式。

2. **接收和测量:** 译码器接收传输的码字,并测量接收到的码字与每个可能的发送码字之间的距离或差异。

这些度量值用于决定哪个发送码字最有可能是原始数据。

3. **路径追踪:** Viterbi算法使用路径追踪技术来跟踪可能的状态序列,并根据度量值来选择最有可能的路径。

这个过程可以看作是在状态图上搜索最佳路径的过程。

4. **译码操作:** 根据最佳路径上的状态序列,译码器重建原始数据位。

这些数据位就是译码器的输出。

卷积码的译码是一种计算密集型的过程,通常需要高效的硬件支持,特别是在高速通信系统中。

Viterbi算法是一种复杂的算法,但它在纠错性能方面非常出色,可以大大提高数据传输的可靠性。

卷积码门限译码

卷积码门限译码是一种在卷积码通信系统中用于译码的技术。

卷积码是一种常用的纠错编码方式,它通过将信息序列映射到一组较长的码字,从而提供一定的错误纠正能力。

门限译码则是卷积码译码的一种方法,通过设定一个阈值来判断接收到的信号是否超过门限,从而进行译码。

在卷积码门限译码中,通常采用最大后验概率(MAP)或最大互信息(MMI)等算法进行译码。

这些算法基于接收到的信号和已知的信道特性,计算出每个码字的概率或互信息,并选择概率或互信息最大的码字作为译码结果。

门限值的选择对译码性能有着重要影响。

如果门限值设置过低,可能会导致过多的误码;如果门限值设置过高,则可能会导致译码失败。

因此,需要根据信道特性、噪声水平、卷积码的约束长度等因素来选择合适的门限值。

总的来说,卷积码门限译码是一种有效的卷积码译码方法,它在通信、雷达、声呐等领域有着广泛的应用。

卷积码的译码研究及DSP实现的开题报告一、选题背景和意义卷积码是一种广泛应用于通信领域中的码型,其通过对原始数据进行编码,以及解码器进行译码,可以大大提高传输信号的可靠性和抗干扰性。

在卷积码的译码研究中,针对不同的码率和误码率要求,可以采用不同的译码算法。

常用的译码算法包括 Viterbi 算法、 BCJR 算法等,其中 Viterbi 算法较为经典和简单,被广泛应用于卷积码的译码中。

本次研究将探究基于 Viterbi 算法的卷积码译码技术,并结合 DSP 软件和硬件平台进行实现,旨在提高传输数据的可靠性和准确性,同时也具有一定的理论研究和应用价值。

二、研究内容和方法1. 研究卷积码的基本原理和编码方法;2. 探究 Viterbi 算法在卷积码译码中的应用;3. 基于 MATLAB 环境,编写卷积码的编码和译码程序,并通过仿真验证其正确性和性能;4. 基于 DSP 软件平台,实现卷积码的编码和译码算法;5. 基于 DSP 硬件平台,实现卷积码的编码和译码算法,并通过硬件验证其性能和可靠性。

三、预期成果和意义1. 掌握卷积码的原理和编码方法,了解 Viterbi 算法在卷积码译码中的应用;2. 编写基于 MATLAB 环境的卷积码编码和译码程序,并通过仿真验证其正确性和性能;3. 实现基于 DSP 软件平台的卷积码编码和译码算法,并通过性能测试;4. 实现基于 DSP 硬件平台的卷积码编码和译码算法,并验证其可靠性和性能;5. 在卷积码译码研究领域,具有一定的理论研究和应用价值。

四、研究进度安排1. 搜集相关文献资料,了解卷积码和 Viterbi 算法的基本原理和应用场景;2. 完成卷积码的编码和译码程序,并通过仿真验证其正确性和性能;3. 基于 DSP 软件平台,实现卷积码编码和译码算法;4. 基于 DSP 硬件平台,实现卷积码编码和译码算法,并验证其可靠性和性能;5. 撰写毕业论文,完成论文答辩。

卷积码-Viterbi译码卷积码在一个二进制分组码(n,k)当中,包含k个信息位,码组长度为n,每个码组的(n-k)个校验位仅与本码组的k个信息位有关,而与其它码组无关。

为了达到一定的纠错能力和编码效率(=k/n),分组码的码组长度n通常都比较大。

编译码时必须把整个信息码组存储起来,由此产生的延时随着n的增加而线性增加。

为了减少这个延迟,人们提出了各种解决方案,其中卷积码就是一种较好的信道编码方式。

这种编码方式同样是把k个信息比特编成n个比特,但k和n通常很小,特别适宜于以串行形式传输信息,减小了编码延时。

与分组码不同,卷积码中编码后的n个码元不仅与当前段的k个信息有关,而且也与前面(N-1)段的信息有关,编码过程中相互关联的码元为nN个。

因此,这N时间内的码元数目nN通常被称为这种码的约束长度。

卷积码的纠错能力随着N 的增加而增大,在编码器复杂程度相同的情况下,卷段积码的性能优于分组码。

另一点不同的是:分组码有严格的代数结构,但卷积码至今尚未找到如此严密的数学手段,把纠错性能与码的结构十分有规律地联系起来,目前大都采用计算机来搜索好码。

下面通过一个例子来简要说明卷积码的编码工作原理。

正如前面已经指出的那样,卷积码编码器在一段时间内输出的n位码,不仅与本段时间内的k位信息位有关,而且还与前面m段规定时间内的信息位有关,这里的m=N-1通常用(n,k,m)表示卷积码(注意:有些文献中也用(n,k,N)来表示卷积码)。

图1就是一个卷积码的编码器,该卷积码的n = 2,k = 1,m = 2,因此,它的约束长度nN = n×(m+1) = 2×3 = 6。

图1 (2,1,2)卷集码编码器在图1中,与为移位寄存器,它们的起始状态均为零。

、与、、之间的关系如下:(1)假如输入的信息为D = [11010],为了使信息D全部通过移位寄存器,还必须在信息位后面加3个零。

表1列出了对信息D进行卷积编码时的状态。

(2,1,2)卷积码的译码设计前⾔卷积码是由伊莱亚斯(Elias)于1954 年⾸先提出来的。

它充分利⽤了各组之间的相关性,本组的信息元不但决定本组的监督元,⽽且也参与决定以后若⼲组的监督元。

同时在译码过程中,不但从该时刻所收到的码组中提取译码信息,⽽且还利⽤以后若⼲时刻内所收到的码组来提取有关信息。

⽆论从理论上还是实际上均已证明其性能优于线性分组码。

近年来众多有关卷积码研究结果表明,卷积码最有希望实现⾹农信道编码定理。

但卷积码在译码理论及实际应⽤较为复杂,这些缺点限制了其进⼀步发展和应⽤。

维特⽐译码算法由维特⽐(Viterbi)1964年提出,算法实质是最⼤似然译码,但它利⽤了编码⽹格图的特殊结构,在⽹格图中选择⼀条路径,使相应的译码序列与接收到的序列之间的汉明距(即量度)最⼩的⼀种最⼤似然译码⽅法,从⽽⼤⼤降低了计算的复杂性。

⽬前,第三代移动通信系统(3G) 在我国已经开始紧锣密⿎地实施,它带来的⾼速度、⾼品质的⽆线通信服务,将使我们领略到信息技术的⽆穷魅⼒。

信道纠错编码技术作为保证信息可靠传输的技术,在3G各系统中⼴泛采⽤,并且我们现在所使⽤的第⼆代移动通信系统,如GSM、 CDMA 通信系统,还有卫星与空间通信系统⼴泛采⽤了卷积码信道编、译码技术。

本次设计将以(2,1,2)卷积码为例,通过单⽚机,实现卷积码的译码,借助RS232完成单⽚机与单⽚机、单⽚机与计算机的串⼝通信,借助7279完成键盘扫描和数码管显⽰。

第⼀章系统组成及⼯作原理本次设计的(2,1,2)卷积码的译码由89C52单⽚机为⼯具,接收来⾃另⼀单⽚机或计算机的编码信息,通过7279的键盘扫描和数码管显⽰功能可以⽅便地观察到单⽚机接收的信息和译码结果。

其系统框图如下图1-1所⽰。

MAX232芯⽚能实现EIA-RS-232C的正负电压与TTL的⾼低电平之间的转换,通过它能够⽅便实现单⽚机与单⽚机、单⽚机与计算机间的串⼝通信。

HD7279是⼀⽚具有串⾏接⼝的, 可同时驱动8位共阴极数码管的智能显⽰驱动芯⽚, 该芯⽚同时还可连接多达64键的键盘矩阵,单⽚即可独⽴完成显⽰、键盘接⼝的全部功能。