Quartus_II_时序仿真步骤-余华-2014-10-14

- 格式:pdf

- 大小:421.89 KB

- 文档页数:14

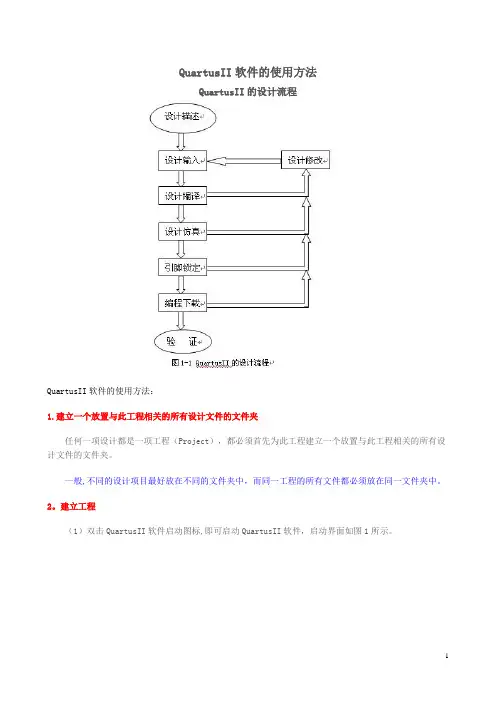

QuartusII软件的使用方法QuartusII的设计流程QuartusII软件的使用方法:1.建立一个放置与此工程相关的所有设计文件的文件夹任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的所有设计文件的文件夹。

一般,不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。

2。

建立工程(1)双击QuartusII软件启动图标,即可启动QuartusII软件,启动界面如图1所示。

(2)选择菜单File→New Preject Wizard命令,即弹出“工程设置”对话框(图2),以此来建立新的工程。

(3)在单击“next”后,出现了设置工程的基本信息,如图3所示。

完成图3中基本信息的输入后,单击图3中的“finish ”按钮。

3。

建立文件当工程建立好以后,我们就可以建立设计文件。

下面我们以一个半加器的VHDL的设计,来介绍在QuartusII如何实现VHDL语言输入。

(1)建立文件。

单击“File”菜单下的“New”命令,在弹出“New”对话框如图4所示。

在“Device Design Files”页面下双击“VHDL File”选项后建立新文件,如图5所示.图5 VHDL文本编辑窗口(2)输入程序。

在图1-11中输入半加器的VHDL程序,如图6所示.(3)保存文件.单击保存文件按钮,将输入的VHDL语言程序保存为half_add.vhd文件,注意后缀名是。

vhd,单击“保存”按钮即可保存文件,如图7.4。

编译工程(1)选择目标芯片。

单击“Assigments"菜单下的“device”命令,在弹出的对话框中按照图8进行设置。

设置完后单击“finish"。

图1-29图8(2)编译工程。

在图1—11中单击水平工具条上的编译按钮,或选择菜单Processing下的Start Complilation,开始编译。

如果编译过程出现错误,要将错误改正,保存后再次编译,直到编译无错误为止。

6.3 Quartus II操作指南6.3.1简介Altera技术领先的Quartus II设计软件配合一系列可供客户选择的IP核,可使设计人员在开发和推出FPGA、CPLD和结构化ASIC设计的同时,获得无与伦比的设计性能、一流的易用性以及最短的市场推出时间。

这是设计人员首次将FPGA移植到结构化ASIC 中,能够对移植以后的性能和功耗进行准确的估算。

Quartus II软件支持VHDL和Verilog硬件描述语言(HDL)的设计输入、基于图形的设计输入方式以及集成系统级设计工具。

Quartus II软件可以将设计、综合、布局和布线以及系统的验证全部都整合到一个无缝的环境之中,其中还包括和第三方EDA工具的接口。

Quartus II的主要特性有:<1>基于模块的设计方法提供工作效率<2>更快集成IP<3>在设计周期的早期对I/0引脚进行分配和确认<4>存储器编译器<5>支持CPLD、FPGA和基于HardCopy 的ASIC<6>使用全新的命令行和脚本功能自动化设计流程<7>高级教程帮助深入了解Quartus II的功能特性。

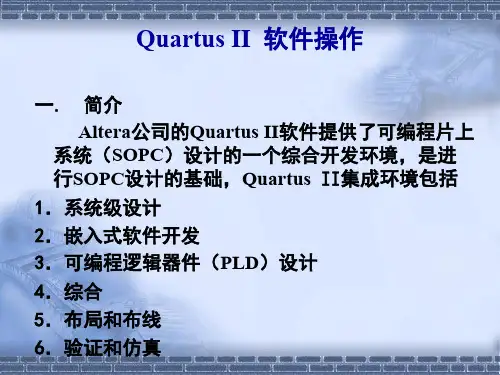

Altera公司的Quartus II软件提供了可编程片上系统(SOPC)设计的一个综合开发环境,是进行SOPC设计的基础。

Quartus II集成环境包括以下内容:系统级设计,嵌入式软件开发,可编程逻辑器件(PLD)设计,综合,布局和布线,验证和仿真。

Quartus II设计软件根据设计者需要提供了一个完整的多平台开发环境,它包括整个FPGA和CPLD设计阶段的解决方案。

有关Quartus II的典型设计流程如图6-43所示。

1图6-43 Quartus II的典型设计流程此外,Quartus II软件为设计流程的每个阶段提供了Quartus II图形用户界面、EDA 工具界面和命令行界面。

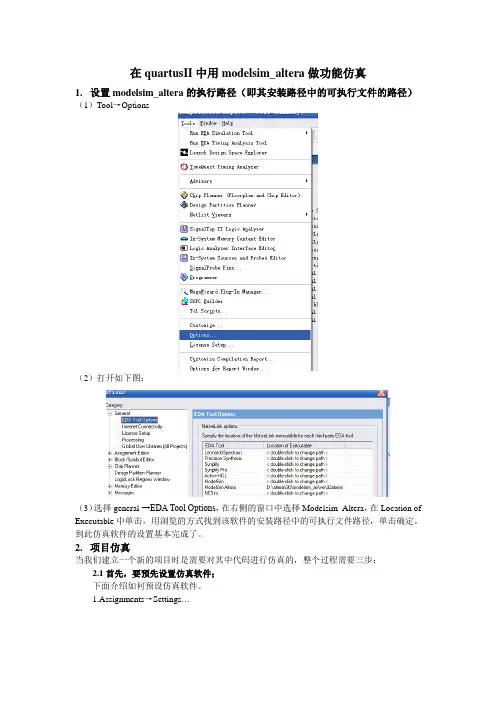

在quartusII中用modelsim_altera做功能仿真1.设置modelsim_altera的执行路径(即其安装路径中的可执行文件的路径)(1)Tool→Options(2)打开如下图:(3)选择general →EDA Tool Options,在右侧的窗口中选择Modelsim_Altera,在Location of Executable中单击,用浏览的方式找到该软件的安装路径中的可执行文件路径,单击确定。

到此仿真软件的设置基本完成了。

2.项目仿真当我们建立一个新的项目时是需要对其中代码进行仿真的,整个过程需要三步:2.1首先,要预先设置仿真软件;下面介绍如何预设仿真软件。

1.Assignments→Settings…2.打开如下界面3选择“Simulation”,右侧设置按上图设置。

2.2其次,仿真之前需要编写测试平台,测试平台有两种的方法:●直接建立XX.v文件●在quartusII中自动生成测试平台模板文件,文件为XX.vt文件下面介绍如何自动生成测试平台模板文件。

1.Processing→Start→Start Test Bench Template Writer注意:要生成testbench模板的前提条件是为项目选择预用的仿真软件,然后模块必须编译成功。

Testbench模板生成后的默认路径为:项目目录\simulation\modelsim\项目名.vt(因为刚才在预设置仿真软件时的“Output Directory”选择的是默认的值simulation\modelsim)。

2.对于自动生成的测试平台模版需要打开修改测试激励信号,这里不做介绍,很简单的。

2.3改写完后要在项目里添加测试平台文件到项目里。

1.Assignments→Settings…2.在打开界面做如下操作:(1)选择“Compile test bench”,然后单击“Test Benches…”(2)打开下面的窗口(3)单击“New”打开下面的窗口,且按图中填写相关信息这个窗口是用来输入testbench的资料和选择testbench的路径的。

仿真工具栏的使用仿真的目的:是通过设置激励(输入)信号,运行后,分析输出信号;通过观察,输入与输出信号之间的逻辑关系,验证电路设计的正确性。

QuartusII仿真常有两种模式:功能仿真(functional)和时序仿真(Timing)。

区别在于,时序仿真结果包含了硬件的延时特征。

仿真模式的选择,可通过Assignment/Settings…菜单,在弹出的窗口(如图2-20)中,选择Category栏下的Simulator Settings项,然后设置Simulation mode为funtional(功能仿真)或timing(时序仿真)来实现。

激励(输入)信号的设置,必须尽可能的反映实际电路工作可能出现的所有情况。

这样的仿真才有实际意义。

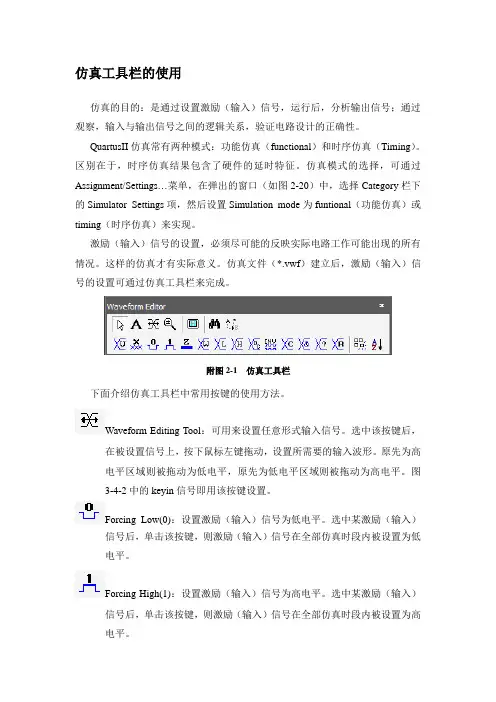

仿真文件(*.vwf)建立后,激励(输入)信号的设置可通过仿真工具栏来完成。

附图2-1 仿真工具栏下面介绍仿真工具栏中常用按键的使用方法。

Waveform Editing Tool:可用来设置任意形式输入信号。

选中该按键后,在被设置信号上,按下鼠标左键拖动,设置所需要的输入波形。

原先为高电平区域则被拖动为低电平,原先为低电平区域则被拖动为高电平。

图3-4-2中的keyin信号即用该按键设置。

Forcing Low(0):设置激励(输入)信号为低电平。

选中某激励(输入)信号后,单击该按键,则激励(输入)信号在全部仿真时段内被设置为低电平。

Forcing High(1):设置激励(输入)信号为高电平。

选中某激励(输入)信号后,单击该按键,则激励(输入)信号在全部仿真时段内被设置为高电平。

High Impedance(Z) :设置激励(输入)信号为高阻状态。

选中某激励(输入)信号后,单击该按键,则激励(输入)信号在全部仿真时段内被设置为高阻状态。

Invert:信号取反。

选中某激励(输入)信号后,单击该按键,则激励(输入)信号在全部仿真时段内,状态取反;原先为高电平则变为低电平,原先为低电平则变为高电平。

实验二十进制计数器实验该实验将使用Verilog 硬件描述语言在DE2-70 开发平台上设计一个基本时序逻辑电路——1 位十进制计数器。

通过这个实验,读者可以了解使用Quartus 工具设计硬件的基本流程以及使用Quartus II 内置的工具进行仿真的基本方法和使用SignalTap II 实际观察电路运行输出情况。

SignalTap II 是Quartus 工具的一个组件,是一个片上的逻辑分析仪,可以通过JTAG 电缆将电路运行的实际输出传回Quartus 进行观察,从而省去了外界逻辑分析仪时的很多麻烦。

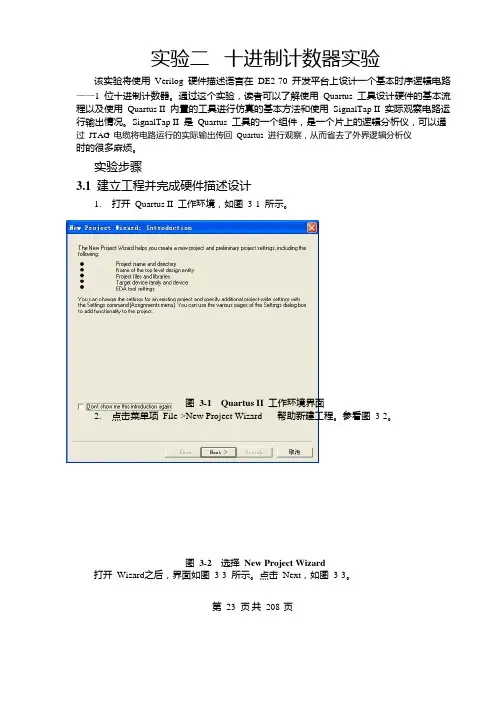

实验步骤3.1建立工程并完成硬件描述设计1. 打开Quartus II 工作环境,如图3-1 所示。

图3-1 Quartus II工作环境界面2. 点击菜单项File->New Project Wizard 帮助新建工程。

参看图3-2。

图3-2 选择New Project Wizard打开Wizard 之后,界面如图3-3 所示。

点击Next,如图3-3。

第23 页共208 页图3-3 New Project Wizard界面3. 输入工程工作路径、工程文件名以及顶层实体名。

这次实验会帮助读者理解顶层实体名和工程名的关系,记住目前指定的工程名与顶层实体名都是Counter10,输入结束后,如图3-4 所示。

点击Next。

图3-4输入设计工程信息4. 添加设计文件。

界面如图3-5 所示。

如果用户之前已经有设计文件(比如.v 文件)。

那么再次添加相应文件,如果没有完成的设计文件,点击Next 之后添加并且编辑设计文件。

图3-5添加设计文件5. 选择设计所用器件。

由于本次实验使用Altera 公司提供的DE2-70 开发板,用户必须选择与DE2-70 开发板相对应的FPGA 器件型号。

在Family 菜单中选择Cyclone II,Package 选FBGA,Pin Count 选896,Speed grade 选6,确认Available devices 中选中EP2C70F896C6,如图3-6。

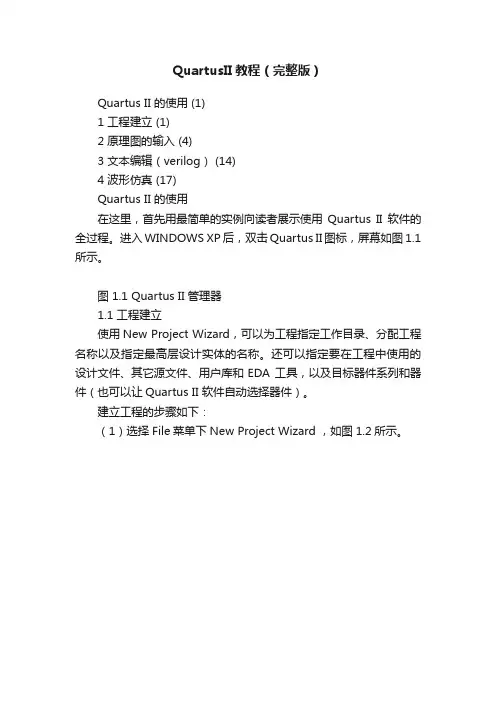

QuartusII教程(完整版)Quartus II 的使用 (1)1 工程建立 (1)2 原理图的输入 (4)3 文本编辑(verilog) (14)4 波形仿真 (17)Quartus II 的使用在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。

进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。

图 1.1 Quartus II 管理器1.1 工程建立使用New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。

还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。

建立工程的步骤如下:(1)选择File菜单下New Project Wizard ,如图1.2所示。

图 1.2 建立项目的屏幕(2)输入工作目录和项目名称,如图1.3所示。

可以直接选择Finish,以下的设置过程可以在设计过程中完成。

图 1.3 项目目录和名称(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。

图 1.4 加入设计文件(4)选择设计器件,如图1.5所示。

图 1.5 选择器件(5)选择第三方EDA综合、仿真和时序分析工具,如图1.6所示。

图 1.6 选择EDA 工具(6)建立项目完成,显示项目概要,如图1.7所示。

图 1.7 项目概要1.2 原理图的输入原理图输入的操作步骤如下:(1)选择File 菜单下New ,新建图表/原理图文件,如图1.8 所示。

图 1.8 新建原理图文件(2)在图1.9的空白处双击,屏幕如图1.10所示:(3)在图1.10的Symbol Name 输入编辑框中键入dff后,单击ok按钮。

此时可看到光标上粘着被选的符号,将其移到合适的位置(参考图1.11)单击鼠标左键,使其固定;(4)重复(2)、(3)步骤,给图中放一个input、not、output 符号,如图1.11所示;在图1.11中,将光标移到右侧input 右侧待连线处单击鼠标左键后,再移动到D触发器的左侧单击鼠标左键,即可看到在input和D触发器之间有一条线生成;图1.9 空白的图形编辑器图1.10 选择元件符号的屏幕图1.11 放置所有元件符号的屏幕(5)重复(4)的方法将DFF和output连起来,完成所有的连线电路如图1.12所示;(6)在图1.12中,双击input_name使其衬低变黑后,再键入clk,及命名该输入信号为clk,用相同的方法将输出信号定义成Q;如图1.13所示。

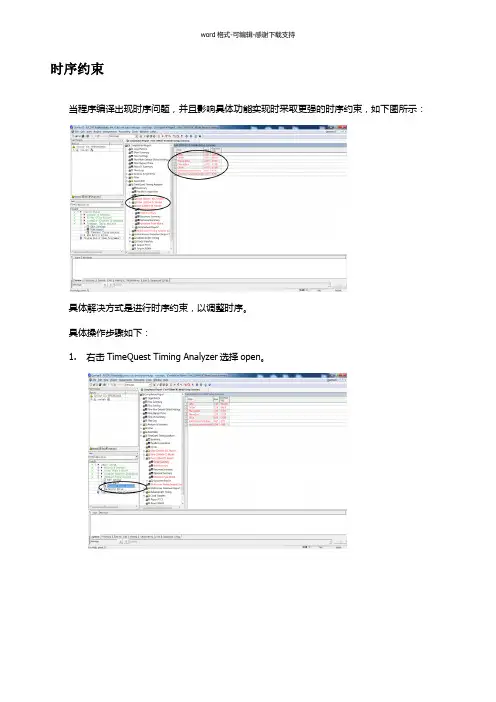

时序约束当程序编译出现时序问题,并且影响具体功能实现时采取更强的时序约束,如下图所示:具体解决方式是进行时序约束,以调整时序。

具体操作步骤如下:1.右击TimeQuest Timing Analyzer选择open。

打开TimeQuest Timing Analyzer如下图所示。

右击Create Timing Netlist,生成网表如下图所示。

2.生成网表后进行时序约束。

在TimeQuest Timing Analyzer菜单栏下选择constraints下的Create Clock。

依次进行时钟设置,Targets需要进行选择。

设置完毕如下图,点击Run设置完毕。

在次选择TimeQuest Timing Analyzer菜单栏下选择constraints下的Create Generated Clock,对约束时钟进行设置。

设置完毕点击Run。

3.运行完毕后右击Write SDC File选择Start,如下图将文件保存为comLogic.out。

扩展名为.sdc的文件。

4.将3步骤中产生的文件加入工程,重新编译。

编译结果如下图,可以看到红色文字全部消失。

则时序约束完成。

5.但是在实际应用过程中此时有可能在Fast 1200mV 0C Model的 Hold Summary仍然出现问题(本次结果没有出现问题)如下图所示:此时需要将主菜单下的Assignments的setting进行设置。

由于芯片工艺等问题需要更强的约束,如图所示需要将Fitter Setting中的Optimize multi-corner timing勾选上等操作。

这样简单的时序约束就可以完成。

练习1.2QuartusII仿真工具的使用练习1.2 Quartus II仿真工具的使用1.首先,打开Quartus II开发软件,新建一个名称为Encoder4_2工程(路径可自行指定,如D:\Design_Project\Altera\Practice1_2),选择器件类型EP2C8Q208C8。

(有关工程的创建,请参考练习1.1)。

2.在菜单栏中,选择“File”->“New”,新建一个名为Encoder4_2.v(或是Encoder4_2.vhd)的文件,编辑好代码并保存,并将此文件添加至工程。

(详细步骤请参见练习1.1)3.接下来,选择菜单栏的“Processing”->“Analyze Current File”,或者在工具栏中找到快捷键并单击,于是Quartus II便开始了分析和综合,以检查代码的语法正确性,并得到电路的逻辑网表。

4.接下来,我们将新建一个向量波形文件,并通过此文件实现对我们编写的源文件的仿真。

5.在菜单栏中,选择“File”->“New”,在如下所示的窗口中,我们在“V erification/DebuggingFiles”的子目录中,选中“V ector Waveform File”,然后点击下方的“OK”按钮。

6.新建的*.vwf文件的视图如下所示,接下来我们需要在这个文件里添加待观测的仿真信号。

我们在其左侧空白处双击,见图。

7.在弹出的“Insert Node or Bus”窗口中,我们点击“Node Finder”按钮。

8.在如下窗口中,我们保持“Named”一栏中的“*”不变,在“Filter”一栏中选择“Pins :all”,然后单击其后的“List”按钮。

9.我们在找到的信号列表中(左侧方框中),选中我们想要添加的信号(按住ctrl键可多选),并点击连个方框中间的按钮,如下图所示。

10.我们在如下图所示的对话框中点击“OK”按钮。

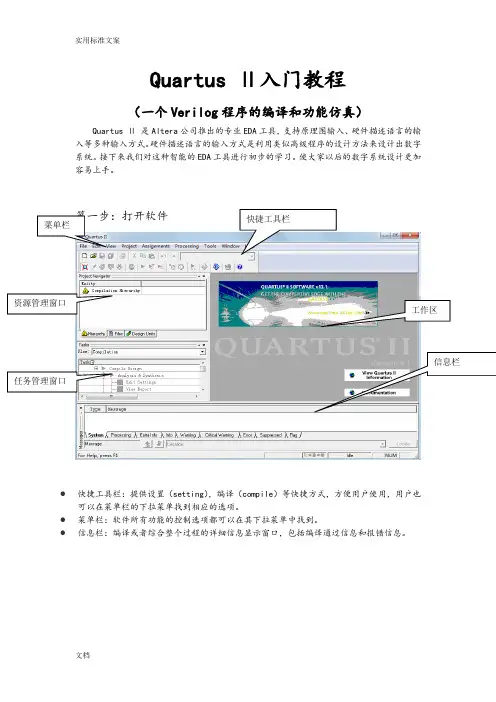

Quartus Ⅱ入门教程(一个Verilog 程序的编译和功能仿真)Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

接下来我们对这种智能的EDA 工具进行初步的学习。

使大家以后的数字系统设计更加容易上手。

●快捷工具栏:提供设置(setting ),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

● 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

第二步:新建工程(file>new Project Wizard1 工程名称:2添加已有文件(没有已有文件的直接跳过next )3 选择芯片型号(我们选择MAX3000A 系列下的EPM3256AQC208-10芯片) (注:如果不下载到开发板上进行测试,这一步可以不用设置)4 选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None ,然后next )5 工程建立完成(点finish )第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序以实现一个与门和或门为例,Verilog描述源文件如下:module test(a,b,out1,out2);input a,b;Output out1,out2;assign out1=a&b;assign out2=a | b;endmodule然后保存源文件;第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis))点击确定完成语法检查第六步:(锁定引脚,点击工具栏的(pin planner ))(注:如果不下载到开发板上进行测试,引脚可以不用分配)双击location各个端口的输入输出第七步:整体编译(工具栏的按钮(start Complilation))第八步:功能仿真(直接利用quratus进行功能仿真)1将仿真类型设置为功能仿真(Assignments>setting>Simulator Settings>下拉>Function)2 建立一个波形文件:(new>Vector Waveform File )然后导入引脚(双击Name 下面空白区域>Node Finder>list>点击):接下来设置激励信号(单击>选择>Timing>Multiplied by 1)设置b 信号源的时候类同设置a 信号源,最后一步改为然后要先生成仿真需要的网表(工具栏processing>Generate Functional Simulation Netlist)接下来开始仿真(仿真前要将波形文件保存,点击工具栏开始仿真):实用标准文案文档观察波形,刚好符合我们的逻辑。

基于Quartus II 9.0 的数字电路设计操作过程图解一.Quartus II 9.0 启动◆方法一、直接双击桌面上的图标,可以打开Quartus II 9.0 软件;◆方法二、执行:【开始】→【程序】→【Altera】→【Quartus II 9.0】→【Quartus II 9.0 TalkBack Install】菜单命令,可以打开软件。

◆启动软件后,若你的电脑没有连接到Internet互联网,会出现如下图所示的提示,提示你没有连接到Altera的官方网站,将无法获得更新的资源。

点击〖确定〗继续,因为这不影响软件的正常使用。

◆若你的电脑已经正常连接到Internet互联网,则在打开软件时就不会出现以上的提示,并且可以通过软件界面右下方的两个图标:,直接连接到Altera公司的官方网站,以便获取更多的信息和资源。

二.Quartus II 9.0软件界面Quartus II 9.0软件的默认启动界面如下图所示,由标题栏、菜单栏、常用工具栏、资源管理窗口、程序编译或仿真运行状态的显示窗口、程序编译或仿真的结果显示窗口和工程编辑工作区组成。

三.Quartus II 9.0软件使用1. 新建项目工程使用QuartusII9.0设计一个数字逻辑电路,并用时序波形图对电路的功能进行仿真,同时还可以将设计正确的电路下载到可编程的逻辑器件(CPLD、FPGA)中。

因软件在完成整个设计、编译、仿真和下载等这些工作过程中,会有很多相关的文件产生,为了便于管理这些设计文件,我们在设计电路之前,先要建立一个项目工程(New Project),并设置好这个工程能正常工作的相关条件和环境。

建立工程的方法和步骤如下:(1)先建一个文件夹。

就在电脑本地硬盘找个地方建一个用于保存下一步工作中要产生的工程项目的文件夹,注意:文件夹的命名及其保存的路径中不能有中文字符。

(2)再开始建立新项目工程,方法如右图点击:【File】菜单,选择下拉列表中的【New Project Wizard...】命令,打开建立新项目工程的向导对话框。

大家是不是被modelsim折磨的死去活来呢?是不是觉得在没有人指点下,学习modelsim就象是黑暗中摸索,everyting is black!.如果我们能直接在quartus中调用modelsim那么我们就可以直接得到我们的仿真波形,不用在modelsim 中建立工程,加入文件,编译,加载波形,运行等等烦琐的工序,而且后仿的时候还经常会出现找不到库的情况,这对出学者来说更是郁闷的要死。

直接调用可以进行rtl级仿真和门级仿真。

一个前仿一个后仿。

因此为了方便大家我特意研究了一下如何实现直接调用。

以下是结论。

在ISE环境中。

1,edit->preferences:ise General->Intergrated tools设置:Model Tech Simulator: C:\Modeltech_6.0\win32\modelsim.exe(看你装在哪里了)2,在Sources in Project窗口里的器件名称上单击左键。

然后双击:Compile HDL Simulation Library3,建立testbench。

方法:Project->new source. vhdl 是:VHDL module verilog hdl 是:verilog test fixture. 4,单击testbench 文件,就可以看到下面框框里的四个仿真级别。

双击分别进行仿真。

5。

用眼睛看modelsim 出来的波形。

在Quartus 中。

1,我的电脑->属性->高级->环境变量.在系统变量里增加:QUARTUS_INIT_PATHC:\Modeltech_6.0\win32 (看你装在哪里了)而在[转帖]引用利用ModelSim进行的功能仿真,综合后仿真,时序仿真中提到如下方法:1.工程编译成功后,自动启用ModelSim来运行门级仿真,前提是要在Quartus II的Options中设置好ModelSim 的路径(和有些参考PDF上说的环境变量好像无关,至少我用的Quartus II 9.0 Web Edtion是这样的)具体方法是,进入Quartus9.0->Tools->Options,在Categroy里选中General下的EDA Tool Options,在ModelSim右边的Location ofExecutable中双击来改变路径,就并且在工程中设置了自动启动ModelSim,就可以自动启用了。

Quartus II 的使用 (1)1 工程建立 (1)2 原理图的输入 (4)3 文本编辑(verilog) (14)4 波形仿真 (17)Quartus II 的使用在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。

进入WINDOWS XP后,双击Quartus II图标,屏幕如图1。

1所示。

图 1.1 Quartus II 管理器1.1 工程建立使用New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。

还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。

建立工程的步骤如下:(1)选择File菜单下New Project Wizard ,如图1。

2所示.图1。

2 建立项目的屏幕(2)输入工作目录和项目名称,如图1。

3所示.可以直接选择Finish,以下的设置过程可以在设计过程中完成。

图1。

3 项目目录和名称(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1。

4所示。

图1。

4 加入设计文件(4)选择设计器件,如图1。

5所示。

图 1.5 选择器件(5)选择第三方EDA综合、仿真和时序分析工具,如图1.6所示。

图 1.6 选择EDA 工具(6)建立项目完成,显示项目概要,如图1.7所示。

图1。

7 项目概要1.2 原理图的输入原理图输入的操作步骤如下:(1)选择File 菜单下New ,新建图表/原理图文件,如图1.8 所示。

图 1.8 新建原理图文件(2)在图1.9的空白处双击,屏幕如图1。

10所示:(3)在图1。

10的Symbol Name 输入编辑框中键入dff后,单击ok按钮。

此时可看到光标上粘着被选的符号,将其移到合适的位置(参考图1。

11)单击鼠标左键,使其固定;(4)重复(2)、(3)步骤,给图中放一个input、not、output 符号,如图1。

Q u a r t u s I I软件的使用入门4.1Quartus II 简介Quautus II是Altera 公司的综合性PLD开发软件,支持原理图、VHDL、Verilog-HDL以及AHDL等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整的PLD设计流程。

它支持Altera的IP核,包含了LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性、加快了设计速度。

对EDA第三方工具的良好支持也使用户可以在设计流程的各个阶段使用熟悉的第三方EDA工具。

在本教程中使用的Quartus II的版本为5.0 。

4.1.1 设计工作流程用户首先对所做项目进行设计,明确设计目的、设计要求。

然后利用原理图输入方式或文本输入方式进行设计输入。

输入完成后进行编译,若编译过程中发现错误,则应检查设计输入以修改错误,直至没有错误产生。

编译完成后进行仿真,检查是否达到了设计要求,若未达到要求,需重新检查设计输入及编译过程,不断迭代、收敛直至满足设计要求。

最后将设计配置到目标器件中进行硬件验证与测试。

4.1.2 Quartus II 的图形用户界面Quartus II 的图形用户界面如图所示,从图中可以看出共有以下几个子窗口。

编辑输入窗口项目导航窗口状态窗口消息窗口图Quartus II软件的图形用户界面1.Project navigator 项目导航窗口项目导航窗口包括3个可以切换的标签:Hierarchy标签用于层次显示,提供了逻辑单元、寄存器、存储器使用等信息;File和Design Units 提供了工程文件和设计单元的列表。

2.编辑输入窗口设计输入的主窗口,无论原理图还是硬件描述语言编译、仿真的报告都显示在这里。

3.Status窗口状态窗口,用以显示各系统运行阶段的进度。

4.Message窗口消息窗口,实时提供系统消息、警告和错误等信息。