DSP课程设计报告

- 格式:doc

- 大小:1.54 MB

- 文档页数:17

dsp简单课程设计一、教学目标本课程旨在让学生了解和掌握DSP(数字信号处理器)的基本原理和应用,培养学生对DSP技术的兴趣和热情。

知识目标:使学生掌握DSP的基本概念、工作原理和主要性能指标;了解DSP 在不同领域的应用,如通信、音视频处理、工业控制等。

技能目标:通过实践操作,培养学生使用DSP芯片进行程序设计和系统应用的能力;使学生能够运用DSP技术解决实际问题,提高创新能力。

情感态度价值观目标:培养学生对新技术的敏感度,增强其对DSP技术的自信心和责任感;激发学生对电子科技和自动化的兴趣,培养其积极向上的学习态度。

二、教学内容本课程的教学内容主要包括DSP的基本原理、DSP芯片的结构与工作原理、DSP程序设计方法和DSP应用实例。

1.DSP基本原理:介绍DSP的定义、分类和发展历程,使学生了解DSP技术的基本概念。

2.DSP芯片结构与工作原理:详细讲解DSP芯片的内部结构、工作原理和主要性能指标,以便学生能够深入理解DSP的运作方式。

3.DSP程序设计方法:教授DSP的编程语言、程序设计流程和调试技巧,使学生具备实际的编程能力。

4.DSP应用实例:分析DSP技术在通信、音视频处理、工业控制等领域的应用实例,帮助学生了解DSP技术的广泛应用。

三、教学方法为了提高教学效果,本课程将采用讲授法、讨论法、案例分析法和实验法等多种教学方法。

1.讲授法:通过教师的讲解,使学生掌握DSP的基本原理和应用。

2.讨论法:学生就DSP技术的相关问题进行讨论,培养学生的思考能力和团队协作精神。

3.案例分析法:分析DSP技术在实际应用中的案例,帮助学生更好地理解DSP技术的价值和应用前景。

4.实验法:安排学生进行DSP实验,锻炼学生的动手能力,提高其对DSP技术的实际应用能力。

四、教学资源为了保证教学效果,我们将准备以下教学资源:1.教材:选用权威、实用的DSP教材,为学生提供系统、全面的学习资料。

2.参考书:提供相关的DSP技术参考书籍,丰富学生的知识储备。

dsp综合设计课程设计报告一、教学目标本课程的教学目标是使学生掌握DSP(数字信号处理器)综合设计的基本理论和实践技能。

通过本课程的学习,学生应能够:1.知识目标:理解DSP的基本概念、原理和应用;熟悉DSP芯片的内部结构和编程方法;掌握DSP算法的设计和实现。

2.技能目标:能够使用DSP芯片进行数字信号处理的设计和实现;具备DSP程序的编写和调试能力;能够进行DSP系统的故障诊断和优化。

3.情感态度价值观目标:培养学生对DSP技术的兴趣和热情,提高学生的问题解决能力和创新意识,使学生认识到DSP技术在现代社会中的重要性和应用价值。

二、教学内容本课程的教学内容主要包括DSP的基本理论、DSP芯片的内部结构和工作原理、DSP程序的设计和调试方法、DSP应用系统的设计和实现等。

具体包括以下几个部分:1.DSP的基本概念和原理:数字信号处理的基本概念、算法和特点;DSP芯片的分类和特点。

2.DSP芯片的内部结构:了解DSP芯片的内部结构和工作原理,包括CPU、内存、接口、外设等部分。

3.DSP程序的设计和调试:学习DSP程序的设计方法,包括算法描述、程序编写和调试技巧。

4.DSP应用系统的设计和实现:掌握DSP应用系统的设计方法,包括系统架构、硬件选型、软件开发和系统测试等。

三、教学方法为了实现本课程的教学目标,我们将采用多种教学方法,包括讲授法、案例分析法、实验法等。

具体方法如下:1.讲授法:通过教师的讲解,使学生掌握DSP的基本理论和原理,引导学生理解DSP技术的核心概念。

2.案例分析法:通过分析具体的DSP应用案例,使学生了解DSP技术的实际应用,培养学生的实际操作能力。

3.实验法:通过实验操作,使学生熟悉DSP芯片的使用方法和编程技巧,提高学生的实践能力。

四、教学资源为了支持本课程的教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:选择一本合适的教材,作为学生学习的基础资料,提供系统的DSP知识。

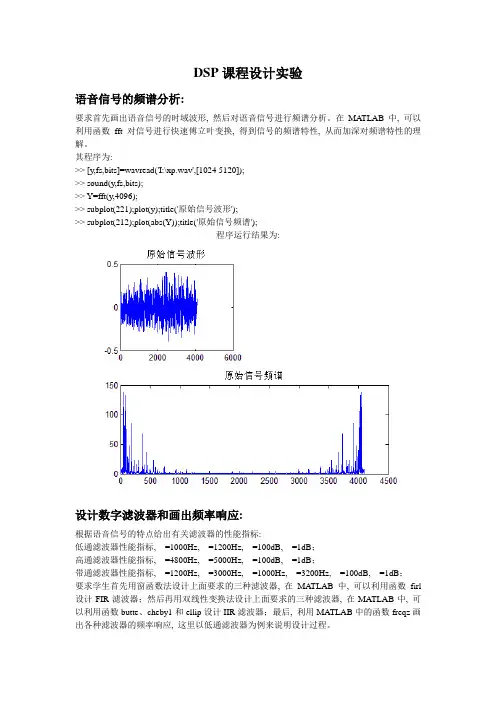

DSP课程设计实验语音信号的频谱分析:要求首先画出语音信号的时域波形, 然后对语音信号进行频谱分析。

在MATLAB中, 可以利用函数fft对信号进行快速傅立叶变换, 得到信号的频谱特性, 从而加深对频谱特性的理解。

其程序为:>> [y,fs,bits]=wavread('I:\xp.wav',[1024 5120]);>> sound(y,fs,bits);>> Y=fft(y,4096);>> subplot(221);plot(y);title('原始信号波形');>> subplot(212);plot(abs(Y));title('原始信号频谱');程序运行结果为:设计数字滤波器和画出频率响应:根据语音信号的特点给出有关滤波器的性能指标:低通滤波器性能指标, =1000Hz, =1200Hz, =100dB, =1dB;高通滤波器性能指标, =4800Hz, =5000Hz, =100dB, =1dB;带通滤波器性能指标, =1200Hz, =3000Hz, =1000Hz, =3200Hz, =100dB, =1dB;要求学生首先用窗函数法设计上面要求的三种滤波器, 在MATLAB中, 可以利用函数firl 设计FIR滤波器;然后再用双线性变换法设计上面要求的三种滤波器, 在MA TLAB中, 可以利用函数butte、cheby1和ellip设计IIR滤波器;最后, 利用MATLAB中的函数freqz画出各种滤波器的频率响应, 这里以低通滤波器为例来说明设计过程。

低通:用窗函数法设计的低通滤波器的程序如下:>> fp=1000;fc=1200;As=100;Ap=1;fs=22050;>> wc=2*fc/fs;wp=2*fp/fs;>> N=ceil((As-7.95)/(14.36*(wc-wp)/2))+1;>> beta=0.1102*(As-8.7);>> Win=Kaiser(N+1,beta);>>b=firl(N,wc,Win);>>freqz(b,1,512,fs);程序运行结果:这里选用凯泽窗设计, 滤波器的幅度和相位响应满足设计指标, 但滤波器长度(N=708)太长, 实现起来很困难, 主要原因是滤波器指标太苛刻, 因此, 一般不用窗函数法设计这种类型的滤波器。

dsp大学课程设计一、教学目标本课程的教学目标旨在帮助学生掌握数字信号处理(DSP)的基本理论、算法和实现方法。

通过本课程的学习,学生应能够:1.知识目标:–理解数字信号处理的基本概念、原理和数学基础。

–熟悉常用的数字信号处理算法,如傅里叶变换、离散余弦变换、快速算法等。

–掌握DSP芯片的基本结构、工作原理和编程方法。

2.技能目标:–能够运用DSP算法进行实际问题的分析和解决。

–具备使用DSP开发工具和实验设备进行软硬件调试的能力。

–能够编写DSP程序,实现数字信号处理算法。

3.情感态度价值观目标:–培养学生的创新意识和团队合作精神,提高解决实际问题的能力。

–增强学生对DSP技术的兴趣和热情,为学生进一步深造和职业发展奠定基础。

二、教学内容本课程的教学内容主要包括以下几个方面:1.数字信号处理基础:包括信号与系统的基本概念、离散信号处理的基本算法等。

2.离散余弦变换和傅里叶变换:离散余弦变换(DCT)和快速傅里叶变换(FFT)的原理和应用。

3.数字滤波器设计:低通、高通、带通和带阻滤波器的设计方法和应用。

4.DSP芯片和编程:DSP芯片的基本结构、工作原理和编程方法,包括C语言和汇编语言编程。

5.实际应用案例:包括音频处理、图像处理、通信系统等领域的实际应用案例分析。

三、教学方法为了提高教学效果,本课程将采用多种教学方法相结合的方式:1.讲授法:通过教师的讲解,使学生掌握数字信号处理的基本概念和原理。

2.讨论法:通过分组讨论和课堂讨论,培养学生的思考能力和团队合作精神。

3.案例分析法:通过分析实际应用案例,使学生了解数字信号处理在工程中的应用。

4.实验法:通过实验操作,使学生掌握DSP芯片的基本编程方法和实验技能。

四、教学资源为了支持本课程的教学,我们将准备以下教学资源:1.教材:《数字信号处理》(或其他指定教材)。

2.参考书:提供相关的参考书籍,供学生自主学习和深入研究。

3.多媒体资料:制作课件、教学视频等,以丰富教学手段和提高学生的学习兴趣。

dsp课程设计报告(同名2257)DSP课程设计总结(2014-2015学年第2学期)题目:数据采集处理和控制系统设计专业班级:电子1202学生姓名:李茹学号:12052203指导教师:李莉设计成绩:2015 年7 月目录一设计目的 (1)二系统分析 (1)1.1设计要求 (1)1.2主要任务 (1)三硬件设计 (2)3.1 硬件总体结构 (2)3.2 DSP模块设计 (4)3.3 电源模块设计 (6)3.4 时钟模块设计 (6)3.5 存储器模块设计 (7)四软件设计 (9)4.1 软件总体流程 (9)4.2 核心模块及实现代码 (9)五课程设计总结 (29)六参考文献 (29)一设计目的此设计结合硬件、软件得到一个基于TMS320VC5416芯片,能完成数据采集、频谱分析、滤波、LCD显示的DSP系统。

以此加强了对DSP功能的认识,复习了Altium Designer 软件的使用方法。

并在此基础上利用CCS软件编程实现A/D采集,FFT变换处理,低通滤波,显示滤波成分等功能的完整的小型数字处理系统。

二系统分析1.1设计要求(1)硬件设计要求设计一个功能完备的,能够独立运行的精简DSP硬件系统,使用Altium Designer绘制出系统原理图和PCB图。

(2)软件设计要求利用实验箱的模拟信号产生单元产生不同频率的信号,或者产生两个频率的信号叠加。

在DSP中采集信号,并且对信号进行频谱分析,滤波等。

通过串口命令选择算法功能,将计算的信号频率或者滤波后的信号频率在LCD上显示。

1.2主要任务(1)DSP 硬件系统设计设计DSP基本结构并绘制单片机最小系统原理图和PCB图。

(2)数据采集处理和控制系统设计利用CCS软件编程实现数据采集x(n)→对数据FFT处理、分析频率成分→根据频率成分设计FIR低通滤波器h(n)→卷积x(n)*h(n)=y(n)得到滤波之后的信号→分析滤波之后y(n)的频率成分→LCD显示高频,低频和滤波器的截止频率。

DSP课程设计报告之混响一、课程目标知识目标:1. 学生能理解混响的概念,掌握混响的物理原理和数学模型。

2. 学生能描述混响在数字信号处理(DSP)中的应用,如音乐制作、声音效果增强等。

3. 学生能解释混响参数对声音效果的影响,如混响时间、湿度、大小等。

技能目标:1. 学生能运用所学知识,使用DSP软件(如Audacity、MATLAB等)进行混响效果的实现和调整。

2. 学生能通过实验和案例分析,分析混响在音频处理中的实际应用,提高解决问题的能力。

情感态度价值观目标:1. 学生通过混响的学习,培养对声音美学的认识和鉴赏能力,提高对音乐和声音艺术的兴趣。

2. 学生在学习过程中,培养合作意识,学会倾听他人意见,提高团队协作能力。

3. 学生通过了解混响在生活中的应用,认识到科技与生活的紧密联系,增强学以致用的意识。

课程性质:本课程为高年级选修课程,以理论讲解和实践操作相结合的方式进行。

学生特点:学生具备一定的数字信号处理基础,对声音处理有一定了解,具有较强的学习能力和动手能力。

教学要求:注重理论与实践相结合,通过案例分析和实验操作,使学生掌握混响的相关知识,提高实际应用能力。

同时,关注学生的情感态度培养,激发学生的学习兴趣和团队合作意识。

在教学过程中,将课程目标分解为具体的学习成果,便于教学设计和评估。

二、教学内容1. 理论部分:- 混响的定义与分类:介绍混响的基本概念,包括自然混响和人工混响,以及混响的类别。

- 混响的物理原理:讲解声音在空间中的传播、反射、吸收等原理,分析影响混响效果的因素。

- 混响的数学模型:介绍混响的常见数学模型,如卷积模型、参数模型等,并分析其优缺点。

2. 实践部分:- 混响效果器的使用:结合教材,教授学生如何使用Audacity、MATLAB等软件中的混响效果器。

- 混响参数调整:指导学生通过调整混响时间、湿度、大小等参数,实现不同混响效果。

- 实践案例:分析实际案例,如音乐作品中的混响处理,使学生更好地理解混响在音频处理中的应用。

dsp交通等课程设计报告一、课程目标知识目标:1. 让学生理解交通信号灯的基本原理,掌握数字信号处理(DSP)技术在交通控制中的应用。

2. 使学生掌握交通流量的基本概念,学会分析交通数据,并运用DSP技术进行优化处理。

3. 帮助学生了解我国交通法规及交通信号控制的相关知识。

技能目标:1. 培养学生运用DSP技术进行交通信号灯控制程序编写的能力。

2. 培养学生运用数据分析方法,对交通流量进行有效监控和优化调整的能力。

3. 提高学生的实践操作能力,学会使用相关软件和硬件进行交通信号控制系统的设计和调试。

情感态度价值观目标:1. 培养学生关注社会交通问题,树立解决实际问题的责任感和使命感。

2. 激发学生对数字信号处理技术的兴趣,提高学生主动学习的积极性。

3. 培养学生的团队协作意识,学会与他人共同探讨、解决问题。

本课程针对年级特点,结合实际交通问题,以数字信号处理技术为载体,旨在提高学生的理论知识水平、实践操作能力以及解决实际问题的能力。

课程目标具体、可衡量,为后续教学设计和评估提供明确方向。

二、教学内容本章节教学内容主要包括以下三个方面:1. 交通信号灯原理及DSP技术基础- 教材章节:第一章 交通信号灯原理;第二章 DSP技术概述- 内容安排:介绍交通信号灯的基本原理、功能及分类;讲解DSP技术的基本概念、发展历程及其在交通控制领域的应用。

2. 交通流量分析及DSP技术应用- 教材章节:第三章 交通流量分析;第四章 DSP技术在交通控制中的应用- 内容安排:分析交通流量的基本特性,讲解数据采集、处理和优化方法;探讨DSP技术在交通信号控制、拥堵缓解等方面的应用实例。

3. 交通信号控制系统设计与实践- 教材章节:第五章 交通信号控制系统设计;第六章 实践操作- 内容安排:介绍交通信号控制系统的设计原理、硬件和软件选型;指导学生进行交通信号控制程序编写,开展实践操作,培养实际动手能力。

教学内容安排和进度:本章节共计12课时,分配如下:- 第1-4课时:交通信号灯原理及DSP技术基础- 第5-8课时:交通流量分析及DSP技术应用- 第9-12课时:交通信号控制系统设计与实践教学内容具有科学性和系统性,结合教材章节和实际案例,旨在帮助学生掌握交通信号控制相关知识,提高实践操作能力。

实验报告||实验名称 D SP课内系统实验课程名称DSP系统设计||一、实验目的及要求1. 掌握用窗函数法设计FIR数字滤波器的原理和方法。

熟悉线性相位FIR 数字滤波器特性。

了解各种窗函数对滤波器特性的影响。

2. 掌握设计IIR数字滤波器的原理和方法。

熟悉IIR数字滤波器特性。

了解IIR数字滤波器的设计方法。

3.掌握自适应数字滤波器的原理和实现方法。

掌握LMS自适应算法及其实现。

了解自适应数字滤波器的程序设计方法。

4.掌握直方图统计的原理和程序设计;了解各种图像的直方图统计的意义及其在实际中的运用。

5.了解边缘检测的算法和用途,学习利用Sobel算子进行边缘检测的程序设计方法。

6.了解锐化的算法和用途,学习利用拉普拉斯锐化运算的程序设计方法。

7.了解取反的算法和用途,学习设计程序实现图像的取反运算。

8.掌握直方图均衡化增强的原理和程序设计;观察对图像进行直方图均衡化增强的效果。

二、所用仪器、设备计算机,dsp实验系统实验箱,ccs操作环境三、实验原理(简化)FIR:有限冲激响应数字滤波器的基础理论,模拟滤波器原理(巴特沃斯滤波器、切比雪夫滤波器、椭圆滤波器、贝塞尔滤波器)。

数字滤波器系数的确定方法。

IIR:无限冲激响应数字滤波器的基础理论。

模拟滤波器原理(巴特沃斯滤波器、切比雪夫滤波器、椭圆滤波器、贝塞尔滤波器)。

数字滤波器系数的确定方法。

、自适应滤波:自适应滤波器主要由两部分组成:系数可调的数字滤波器和用来调节或修正滤波器系数的自适应算法。

e(n)=z(n)-y(n)=s(n)+d(n)-y(n)直方图:灰度直方图描述了一幅图像的灰度级内容。

灰度直方图是灰度值的函数,描述的是图像中具有该灰度值的像素的个数,其横坐标表示像素的灰度级别,纵坐标是该灰度出现的频率(像素个数与图像像素总数之比)。

图像边缘化:所谓边缘(或边沿)是指其周围像素灰度有阶跃变化。

经典的边缘提取方法是考察图像的每个像素在某个邻域内灰度的变化,利用边缘临近一阶或二阶方向导数变化规律,用简单的方法检测边缘。

基于dsp的课程设计word一、教学目标本课程的教学目标是使学生掌握DSP(数字信号处理器)的基本原理、应用方法和编程技巧。

通过本课程的学习,学生将能够:1.理解DSP的基本概念、发展和分类;2.掌握DSP的基本结构和原理,包括CPU、内存、外设等;3.熟悉DSP的编程语言和开发环境;4.掌握DSP的基本算法和应用,如滤波、均衡、编码等;5.能够运用DSP解决实际信号处理问题。

二、教学内容本课程的教学内容主要包括以下几个部分:1.DSP概述:介绍DSP的发展、分类和应用领域;2.DSP基本结构:讲解DSP的CPU、内存、外设等基本组成部分及其工作原理;3.DSP编程基础:介绍DSP的编程语言、开发环境和编程方法;4.DSP算法与应用:讲解DSP的基本算法,如滤波、均衡、编码等,并介绍其在实际信号处理中的应用;5.实践环节:通过实验使学生掌握DSP的实际应用和编程技巧。

三、教学方法为了实现教学目标,我们将采用以下教学方法:1.讲授法:讲解DSP的基本概念、原理和算法;2.讨论法:引导学生探讨DSP的应用问题和解决方案;3.案例分析法:分析实际信号处理问题,引导学生运用DSP进行解决;4.实验法:让学生通过实际操作,掌握DSP的编程和应用技巧。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:选用权威、实用的DSP教材,为学生提供系统的理论知识;2.参考书:提供相关的DSP参考书籍,丰富学生的知识体系;3.多媒体资料:制作课件、视频等多媒体资料,增强课堂教学的趣味性和生动性;4.实验设备:准备DSP开发板、仿真器等实验设备,让学生能够进行实际操作和编程练习。

五、教学评估本课程的评估方式包括平时表现、作业和考试三个部分,以全面客观地评价学生的学习成果。

1.平时表现:通过课堂参与、提问、讨论等方式评估学生的学习态度和积极性。

2.作业:布置适量的作业,评估学生对知识的理解和应用能力。

dsp综合课程设计一、教学目标本课程的教学目标旨在帮助学生掌握数字信号处理(DSP)的基本原理和应用技能,通过理论学习与实践操作相结合的方式,培养学生的技术创新能力和实际问题解决能力。

知识目标:学生将掌握数字信号处理的基本概念、算法和典型的DSP芯片应用。

具体包括:•数字信号处理的基础理论•常用数字滤波器的设计与分析•快速算法实现,如FFT、IFFT等•DSP芯片的工作原理及编程方法技能目标:通过课程学习和实践操作,学生将能够熟练使用DSP相关软件(如MATLAB等)进行算法仿真和系统设计,并具备一定的硬件操作能力,包括:•利用仿真工具对DSP算法进行验证•设计简单的数字信号处理系统•进行DSP芯片编程和硬件调试情感态度价值观目标:通过课程学习,培养学生对数字信号处理技术的兴趣和热情,增强其科技责任感和创新意识,激发学生将所学知识应用于工程实践和科研探索中,为我国信息技术产业的发展贡献自己的力量。

二、教学内容教学内容围绕数字信号处理的基本理论、算法实现、DSP芯片应用及系统设计展开。

1.数字信号处理基础:涵盖信号的采样与恢复、离散时间信号处理、离散时间系统特性等基本概念。

2.数字滤波器设计:包括常用滤波器(低通、高通、带通、带阻)的设计方法和理论。

3.快速算法:重点讲解快速傅里叶变换(FFT)、快速卷积等高效算法。

4.DSP芯片介绍:详细讲解DSP芯片的结构、工作原理及编程环境。

5.实际应用案例:结合实际案例,使学生理解DSP技术在现代通信、音视频处理等领域的应用。

三、教学方法结合课程特点,采用多种教学方法激发学生的学习兴趣和主动性:1.讲授法:系统讲解理论知识,确保学生掌握扎实的基础。

2.案例分析法:通过具体案例,使学生理解DSP技术的应用。

3.实验法:安排实验课,让学生动手实践,加深对理论知识的理解。

4.小组讨论法:鼓励学生分组讨论,培养团队合作精神,提高问题解决能力。

四、教学资源为支持课程的顺利进行,将准备以下教学资源:1.教材:《数字信号处理》(或等同教材)2.参考书籍:提供相关领域的参考书籍,丰富学生的知识视野。

我不应把我的作品全归功于自己的智慧,还应归功于我以外向我提供素材的成千成万的事情和人物!——采于网,整于己,用于民2021年5月12日dsp实验报告总结篇一:dsp课程设计实验报告总结DSP课程设计总结(XX-XX学年第2学期)题目:专业班级:电子1103 学生姓名:万蒙学号:指导教师:设计成绩:XX 年6 月目录一设计目的----------------------------------------------------------------------3 二系统分析----------------------------------------------------------------------3 三硬件设计3.1 硬件总体结构-----------------------------------------------------------3 3.2 DSP模块设计-----------------------------------------------------------4 3.3 电源模块设计----------------------------------------------------------4 3.4 时钟模块设计----------------------------------------------------------5 3.5 存储器模块设计--------------------------------------------------------6 3.6 复位模块设计----------------------------------------------------------6 3.7 JTAG模块设计--------------------------------------------------------7 四软件设计4.1 软件总体流程-----------------------------------------------------74.2 核心模块及实现代码---------------------------------------8五课程设计总结-----------------------------------------------------14一、设计目的设计一个功能完备,能够独立运行的精简DSP硬件系统,并设计简单的DSP控制程序。

dsp课程设计报告绪论一、教学目标本课程的教学目标是使学生掌握数字信号处理的基本理论、方法和应用,培养学生运用数字信号处理技术解决实际问题的能力。

具体分为以下三个层面:1.知识目标:学生需要掌握数字信号处理的基本概念、理论体系和常用算法,包括离散时间信号处理、离散傅里叶变换、快速傅里叶变换、数字滤波器设计等。

2.技能目标:学生能够运用数字信号处理理论分析和解决实际问题,具备使用相关软件工具进行数字信号处理的能力,如MATLAB、Python等。

3.情感态度价值观目标:培养学生对数字信号处理学科的兴趣和热情,激发学生创新意识和团队合作精神,使学生在面对复杂问题时,能够运用所学知识为社会发展做出贡献。

二、教学内容根据教学目标,本课程的教学内容主要包括以下几个部分:1.数字信号处理基本概念:离散时间信号、离散时间系统、Z域变换等。

2.离散傅里叶变换:DFT的基本性质、计算方法、频谱分析等。

3.快速傅里叶变换:FFT的原理、计算方法、应用实例等。

4.数字滤波器设计:滤波器的基本类型、设计方法、频率响应分析等。

5.数字信号处理应用:噪声抑制、信号恢复、图像处理等。

三、教学方法为了提高教学效果,本课程将采用多种教学方法相结合的方式进行教学:1.讲授法:教师通过讲解、演示和案例分析,引导学生掌握数字信号处理的基本理论和方法。

2.讨论法:学生针对实际问题进行讨论,培养学生的思考能力和团队协作精神。

3.案例分析法:通过分析具体案例,使学生更好地理解数字信号处理技术的应用。

4.实验法:安排实验课程,让学生动手实践,提高实际操作能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:选用权威、实用的教材,为学生提供系统、全面的学习资料。

2.参考书:推荐学生阅读相关参考书籍,丰富学生的知识体系。

3.多媒体资料:制作课件、教学视频等多媒体资料,提高课堂教学效果。

4.实验设备:配置相应的实验设备,确保学生能够进行实际操作。

DSP设计课程设计一、课程目标知识目标:1. 让学生理解DSP(数字信号处理)的基本原理和概念,包括采样定理、傅里叶变换和数字滤波器设计等。

2. 使学生掌握DSP算法的数学推导和实现方法,具备使用DSP芯片进行信号处理的能力。

3. 帮助学生了解DSP技术在通信、音视频处理等领域的应用。

技能目标:1. 培养学生运用数学工具进行DSP相关算法推导和仿真能力。

2. 提高学生实际操作DSP芯片,完成信号处理实验的能力。

3. 培养学生团队协作和沟通能力,能够就DSP技术问题进行讨论和分析。

情感态度价值观目标:1. 激发学生对数字信号处理技术的兴趣,培养其探索精神和创新意识。

2. 培养学生严谨的科学态度,注重实践和理论相结合。

3. 引导学生关注DSP技术在国家和社会发展中的应用,增强其社会责任感和使命感。

分析课程性质、学生特点和教学要求,本课程旨在让学生通过学习DSP设计,掌握数字信号处理的基本原理和方法,培养其实践操作能力。

课程目标分解为具体学习成果,以便后续教学设计和评估:学生能够独立完成DSP算法推导、仿真和实验操作,具备解决实际问题的能力,并在团队合作中发挥积极作用。

二、教学内容1. DSP基本原理与概念- 采样定理与信号重建- 傅里叶变换及其应用- 数字滤波器设计原理2. DSP算法及其数学推导- 离散时间信号处理基础- 快速傅里叶变换(FFT)算法- 数字滤波器算法实现3. DSP芯片与应用- DSP芯片架构与特点- DSP芯片编程与实验操作- DSP技术在通信、音视频处理等领域的应用案例4. 教学大纲安排与进度- 第一阶段:基本原理与概念(2周)- 课本章节:第1-3章- 第二阶段:DSP算法及其数学推导(3周)- 课本章节:第4-6章- 第三阶段:DSP芯片与应用(3周)- 课本章节:第7-9章教学内容按照课程目标进行选择和组织,确保科学性和系统性。

在教学过程中,教师将依据教学大纲,引导学生学习课本相关章节,完成教学内容的学习。

电子通信工程系DSP原理及应用实验报告学号:姓名:专业:指导老师:实验一CCS的安装与设置1.实验目的掌握CCS 2(…2000)集成开发环境的安装;掌握软件仿真环境的设置方法;熟悉CCS集成开发环境的应用界面。

2.实验设备PC机、CCS 2(…2000)IDE软件、EXP-IV DSP实验箱3.实验要求●熟悉安装CCS 2(…2000)IDE软件的步骤●根据DSP芯片的型号正确设置软件仿真环境●了解CCS集成开发环境应用界面的各项内容4.实验内容(1)CCS 2(…2000)IDE软件的安装步骤S的安装1.1退出病毒防火墙及杀毒软件1.2解压CCS20002.2 .rar文件并运行setup.exe安装程序文件。

1.3选择安装界面中“Code Cmposter Studio”选项。

如下图(1-1)所示图(1-1)1.4完成上述步骤后只需点“Next”继续。

在出现提示确认没有运行病毒检测软件的提示窗口时点“确定”。

如下图(1-2)所示图(1-2)1.5选择“Yes”同意CCS的安装协议。

如下图(1-3)所示图(1-3)1.6选择默认安装组件,点“Next”。

如下图(1-4)所示图(1-4)1.7选择默认安装路径“C:\ti”点“Next”。

如下图(1-5)所示图(1-5)1.8出现下图(1-6)所示时取消勾选项,并点击“Finish”。

图(1-6)1.9完成上述步骤,再出现的对话框中点击“确定”。

如下图(1-7)所示图(1-7)1.10安装完成后,计算机桌面出现如下图(1-8)所示的快捷方式图标。

图(1-8)(2)TMS320F2812 微处理器的软件仿真环境的设置2.1双击桌面“Setup CCS 2”的快捷方式启动设置程序。

2.2在出现的如下图(1-9)所示的窗口中依次进行①单击“Clear”清除原有设置②选择“F2812 Device Simulator”配置③单击“Import”输入配置④单击“Save and Quit”图(1-9)2.3在接下来的对话框中单击“否”完成对CCS的设置。

dsp课程设计报告像处理一、课程目标知识目标:1. 让学生掌握数字信号处理(DSP)的基本概念,包括采样、量化、滤波器等;2. 使学生了解图像处理的基本原理,如图像的表示、转换和增强;3. 引导学生掌握图像处理中常用的算法,如卷积、边缘检测、图像压缩等。

技能目标:1. 培养学生运用DSP技术解决实际图像处理问题的能力;2. 培养学生运用编程工具(如MATLAB)实现图像处理算法的能力;3. 培养学生通过小组合作、讨论和思考,解决图像处理中遇到的难题。

情感态度价值观目标:1. 激发学生对数字信号处理和图像处理领域的兴趣,培养其探索精神;2. 培养学生具备良好的团队协作和沟通能力,学会倾听、尊重他人意见;3. 培养学生具备严谨的科学态度和较强的实践能力,善于发现和解决问题。

课程性质分析:本课程为选修课,适用于高年级学生,具有一定的理论深度和实用性。

结合学生特点和教学要求,课程目标旨在使学生掌握数字信号处理和图像处理的基本知识,培养其实践能力和创新思维。

二、教学内容1. 数字信号处理基础- 采样与重建- 量化与编码- 离散时间信号与系统- 傅里叶变换及其应用2. 图像处理基本原理- 图像表示与转换- 图像增强- 图像滤波- 边缘检测3. 常用图像处理算法- 卷积算法- 图像压缩(如JPEG、PNG)- 图像分割- 特征提取4. 实践教学- 使用MATLAB进行图像处理编程实践- 分析实际图像处理案例- 小组项目:设计与实现一个简单的图像处理应用教学大纲安排:第一周:数字信号处理基础第二周:图像处理基本原理第三周:常用图像处理算法第四周:实践教学与小组项目教学内容进度:第一周:完成采样、重建、量化、编码等基础知识的讲解与练习;第二周:学习图像表示、转换、增强、滤波等原理,并进行相关实践;第三周:讲解卷积、图像压缩、图像分割等算法,进行案例分析;第四周:指导学生进行MATLAB编程实践,完成小组项目设计与实现。

数据采集处理和控制系统设计一课程设计要求1.基本DSP硬件系统设计要求①基本DSP硬件系统以TMS320C54x系列为核心处理器,包括最小系统、存储器扩展、显示器、键盘、AD、DA等电路模块;②硬件设计画出主要芯片及电路模块之间的连接即可,重点考查电路模块方案设计与系统地址分配;③设计方案以电路示意图为主,辅以必要的文字说明。

2.基本软件设计要求①看懂所给例程,画出例程输出波形示意图;②修改例程程序,使之输出其它波形,如方波、三角波、锯齿波等均可;③设计方案以程序实现为主,辅以必要的文字说明。

3.课程设计报告要求①硬件系统设计:设计思路、设计系统功能、主要芯片选型及使用方法、设计方案说明、电路示意图②软件系统设计:示例程序功能解读及输出波形示意图、设计软件功能、设计思路、实现源码(带程序注释)③报告总结二系统分析利用实验箱的模拟信号产生单元产生不同频率的信号,或者产生两个频率的信号的叠加。

在DSP 中采集信号,并且对信号进行频谱分析,滤波等。

通过键盘或者串口命令选择算法的功能,将计算的信号频率或者滤波后信号的频率在LCD 上显示。

主要功能如下:(1)对外部输入的模拟信号采集到DSP 内存,会用CCS 软件显示采集的数据波形。

(2)对采集的数据进行如下算法分析:①频谱分析:使用fft 算法计算信号的频率。

②对信号进行IIR 滤波或FIR 滤波,并且计算滤波前后信号的频率。

③外部键盘或者从计算机来的串口命令选择算法功能,并且将结果在LCD 上显示。

绘制出DSP系统的功能框图、使用AD(Altium Designer)绘制出系统的原理图和PCB 版图。

在 DSP 中采集信号,用CCS 软件显示采集的数据波形,以及对采集的数据进行算法分析。

三硬件设计3.1 硬件总体结构3.2 DSP模块设计3.3 电源模块设计将5V电源电压转换为3.3V和1.6V电源3.4 时钟模块设计此处由外部晶振提供时钟信号3.5 存储器模块设计DSP上只有一个读写控制信号引脚,而FLASH有两个引脚,将读、写分开,故在OE上接一个非门电路,实现高时读,低时写。

dsp项目课程设计一、课程目标知识目标:1. 学生能理解数字信号处理(DSP)的基本概念,掌握其基本原理和应用领域。

2. 学生能运用数学知识,如傅里叶变换、Z变换等,分析并解决实际问题。

3. 学生能了解DSP技术在现实生活中的应用,如音频处理、图像处理等。

技能目标:1. 学生能够熟练使用DSP开发工具和软件,完成简单的项目设计。

2. 学生能够运用所学知识,设计并实现一个简单的DSP应用系统,如音频信号滤波、图像去噪等。

3. 学生能够通过小组合作,培养团队协作和沟通能力,提高问题解决能力。

情感态度价值观目标:1. 学生能够认识到数字信号处理在科技发展中的重要性,激发对相关领域的兴趣。

2. 学生在学习过程中,培养勇于探索、积极进取的精神,增强自信心。

3. 学生通过课程学习,认识到科技发展对社会的贡献,树立正确的价值观。

课程性质:本课程为实践性较强的课程,结合理论教学和实际操作,培养学生对数字信号处理技术的理解和应用能力。

学生特点:学生具备一定的数学基础和编程能力,对新技术充满好奇,喜欢动手实践。

教学要求:教师需结合课本内容,以实际项目为导向,引导学生掌握基本理论,提高实际操作能力。

在教学过程中,注重培养学生的团队协作和创新能力,提高学生的综合素质。

通过课程目标分解,确保学生能够达到预期学习成果,为后续教学设计和评估提供依据。

二、教学内容1. 数字信号处理基础理论:- 傅里叶变换理论及其应用- Z变换及其性质- 离散时间信号与系统2. DSP算法与应用:- 数字滤波器设计- 快速傅里叶变换(FFT)算法- 数字信号处理在音频、图像领域的应用3. DSP实践项目:- 项目一:音频信号处理(滤波、增强)- 项目二:图像处理(去噪、边缘检测)- 项目三:DSP综合应用(如语音识别、图像识别)4. 教学内容的安排与进度:- 基础理论部分:占总课时的1/3,以课本相关章节为基础,逐步引导学生掌握基本概念和原理。

共享知识分享快乐盛年不重来,一日难再晨。

及时宜自勉,岁月不待人。

数据采集处理和控制系统设计一课程设计要求1.基本DSP硬件系统设计要求①基本DSP硬件系统以TMS320C54x系列为核心处理器,包括最小系统、存储器扩展、显示器、键盘、AD、DA等电路模块;②硬件设计画出主要芯片及电路模块之间的连接即可,重点考查电路模块方案设计与系统地址分配;③设计方案以电路示意图为主,辅以必要的文字说明。

2.基本软件设计要求①看懂所给例程,画出例程输出波形示意图;②修改例程程序,使之输出其它波形,如方波、三角波、锯齿波等均可;③设计方案以程序实现为主,辅以必要的文字说明。

3.课程设计报告要求①硬件系统设计:设计思路、设计系统功能、主要芯片选型及使用方法、设计方案说明、电路示意图②软件系统设计:示例程序功能解读及输出波形示意图、设计软件功能、设计思路、实现源码(带程序注释)③报告总结二系统分析利用实验箱的模拟信号产生单元产生不同频率的信号,或者产生两个频率的信号的叠加。

在DSP 中采集信号,并且对信号进行频谱分析,滤波等。

通过键盘或者串口命令选择算法的功能,将计算的信号频率或者滤波后信号的频率在LCD 上显示。

主要功能如下:(1)对外部输入的模拟信号采集到DSP 内存,会用CCS 软件显示采集的数据波形。

(2)对采集的数据进行如下算法分析:①频谱分析:使用fft 算法计算信号的频率。

②对信号进行IIR 滤波或FIR 滤波,并且计算滤波前后信号的频率。

③外部键盘或者从计算机来的串口命令选择算法功能,并且将结果在LCD 上显示。

绘制出DSP系统的功能框图、使用AD(Altium Designer)绘制出系统的原理图和PCB 版图。

在 DSP 中采集信号,用CCS 软件显示采集的数据波形,以及对采集的数据进行算法分析。

三硬件设计3.1 硬件总体结构CLKSTMS32054X11CONTROL1MX16BIT FLASH2016D[15..0]A[19..0]XDS510 JTAGRESETPower (73HD3XX)16WE OECE复位电路3.2 DSP 模块设计3.3 电源模块设计将5V电源电压转换为3.3V和1.6V电源3.4 时钟模块设计此处由外部晶振提供时钟信号3.5 存储器模块设计DSP上只有一个读写控制信号引脚,而FLASH有两个引脚,将读、写分开,故在OE上接一个非门电路,实现高时读,低时写。

FLASH上的地址线和数据线与DSP上的地址线、数据线相连3.6 JATG模块设计3.7 TMS320VC5416 最小系统 PCB 版图板上包括了支持TMS320VC5416独立运行的时钟电路、复位电路、Flash模块、JTAG仿真接口电路以及电源模块等。

为节省空间和材料,部分器件放在了反面。

四软件设计4.1正弦波信号发生器所给例程输出波形为正弦波,波形如下图所示:4.2三角波(方波)信号发生器******************************************************************** ****************三角波信号发生程序(括号内为方波)****************** ********************************************************************.mmregs.def startk1 .usect "k",1outdata1 .set 0800h(0800h)outdata2 .set 09ffh(0fffh)outdata3 .set 0affh(0fffh)outdata4 .set 0bffh(0fffh)outdata5 .set 0cffh(0fffh)outdata6 .set 0dffh(0fffh)outdata7 .set 0effh(0fffh)outdata8 .set 0fffh(0fffh)outdata9 .set 1000h(0fffh)outdata10 .set 0fffh(0fffh)outdata11 .set 0effh(0fffh)outdata12 .set 0dffh(0fffh)outdata13 .set 0cffh(0fffh)outdata14 .set 0bffh(0fffh)outdata15 .set 0affh(0fffh)outdata16 .set 09ffh(0fffh)outdata17 .set 08ffh(0800h)outdata18 .set 07ffh(0000h)outdata19 .set 06ffh(0000h)outdata20 .set 05ffh(0000h)outdata21 .set 04ffh(0000h)outdata22 .set 03ffh(0000h)outdata23 .set 02ffh(0000h)outdata24 .set 01ffh(0000h)outdata25 .set 00ffh(0000h)outdata26 .set 01ffh(0000h)outdata27 .set 02ffh(0000h)outdata28 .set 03ffh(0000h)outdata29 .set 04ffh(0000h)outdata30 .set 05ffh(0000h)outdata31 .set 06ffh(0000h)outdata32 .set 07ffh(0000h)//定义输出数据.textstart:stm 2000h,sp//置堆栈指针stm #k1,ar2//将操作数#k1装入ar2 st #outdata1,*ar2//将数据送到*ar2nopnopbegin:st #outdata1,*ar2portw *ar2,0bfffh//将*ar2内容从D/A转换器输出rpt #7fffh//等待一段时间nopst #outdata2,*ar2portw *ar2,0bfffhrpt #7fffhnopst #outdata3,*ar2portw *ar2,0bfffhrpt #7fffhst #outdata4,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata5,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata6,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata7,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata8,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata9,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata10,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata11,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata12,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata13,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata14,*ar2portw *ar2,0bfffh rpt #7fffhst #outdata15,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata16,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata17,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata18,*ar2 portw *ar2,0bfffh rpt #7fffhnopst #outdata19,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata20,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata21,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata22,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata23,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata24,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata25,*ar2portw *ar2,0bfffh rpt #7fffhst #outdata26,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata27,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata28,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata29,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata30,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata31,*ar2portw *ar2,0bfffh rpt #7fffhnopst #outdata32,*ar2portw *ar2,0bfffh rpt #7fffhnopb begin//循环输出32个数据.end//代码段结束4.3 本系统软件总体流程4.4 核心模块及实现代码FFT算法程序:void kfft(double pr[Length],double pi[Length],int n,int k,double fr[Length],double fi[Length],int l,int il){int it,m,is,i,j,nv,l0;double p,q,s,vr,vi,poddr,poddi;for (it=0; it<=n-1; it++){ m=it; is=0;for (i=0; i<=k-1; i++){ j=m/2; is=2*is+(m-2*j); m=j;}fr[it]=pr[is]; fi[it]=pi[is];}pr[0]=1.0; pi[0]=0.0;p=6.283185306/(1.0*n);pr[1]=cos(p); pi[1]=-sin(p);if (l!=0) pi[1]=-pi[1];for (i=2; i<=n-1; i++){ p=pr[i-1]*pr[1]; q=pi[i-1]*pi[1];s=(pr[i-1]+pi[i-1])*(pr[1]+pi[1]);pr[i]=p-q; pi[i]=s-p-q;}for (it=0; it<=n-2; it=it+2){ vr=fr[it]; vi=fi[it];fr[it]=vr+fr[it+1]; fi[it]=vi+fi[it+1];fr[it+1]=vr-fr[it+1]; fi[it+1]=vi-fi[it+1];}m=n/2; nv=2;for (l0=k-2; l0>=0; l0--){ m=m/2; nv=2*nv;for (it=0; it<=(m-1)*nv; it=it+nv)for (j=0; j<=(nv/2)-1; j++){ p=pr[m*j]*fr[it+j+nv/2];q=pi[m*j]*fi[it+j+nv/2];s=pr[m*j]+pi[m*j];s=s*(fr[it+j+nv/2]+fi[it+j+nv/2]);poddr=p-q; poddi=s-p-q;fr[it+j+nv/2]=fr[it+j]-poddr;fi[it+j+nv/2]=fi[it+j]-poddi;fr[it+j]=fr[it+j]+poddr;fi[it+j]=fi[it+j]+poddi;}}if (l!=0)for (i=0; i<=n-1; i++){ fr[i]=fr[i]/(1.0*n);fi[i]=fi[i]/(1.0*n);}if (il!=0)for (i=0; i<=n-1; i++){ pr[i]=sqrt(fr[i]*fr[i]+fi[i]*fi[i]);if (fabs(fr[i])<0.000001*fabs(fi[i])){ if ((fi[i]*fr[i])>0) pi[i]=90.0;else pi[i]=-90.0;}elsepi[i]=atan(fi[i]/fr[i])*360.0/6.283185306;}}卷积程序:void Convolveok( //卷积函数double *x, // 原始输入数据double *h, // 冲击响应double *y, // 卷积输出结果UINT16 Leng, // 序列长度UINT16 h_Len){UINT16 m,p,j;double r,rm;double xmean = 0.0;double xmid[100];for(m=0;m<h_Len;m++){xmid[m] = 0.0;}for (m=0; m<Leng; m++){xmean = x[m] + xmean;}xmean = 1.0*xmean/Length;for (m=0; m<Leng; m++){x[m] = x[m] - xmean;}for (m=0; m<Leng; m++){for (p=0; p<h_Len; p++){xmid[h_Len-p-1] = xmid[h_Len-p-2];}xmid[0] = x[m];r = 0.0;rm= 0.0;for (j=0; j<h_Len; j++){r = xmid[j] * h[j];rm = rm + r;}y[m] = rm;}}求最大值和次大值函数:void max(){ int k1,k2; //k1 最大值,k2 次最大值int r;for(r=0;r<16;r++){if(pr[k1]<pr[r]){k1=r;}}for(r=20;r<64;r++){if(pr[k2]<pr[r]){k2=r;}}f0=250000.0/256*k1;f1=250000.0/256*k2;fc=(f0+f1)/2;}归一化函数:void avg(){ int j;sum= 0.0;for(j=0;j<256;j++){sum+=(data_buff[j]/256.0); }for(j=0;j<256;j++){pr[j]=data_buff[j]-sum;pi[j]=0.0;}}FIR滤波器设计函数:void firdes(double npass)//求h(n) {int t;for (t=0; t<FLen; t++){h[t]=sin((t-(FLen-1)/2.0)*npass*3.1415926)/(3.1415926*(t-(FLen-1) /2.0));}if (t == ((FLen-1)/2)) h[t]=npass;}外部中断2服务函数:void interrupt ExtInt2(void){int i1,j;*(unsigned int*)IFR=0xFFFF; //清除所有中断标志data_buff[i1] = port8002 & 0x00ff;i1++;if(i1 == 256){avg();kfft(pr,pi,256,8,fr,fi,0,1);max();npass=fc/250000.0;firdes(npass);Convolveok(data_buff,h,y,256,51);for(j=0;j<256;j++){yr[j]=y[j];yi[j]=0.0;}kfft(yr,yi,256,8,Yr,Yi,0,1);flag=1;i1 = 0;}4.5 程序运行效果①采集的数据及其FFT计算结果②51阶滤波器H(n)波形③滤波前后信号频谱图:由滤波前后高低频分量的相对大小证明低通滤波器对高频分量的衰减作用比较强,但没有完全滤出去④采集数据波形与滤波后波形比较由图可见滤波后信号中的高频分量得到了较大的衰减,滤波后波形变得平滑。