基于FPGA的QDPSK调制器的设计与实现

- 格式:pdf

- 大小:1.02 MB

- 文档页数:4

基于FPGA的QPSK解调技术的设计与实现的开题报告一、选题背景及意义随着现代通信技术的发展,频谱资源越来越紧张,为提高频谱利用效率,射频通信系统中使用数字调制技术是一种可有效降低带宽能量占用和提高信道容量的方式。

其中一种常用的数字调制技术是QPSK调制,它可以将两路单极性NRZ数据分别调制在正弦波和余弦波载波上,实现带宽利用率的提高。

在接收端,解调器需要对QPSK调制信号进行还原,提取出原始的信息数据。

因此,本课题选取了基于FPGA的QPSK解调技术的设计与实现作为研究方向,旨在探索一种高效实现数字信号解调的方法,为提高现代通信技术的发展水平做出贡献。

二、研究内容1. 系统总体设计本课题设计的QPSK解调系统包括射频前端的载频同步、时序同步、均衡、解调等模块,还包括数字信号处理相关的滤波器、采样率变换等模块。

通过这些模块的协同作用,将接收到的QPSK调制信号解调还原成原始的数字信号数据流。

2. 载频同步模块该模块负责完成载频的同步,用于去除接收端的时移影响和相位偏差。

常用的载频同步算法有Costas算法、DDS算法、ZT算法等。

3. 时序同步模块该模块用于解决接收数据中时序抖动的问题,采用软判决算法实现。

4. 均衡模块该模块用于抑制信道传输时产生的干扰,提高系统的抗干扰性能。

常用的均衡算法有线性均衡算法、决策反馈均衡算法等。

5. 解调模块该模块用于将QPSK调制信号还原成原始数字信号。

该模块通常包括滤波器、采样率变换器等子模块。

三、研究计划第一年:我们将完成系统的总体设计,并完成载频同步模块和时序同步模块的算法研究和验证。

同时进行硬件平台的搭建和仿真测试。

第二年:我们计划完成均衡模块和解调模块的算法研究和验证,并将这些模块集成到硬件平台上。

在验证完成后,完善系统的功能和性能,并进行实际场景测试。

第三年:在系统的测试和实际应用中不断完善和优化,提高系统的性能和稳定性,并探索将该技术应用到更广泛领域的可能性,为现代通信技术的发展做出更大的贡献。

实验题目:基于FPGA的PSK调制系统专业班级:学生姓名:指导教师:设计时间:基于FPGA的PSK调制系统一、实验目的1.掌握利用原理图输入法设计电路的方法,掌握QuartusII的层次化设计方法。

通过PSK调制系统的设计,熟悉用EDA软件进行电路设计的详细流程,以及在硬件上的应用。

2.掌握绝对码、相对码的概念以及它们之间的变换关系和变换方法。

3.掌握用键控法产生2PSK信号的方法。

4.掌握相对码波形与2PSK信号波形之间的关系、绝对码波形与2DPSK信号波形之间的关系。

二、实验要求利用实验板具有模拟信号处理的功能,设计一个移相键控信号发生器。

要求利用板上的8位DIP开关设置基带信号码(8bit)。

板上的DAC送出己调信号(正弦波),对8bit基带信号循环调制。

要有用于观察的同步脉冲输出。

传输速率1200bps。

为简单起见,载波频率也是1200Hz。

为简单起见,已调信号的相位和基带信号码的夫系柬用绝对调相方式。

即基带信号为l,己调信号的相位相对于参考相位改变180度。

基带信号为0,已调信号的相位与参考相位相同。

三、实验内容1、PSK调制原理相移键控(Phase Shift Keying,PSK),它是受键控的载波相位按数字基带脉冲的规律而改变的一种数字调制方式。

这种以载波的不同相位直接表示相应数字信息的相位键控,通常被称为绝对移相方式。

当基带信号为二进制数字脉冲序列时,所得到的相位键控信号为二进制相位键控,即2PSK,它的表达式为式中,φ(t)由数字信息“0”“1”控制。

在绝对移相中,因为φ(t)选用的参考相位基准就是未调制的载波,所以φ(t)就是载波的绝对值。

一般说来,数字信息为“1”时,φ(t)=0,数字信息为“0”时,φ(t)=π。

即如图所示2、系统总体设计系统的结构框图3、系统详细设计1 分频器设计根据题目中载波频率小于30kHZ的要求,生成载波信号的正弦信号发生器选择16位累加器,则其需要的时钟在30kHZ以上即可。

_4_DQPSK调制解调位同步算法及其FPGA的实现_冯娟可编程器件应⽤电 ⼦ 测 量 技 术ELEC TRON IC M EAS UREM EN T TEC HNO LOGY 第31卷第6期2008年6⽉ π/4-DQPSK调制解调位同步算法及其FPGA的实现冯 娟 林 彬(四川师范⼤学草堂校区⼯程技术系 成都 610072)摘 要:本⽂详细介绍了π/4-DQ PSK调制解调过程中Ga rdner位同步定时算法的原理。

应⽤了G ardner位同步算法实现解调,Ga rdner位同步算法只需要在⼀个符号内的2个采样点,这就使得解调算法和位同步算法结构简单,运算量⼩,适应性更强,便于全数字接收机的实现。

并利⽤F PGA芯⽚来实现该算法的关键技术。

实验表明,位定时同步的研究⽐数字锁相环的⽅法可调参数更多,适应性更强,获得了较好的同步效果。

关键词:π/4-DQ PSK;位同步;F PGA中图分类号:T N929.5 ⽂献标识码:Aπ/4-DQPSK demodulation bit synchronizationalgorithm andimplementation in FPG AFeng Juan L in Bin(Departm ent of Engneering T echnology,S ichu an Normal University Caotang Campus,Chengdu610072)A bstract:T his paper proposes the theo ry o f Ga rdner sy mbo l sy nchro niza tion algo rithm in theπ/4-DQ PSK modulatio n a nd demo dula tion,and applies the G ardner sy mbo l sy nch ronizatio n alg orithm to implement the demo dulation,w hich o nly need two sampling points in a symbol.So the algo rithm is sim ple and the opera tion is a lso simple and the same times it is bet ter to implement the all digital r eceiver.M eanwhile implementing this theo ry makes use o f F PGA.T he result show s this method is prefer to DL L in acco mmo da ting pa rameter and adaptability.It also achieves success in sy nchro niza tion. Keywords:π/4-D QP SK;symbol sy nchr onization;F PG A0 引⾔π/4-DQPSK最早是由贝尔实验室的P.A.Baker⾸先提出的,π/4-DQPSK调制技术具有较⾼的频谱利⽤率和抗衰落等优点,可以满⾜数字移动通信系统对调制技术的要求,在近年来陆地移动通信和数字卫星移动通信、DAB (digital audio broadc asting,数字⾳频⼴播)等系统中受到了⼴泛的重视和研究。

基于FPGA的QDPSK调制器的设计与实现刘国华;李二喜【期刊名称】《电子设计工程》【年(卷),期】2011(19)9【摘要】This article first introduced the advantage of QPSK and analyzed the implementation principle, then proposed a high-preformance QDPSK digital modulator's implementation method based on FPGA. By using top-to-down design, the system was divied into four modules, serial/parallel conversion, differentiate encoder, logic phase selection circuit and four-phase carrier generator. And it respectively achieved the specific design of each module by schematic, VHDL, and PLL core The simulation and experiment of FPGA design were given with Quartus II. Result shows that the QDPSK modulator based on PLL is simple to design, convenient to modify or debug, and it operates stable.%介绍了QDPSK信号的优点,并分析了其实现原理,提出一种QDPSK高性能数字调制器的FPGA实现方案.采用自顶向下的设计思想,将系统分成串,并变换器、差分编码器、逻辑选相电路、四相载波发生器等4大模块.用原理图输入、VHDL语言设计和调用PLL核相结合的多种设计方法,分别实现了各模块的具体设计,并给出了其在Quar-tusⅡ环境下的仿真结果.结果表明,基于PLL的QDPSK调制器,设计简单,便于修改和调试,性能稳定.【总页数】4页(P22-25)【作者】刘国华;李二喜【作者单位】株洲职业技术学院,湖南,株洲,412008;株洲职业技术学院,湖南,株洲,412008【正文语种】中文【中图分类】TP311;TN919【相关文献】1.基于FPGA的调频广播调制器的设计与实现 [J], 黄红伟2.基于FPGA的QDPSK全数字通信电路的设计与实现 [J], 高雨晨;屈星3.基于FPGA的数字调制器设计与实现 [J], 蒋小燕;宗华姣;成旭;钱显毅;4.基于FPGA的数字调制器设计与实现 [J], 蒋小燕;宗华姣;成旭;钱显毅5.基于FPGA的QPSK调制器的设计与实现 [J], 虞亚君; 赵参因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的QPSK调制解调电路设计与实现数字调制信号又称为键控信号,调制过程可用键控的方法由基带信号对载频信号的振幅、频率及相位进行调制,最基本的方法有3种:正交幅度调制(QAM)、频移键控(FSK)、相移键控(PSK).根据所处理的基带信号的进制不同分为二进制和多进制调制(M进制).多进制数字调制与二进制相比,其频谱利用率更高.其中QPSK(即4PSK)是MPSK(多进制相移键控)中应用最广泛的一种调制方式。

1 QPSK简介QPSK信号有00、01、10、11四种状态.所以,对输入的二进制序列,首先必须分组,每两位码元一组。

然后根据组合情况,用载波的四种相位表征它们。

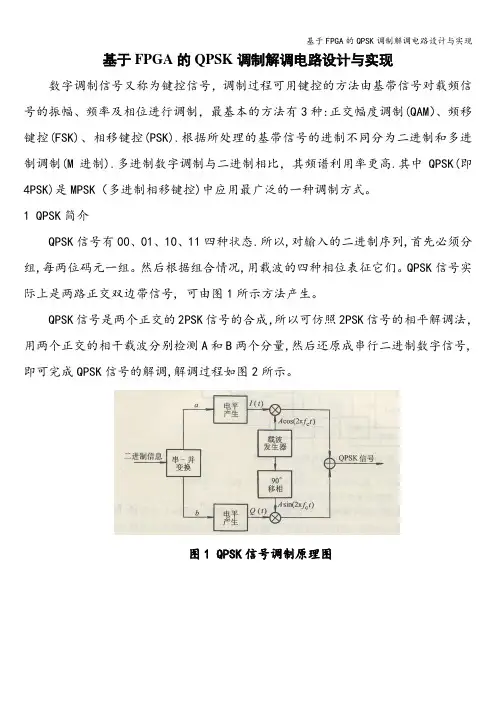

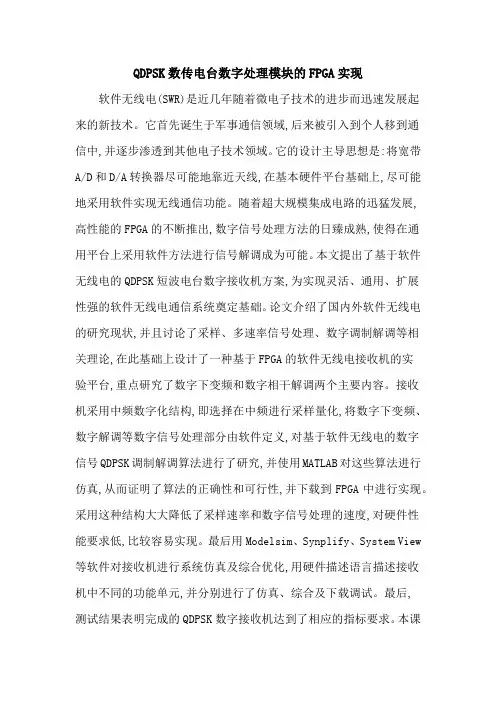

QPSK信号实际上是两路正交双边带信号, 可由图1所示方法产生。

QPSK信号是两个正交的2PSK信号的合成,所以可仿照2PSK信号的相平解调法,用两个正交的相干载波分别检测A和B两个分量,然后还原成串行二进制数字信号,即可完成QPSK信号的解调,解调过程如图2所示。

图1 QPSK信号调制原理图图2 QPSK 信号解调原理图2 QPSK 调制电路的FPGA 实现及仿真 2。

1基于FPGA 的QPSK 调制电路方框图基带信号通过串/并转换器得到2位并行信号,,四选一开关根据该数据,选择载波对应的相位进行输出,即得到调制信号,调制框图如图3所示。

基带信号clkstart串/并转换四选一开关分 频0°90°180°270°调制信号FPGA3 QPSK 调制电路框图系统顶层框图如下图中输入信号clk为调制模块时钟,start为调制模块的使能信号,x为基带信号,y是qpsk调制信号的输出端,carrier【3。

0】为4种不同相位的载波,其相位非别为0、90、180、270度,锁相环模块用来进行相位调节,用来模拟通信系统中发送时钟与接收时钟的不同步start1为解调模块的使能信号。

y2为解调信号的输出端。

图1QPSK 调制的原理架构低比特位a高比特位b载波相位θ00011111概述在无线通信与卫星通信中,针对数字信号处理,QPSK 是一种调制方法[1],它的频谱利用率高、抗干扰性强,是一种非常重要的调制解调方式。

近几年来,随着集成电路技术工艺革新,尤其是数字芯片越来越小型化与高速化,数字信号处理技术在通信系统中发挥的作用越发重要,越来越引起人们的重视。

介绍了QPSK 调制原理,运用硬件描述语言实现QPSK 调制,验证了数字调制系统的实现可行性。

2基本原理一个多进制数字相位调制(MPSK)信号码元[2]可以用以下公式(1)表示:(1)M =2k ,其中k 为正整数。

(2)其中A 为振幅,w 为角速度,两者都为常数,t 为调制时间。

θk 为间隔均匀的调试相位,它的值映射了基带码元的取值情况;公式(2)表示相位情况个数,当M =4时,调制方式即为QPSK 调制,它规定了4种载波相位:45°、135°、225°和315°。

QPSK 调制的输入数据是二进制数字序列,考虑到要和四进制的载波相位对应起来,要进行二进制转四进制,即把输入的二进制数据两两比特分组,共有4种组合情况:00、01、10、11,每一组称为双比特码元,它们表示四进制4个符号中的一个符号。

QPSK 调制每次可传输一个双比特码元[3],映射到4种相位的载波。

表1表示了双比特码元和载波相位θ之间映射关系,由表1可见,双比特码元采用格雷码的编码,好处在于相邻相位的双比特码元只有一位不同,假若发生相位误差至相邻相位上的情况,那么这样编码只会造成仅一个比特的误差。

目前,相位调制法与相位选择法[4]为QPSK 调制的主要实现方法,选取了相位选择法,编码调试在FPGA 环境下完成。

原理架构如图1所示,有源晶振50MHz 作为系统时钟,信号源模块使用伪随机序列PRBS,然后把序列输入串并转换模块,输出双比特流数据。

4种相位的载波从四相载波发生器产生。

QDPSK数传电台数字处理模块的FPGA实现软件无线电(SWR)是近几年随着微电子技术的进步而迅速发展起来的新技术。

它首先诞生于军事通信领域,后来被引入到个人移到通信中,并逐步渗透到其他电子技术领域。

它的设计主导思想是:将宽带A/D和D/A转换器尽可能地靠近天线,在基本硬件平台基础上,尽可能地采用软件实现无线通信功能。

随着超大规模集成电路的迅猛发展,高性能的FPGA的不断推出,数字信号处理方法的日臻成熟,使得在通用平台上采用软件方法进行信号解调成为可能。

本文提出了基于软件无线电的QDPSK短波电台数字接收机方案,为实现灵活、通用、扩展性强的软件无线电通信系统奠定基础。

论文介绍了国内外软件无线电的研究现状,并且讨论了采样、多速率信号处理、数字调制解调等相关理论,在此基础上设计了一种基于FPGA的软件无线电接收机的实验平台,重点研究了数字下变频和数字相干解调两个主要内容。

接收机采用中频数字化结构,即选择在中频进行采样量化,将数字下变频、数字解调等数字信号处理部分由软件定义,对基于软件无线电的数字信号QDPSK调制解调算法进行了研究,并使用MATLAB对这些算法进行仿真,从而证明了算法的正确性和可行性,并下载到FPGA中进行实现。

采用这种结构大大降低了采样速率和数字信号处理的速度,对硬件性能要求低,比较容易实现。

最后用Modelsim、Synplify、System View 等软件对接收机进行系统仿真及综合优化,用硬件描述语言描述接收机中不同的功能单元,并分别进行了仿真、综合及下载调试。

最后,测试结果表明完成的QDPSK数字接收机达到了相应的指标要求。

本课题设计使用MATLAB编制了基于软件无线电结构的通信信号调制解调平台软件,从而验证了软件无线电调制解调结构和算法的正确性,并实现了对各个功能模块的VHDL编程。

同时还提出了软件无线电平台的硬件结构设计思路,为对软件无线电理论的进一步研究奠定了基础。

1 引言交错正交相移键控(OQPSK)是继QPSK之后发展起来的一种恒包络数字调制技术,是QPSK的一种改进形式,也称为偏移四相相移键控(offset-QPSK),有时又称为参差四相相移键控(SQPSK)或者双二相相移键控(Double-QPSK)等。

它和QPSK有同样的相位关系,也是把输入码流分成两路,然后进行正交调制。

与普通的QPSK比较,交错正交相移键控的同相与正交两支路的数据流在时间上相互错开了半个码元周期,而不像QPSK那样I、Q两个数据流在时间上是一致的(即码元的沿是对齐的)。

OQPSK信号中,I(同相)、Q(正交)两个数据流,每次只有其中一个可能发生极性转换。

所以每当一个新的输入比特进入调制器的I 或Q信道时,输出的OQPSK信号中只有0°、±90°三个相位跳变值,而根本不可能出现180°相位跳变。

所以频带受限OQPSK的信号包络起伏比频带受限QPSK 的信号小,经限幅放大后频带展宽得少,故OQPSK性能优于QPSK。

本设计中OQPSK解调器接收端接收的信号是10.7MHz已调信号,按照软件无线电的设计思想,先进行计算机的模拟仿真,充分利用FPGA的特点,成功实现了对的10.7MHz的OQPSK信号差分解调。

解调器的技术指标为:解调器输出码:256 kb/s 、TTL电平;解调器输出时钟:256 KHz 、占空比50%。

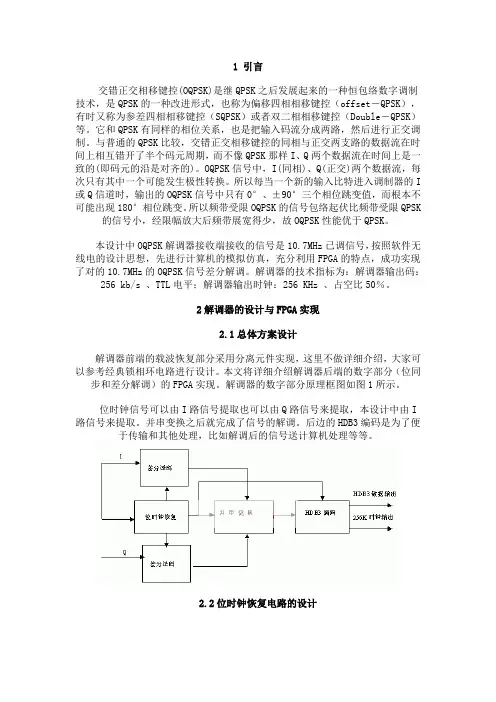

2解调器的设计与FPGA实现2.1总体方案设计解调器前端的载波恢复部分采用分离元件实现,这里不做详细介绍,大家可以参考经典锁相环电路进行设计。

本文将详细介绍解调器后端的数字部分(位同步和差分解调)的FPGA实现。

解调器的数字部分原理框图如图1所示。

位时钟信号可以由I路信号提取也可以由Q路信号来提取,本设计中由I 路信号来提取。

并串变换之后就完成了信号的解调。

后边的HDB3编码是为了便于传输和其他处理,比如解调后的信号送计算机处理等等。

基于FPGA的QDPSK全数字通信电路的设计与实现高雨晨;屈星【期刊名称】《电脑知识与技术》【年(卷),期】2013(000)016【摘要】In this paper, the basic principle is introduced ,and communication scheme is realized on FPGA. In the scheme, scram?bling code is added to the input data. After serial to parallel transformation and differential operation, the output sequence is the QDPSK signal. Then, the QDPSK signal is modulated. In the receiving terminal, through a series of inverse operation, the origi?nal signal is separated form obtained ODPSK signal. In whole system, programming language is Verilog, and all programs are sim?ulated in MaxPlusII. At last hardware test on FPGA indicates that the system is good.%介绍了QDPSK基本原理,提出基于FPGA 的全数字QDPSK通信方案。

该方案对输入序列进行加扰、串并和差分运算,得到QDPSK,然后加到载波上;在接收端载波与信号分离,再进行解差分、解扰运算,还原出输入信号,实现QDPSK全数字调制与解调。

整个系统采用Verilog编程,在MaxPlusII环境仿真、布局和综合,最后下载到FPGA通过示波器观察输入输出信号,实验效果良好。

网络通讯及安全本栏目责任编辑:冯蕾基于FPGA的QDPSK调制解调技术的研究及实现王磊,厉彦峰(天津工业大学信息与通信工程学院,天津300160)摘要:本文简述了调制解调系统的发展现状及FPGA的相关知识,介绍了QDPSK调制解调系统的理论算法,提出了QDPSK解调调制系统的具体实现方法。

关键词:FPGA;QDPSK;调制解调技术中图分类号:TP311文献标识码:A文章编号:1009-3044(2008)20-30237-03TheResearchandImplementationoftheModemTechnologyQDPSKVasedonFPGAWANGLei,LIYan-feng(TianjinIndustryUniversity,InformationandCommunicationEngineeringInstitute,Tianjin300160,China)Abstract:ThispaperdescribesthemodemsystemandthedevelopmentoftheFPGA-relatedknowledge,introducedtheQDPSKmodemsystemstheoryalgorithm,theQDPSKdemodulatormodulationsystemtoachievethespecificmethod.Keywords:FPGA;QDPSK;Modemtechnology1引言随着超大规模集成电路的发展,尤其是微电子技术和计算机技术的迅猛发展和广泛应用,数字化成为目前通信技术发展的趋势,它具有可靠性高,灵活性强,易大规模集成等优点,日益受到重视。

目前,数字化的手段主要有专用集成电路(ASIC)和通用数字信号处理器(DSP)。

专用集成电路是一种“硬”的设计方法,其优点是处理速度快,缺点是灵活性差。

DSP是一种“软”的设计方法,它能完成十分复杂的算法,使用灵活,易实现模块化,缺点是受处理器速度的限制。

QPSK调制解调器的设计及FPGA实现一、本文概述随着无线通信技术的飞速发展,调制解调器作为信息传输的关键部分,其性能对整个通信系统的稳定性和可靠性有着至关重要的影响。

四相相移键控(Quadrature Phase Shift Keying,QPSK)作为一种高效且稳定的调制方式,在无线通信中得到了广泛应用。

本文旨在深入研究QPSK调制解调器的设计,并探讨其在现场可编程门阵列(Field Programmable Gate Array,FPGA)上的实现方法。

本文首先将对QPSK调制解调的基本原理进行详细阐述,包括其信号处理方式、调制解调流程以及关键性能指标。

在此基础上,我们将探讨QPSK调制解调器的设计方法,包括调制器与解调器的结构选择、参数优化等。

同时,我们还将分析影响QPSK调制解调器性能的关键因素,如噪声、失真等,并提出相应的优化策略。

为了实现QPSK调制解调器的硬件化,本文将重点研究其在FPGA 上的实现方法。

我们将首先分析FPGA在数字信号处理方面的优势,然后详细介绍如何在FPGA上设计并实现QPSK调制解调器,包括硬件架构的选择、关键模块的设计与实现、以及资源优化等方面的内容。

我们还将讨论如何在实际应用中测试和优化FPGA实现的QPSK调制解调器,以确保其性能达到最佳状态。

本文旨在深入研究QPSK调制解调器的设计及其在FPGA上的实现方法,为无线通信系统的优化和升级提供理论支持和技术指导。

通过本文的研究,我们期望能够为相关领域的工程师和研究人员提供有益的参考和启示,推动QPSK调制解调技术的发展和应用。

二、QPSK调制原理QPSK,即四相相移键控(Quadrature Phase Shift Keying),是一种数字调制方式,它在每一符号周期内通过改变载波信号的相位来传递信息。

QPSK调制利用四个不同的相位状态来表示两个不同的比特组合,从而实现了更高的数据传输效率。

在QPSK调制中,每个符号通常代表两个比特的信息。

QPSK 调制器的FPGA 设计与实现高 松,彭大芹(重庆邮电大学 重庆 400065)摘 要:首先介绍QPSK 调制的基本原理,提出了一种基于FP GA 的全数字Q PSK 调制方案。

本文重点介绍了Q PSK 数字调制系统各个子模块的设计思路和流程,并对Quartus Ⅱ软件进行简单介绍,通过QuartusII 软件对各子模块和顶层文件进行综合和仿真,最后在基于stratix Ⅱ系列芯片EP2S30F672C5的PCB 板上证验了本设计的正确性和可行性。

关键词:Q PSK;FP GA ;Quartus Ⅱ;综合;仿真中图分类号:TN91 文献标识码:AQ PS K modulator FP GA design and implementationG ao Song ,Peng Daqin(Chongqing university of posts and telecommunication ,Chongqing 400065)Abstract :This paper first introduces t he basic p rinciples of Q PS K modulation ,and proposes a FP GA 2based all 2digital Q PS K modulation scheme.This article focuses on t he Q PS K digital modulation system sub 2module design and p rocess ,t hen give a brief int roduction of Quart us Ⅱ,t hrough t he various Sub 2module modules and top 2level document simulation ,and verify t he cor 2rect ness and feasibility of t he design in t he PCB board based on stratix Ⅱseries chip EP2S30F672C5.K eyw ords :Q PS K;FP GA ;Quart us Ⅱ;Synt hesis ;simulation0 引 言Q PS K 是在无线通信中应用比较广泛的一种调制方式,它具有较高的频谱利用率、较强的抗干扰性。